Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | S08                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 40MHz                                                                |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 17                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 512 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                      |

| Supplier Device Package    | 20-TSSOP                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh8ctj |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Section Number**

Title

### Page

| 6.3 | Ganged            | Output                        | 77 |  |  |

|-----|-------------------|-------------------------------|----|--|--|

| 6.4 | .4 Pin Interrupts |                               |    |  |  |

|     | 6.4.1             | Edge Only Sensitivity         | 78 |  |  |

|     | 6.4.2             | Edge and Level Sensitivity    | 78 |  |  |

|     | 6.4.3             | Pull-up/Pull-down Resistors   | 79 |  |  |

|     | 6.4.4             | Pin Interrupt Initialization  | 79 |  |  |

| 6.5 | Pin Beh           | avior in Stop Modes           | 79 |  |  |

| 6.6 | Parallel          | I/O and Pin Control Registers | 79 |  |  |

|     | 6.6.1             | Port A Registers              | 80 |  |  |

|     |                   | Port B Registers              |    |  |  |

|     | 6.6.3             | Port C Registers              | 89 |  |  |

|     |                   |                               |    |  |  |

## Chapter 7 Central Processor Unit (S08CPUV2)

| 7.1 | Introdu | ction                           | 93  |

|-----|---------|---------------------------------|-----|

|     | 7.1.1   | Features                        |     |

| 7.2 | Program | nmer's Model and CPU Registers  | 94  |

|     | 7.2.1   | Accumulator (A)                 | 94  |

|     | 7.2.2   | Index Register (H:X)            | 94  |

|     | 7.2.3   | Stack Pointer (SP)              | 95  |

|     | 7.2.4   | Program Counter (PC)            | 95  |

|     | 7.2.5   | Condition Code Register (CCR)   | 95  |

| 7.3 | Address | sing Modes                      | 97  |

|     | 7.3.1   | Inherent Addressing Mode (INH)  | 97  |

|     | 7.3.2   | Relative Addressing Mode (REL)  | 97  |

|     | 7.3.3   | Immediate Addressing Mode (IMM) | 97  |

|     | 7.3.4   | Direct Addressing Mode (DIR)    | 97  |

|     | 7.3.5   | Extended Addressing Mode (EXT)  |     |

|     | 7.3.6   | Indexed Addressing Mode         |     |

| 7.4 | Special | Operations                      |     |

|     | 7.4.1   | Reset Sequence                  |     |

|     | 7.4.2   | Interrupt Sequence              |     |

|     | 7.4.3   | Wait Mode Operation             | 100 |

|     | 7.4.4   | Stop Mode Operation             | 100 |

|     | 7.4.5   | BGND Instruction                | 101 |

| 7.5 | HCS08   | Instruction Set Summary         | 102 |

# Chapter 8 Analog Comparator 5-V (S08ACMPV2)

| 8.1 | Introduc | ction                          | 113 |

|-----|----------|--------------------------------|-----|

|     |          | ACMP Configuration Information |     |

|     | 8.1.2    | ACMP in Stop3 Mode             | 113 |

MC9S08SH8 MCU Series Data Sheet, Rev. 3

## **Section Number**

Title

## Page

|     | 8.1.3    | ACMP/TPM Configuration Information | 113 |

|-----|----------|------------------------------------|-----|

|     |          | Features                           |     |

|     | 8.1.5    | Modes of Operation                 | 115 |

|     |          | Block Diagram                      |     |

| 8.2 | External | Signal Description                 | 117 |

|     |          | Map                                |     |

|     |          | Register Descriptions              |     |

| 8.4 |          | al Description                     |     |

# Chapter 9 Analog-to-Digital Converter (S08ADCV1)

| 9.1 | Introduc | ction                                       | 121 |

|-----|----------|---------------------------------------------|-----|

|     | 9.1.1    | Channel Assignments                         | 121 |

|     | 9.1.2    | Alternate Clock                             | 122 |

|     | 9.1.3    | Hardware Trigger                            | 122 |

|     | 9.1.4    | Temperature Sensor                          | 122 |

|     | 9.1.5    | Features                                    | 125 |

|     | 9.1.6    | Block Diagram                               | 125 |

| 9.2 | Externa  | l Signal Description                        |     |

|     | 9.2.1    | Analog Power (V <sub>DDAD</sub> )           | 127 |

|     | 9.2.2    | Analog Ground (V <sub>SSAD</sub> )          | 127 |

|     | 9.2.3    | Voltage Reference High (V <sub>REFH</sub> ) | 127 |

|     | 9.2.4    | Voltage Reference Low (V <sub>REFL</sub> )  | 127 |

|     | 9.2.5    | Analog Channel Inputs (ADx)                 |     |

| 9.3 | Register | r Definition                                |     |

|     | 9.3.1    | Status and Control Register 1 (ADCSC1)      | 127 |

|     | 9.3.2    | Status and Control Register 2 (ADCSC2)      | 129 |

|     | 9.3.3    | Data Result High Register (ADCRH)           | 130 |

|     | 9.3.4    | Data Result Low Register (ADCRL)            | 130 |

|     | 9.3.5    | Compare Value High Register (ADCCVH)        | 131 |

|     | 9.3.6    | Compare Value Low Register (ADCCVL)         | 131 |

|     | 9.3.7    | Configuration Register (ADCCFG)             |     |

|     | 9.3.8    | Pin Control 1 Register (APCTL1)             | 133 |

|     | 9.3.9    | Pin Control 2 Register (APCTL2)             |     |

|     | 9.3.10   | Pin Control 3 Register (APCTL3)             | 135 |

| 9.4 | Function | nal Description                             | 136 |

|     | 9.4.1    | Clock Select and Divide Control             | 136 |

|     | 9.4.2    | Input Select and Pin Control                | 137 |

|     | 9.4.3    | Hardware Trigger                            | 137 |

|     | 9.4.4    | Conversion Control                          | 137 |

|     | 9.4.5    | Automatic Compare Function                  | 140 |

|     | 9.4.6    | MCU Wait Mode Operation                     | 140 |

#### MC9S08SH8 MCU Series Data Sheet, Rev. 3

### **Section Number**

### Title

### Page

|      | 13.3.3 RTC Modulo Register (RTCMOD)    |  |

|------|----------------------------------------|--|

| 13.4 | Functional Description                 |  |

|      | 13.4.1 RTC Operation Example           |  |

| 13.5 | Initialization/Application Information |  |

## Chapter 14 Serial Communications Interface (S08SCIV4)

| 14.1 | Introduc | tion                                       |  |

|------|----------|--------------------------------------------|--|

|      | 14.1.1   | Features                                   |  |

|      | 14.1.2   | Modes of Operation                         |  |

|      | 14.1.3   | Block Diagram                              |  |

| 14.2 | Register | Definition                                 |  |

|      |          | SCI Baud Rate Registers (SCIxBDH, SCIxBDL) |  |

|      | 14.2.2   | SCI Control Register 1 (SCIxC1)            |  |

|      | 14.2.3   | SCI Control Register 2 (SCIxC2)            |  |

|      | 14.2.4   | SCI Status Register 1 (SCIxS1)             |  |

|      | 14.2.5   | SCI Status Register 2 (SCIxS2)             |  |

|      | 14.2.6   | SCI Control Register 3 (SCIxC3)            |  |

|      | 14.2.7   | SCI Data Register (SCIxD)                  |  |

| 14.3 | Function | nal Description                            |  |

|      | 14.3.1   | Baud Rate Generation                       |  |

|      | 14.3.2   | Transmitter Functional Description         |  |

|      | 14.3.3   | Receiver Functional Description            |  |

|      |          | Interrupts and Status Flags                |  |

|      | 14.3.5   | Additional SCI Functions                   |  |

## Chapter 15 Serial Peripheral Interface (S08SPIV3)

| 15.1 | Introduction                                 |  |

|------|----------------------------------------------|--|

|      | 15.1.1 Features                              |  |

|      | 15.1.2 Block Diagrams                        |  |

|      | 15.1.3 SPI Baud Rate Generation              |  |

| 15.2 | External Signal Description                  |  |

|      | 15.2.1 SPSCK — SPI Serial Clock              |  |

|      | 15.2.2 MOSI — Master Data Out, Slave Data In |  |

|      | 15.2.3 MISO — Master Data In, Slave Data Out |  |

|      | 15.2.4 $\overline{SS}$ — Slave Select        |  |

| 15.3 | Modes of Operation                           |  |

|      | 15.3.1 SPI in Stop Modes                     |  |

| 15.4 | Register Definition                          |  |

|      | 15.4.1 SPI Control Register 1 (SPIC1)        |  |

|      | 15.4.2 SPI Control Register 2 (SPIC2)        |  |

|      |                                              |  |

# Chapter 1 Device Overview

The MC9S08SH8 members of the low-cost, high-performance HCS08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available with a variety of modules, memory sizes, memory types, and package types.

# 1.1 Devices in the MC9S08SH8 Series

Table 1-1 summarizes the feature set available in the MC9S08SH8 series of MCUs.

| Feature              | 9S08SH8 |     |     |                  | 9S08SH4 |      |     |                  |  |

|----------------------|---------|-----|-----|------------------|---------|------|-----|------------------|--|

| FLASH size (bytes)   |         | 81  | 92  |                  |         | 4096 |     |                  |  |

| RAM size (bytes)     |         | 5   | 12  |                  |         | 2    | 56  |                  |  |

| Pin quantity         | 24      | 20  | 16  | 8                | 24      | 20   | 16  | 8                |  |

| ACMP                 |         |     |     | ye               | es      |      |     |                  |  |

| ADC channels         | 12      | 12  | 8   | 4                | 12      | 12   | 8   | 4                |  |

| DBG                  |         |     |     | ye               | es      |      |     |                  |  |

| ICS                  | yes     | yes | yes | yes <sup>1</sup> | yes     | yes  | yes | yes <sup>1</sup> |  |

| IIC                  |         |     |     | ye               | es      |      |     |                  |  |

| MTIM                 |         |     |     | ye               | es      |      |     |                  |  |

| Pin Interrupts       | 8       | 8   | 8   | 4                | 8       | 8    | 8   | 4                |  |

| Pin I/O <sup>2</sup> | 17      | 17  | 13  | 5                | 17      | 17   | 13  | 5                |  |

| RTC                  |         |     |     | ye               | es      |      |     |                  |  |

| SCI                  | yes     | yes | yes | no               | yes     | yes  | yes | no               |  |

| SPI                  | yes     | yes | yes | no               | yes     | yes  | yes | no               |  |

| TPM1 channels        | 2       | 2   | 2   | 1                | 2       | 2    | 2   | 1                |  |

| TPM2 channels        | 2       | 2   | 2   | 1                | 2       | 2    | 2   | 1                |  |

| XOSC                 | yes     | yes | yes | no               | yes     | yes  | yes | no               |  |

#### Table 1-1. MC9S08SH8 Features by MCU and Package

<sup>1</sup> FBE and FEE modes are not available in 8-pin packages.

<sup>2</sup> Port I/O count does not include the output-only PTA4/ACMPO/BKGD/MS.

#### Table 1-2 provides the functional version of the on-chip modules

| Module                          | Version |   |

|---------------------------------|---------|---|

| Analog Comparator (5V)          | (ACMP)  | 2 |

| Analog-to-Digital Converter     | (ADC)   | 1 |

| Central Processor Unit          | (CPU)   | 2 |

| Inter-Integrated Circuit        | (IIC)   | 2 |

| Internal Clock Source           | (ICS)   | 2 |

| Serial Peripheral Interface     | (SPI)   | 3 |

| Serial Communications Interface | (SCI)   | 4 |

| Modulo Timer                    | (MTIM)  | 1 |

| Real-Time Counter               | (RTC)   | 1 |

| Timer Pulse Width Modulator     | (TPM)   | 3 |

#### Table 1-2. Module Versions

Chapter 4 Memory

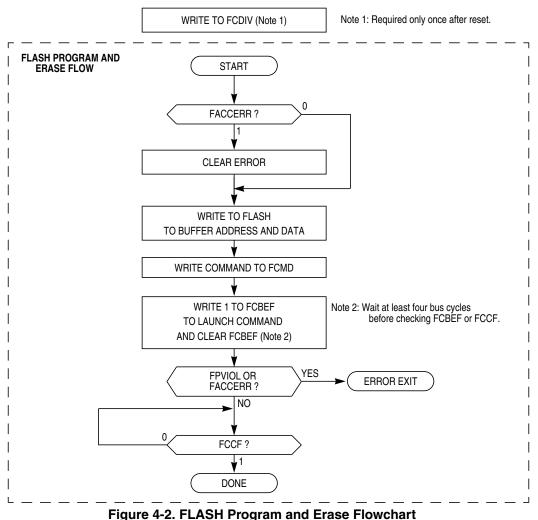

#### rigure +-2. I EASIT Program and Erase Prowe

#### 4.5.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst program command is issued, the charge pump is enabled and then remains enabled after completion of the burst program operation if these two conditions are met:

- The next burst program command has been queued before the current program operation has completed.

- The next sequential address selects a byte on the same physical row as the current byte being programmed. A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero.

**Chapter 6 Parallel Input/Output Control**

## 6.6.1 Port A Registers

Port A is controlled by the registers listed below.

The pins PTA4 and PTA5 are unique. PTA4 is output-only, so the control bits for the input function will not have any effect on this pin. PTA5, when configured as an output, is open drain with low drive strength.

#### NOTE

This PTA5 pin does not contain a clamp diode to  $V_{\text{DD}}$  and should not be driven above  $V_{\text{DD}}.$

When the internal pullup device is enabled on PTA5 when used as an input or open drain output the voltage measured on PTA5 will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . If the PTA5 pin is required to drive to a  $V_{DD}$  level an external pullup should be used.

### 6.6.1.1 Port A Data Register (PTAD)

|        | 7 | 6 | 5      | 4                  | 3      | 2      | 1     | 0     |

|--------|---|---|--------|--------------------|--------|--------|-------|-------|

| R      | 0 | 0 | PTAD5  | PTAD4 <sup>1</sup> | PTAD3  | PTAD2  | PTAD1 | PTAD0 |

| w      |   |   | F IAD5 | F IAD4             | F IAD3 | F IAD2 | FIADI | FIADU |

| Reset: | 0 | 0 | 0      | 0                  | 0      | 0      | 0     | 0     |

#### Figure 6-3. Port A Data Register (PTAD)

<sup>1</sup> Reads of bit PTAD4 always return the contents of PTAD4, regardless of the value stored in bit PTADD4.

#### Table 6-2. PTAD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0<br>PTAD[5:0] | Port A Data Register Bits — For port A pins that are inputs, reads return the logic level on the pin. For port A pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port A pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTAD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups/pull-downs disabled. |

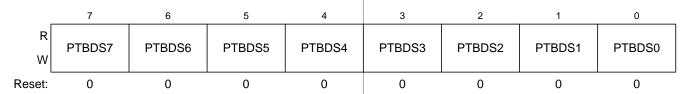

## 6.6.2.5 Port B Drive Strength Selection Register (PTBDS)

Figure 6-15. Drive Strength Selection for Port B Register (PTBDS)

#### Table 6-14. PTBDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBDS[7:0] | <ul> <li>Output Drive Strength Selection for Port B Bits — Each of these control bits selects between low and high output drive for the associated PTB pin. For port B pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port B bit n.</li> <li>1 High output drive strength selected for port B bit n.</li> </ul> |

### 6.6.2.6 Port B Interrupt Status and Control Register (PTBSC)

|        | 7 | 6 | 5 | 4 | 3     | 2      | 1     | 0       |

|--------|---|---|---|---|-------|--------|-------|---------|

| R      | 0 | 0 | 0 | 0 | PTBIF | 0      | PTBIE | PTBMOD  |

| W      |   |   |   |   |       | PTBACK | PIDE  | PIDNUUD |

| Reset: | 0 | 0 | 0 | 0 | 0     | 0      | 0     | 0       |

Figure 6-16. Port B Interrupt Status and Control Register (PTBSC)

#### Table 6-15. PTBSC Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PTBIF  | <ul> <li>Port B Interrupt Flag — PTBIF indicates when a Port B interrupt is detected. Writes have no effect on PTBIF.</li> <li>0 No Port B interrupt detected.</li> <li>1 Port B interrupt detected.</li> </ul>                         |

| 2<br>PTBACK | <b>Port B Interrupt Acknowledge</b> — Writing a 1 to PTBACK is part of the flag clearing mechanism. PTBACK always reads as 0.                                                                                                           |

| 1<br>PTBIE  | <ul> <li>Port B Interrupt Enable — PTBIE determines whether a port B interrupt is requested.</li> <li>0 Port B interrupt request not enabled.</li> <li>1 Port B interrupt request enabled.</li> </ul>                                   |

| 0<br>PTBMOD | <ul> <li>Port B Detection Mode — PTBMOD (along with the PTBES bits) controls the detection mode of the port B interrupt pins.</li> <li>0 Port B pins detect edges only.</li> <li>1 Port B pins detect both edges and levels.</li> </ul> |

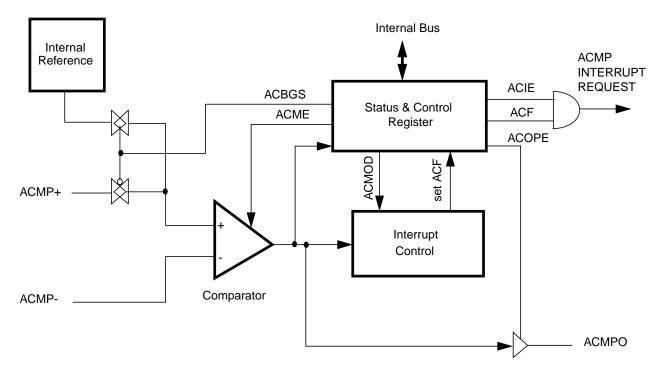

Chapter 8 Analog Comparator (S08ACMPV2)

Figure 8-2. Analog Comparator 5V (ACMP5) Block Diagram

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>ACFE  | <ul> <li>Compare Function Enable — ACFE is used to enable the compare function.</li> <li>0 Compare function disabled</li> <li>1 Compare function enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                            |

| 4<br>ACFGT | <ul> <li>Compare Function Greater Than Enable — ACFGT is used to configure the compare function to trigger when the result of the conversion of the input being monitored is greater than or equal to the compare value. The compare function defaults to triggering when the result of the compare of the input being monitored is less than the compare value.</li> <li>0 Compare triggers when input is less than compare level</li> <li>1 Compare triggers when input is greater than or equal to compare level</li> </ul> |

#### Table 9-4. ADCSC2 Register Field Descriptions (continued)

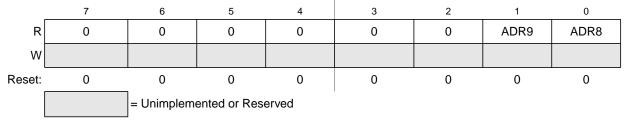

### 9.3.3 Data Result High Register (ADCRH)

ADCRH contains the upper two bits of the result of a 10-bit conversion. When configured for 8-bit conversions both ADR8 and ADR9 are equal to zero. ADCRH is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. In 10-bit MODE, reading ADCRH prevents the ADC from transferring subsequent conversion results into the result registers until ADCRL is read. If ADCRL is not read until after the next conversion is completed, then the intermediate conversion result will be lost. In 8-bit mode there is no interlocking with ADCRL. In the case that the MODE bits are changed, any data in ADCRH becomes invalid.

Figure 9-6. Data Result High Register (ADCRH)

### 9.3.4 Data Result Low Register (ADCRL)

ADCRL contains the lower eight bits of the result of a 10-bit conversion, and all eight bits of an 8-bit conversion. This register is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. In 10-bit mode, reading ADCRH prevents the ADC from transferring subsequent conversion results into the result registers until ADCRL is read. If ADCRL is not read until the after next conversion is completed, then the intermediate conversion results will be lost. In 8-bit mode, there is no interlocking with ADCRH. In the case that the MODE bits are changed, any data in ADCRL becomes invalid.

Chapter 9 Analog-to-Digital Converter (S08ADC10V1)

## 10.1.4.4 FLL Bypassed Internal Low Power (FBILP)

In FLL bypassed internal low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the internal reference clock. The BDC clock is not available.

## 10.1.4.5 FLL Bypassed External (FBE)

In FLL bypassed external mode, the FLL is enabled and controlled by an external reference clock, but is bypassed. The ICS supplies a clock derived from the external reference clock. The external reference clock can be an external crystal/resonator supplied by an OSC controlled by the ICS, or it can be another external clock source. The BDC clock is supplied from the FLL.

## 10.1.4.6 FLL Bypassed External Low Power (FBELP)

In FLL bypassed external low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the external reference clock. The external reference clock can be an external crystal/resonator supplied by an OSC controlled by the ICS, or it can be another external clock source. The BDC clock is not available.

### 10.1.4.7 Stop (STOP)

In stop mode the FLL is disabled and the internal or external reference clocks can be selected to be enabled or disabled. The BDC clock is not available and the ICS does not provide an MCU clock source.

## 10.2 External Signal Description

There are no ICS signals that connect off chip.

## 10.3 Register Definitio

Figure 10-1 is a summary of ICS registers.

| Table 10-1 | ICS | Register | Summary |

|------------|-----|----------|---------|

|------------|-----|----------|---------|

| Name   |   | 7    | 6 | 5     | 4      | 3    | 2     | 1          | 0        |

|--------|---|------|---|-------|--------|------|-------|------------|----------|

| ICSC1  | R | CLKS |   |       | RDIV   |      | IREFS | IRCLKEN    | IREFSTEN |

|        | W |      |   | NDIV  |        |      |       | INCOLINEIN |          |

| ICSC2  | R | BDIV |   | RANGE | HGO    | LP   | EREFS | ERCLKEN    | EREFSTEN |

| 10002  | W |      |   |       | 100    | L1   |       |            |          |

| ICSTRM | R |      |   |       |        | TRIM |       |            |          |

|        | W |      |   |       |        |      |       |            |          |

| ICSSC  | R | 0    | 0 | 0     | IREFST | CL   | KST   | OSCINIT    | FTRIM    |

| 10350  | W |      |   |       |        |      |       |            |          |

If EREFSTEN is set and the ERCLKEN bit is written to 1, the external reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

## 10.4.7 Fixed Frequency Clock

The ICS presents the divided FLL reference clock as ICSFFCLK for use as an additional clock source for peripheral modules. The ICS provides an output signal (ICSFFE) which indicates when the ICS is providing ICSOUT frequencies four times or greater than the divided FLL reference clock (ICSFFCLK). In FLL Engaged mode (FEI and FEE) this is always true and ICSFFE is always high. In ICS Bypass modes, ICSFFE will get asserted for the following combinations of BDIV and RDIV values:

- BDIV=00 (divide by 1), RDIV  $\geq$  010

- BDIV=01 (divide by 2), RDIV  $\ge$  011

- BDIV=10 (divide by 4), RDIV  $\geq$  100

- BDIV=11 (divide by 8), RDIV  $\geq$  101

message characters. At the end of a message, or at the beginning of the next message, all receivers automatically force RWU to 0 so all receivers wake up in time to look at the first character(s) of the next message.

#### 14.3.3.2.1 Idle-Line Wakeup

When WAKE = 0, the receiver is configured for idle-line wakeup. In this mode, RWU is cleared automatically when the receiver detects a full character time of the idle-line level. The M control bit selects 8-bit or 9-bit data mode that determines how many bit times of idle are needed to constitute a full character time (10 or 11 bit times because of the start and stop bits).

When RWU is one and RWUID is zero, the idle condition that wakes up the receiver does not set the IDLE flag. The receiver wakes up and waits for the first data character of the next message which will set the RDRF flag and generate an interrupt if enabled. When RWUID is one, any idle condition sets the IDLE flag and generates an interrupt if enabled, regardless of whether RWU is zero or one.

The idle-line type (ILT) control bit selects one of two ways to detect an idle line. When ILT = 0, the idle bit counter starts after the start bit so the stop bit and any logic 1s at the end of a character count toward the full character time of idle. When ILT = 1, the idle bit counter does not start until after a stop bit time, so the idle detection is not affected by the data in the last character of the previous message.

#### 14.3.3.2.2 Address-Mark Wakeup

When WAKE = 1, the receiver is configured for address-mark wakeup. In this mode, RWU is cleared automatically when the receiver detects a logic 1 in the most significant bit of a received character (eighth bit in M = 0 mode and ninth bit in M = 1 mode).

Address-mark wakeup allows messages to contain idle characters but requires that the MSB be reserved for use in address frames. The logic 1 MSB of an address frame clears the RWU bit before the stop bit is received and sets the RDRF flag. In this case the character with the MSB set is received even though the receiver was sleeping during most of this character time.

### 14.3.4 Interrupts and Status Flags

The SCI system has three separate interrupt vectors to reduce the amount of software needed to isolate the cause of the interrupt. One interrupt vector is associated with the transmitter for TDRE and TC events. Another interrupt vector is associated with the receiver for RDRF, IDLE, RXEDGIF and LBKDIF events, and a third vector is used for OR, NF, FE, and PF error conditions. Each of these ten interrupt sources can be separately masked by local interrupt enable masks. The flags can still be polled by software when the local masks are cleared to disable generation of hardware interrupt requests.

The SCI transmitter has two status flags that optionally can generate hardware interrupt requests. Transmit data register empty (TDRE) indicates when there is room in the transmit data buffer to write another transmit character to SCIxD. If the transmit interrupt enable (TIE) bit is set, a hardware interrupt will be requested whenever TDRE = 1. Transmit complete (TC) indicates that the transmitter is finished transmitting all data, preamble, and break characters and is idle with TxD at the inactive level. This flag is often used in systems with modems to determine when it is safe to turn off the modem. If the transmit complete interrupt enable (TCIE) bit is set, a hardware TC = 1.

# 16.3 Register Definitio

This section consists of register descriptions in address order. A typical MCU system may contain multiple TPMs, and each TPM may have one to eight channels, so register names include placeholder characters to identify which TPM and which channel is being referenced. For example, TPMxCnSC refers to timer (TPM) x, channel n. TPM1C2SC would be the status and control register for channel 2 of timer 1.

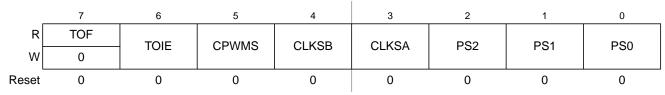

## 16.3.1 TPM Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits used to configure the interrupt enable, TPM configuration, clock source, and prescale factor. These controls relate to all channels within this timer module.

Figure 16-7. TPM Status and Control Register (TPMxSC)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF   | Timer overflow flag. This read/write flag is set when the TPM counter resets to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. Clear TOF by reading the TPM status and control register when TOF is set and then writing a logic 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. This is done so a TOF interrupt request cannot be lost during the clearing sequence for a previous TOF. Reset clears TOF. Writing a logic 1 to TOF has no effect.<br>0 TPM counter has not reached modulo value or overflow<br>1 TPM counter has overflowed |

| 6<br>TOIE  | Timer overflow interrupt enable. This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals one. Reset clears TOIE.<br>0 TOF interrupts inhibited (use for software polling)<br>1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5<br>CPWMS | <ul> <li>Center-aligned PWM select. When present, this read/write bit selects CPWM operating mode. By default, the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up/down counting mode for CPWM functions. Reset clears CPWMS.</li> <li>0 All channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register.</li> <li>1 All channels operate in center-aligned PWM mode.</li> </ul>                                                                                                                                  |

| CPWMS | MSnB:MSnA | ELSnB:ELSnA | Mode                  | Configuratio                                  |

|-------|-----------|-------------|-----------------------|-----------------------------------------------|

| 0     | 00        | 01          | Input capture         | Capture on rising edge only                   |

|       |           | 10          |                       | Capture on falling edge only                  |

|       |           | 11          |                       | Capture on rising or falling edge             |

|       | 01        | 01          | Output compare        | Toggle output on compare                      |

|       |           | 10          |                       | Clear output on compare                       |

|       |           | 11          | _                     | Set output on compare                         |

|       | 1X        | 10          | Edge-aligned<br>PWM   | High-true pulses (clear output on compare)    |

|       |           | X1          |                       | Low-true pulses (set output on compare)       |

| 1     | XX        | 10          | Center-aligned<br>PWM | High-true pulses (clear output on compare-up) |

|       |           | X1          |                       | Low-true pulses (set output on compare-up)    |

Table 16-7. Mode, Edge, and Level Selection

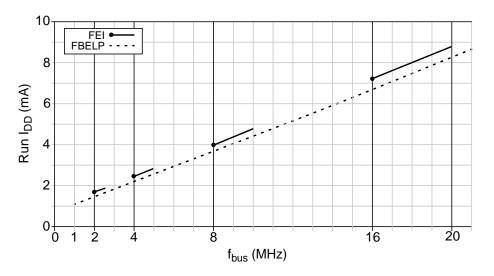

#### 16.3.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)

These read/write registers contain the captured TPM counter value of the input capture function or the output compare value for the output compare or PWM functions. The channel registers are cleared by reset.

| _      | 7      | 6  | 5  | 4  | 3  | 2  | 1 | 0     |

|--------|--------|----|----|----|----|----|---|-------|

| R<br>W | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

| Reset  | 0      | 0  | 0  | 0  | 0  | 0  | 0 | 0     |

|        | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

Figure 16-14. TPM Channel Value Register Low (TPMxCnVL)

In input capture mode, reading either byte (TPMxCnVH or TPMxCnVL) latches the contents of both bytes into a buffer where they remain latched until the other half is read. This latching mechanism also resets

MC9S08SH8 MCU Series Data Sheet, Rev. 3

#### Chapter 16 Timer/PWM Module (S08TPMV3)

(becomes unlatched) when the TPMxCnSC register is written (whether BDM mode is active or not). Any write to the channel registers will be ignored during the input capture mode.

When BDM is active, the coherency mechanism is frozen (unless reset by writing to TPMxCnSC register) such that the buffer latches remain in the state they were in when the BDM became active, even if one or both halves of the channel register are read while BDM is active. This assures that if the user was in the middle of reading a 16-bit register when BDM became active, it will read the appropriate value from the other half of the 16-bit value after returning to normal execution. The value read from the TPMxCnVH and TPMxCnVL registers in BDM mode is the value of these registers and not the value of their read buffer.

In output compare or PWM modes, writing to either byte (TPMxCnVH or TPMxCnVL) latches the value into a buffer. After both bytes are written, they are transferred as a coherent 16-bit value into the timer-channel registers according to the value of CLKSB:CLKSA bits and the selected mode, so:

- If (CLKSB:CLKSA = 0:0), then the registers are updated when the second byte is written.

- If (CLKSB:CLKSA not = 0:0 and in output compare mode) then the registers are updated after the second byte is written and on the next change of the TPM counter (end of the prescaler counting).

- If (CLKSB:CLKSA not = 0:0 and in EPWM or CPWM modes), then the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL - 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter then the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

The latching mechanism may be manually reset by writing to the TPMxCnSC register (whether BDM mode is active or not). This latching mechanism allows coherent 16-bit writes in either big-endian or little-endian order which is friendly to various compiler implementations.

When BDM is active, the coherency mechanism is frozen such that the buffer latches remain in the state they were in when the BDM became active even if one or both halves of the channel register are written while BDM is active. Any write to the channel registers bypasses the buffer latches and directly write to the channel register while BDM is active. The values written to the channel register while BDM is active are used for PWM & output compare operation once normal execution resumes. Writes to the channel registers while BDM is active do not interfere with partial completion of a coherency sequence. After the coherency mechanism has been fully exercised, the channel registers are updated using the buffered values written (while BDM was not active) by the user.

# 16.4 Functional Description

All TPM functions are associated with a central 16-bit counter which allows flexible selection of the clock source and prescale factor. There is also a 16-bit modulo register associated with the main counter.

The CPWMS control bit chooses between center-aligned PWM operation for all channels in the TPM (CPWMS=1) or general purpose timing functions (CPWMS=0) where each channel can independently be configured to operate in input capture, output compare, or edge-aligned PWM mode. The CPWMS control bit is located in the main TPM status and control register because it affects all channels within the TPM and influences the way the main counter operates. (In CPWM mode, the counter changes to an up/down mode rather than the up-counting mode used for general purpose timer functions.)

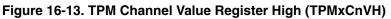

- <sup>1</sup> Typical values are based on characterization data at 25°C. See Figure A-5 through Figure A-7 for typical curves across voltage/temperature.

- <sup>2</sup> Max values in this column apply for the full operating temperature range of the device unless otherwise noted.

- <sup>3</sup> All modules except ADC active, ICS configured for FBE, and does not include any dc loads on port pins.

- <sup>4</sup> All modules except ADC active, ICS configured for FEI, and does not include any dc loads on port pins.

- <sup>5</sup> Stop currents are tested in production for 25°C on all parts. Tests at other temperatures depend upon the part number suffix and maturity of the product. Freescale may eliminate a test insertion at a particular temperature from the production test flow once sufficient data has been collected and is approved.

- <sup>6</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode.

- <sup>7</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768kHz crystal and low power mode (HGO = 0).

Figure A-5. Typical Run  $I_{DD}$  vs. Bus Frequency ( $V_{DD} = 5V$ )

**Appendix A Electrical Characteristics**

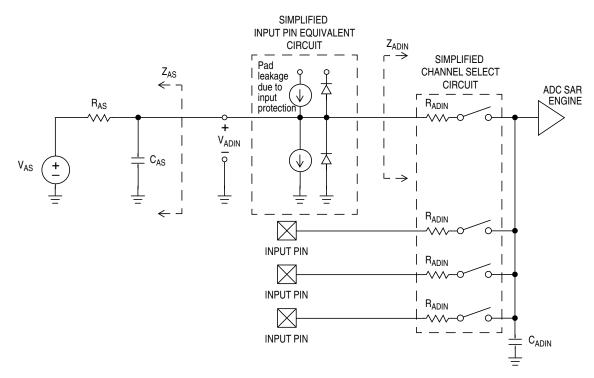

# A.11 ADC Characteristics

Table A-11. ADC Operating Conditions

| Characteristic                   | Conditions                                                          | Symb              | Min               | Typ <sup>1</sup> | Max               | Unit | Comment         |

|----------------------------------|---------------------------------------------------------------------|-------------------|-------------------|------------------|-------------------|------|-----------------|

| Supply voltage                   | Absolute                                                            | V <sub>DDAD</sub> | 2.7               | _                | 5.5               | V    |                 |

| Input Voltage                    |                                                                     | V <sub>ADIN</sub> | V <sub>REFL</sub> | _                | V <sub>REFH</sub> | V    |                 |

| Input<br>Capacitance             |                                                                     | C <sub>ADIN</sub> | _                 | 4.5              | 5.5               | pF   |                 |

| Input<br>Resistance              |                                                                     | R <sub>ADIN</sub> | _                 | 3                | 5                 | kΩ   |                 |

| Analog Source<br>Resistance      | 10 bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz | R <sub>AS</sub>   |                   |                  | 5<br>10           | kΩ   | External to MCU |

|                                  | 8 bit mode (all valid f <sub>ADCK</sub> )                           |                   | _                 | _                | 10                |      |                 |

| ADC<br>Conversion<br>Clock Freq. | High Speed (ADLPC=0)                                                | f <sub>ADCK</sub> | 0.4               | _                | 8.0               | MHz  |                 |

|                                  | Low Power (ADLPC=1)                                                 |                   | 0.4               | _                | 4.0               |      |                 |

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = V<sub>DD</sub> = 5.0V, Temp = 25°C, fADCK=1.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

Figure A-9. ADC Input Impedance Equivalency Diagram

| Characteristic                                             | Conditions                    | С     | Symb                                   | Min        | Typ <sup>1</sup> | Max      | Unit             | Comment                                                |

|------------------------------------------------------------|-------------------------------|-------|----------------------------------------|------------|------------------|----------|------------------|--------------------------------------------------------|

| Supply current                                             | ADLPC=1<br>ADLSMP=1<br>ADCO=1 | Т     | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _          | 133              | _        | μA               | ADC current<br>only                                    |

| Supply current                                             | ADLPC=1<br>ADLSMP=0<br>ADCO=1 | Т     | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _          | 218              | _        | μА               | ADC current<br>only                                    |

| Supply current                                             | ADLPC=0<br>ADLSMP=1<br>ADCO=1 | Т     | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _          | 327              | _        | μА               | ADC current<br>only                                    |

| Supply current                                             | ADLPC=0<br>ADLSMP=0<br>ADCO=1 | Ρ     | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _          | 0.582            | 1        | mA               | ADC current<br>only                                    |

| ADC<br>asynchronous<br>clock source                        | High speed (ADLPC=0)          | P     | f <sub>ADACK</sub>                     | 2          | 3.3              | 5        | MHz              | t <sub>ADACK</sub> =<br>1/f <sub>ADACK</sub>           |

|                                                            | Low power (ADLPC=1)           |       |                                        | 1.25       | 2                | 3.3      |                  |                                                        |

| Conversion time                                            | Short sample (ADLSMP=0)       |       | t <sub>ADC</sub>                       | _          | 20               | _        | ADCK<br>cycles   | See ADC<br>Chapter for<br>conversion<br>time variances |

| (including sample time)                                    | Long sample (ADLSMP=1)        | D     |                                        | _          | 40               | _        |                  |                                                        |

| Sample time                                                | Short sample (ADLSMP=0)       | D     | t <sub>ADS</sub>                       | _          | 3.5              | _        | ADCK<br>cycles   |                                                        |

|                                                            | Long sample (ADLSMP=1)        |       |                                        | _          | 23.5             | _        |                  |                                                        |

| Total unadjusted<br>error (Includes<br>quantization)       | 10 bit mode                   | - P   | E <sub>TUE</sub>                       | _          | ±1.5             | ±3.5     | LSB <sup>2</sup> |                                                        |

|                                                            | 8 bit mode                    |       |                                        |            | ±0.7             | ±1.5     | LSB <sup>2</sup> |                                                        |

| Differential<br>Non-Linearity                              | 10 bit mode                   | - P   | DNL                                    | _          | ±0.5             | ±1.0     | LSB <sup>2</sup> |                                                        |

|                                                            | 8 bit mode                    |       |                                        | _          | ±0.3             | ±0.5     |                  |                                                        |

|                                                            | Ν                             | lonot | onicity and N                          | No-Missing | J-Codes gu       | aranteed |                  |                                                        |

| Integral<br>non-linearity                                  | 10 bit mode                   | - т   | INL                                    | _          | ±0.5             | ±1.0     | LSB <sup>2</sup> |                                                        |

|                                                            | 8 bit mode                    |       |                                        | _          | ±0.3             | ±0.5     |                  |                                                        |

| Zero-scale error                                           | 10 bit mode                   | P     | E <sub>ZS</sub>                        | _          | ±1.5             | ±2.5     | LSB <sup>2</sup> |                                                        |

|                                                            | 8 bit mode                    |       |                                        | _          | ±0.5             | ±0.7     |                  |                                                        |

| Full-scale error<br>(V <sub>ADIN</sub> = V <sub>DD</sub> ) | 10 bit mode                   | - т   | E <sub>FS</sub>                        | 0          | ±1.0             | ±1.5     | LSB <sup>2</sup> |                                                        |

|                                                            | 8 bit mode                    |       |                                        | 0          | ±0.5             | ±0.5     |                  |                                                        |

| Quantization error                                         | 10 bit mode                   | - D   | EQ                                     | _          | _                | ±0.5     | LSB <sup>2</sup> |                                                        |

|                                                            | 8 bit mode                    |       |                                        | _          | _                | ±0.5     |                  |                                                        |

| Input leakage error                                        | 10 bit mode                   | – D   | E <sub>IL</sub>                        | 0          | ±0.2             | ±2.5     | LSB <sup>2</sup> | Pad leakage <sup>2</sup> *<br>R <sub>AS</sub>          |

|                                                            | 8 bit mode                    |       |                                        | 0          | ±0.1             | ±1       |                  |                                                        |

#### Table A-12. ADC Characteristics