# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 17                                                                    |

| Program Memory Size        | 8KB (8K × 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 20-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh8cwjr |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Freescale Semiconductor**

Datasheet Addendum

MC9S08SH8AD Rev. 1, 05/2012

# MC9S08SH8 Datasheet Addendum

This addendum describes corrections or updates to the *MC9S08SH8 Datasheet*, file named as MC9S08SH8. Please check our website at http://www.freescale.com/, for the latest updates.

The current version available of the *MC9S08SH8 Datasheet* is Revision 3.0.

#### Table of Contents

| 1 | Addendum for Revision 3.0. | 2 |

|---|----------------------------|---|

| 2 | Revision History           | 2 |

## **Section Number**

Title

## Page

|      | 17.2.2   | Communication Details                                | 270 |

|------|----------|------------------------------------------------------|-----|

|      | 17.2.3   | BDC Commands                                         | 274 |

|      | 17.2.4   | BDC Hardware Breakpoint                              | 276 |

| 17.3 | On-Chip  | Debug System (DBG)                                   | 277 |

|      | 17.3.1   | Comparators A and B                                  | 277 |

|      | 17.3.2   | Bus Capture Information and FIFO Operation           | 277 |

|      | 17.3.3   | Change-of-Flow Information                           | 278 |

|      | 17.3.4   | Tag vs. Force Breakpoints and Triggers               | 278 |

|      | 17.3.5   | Trigger Modes                                        | 279 |

|      | 17.3.6   | Hardware Breakpoints                                 | 281 |

| 17.4 | Register | Definition                                           | 281 |

|      | 17.4.1   | BDC Registers and Control Bits                       | 281 |

|      | 17.4.2   | System Background Debug Force Reset Register (SBDFR) | 283 |

|      | 17.4.3   | DBG Registers and Control Bits                       | 284 |

|      |          |                                                      |     |

# Appendix A Electrical Characteristics

| A.1  | Introduction                                |     |

|------|---------------------------------------------|-----|

| A.2  | Parameter Classification                    |     |

| A.3  | Absolute Maximum Ratings                    |     |

| A.4  | Thermal Characteristics                     | 291 |

| A.5  | ESD Protection and Latch-Up Immunity        |     |

| A.6  | DC Characteristics                          |     |

| A.7  | Supply Current Characteristics              | 298 |

| A.8  | External Oscillator (XOSC) Characteristics  | 301 |

| A.9  | Internal Clock Source (ICS) Characteristics | 303 |

|      | Analog Comparator (ACMP) Electricals        |     |

| A.11 | ADC Characteristics                         |     |

| A.12 | AC Characteristics                          |     |

|      | A.12.1 Control Timing                       |     |

|      | A.12.2 TPM/MTIM Module Timing               | 311 |

|      | A.12.3 SPI                                  |     |

| A.13 | FLASH Specifications                        |     |

| A.14 | EMC Performance                             |     |

|      | A.14.1 Radiated Emissions                   |     |

|      | A.14.2 Conducted Transient Susceptibility   |     |

|      |                                             |     |

# Appendix B Ordering Information and Mechanical Drawings

| <b>B</b> .1 | Orderin | g Information           | 319 |

|-------------|---------|-------------------------|-----|

|             | B.1.1   | Device Numbering Scheme | 319 |

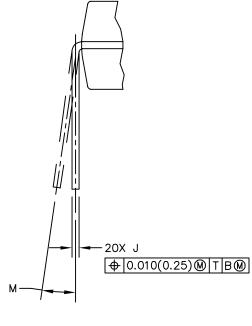

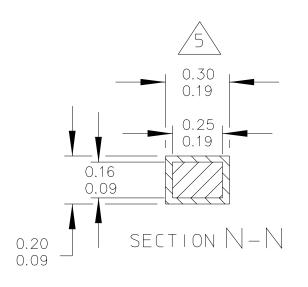

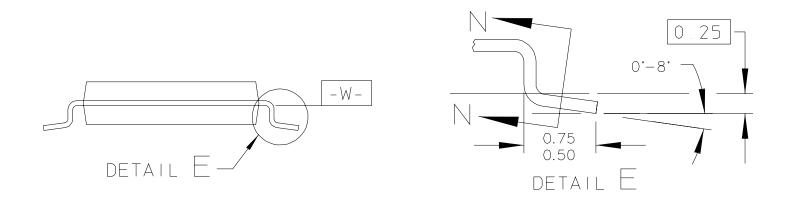

| <b>B</b> .2 | Mechan  | nical Drawings          | 320 |

MC9S08SH8 MCU Series Data Sheet, Rev. 3

# Chapter 2 Pins and Connections

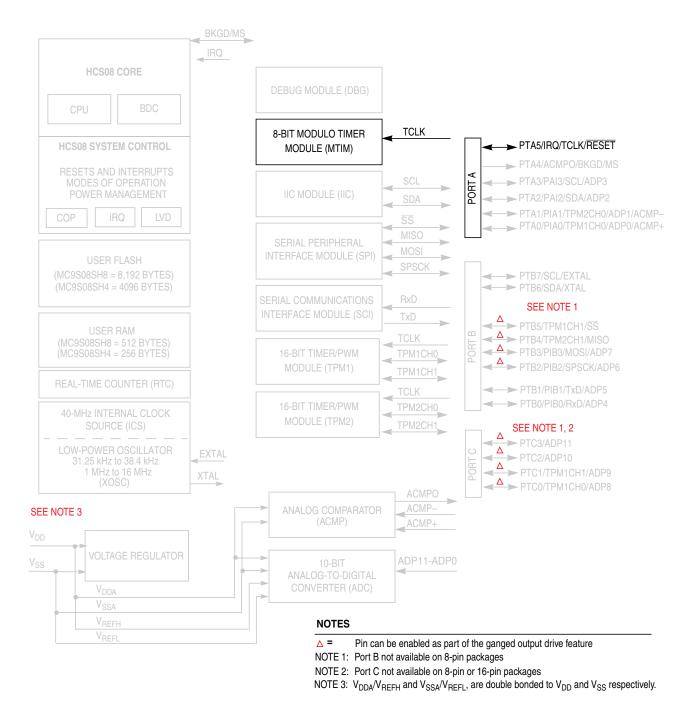

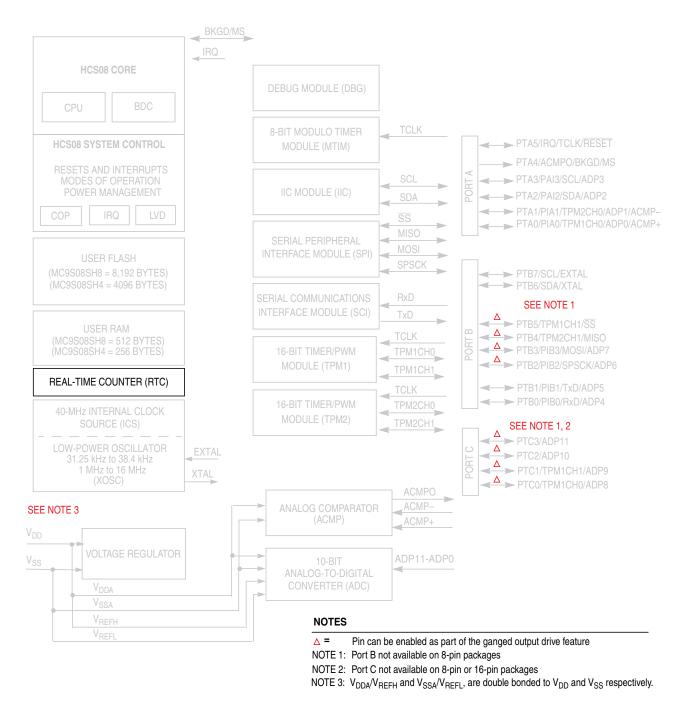

This section describes signals that connect to package pins. It includes pinout diagrams, recommended system connections, and detailed discussions of signals.

# 2.1 Device Pin Assignment

Figure 2-1 - Figure 2-4 shows the pin assignments for the MC9S08SH8 devices.

Figure 2-1. 24-Pin QFN

MC9S08SH8 MCU Series Data Sheet, Rev. 3

Chapter 2 Pins and Connections

Chapter 4 Memory

Table 4-2. Direct-Page Register Summary (Sheet 1 of 3)

| Address                            | Register<br>Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|------------------------------------|------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x00 <b>00</b>                     | PTAD             | 0      | 0      | PTAD5  | PTAD4  | PTAD3  | PTAD2  | PTAD1  | PTAD0  |

| 0x00 <b>01</b>                     | PTADD            | 0      | 0      | PTADD5 | PTADD4 | PTADD3 | PTADD2 | PTADD1 | PTADD0 |

| 0x00 <b>02</b>                     | PTBD             | PTBD7  | PTBD6  | PTBD5  | PTBD4  | PTBD3  | PTBD2  | PTBD1  | PTBD0  |

| 0x00 <b>03</b>                     | PTBDD            | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| 0x00 <b>04</b>                     | PTCD             | 0      | 0      | 0      | 0      | PTCD3  | PTCD2  | PTCD1  | PTCD0  |

| 0x00 <b>05</b>                     | PTCDD            | 0      | 0      | 0      | 0      | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| 0x00 <b>06</b> –<br>0x00 <b>0D</b> | Reserved         |        |        |        |        |        |        | _      | _      |

| 0x00 <b>0E</b>                     | ACMPSC           | ACME   | ACBGS  | ACF    | ACIE   | ACO    | ACOPE  | ACMOD1 | ACMOD0 |

| 0x00 <b>0F</b>                     | Reserved         |        | _      |        | _      |        |        | —      | —      |

| 0x00 <b>10</b>                     | ADSC1            | сосо   | AIEN   | ADCO   |        |        | ADCH   |        |        |

| 0x00 <b>11</b>                     | ADSC2            | ADACT  | ADTRG  | ACFE   | ACFGT  | _      | _      | —      | —      |

| 0x00 <b>12</b>                     | ADRH             | 0      | 0      | 0      | 0      | 0      | 0      | ADR9   | ADR8   |

| 0x00 <b>13</b>                     | ADRL             | ADR7   | ADR6   | ADR5   | ADR4   | ADR3   | ADR2   | ADR1   | ADR0   |

| 0x00 <b>14</b>                     | ADCVH            | 0      | 0      | 0      | 0      | 0      | 0      | ADCV9  | ADCV8  |

| 0x00 <b>15</b>                     | ADCVL            | ADCV7  | ADCV6  | ADCV5  | ADCV4  | ADCV3  | ADCV2  | ADCV1  | ADCV0  |

| 0x00 <b>16</b>                     | ADCFG            | ADLPC  | AD     | DIV    | ADLSMP | MC     | DE     | ADI    | CLK    |

| 0x00 <b>17</b>                     | APCTL1           | ADPC7  | ADPC6  | ADPC5  | ADPC4  | ADPC3  | ADPC2  | ADPC1  | ADPC0  |

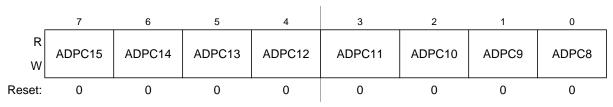

| 0x00 <b>18</b>                     | APCTL2           | 0      | 0      | 0      | 0      | ADPC11 | ADPC10 | ADPC9  | ADPC8  |

| 0x00 <b>19</b>                     | Reserved         | —      |        |        | _      | _      | —      | —      | —      |

| 0x00 <b>1A</b>                     | IRQSC            | 0      | IRQPDD | IRQEDG | IRQPE  | IRQF   | IRQACK | IRQIE  | IRQMOD |

| 0x00 <b>1B</b>                     | Reserved         | —      |        |        | _      | _      | —      | —      | —      |

| 0x00 <b>1C</b>                     | MTIMSC           | TOF    | TOIE   | TRST   | TSTP   | 0      | 0      | 0      | 0      |

| 0x00 <b>1D</b>                     | MTIMCLK          | 0      | 0      | CL     | KS     |        | Р      | Ś      |        |

| 0x00 <b>1E</b>                     | MTIMCNT          |        |        |        | CI     | NT     |        |        |        |

| 0x00 <b>1F</b>                     | MTIMMOD          |        |        |        | МС     | DD     |        |        |        |

| 0x00 <b>20</b>                     | TPM1SC           | TOF    | TOIE   | CPWMS  | CLKSB  | CLKSA  | PS2    | PS1    | PS0    |

| 0x00 <b>21</b>                     | TPM1CNTH         | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>22</b>                     | TPM1CNTL         | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>23</b>                     | TPM1MODH         | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>24</b>                     | TPM1MODL         | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>25</b>                     | TPM1C0SC         | CH0F   | CH0IE  | MS0B   | MS0A   | ELS0B  | ELS0A  | 0      | 0      |

| 0x00 <b>26</b>                     | TPM1C0VH         | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>27</b>                     | TPM1C0VL         | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>28</b>                     | TPM1C1SC         | CH1F   | CH1IE  | MS1B   | MS1A   | ELS1B  | ELS1A  | 0      | 0      |

| 0x00 <b>29</b>                     | TPM1C1VH         | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>2A</b>                     | TPM1C1VL         | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>2B</b> –<br>0x00 <b>37</b> | Reserved         |        | _      | _      | _      |        |        | _      |        |

Chapter 5 Resets, Interrupts, and General System Control

**Chapter 6 Parallel Input/Output Control**

# 6.4 Pin Interrupts

Port A[3:0] and port B[3:0] pins can be configured as external interrupt inputs and as an external means of waking the MCU from stop3 or wait low-power modes.

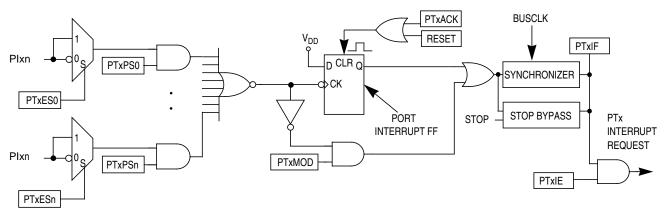

The block diagram for the pin interrupts is shown Figure 6-2.

Figure 6-2. Pin Interrupt Block Diagram

Writing to the PTxPSn bits in the port interrupt pin enable register (PTxPS) independently enables or disables each port pin interrupt. Each port can be configured as edge sensitive or edge and level sensitive based on the PTxMOD bit in the port interrupt status and control register (PTxSC). Edge sensitivity can be software programmed to be either falling or rising; the level can be either low or high. The polarity of the edge or edge and level sensitivity is selected using the PTxESn bits in the port interrupt edge select register (PTxES).

Synchronous logic is used to detect edges. Prior to detecting an edge, enabled pin interrupt inputs must be at the deasserted logic level. A falling edge is detected when an enabled port input signal is seen as a logic 1 (the deasserted level) during one bus cycle and then a logic 0 (the asserted level) during the next cycle. A rising edge is detected when the input signal is seen as a logic 0 during one bus cycle and then a logic 1 during the next cycle.

## 6.4.1 Edge Only Sensitivity

A valid edge on an enabled pin interrupt will set PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request will be presented to the CPU. Clearing of PTxIF is accomplished by writing a 1 to PTxACK in PTxSC.

## 6.4.2 Edge and Level Sensitivity

A valid edge or level on an enabled pin interrupt will set PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request will be presented to the CPU. Clearing of PTxIF is accomplished by writing a 1 to PTxACK in PTxSC provided all enabled pin interrupt inputs are at their deasserted levels. PTxIF will remain set if any enabled pin interrupt is asserted while attempting to clear by writing a 1 to PTxACK.

Chapter 6 Parallel Input/Output Control

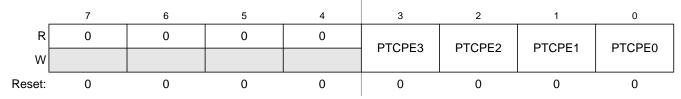

# 6.6.3.3 Port C Pull Enable Register (PTCPE)

Figure 6-21. Internal Pull Enable for Port C Register (PTCPE)

#### Table 6-20. PTCPE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTCPE[3:0] | <ul> <li>Internal Pull Enable for Port C Bits — Each of these control bits determines if the internal pull-up device is enabled for the associated PTC pin. For port C pins that are configured as outputs, these bits have no effect and the internal pull devices are disabled.</li> <li>0 Internal pull-up device disabled for port C bit n.</li> <li>1 Internal pull-up device enabled for port C bit n.</li> </ul> |

## 6.6.3.4 Port C Slew Rate Enable Register (PTCSE)

|        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|---|---|--------|--------|--------|--------|

| R      | 0 | 0 | 0 | 0 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| W      |   |   |   |   | FICSES | FICSEZ | FICSEI | FICSED |

| Reset: | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      |

Figure 6-22. Slew Rate Enable for Port C Register (PTCSE)

#### Table 6-21. PTCSE Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Output Slew Rate Enable for Port C Bits — Each of these control bits determines if the output slew rate control is enabled for the associated PTC pin. For port C pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port C bit n.</li> <li>Output slew rate control enabled for port C bit n.</li> </ul> |

#### Chapter 7 Central Processor Unit (S08CPUV2)

interrupt service routine, this would allow nesting of interrupts (which is not recommended because it leads to programs that are difficult to debug and maintain).

For compatibility with the earlier M68HC05 MCUs, the high-order half of the H:X index register pair (H) is not saved on the stack as part of the interrupt sequence. The user must use a PSHH instruction at the beginning of the service routine to save H and then use a PULH instruction just before the RTI that ends the interrupt service routine. It is not necessary to save H if you are certain that the interrupt service routine does not use any instructions or auto-increment addressing modes that might change the value of H.

The software interrupt (SWI) instruction is like a hardware interrupt except that it is not masked by the global I bit in the CCR and it is associated with an instruction opcode within the program so it is not asynchronous to program execution.

## 7.4.3 Wait Mode Operation

The WAIT instruction enables interrupts by clearing the I bit in the CCR. It then halts the clocks to the CPU to reduce overall power consumption while the CPU is waiting for the interrupt or reset event that will wake the CPU from wait mode. When an interrupt or reset event occurs, the CPU clocks will resume and the interrupt or reset event will be processed normally.

If a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in wait mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in wait mode.

## 7.4.4 Stop Mode Operation

Usually, all system clocks, including the crystal oscillator (when used), are halted during stop mode to minimize power consumption. In such systems, external circuitry is needed to control the time spent in stop mode and to issue a signal to wake up the target MCU when it is time to resume processing. Unlike the earlier M68HC05 and M68HC08 MCUs, the HCS08 can be configured to keep a minimum set of clocks running in stop mode. This optionally allows an internal periodic signal to wake the target MCU from stop mode.

When a host debug system is connected to the background debug pin (BKGD) and the ENBDM control bit has been set by a serial command through the background interface (or because the MCU was reset into active background mode), the oscillator is forced to remain active when the MCU enters stop mode. In this case, if a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in stop mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in stop mode.

Recovery from stop mode depends on the particular HCS08 and whether the oscillator was stopped in stop mode. Refer to the Modes of Operation chapter for more details.

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                   | Aff<br>on (           | ect<br>CCR |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------|-----------------------|------------|

| Form                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ρd                                                  |                                                                                  | S                               |                                                         | <b>V</b> 1 1 <b>H</b> | INZC       |

| MOV opr8a,opr8a<br>MOV opr8a,X+<br>MOV #opr8i,opr8a<br>MOV ,X+,opr8a                                            | $\begin{array}{l} \mbox{Move} \\ (M)_{destination} \leftarrow (M)_{source} \\ \mbox{In IX+/DIR and DIR/IX+ Modes,} \\ \mbox{H:X} \leftarrow (H:X) + \$0001 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DIR/DIR<br>DIR/IX+<br>IMM/DIR<br>IX+/DIR            | 4E dd dd<br>5E dd<br>6E ii dd<br>7E dd                                           | 5<br>5<br>4<br>5                | rpwpp<br>rfwpp<br>pwpp<br>rfwpp                         | 011-                  | - \$ \$ -  |

| MUL                                                                                                             | Unsigned multiply $X:A \leftarrow (X) \times (A)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INH                                                 | 42                                                                               | 5                               | ffffp                                                   | - 1 1 0               | 0          |

| NEG opr8a<br>NEGA<br>NEGX<br>NEG oprx8,X<br>NEG ,X<br>NEG oprx8,SP                                              | $\begin{array}{lll} \mbox{Negate} & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ (\mbox{Two's Complement}) & \mbox{A} \leftarrow - (\mbox{A}) = \$00 - (\mbox{A}) \\ & \mbox{X} \leftarrow - (\mbox{A}) = \$00 - (\mbox{X}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$00 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) \\ & \mbox{M} \leftarrow - (\mbox{M}) = \$0 - (\mbox{M}) $ | IX                                                  | 30 dd<br>40<br>50<br>60 ff<br>70<br>9E 60 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp              | ↓ 1 1 -               | - ↓ ↓ ↓    |

| NOP                                                                                                             | No Operation — Uses 1 Bus Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | INH                                                 | 9D                                                                               | 1                               | q                                                       | - 1 1 -               |            |

| NSA                                                                                                             | Nibble Swap Accumulator $A \leftarrow (A[3:0]:A[7:4])$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INH                                                 | 62                                                                               | 1                               | q                                                       | - 1 1 -               |            |

| ORA #opr8i<br>ORA opr8a<br>ORA opr16a<br>ORA oprx16,X<br>ORA oprx8,X<br>ORA ,X<br>ORA oprx16,SP<br>ORA oprx8,SP | Inclusive OR Accumulator and Memory $A \leftarrow (A) \mid (M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AA ii<br>BA dd<br>CA hh 11<br>DA ee ff<br>EA ff<br>FA<br>9E DA ee ff<br>9E EA ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>prpp<br>prpp | 011-                  | - ‡ ‡ -    |

| PSHA                                                                                                            | Push Accumulator onto Stack<br>Push (A); SP $\leftarrow$ (SP) – \$0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INH                                                 | 87                                                                               | 2                               | sp                                                      | - 1 1 -               |            |

| PSHH                                                                                                            | Push H (Index Register High) onto Stack<br>Push (H); SP $\leftarrow$ (SP) – \$0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | INH                                                 | 8B                                                                               | 2                               | sp                                                      | - 1 1 -               |            |

| PSHX                                                                                                            | Push X (Index Register Low) onto Stack Push (X); SP $\leftarrow$ (SP) – \$0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | INH                                                 | 89                                                                               | 2                               | sp                                                      | - 1 1 -               |            |

| PULA                                                                                                            | Pull Accumulator from Stack SP $\leftarrow$ (SP + \$0001); Pull (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INH                                                 | 86                                                                               | 3                               | ufp                                                     | - 1 1 -               |            |

| PULH                                                                                                            | Pull H (Index Register High) from Stack $SP \leftarrow (SP + \$0001)$ ; Pull (H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 8A                                                                               | 3                               | ufp                                                     | - 1 1 -               |            |

| PULX                                                                                                            | Pull X (Index Register Low) from Stack $SP \leftarrow (SP + \$0001)$ ; Pull (X)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | INH                                                 | 88                                                                               | 3                               | ufp                                                     | - 1 1 -               |            |

| ROL <i>opr8a</i><br>ROLA<br>ROLX<br>ROL <i>oprx8</i> ,X<br>ROL ,X<br>ROL <i>oprx8</i> ,SP                       | Rotate Left through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39 dd<br>49<br>59<br>69 ff<br>79<br>9E 69 ff                                     | 5<br>1<br>5<br>4<br>6           | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp                   | ↓11-                  | - \$ \$ \$ |

| ROR opr8a<br>RORA<br>RORX<br>ROR oprx8,X<br>ROR ,X<br>ROR oprx8,SP                                              | Rotate Right through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36 dd<br>46<br>56<br>66 ff<br>76<br>9E 66 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwp                    | ↓11-                  | - ‡ ‡ ‡    |

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                          | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                            | Affect<br>on CCR      |                                                |  |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|-----------------------|------------------------------------------------|--|

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                    | PΦ<br>Φ                                             |                                                                                  | δ                               | Details                                          | <b>V</b> 1 1 <b>H</b> | INZC                                           |  |

| SUB #opr8i<br>SUB opr8a<br>SUB opr16a<br>SUB oprx16,X<br>SUB oprx8,X<br>SUB ,X<br>SUB oprx16,SP<br>SUB oprx8,SP | Subtract<br>A $\leftarrow$ (A) – (M)                                                                                                                                                                                                                                                                                                                                                               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A0 ii<br>B0 dd<br>C0 hh ll<br>D0 ee ff<br>E0 ff<br>F0<br>9E D0 ee ff<br>9E E0 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | ↓11-                  | - ↓ ↓ ↓                                        |  |

| SWI                                                                                                             | Software Interrupt<br>PC $\leftarrow$ (PC) + \$0001<br>Push (PCL); SP $\leftarrow$ (SP) - \$0001<br>Push (PCH); SP $\leftarrow$ (SP) - \$0001<br>Push (X); SP $\leftarrow$ (SP) - \$0001<br>Push (A); SP $\leftarrow$ (SP) - \$0001<br>Push (CCR); SP $\leftarrow$ (SP) - \$0001<br>I $\leftarrow$ 1;<br>PCH $\leftarrow$ Interrupt Vector High Byte<br>PCL $\leftarrow$ Interrupt Vector Low Byte | INH                                                 | 83                                                                               | 11                              | sssssvvfppp                                      | - 1 1 -               | 1 – – –                                        |  |

| ТАР                                                                                                             | Transfer Accumulator to CCR CCR $\leftarrow$ (A)                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 84                                                                               | 1                               | р                                                | \$ 1 1 \$             | $\uparrow \uparrow \uparrow \uparrow \uparrow$ |  |

| ТАХ                                                                                                             | Transfer Accumulator to X (Index Register Low) $X \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                  | INH                                                 | 97                                                                               | 1                               | p                                                | - 1 1 -               |                                                |  |

| ТРА                                                                                                             | Transfer CCR to Accumulator $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 85                                                                               | 1                               | q                                                | - 1 1 -               |                                                |  |

| TST opr8a<br>TSTA<br>TSTX<br>TST oprx8,X<br>TST ,X<br>TST oprx8,SP                                              | Test for Negative or Zero (M) - \$00<br>(A) - \$00<br>(X) - \$00<br>(M) - \$00<br>(M) - \$00<br>(M) - \$00                                                                                                                                                                                                                                                                                         | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3D dd<br>4D<br>5D<br>6D ff<br>7D<br>9E 6D ff                                     | 4<br>1<br>4<br>3<br>5           | rfpp<br>p<br>rfpp<br>rfp<br>prfpp                | 011-                  | - \$ \$ -                                      |  |

| TSX                                                                                                             | Transfer SP to Index Reg.<br>H:X $\leftarrow$ (SP) + \$0001                                                                                                                                                                                                                                                                                                                                        | INH                                                 | 95                                                                               | 2                               | fp                                               | - 1 1 -               |                                                |  |

| ТХА                                                                                                             | Transfer X (Index Reg. Low) to Accumulator $A \leftarrow (X)$                                                                                                                                                                                                                                                                                                                                      | INH                                                 | 9F                                                                               | 1                               | q                                                | - 1 1 -               |                                                |  |

#### Table 7-2. Instruction Set Summary (Sheet 8 of 9)