#### NXP USA Inc. - <u>MC9S08SH8MTG Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | S08                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 40MHz                                                                |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 13                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 512 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 8x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                      |

| Supplier Device Package    | 16-TSSOP                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh8mtg |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

| Part Number   | Package Description | Original (gold wire)<br>package document number | Current (copper wire)<br>package document number |

|---------------|---------------------|-------------------------------------------------|--------------------------------------------------|

| MC68HC908JW32 | 48 QFN              | 98ARH99048A                                     | 98ASA00466D                                      |

| MC9S08AC16    |                     |                                                 |                                                  |

| MC9S908AC60   |                     |                                                 |                                                  |

| MC9S08AC128   |                     |                                                 |                                                  |

| MC9S08AW60    |                     |                                                 |                                                  |

| MC9S08GB60A   |                     |                                                 |                                                  |

| MC9S08GT16A   |                     |                                                 |                                                  |

| MC9S08JM16    |                     |                                                 |                                                  |

| MC9S08JM60    |                     |                                                 |                                                  |

| MC9S08LL16    |                     |                                                 |                                                  |

| MC9S08QE128   |                     |                                                 |                                                  |

| MC9S08QE32    |                     |                                                 |                                                  |

| MC9S08RG60    |                     |                                                 |                                                  |

| MCF51CN128    |                     |                                                 |                                                  |

| MC9RS08LA8    | 48 QFN              | 98ARL10606D                                     | 98ASA00466D                                      |

| MC9S08GT16A   | 32 QFN              | 98ARH99035A                                     | 98ASA00473D                                      |

| MC9S908QE32   | 32 QFN              | 98ARE10566D                                     | 98ASA00473D                                      |

| MC9S908QE8    | 32 QFN              | 98ASA00071D                                     | 98ASA00736D                                      |

| MC9S08JS16    | 24 QFN              | 98ARL10608D                                     | 98ASA00734D                                      |

| MC9S08QB8     |                     |                                                 |                                                  |

| MC9S08QG8     | 24 QFN              | 98ARL10605D                                     | 98ASA00474D                                      |

| MC9S08SH8     | 24 QFN              | 98ARE10714D                                     | 98ASA00474D                                      |

| MC9RS08KB12   | 24 QFN              | 98ASA00087D                                     | 98ASA00602D                                      |

| MC9S08QG8     | 16 QFN              | 98ARE10614D                                     | 98ASA00671D                                      |

| MC9RS08KB12   | 8 DFN               | 98ARL10557D                                     | 98ASA00672D                                      |

| MC9S08QG8     |                     |                                                 |                                                  |

| MC9RS08KA2    | 6 DFN               | 98ARL10602D                                     | 98ASA00735D                                      |

Chapter 1 Device Overview

# 1.3 System Clock Distribution

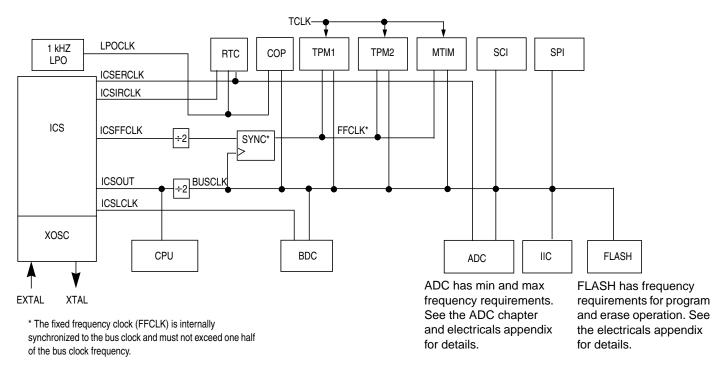

Figure 1-2 shows a simplified clock connection diagram. Some modules in the MCU have selectable clock inputs as shown. The clock inputs to the modules indicate the clock(s) that are used to drive the module function.

The following defines the clocks used in this MCU:

- BUSCLK The frequency of the bus is always half of ICSOUT.

- ICSOUT Primary output of the ICS and is twice the bus frequency.

- ICSLCLK Development tools can select this clock source to speed up BDC communications in systems where the bus clock is configured to run at a very slow frequency.

- ICSERCLK External reference clock can be selected as the RTC clock source and as the alternate clock for the ADC module.

- ICSIRCLK Internal reference clock can be selected as the RTC clock source.

- ICSFFCLK Fixed frequency clock can be selected as clock source for the TPM1, TPM2 and MTIM modules.

- LPOCLK Independent 1-kHz clock source that can be selected as the clock source for the COP and RTC modules.

- TCLK External input clock source for TPM1, TPM2 and MTIM and is referenced as TPMCLK in TPM chapters.

Figure 1-2. System Clock Distribution Diagram

MC9S08SH8 MCU Series Data Sheet, Rev. 3

Chapter 4 Memory

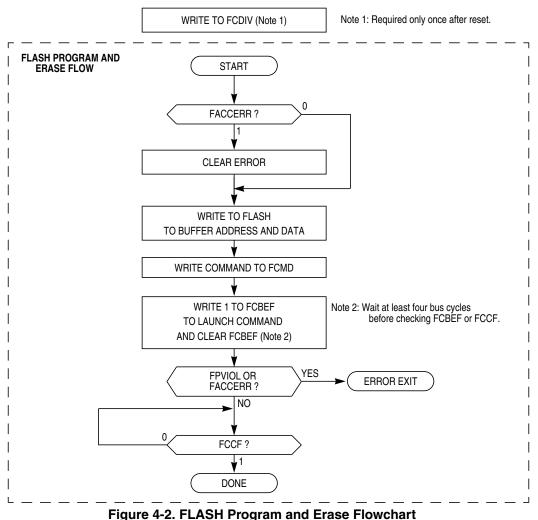

#### rigure +-2. I EASIT Program and Erase Prowe

#### 4.5.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst program command is issued, the charge pump is enabled and then remains enabled after completion of the burst program operation if these two conditions are met:

- The next burst program command has been queued before the current program operation has completed.

- The next sequential address selects a byte on the same physical row as the current byte being programmed. A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero.

| Table 4-12. FSTAT Register Field D | Descriptions (continued) |

|------------------------------------|--------------------------|

|------------------------------------|--------------------------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>FACCERR | Access Error Flag — FACCERR is set automatically when the proper command sequence is not obeyed exactly (the erroneous command is ignored), if a program or erase operation is attempted before the FCDIV register has been initialized, or if the MCU enters stop while a command was in progress. For a more detailed discussion of the exact actions that are considered access errors, see Section 4.5.5, "Access Errors." FACCERR is cleared by writing a 1 to FACCERR. Writing a 0 to FACCERR has no meaning or effect.<br>0 No access error.<br>1 An access error has occurred. |

| 2<br>FBLANK  | <ul> <li>FLASH Verifie as All Blank (erased) Flag — FBLANK is set automatically at the conclusion of a blank check command if the entire FLASH array was verified to be erased. FBLANK is cleared by clearing FCBEF to write a new valid command. Writing to FBLANK has no meaning or effect.</li> <li>0 After a blank check command is completed and FCCF = 1, FBLANK = 0 indicates the FLASH array is not completely erased.</li> <li>1 After a blank check command is completed and FCCF = 1, FBLANK = 1 indicates the FLASH array is completely erased (all 0xFF).</li> </ul>      |

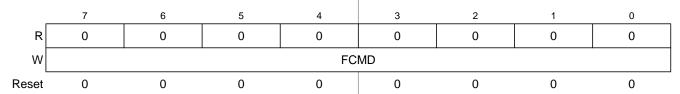

## 4.7.6 FLASH Command Register (FCMD)

Only five command codes are recognized in normal user modes as shown in Table 4-13. Refer to Section 4.5.3, "Program and Erase Command Execution," for a detailed discussion of FLASH programming and erase operations.

Figure 4-10. FLASH Command Register (FCMD)

| Command                     | FCMD | Equate File Label |

|-----------------------------|------|-------------------|

| Blank check                 | 0x05 | mBlank            |

| Byte program                | 0x20 | mByteProg         |

| Byte program — burst mode   | 0x25 | mBurstProg        |

| Page erase (512 bytes/page) | 0x40 | mPageErase        |

| Mass erase (all FLASH)      | 0x41 | mMassErase        |

Table 4-13. FLASH Commands

All other command codes are illegal and generate an access error.

It is not necessary to perform a blank check command after a mass erase operation. Only blank check is required as part of the security unlocking mechanism.

#### 5.7.4 System Options Register 1 (SOPT1)

This high page register is a write-once register so only the first write after reset is honored. It can be read at any time. Any subsequent attempt to write to SOPT1 (intentionally or unintentionally) is ignored to avoid accidental changes to these sensitive settings. SOPT1 should be written during the user's reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

|        | 7                             | 6    | 5     | 4 <sup>1</sup> | 3 | 2     | 1      | 0              |

|--------|-------------------------------|------|-------|----------------|---|-------|--------|----------------|

| R<br>W |                               | СОРТ | STOPE |                | 0 | IICPS | BKGDPE | RSTPE          |

| Reset: | 1                             | 1    | 0     | 0              | 0 | 0     | 1      | u <sup>2</sup> |

| POR:   | 1                             | 1    | 0     | 0              | 0 | 0     | 1      | 0              |

| LVR:   | 1                             | 1    | 0     | 0              | 0 | 0     | 1      | u              |

| [      | = I Inimplemented or Reserved |      |       |                |   |       |        |                |

= Unimplemented or Reserved

Figure 5-5. System Options Register 1 (SOPT1)

<sup>1</sup> Bit 4 is reserved, writes change the value, but will have no effect on this MCU.

<sup>2</sup> u = unaffected

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>COPT[1:0] | <b>COP Watchdog Timeout</b> — These write-once bits select the timeout period of the COP. COPT along with COPCLKS in SOPT2 defines the COP timeout period. See Table 5-1.                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>STOPE       | <ul> <li>Stop Mode Enable — This write-once bit is used to enable stop mode. If stop mode is disabled and a user program attempts to execute a STOP instruction, an illegal opcode reset is forced.</li> <li>0 Stop mode disabled.</li> <li>1 Stop mode enabled.</li> </ul>                                                                                                                                                                                                                                                                                       |

| 2<br>IICPS       | <ul> <li>IIC Pin Select — This bit selects the location of the SDA and SCL pins of the IIC module.</li> <li>0 SDA on PTA2, SCL on PTA3.</li> <li>1 SDA on PTB6, SCL on PTB7.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                           |

| 1<br>BKGDPE      | <ul> <li>Background Debug Mode Pin Enable — This write-once bit when set enables the PTA4/ACMPO/BKGD/MS pin to function as BKGD/MS. When clear, the pin functions as one of its output-only alternative functions. This pin defaults to the BKGD/MS function following any MCU reset.</li> <li>0 PTA4/ACMPO/BKGD/MS pin functions as PTA4 or ACMPO.</li> <li>1 PTA4/ACMPO/BKGD/MS pin functions as BKGD/MS.</li> </ul>                                                                                                                                            |

| 0<br>RSTPE       | <b>RESET Pin Enable</b> — This write-once bit when set enables the PTA5/IRQ/TCLK/RESET pin to function as RESET. When clear, the pin functions as one of its alternative functions. This pin defaults to a general-purpose input port function following a POR reset. When configured as RESET, the pin will be unaffected by LVR or other internal resets. When RSTPE is set, an internal pullup device is enabled on RESET.         0       PTA5/IRQ/TCLK/RESET pin functions as PTA5, IRQ or TCLK.         1       PTA5/IRQ/TCLK/RESET pin functions as RESET. |

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                                    | Address<br>Mode<br>Opje                             | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                   | Affect<br>on CCR      |                                            |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------|-----------------------|--------------------------------------------|

| Form                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                              | PdA                                                 |                                                                                  | с<br>С                          |                                                         | <b>V</b> 1 1 <b>H</b> | INZC                                       |

| CMP #opr8i<br>CMP opr8a<br>CMP opr16a<br>CMP oprx16,X<br>CMP oprx8,X<br>CMP ,X<br>CMP oprx16,SP<br>CMP oprx8,SP | Compare Accumulator with Memory<br>A – M<br>(CCR Updated But Operands Not Changed)                                                                                                                                                                                                                                                                                                                           | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | Al ii<br>Bl dd<br>Cl hh ll<br>Dl ee ff<br>El ff<br>Fl<br>9E Dl ee ff<br>9E El ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>prpp<br>prpp<br>prpp | \$11−                 | - \$ \$ \$                                 |

| COM opr8a<br>COMA<br>COMX<br>COM oprx8,X<br>COM ,X<br>COM oprx8,SP                                              | $\begin{array}{ll} \mbox{Complement} & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \\ \mbox{(One's Complement)} & \mbox{A} \leftarrow (\overline{A}) = \$ FF - (A) \\ & \mbox{X} \leftarrow (\overline{X}) = \$ FF - (X) \\ & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \\ & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \\ & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \end{array}$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33 dd<br>43<br>53<br>63 ff<br>73<br>9E 63 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwp                    | 011-                  | - ↓ ↓ 1                                    |

| CPHX opr16a<br>CPHX #opr16i<br>CPHX opr8a<br>CPHX oprx8,SP                                                      | Compare Index Register (H:X) with Memory<br>(H:X) – (M:M + \$0001)<br>(CCR Updated But Operands Not Changed)                                                                                                                                                                                                                                                                                                 | EXT<br>IMM<br>DIR<br>SP1                            | 3E hh ll<br>65 jj kk<br>75 dd<br>9E F3 ff                                        | 6<br>3<br>5<br>6                | prrfpp<br>ppp<br>rrfpp<br>prrfpp                        | ↓11-                  | $- \updownarrow \updownarrow \updownarrow$ |

| CPX #opr8i<br>CPX opr8a<br>CPX opr16a<br>CPX oprx16,X<br>CPX oprx8,X<br>CPX ,X<br>CPX oprx16,SP<br>CPX oprx8,SP | Compare X (Index Register Low) with<br>Memory<br>X – M<br>(CCR Updated But Operands Not Changed)                                                                                                                                                                                                                                                                                                             | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A3 ii<br>B3 dd<br>C3 hh 11<br>D3 ee ff<br>E3 ff<br>F3<br>9E D3 ee ff<br>9E E3 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rpp<br>rfp<br>pprpp<br>prpp | ↓11 –                 | - ↓ ↓ ↓                                    |

| DAA                                                                                                             | Decimal Adjust Accumulator<br>After ADD or ADC of BCD Values                                                                                                                                                                                                                                                                                                                                                 | INH                                                 | 72                                                                               | 1                               | P                                                       | U 1 1 –               | - 1 1 1                                    |

| DBNZ opr8a,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ oprx8,X,rel<br>DBNZ ,X,rel<br>DBNZ oprx8,SP,rel                | Decrement A, X, or M and Branch if Not Zero<br>(if (result) ≠ 0)<br>DBNZX Affects X Not H                                                                                                                                                                                                                                                                                                                    | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B dd rr<br>4B rr<br>5B rr<br>6B ff rr<br>7B rr<br>9E 6B ff rr                   | 7<br>4<br>4<br>7<br>6<br>8      | rfwpppp<br>fppp<br>fppp<br>rfwpppp<br>rfwppp<br>prfwppp | - 1 1 -               |                                            |

| DEC opr8a<br>DECA<br>DECX<br>DEC oprx8,X<br>DEC ,X<br>DEC oprx8,SP                                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                         | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A dd<br>4A<br>5A<br>6A ff<br>7A<br>9E 6A ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp              | ↓ 1 1 -               | - \$ \$ -                                  |

| DIV                                                                                                             | Divide $A \leftarrow (H:A)+(X); H \leftarrow Remainder$                                                                                                                                                                                                                                                                                                                                                      | INH                                                 | 52                                                                               | 6                               | ffffp                                                   | - 1 1 -               | ‡ ‡                                        |

| EOR #opr8i<br>EOR opr8a<br>EOR opr16a<br>EOR oprx16,X<br>EOR oprx8,X<br>EOR ,X<br>EOR oprx16,SP<br>EOR oprx8,SP | Exclusive OR Memory with Accumulator $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                             | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A8 ii<br>B8 dd<br>C8 hh ll<br>D8 ee ff<br>E8 ff<br>F8<br>9E D8 ee ff<br>9E E8 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>prpp<br>prpp         | 011-                  | - ‡ ‡ -                                    |

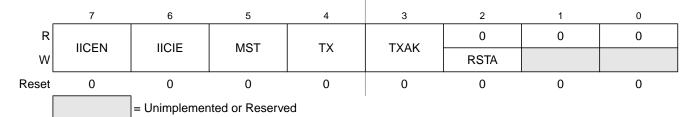

# 11.3.3 IIC Control Register (IICC1)

Figure 11-5. IIC Control Register (IICC1)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IICEN | IIC Enable. The IICEN bit determines whether the IIC module is enabled.         0 IIC is not enabled         1 IIC is enabled                                                                                                                                                                                                                                               |

| 6<br>IICIE | <ul> <li>IIC Interrupt Enable. The IICIE bit determines whether an IIC interrupt is requested.</li> <li>0 IIC interrupt request not enabled</li> <li>1 IIC interrupt request enabled</li> </ul>                                                                                                                                                                             |

| 5<br>MST   | <ul> <li>Master Mode Select. The MST bit changes from a 0 to a 1 when a start signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a stop signal is generated and the mode of operation changes from master to slave.</li> <li>0 Slave mode</li> <li>1 Master mode</li> </ul>                                                  |

| 4<br>TX    | Transmit Mode Select. The TX bit selects the direction of master and slave transfers. In master mode, this bit<br>should be set according to the type of transfer required. Therefore, for address cycles, this bit is always high.<br>When addressed as a slave, this bit should be set by software according to the SRW bit in the status register.0Receive<br>11Transmit |

| 3<br>TXAK  | <ul> <li>Transmit Acknowledge Enable. This bit specifies the value driven onto the SDA during data acknowledge cycles for master and slave receivers.</li> <li>0 An acknowledge signal is sent out to the bus after receiving one data byte</li> <li>1 No acknowledge signal response is sent</li> </ul>                                                                    |

| 2<br>RSTA  | <b>Repeat start.</b> Writing a 1 to this bit generates a repeated start condition provided it is the current master. This bit is always read as cleared. Attempting a repeat at the wrong time results in loss of arbitration.                                                                                                                                              |

## 12.3 Register Definitio

| Name     |   | 7     | 6    | 5    | 4    | 3  | 2 | 1 | 0 |  |

|----------|---|-------|------|------|------|----|---|---|---|--|

| MTIMSC   | R | TOF   | TOIE | 0    | TSTP | 0  | 0 | 0 | 0 |  |

| MTIMOC   | W |       |      | TRST |      |    |   |   |   |  |

| MTIMCLK  | R | 0     | 0    | CLKS |      | PS |   |   |   |  |

| WITHWOLK | W |       |      |      |      | 13 |   |   |   |  |

| MTIMCNT  | R | COUNT |      |      |      |    |   |   |   |  |

|          | W |       |      |      |      |    |   |   |   |  |

| MTIMMOD  | R | MOD   |      |      |      |    |   |   |   |  |

|          | W |       |      |      |      |    |   |   |   |  |

Figure 12-3 is a summary of MTIM registers.

Figure 12-3. MTIM Register Summary

Each MTIM includes four registers:

- An 8-bit status and control register

- An 8-bit clock configuration register

- An 8-bit counter register

- An 8-bit modulo register

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all MTIM registers. This section refers to registers and control bits only by their names and relative address offsets.

Some MCUs may have more than one MTIM, so register names include placeholder characters to identify which MTIM is being referenced.

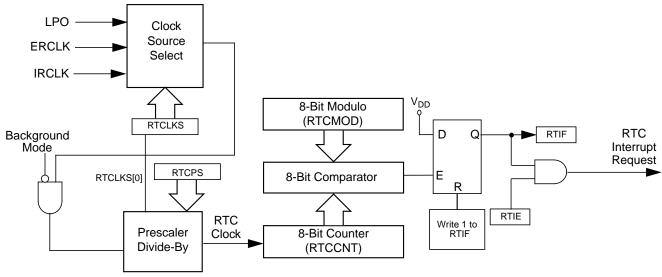

Chapter 13 Real-Time Counter (S08RTCV1)

### 13.1.3 Block Diagram

The block diagram for the RTC module is shown in Figure 13-2.

Figure 13-2. Real-Time Counter (RTC) Block Diagram

## 13.2 External Signal Description

The RTC does not include any off-chip signals.

## 13.3 Register Definitio

The RTC includes a status and control register, an 8-bit counter register, and an 8-bit modulo register.

Refer to the direct-page register summary in the memory section of this document for the absolute address assignments for all RTC registers. This section refers to registers and control bits only by their names and relative address offsets.

Table 13-1 is a summary of RTC registers.

| Name   | 7 | 6      | 5   | 4      | 3 | 2     | 1 | 0 |  |

|--------|---|--------|-----|--------|---|-------|---|---|--|

| RTCSC  | R | RTIF   | PTC | RTCLKS |   | RTCPS |   |   |  |

| KTCSC  | W | 1X111  |     |        |   |       |   |   |  |

| RTCCNT | R | RTCCNT |     |        |   |       |   |   |  |

|        | W |        |     |        |   |       |   |   |  |

| RTCMOD | R | RTCMOD |     |        |   |       |   |   |  |

| KTCMOD | W |        |     |        |   |       |   |   |  |

#### Chapter 13 Real-Time Counter (S08RTCV1)

```

#pragma TRAP_PROC

void RTC_ISR(void)

{

/* Clear the interrupt flag */

RTCSC.byte = RTCSC.byte | 0x80;

/* RTC interrupts every 1 Second */

Seconds++;

/* 60 seconds in a minute */

if (Seconds > 59){

Minutes++;

Seconds = 0;

}

/* 60 minutes in an hour */

if (Minutes > 59){

Hours++;

Minutes = 0;

}

/* 24 hours in a day */

if (Hours > 23){

Days ++;

Hours = 0;

}

}

```

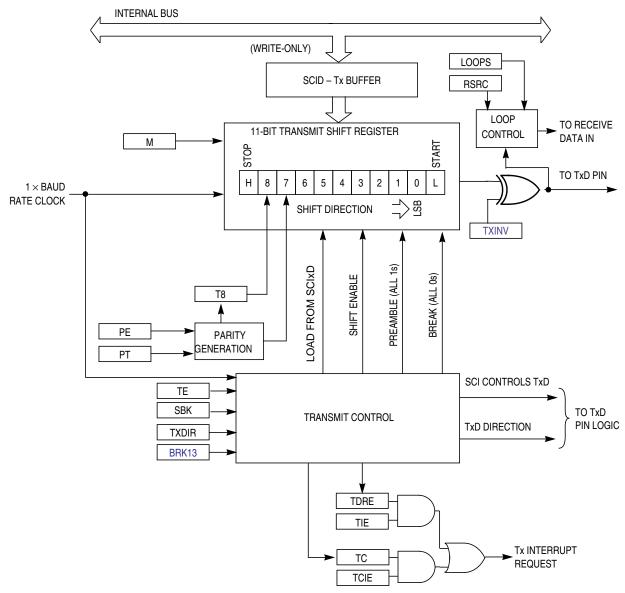

Chapter 14 Serial Communications Interface (S08SCIV4)

## 14.1.3 Block Diagram

Figure 14-2 shows the transmitter portion of the SCI.

Figure 14-2. SCI Transmitter Block Diagram

| Table 14-4. SCIxC2 Field Descrip | ptions (continued) |

|----------------------------------|--------------------|

|----------------------------------|--------------------|

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>TE  | Transmitter Enable         0       Transmitter off.         1       Transmitter on.         TE must be 1 in order to use the SCI transmitter. When TE = 1, the SCI forces the TxD pin to act as an output for the SCI system.         When the SCI is configured for single-wire operation (LOOPS = RSRC = 1), TXDIR controls the direction of traffic on the single SCI communication line (TxD pin).         TE also can be used to queue an idle character by writing TE = 0 then TE = 1 while a transmission is in progress.         Refer to Section 14.3.2.1, "Send Break and Queued Idle" for more details.         When TE is written to 0, the transmitter keeps control of the port TxD pin until any data, queued idle, or queued break character finishes transmitting before allowing the pin to revert to a general-purpose I/O pin. |

| 2<br>RE  | <ul> <li>Receiver Enable — When the SCI receiver is off, the RxD pin reverts to being a general-purpose port I/O pin.</li> <li>If LOOPS = 1 the RxD pin reverts to being a general-purpose I/O pin even if RE = 1.</li> <li>0 Receiver off.</li> <li>1 Receiver on.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1<br>RWU | <ul> <li>Receiver Wakeup Control — This bit can be written to 1 to place the SCI receiver in a standby state where it waits for automatic hardware detection of a selected wakeup condition. The wakeup condition is either an idle line between messages (WAKE = 0, idle-line wakeup), or a logic 1 in the most significant data bit in a character (WAKE = 1, address-mark wakeup). Application software sets RWU and (normally) a selected hardware condition automatically clears RWU. Refer to Section 14.3.3.2, "Receiver Wakeup Operation" for more details.</li> <li>0 Normal SCI receiver operation.</li> <li>1 SCI receiver in standby waiting for wakeup condition.</li> </ul>                                                                                                                                                          |

| 0<br>SBK | <ul> <li>Send Break — Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional break characters of 10 or 11 (13 or 14 if BRK13 = 1) bit times of logic 0 are queued as long as SBK = 1. Depending on the timing of the set and clear of SBK relative to the information currently being transmitted, a second break character may be queued before software clears SBK. Refer to Section 14.3.2.1, "Send Break and Queued Idle" for more details.</li> <li>0 Normal transmitter operation.</li> <li>1 Queue break character(s) to be sent.</li> </ul>                                                                                                                                                                                                                                                      |

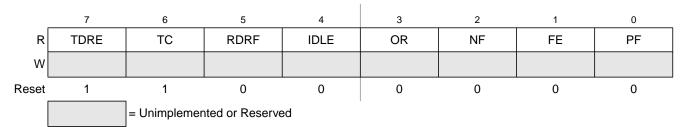

## 14.2.4 SCI Status Register 1 (SCIxS1)

This register has eight read-only status flags. Writes have no effect. Special software sequences (which do not involve writing to this register) are used to clear these status flags.

Figure 14-8. SCI Status Register 1 (SCIxS1)

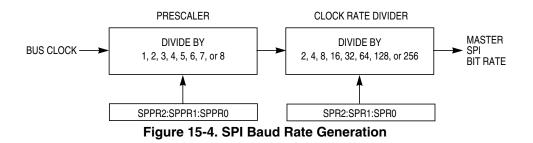

Chapter 15 Serial Peripheral Interface (S08SPIV3)

## 15.2 External Signal Description

The SPI optionally shares four port pins. The function of these pins depends on the settings of SPI control bits. When the SPI is disabled (SPE = 0), these four pins revert to being general-purpose port I/O pins that are not controlled by the SPI.

### 15.2.1 SPSCK — SPI Serial Clock

When the SPI is enabled as a slave, this pin is the serial clock input. When the SPI is enabled as a master, this pin is the serial clock output.

### 15.2.2 MOSI — Master Data Out, Slave Data In

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data output. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data input. If SPC0 = 1 to select single-wire bidirectional mode, and master mode is selected, this pin becomes the bidirectional data I/O pin (MOMI). Also, the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and slave mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

## 15.2.3 MISO — Master Data In, Slave Data Out

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data input. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data output. If SPC0 = 1 to select single-wire bidirectional mode, and slave mode is selected, this pin becomes the bidirectional data I/O pin (SISO) and the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and master mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

## 15.2.4 SS — Slave Select

When the SPI is enabled as a slave, this pin is the low-true slave select input. When the SPI is enabled as a master and mode fault enable is off (MODFEN = 0), this pin is not used by the SPI and reverts to being a general-purpose port I/O pin. When the SPI is enabled as a master and MODFEN = 1, the slave select output enable bit determines whether this pin acts as the mode fault input (SSOE = 0) or as the slave select output (SSOE = 1).

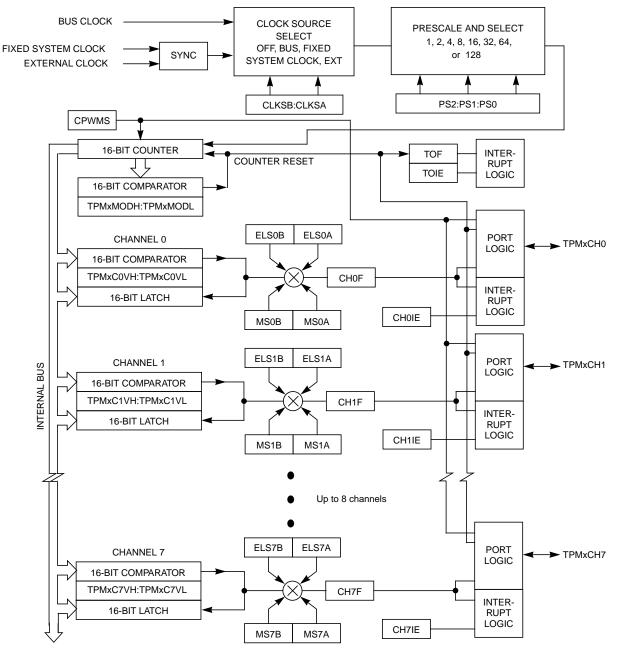

Chapter 16 Timer/PWM Module (S08TPMV3)

Figure 16-2. TPM Block Diagram

#### 16.4.2.1 Input Capture Mode

With the input-capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input-capture channel, the TPM latches the contents of the TPM counter into the channel-value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

In input capture mode, the TPMxCnVH and TPMxCnVL registers are read only.

When either half of the 16-bit capture register is read, the other half is latched into a buffer to support coherent 16-bit accesses in big-endian or little-endian order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An input capture event sets a flag bit (CHnF) which may optionally generate a CPU interrupt request.

While in BDM, the input capture function works as configured by the user. When an external event occurs, the TPM latches the contents of the TPM counter (which is frozen because of the BDM mode) into the channel value registers and sets the flag bit.

#### 16.4.2.2 Output Compare Mode

With the output-compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel-value registers of an output-compare channel, the TPM can set, clear, or toggle the channel pin.

In output compare mode, values are transferred to the corresponding timer channel registers only after both 8-bit halves of a 16-bit register have been written and according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), the registers are updated at the next change of the TPM counter (end of the prescaler counting) after the second byte is written.

The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An output compare event sets a flag bit (CHnF) which may optionally generate a CPU-interrupt request.

#### 16.4.2.3 Edge-Aligned PWM Mode

This type of PWM output uses the normal up-counting mode of the timer counter (CPWMS=0) and can be used when other channels in the same TPM are configured for input capture or output compare functions. The period of this PWM signal is determined by the value of the modulus register (TPMxMODH:TPMxMODL) plus 1. The duty cycle is determined by the setting in the timer channel register (TPMxCnVH:TPMxCnVL). The polarity of this PWM signal is determined by the setting in the ELSnA control bit. 0% and 100% duty cycle cases are possible.

The output compare value in the TPM channel registers determines the pulse width (duty cycle) of the PWM signal (Figure 16-15). The time between the modulus overflow and the output compare is the pulse width. If ELSnA=0, the counter overflow forces the PWM signal high, and the output compare forces the PWM signal low. If ELSnA=1, the counter overflow forces the PWM signal low, and the output compare forces the PWM signal high.

**Chapter 17 Development Support**

#### 17.1.2 Features

Features of the BDC module include:

- Single pin for mode selection and background communications

- BDC registers are not located in the memory map

- SYNC command to determine target communications rate

- Non-intrusive commands for memory access

- Active background mode commands for CPU register access

- GO and TRACE1 commands

- BACKGROUND command can wake CPU from stop or wait modes

- One hardware address breakpoint built into BDC

- Oscillator runs in stop mode, if BDC enabled

- COP watchdog disabled while in active background mode

Features of the ICE system include:

- Two trigger comparators: Two address + read/write (R/W) or one full address + data + R/W

- Flexible 8-word by 16-bit FIFO (first-in, first-out) buffer for capture information:

- Change-of-flow addresses or

- Event-only data

- Two types of breakpoints:

- Tag breakpoints for instruction opcodes

- Force breakpoints for any address access

- Nine trigger modes:

- Basic: A-only, A OR B

- Sequence: A then B

- Full: A AND B data, A AND NOT B data

- Event (store data): Event-only B, A then event-only B

- Range: Inside range (A  $\leq$  address  $\leq$  B), outside range (address < A or address > B)

# 17.2 Background Debug Controller (BDC)

All MCUs in the HCS08 Family contain a single-wire background debug interface that supports in-circuit programming of on-chip nonvolatile memory and sophisticated non-intrusive debug capabilities. Unlike debug interfaces on earlier 8-bit MCUs, this system does not interfere with normal application resources. It does not use any user memory or locations in the memory map and does not share any on-chip peripherals.

BDC commands are divided into two groups:

• Active background mode commands require that the target MCU is in active background mode (the user program is not running). Active background mode commands allow the CPU registers to be read or written, and allow the user to trace one user instruction at a time, or GO to the user program from active background mode.

#### **Chapter 17 Development Support**

When no debugger pod is connected to the 6-pin BDM interface connector, the internal pullup on BKGD chooses normal operating mode. When a debug pod is connected to BKGD it is possible to force the MCU into active background mode after reset. The specific conditions for forcing active background depend upon the HCS08 derivative (refer to the introduction to this Development Support section). It is not necessary to reset the target MCU to communicate with it through the background debug interface.

#### 17.2.2 Communication Details

The BDC serial interface requires the external controller to generate a falling edge on the BKGD pin to indicate the start of each bit time. The external controller provides this falling edge whether data is transmitted or received.

BKGD is a pseudo-open-drain pin that can be driven either by an external controller or by the MCU. Data is transferred MSB first at 16 BDC clock cycles per bit (nominal speed). The interface times out if 512 BDC clock cycles occur between falling edges from the host. Any BDC command that was in progress when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.

Chapter 17 Development Support

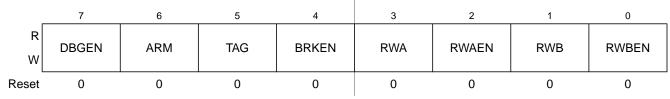

### 17.4.3.7 Debug Control Register (DBGC)

This register can be read or written at any time.

Figure 17-7. Debug Control Register (DBGC)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DBGEN | <b>Debug Module Enable</b> — Used to enable the debug module. DBGEN cannot be set to 1 if the MCU is secure.<br>0 DBG disabled<br>1 DBG enabled                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6<br>ARM   | <ul> <li>Arm Control — Controls whether the debugger is comparing and storing information in the FIFO. A write is used to set this bit (and ARMF) and completion of a debug run automatically clears it. Any debug run can be manually stopped by writing 0 to ARM or to DBGEN.</li> <li>0 Debugger not armed</li> <li>1 Debugger armed</li> </ul>                                                                                                                                                                                                                                       |

| 5<br>TAG   | Tag/Force Select — Controls whether break requests to the CPU will be tag or force type requests. If         BRKEN = 0, this bit has no meaning or effect.         0 CPU breaks requested as force type requests         1 CPU breaks requested as tag type requests                                                                                                                                                                                                                                                                                                                     |

| 4<br>BRKEN | <ul> <li>Break Enable — Controls whether a trigger event will generate a break request to the CPU. Trigger events can cause information to be stored in the FIFO without generating a break request to the CPU. For an end trace, CPU break requests are issued to the CPU when the comparator(s) and R/W meet the trigger requirements. For a begin trace, CPU break requests are issued when the FIFO becomes full. TRGSEL does not affect the timing of CPU break requests.</li> <li>0 CPU break requests not enabled</li> <li>1 Triggers cause a break request to the CPU</li> </ul> |

| 3<br>RWA   | <ul> <li>R/W Comparison Value for Comparator A — When RWAEN = 1, this bit determines whether a read or a write access qualifies comparator A. When RWAEN = 0, RWA and the R/W signal do not affect comparator A.</li> <li>0 Comparator A can only match on a write cycle</li> <li>1 Comparator A can only match on a read cycle</li> </ul>                                                                                                                                                                                                                                               |

| 2<br>RWAEN | <ul> <li>Enable R/W for Comparator A — Controls whether the level of R/W is considered for a comparator A match.</li> <li>0 R/W is not used in comparison A</li> <li>1 R/W is used in comparison A</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

| 1<br>RWB   | <ul> <li>R/W Comparison Value for Comparator B — When RWBEN = 1, this bit determines whether a read or a write access qualifies comparator B. When RWBEN = 0, RWB and the R/W signal do not affect comparator B.</li> <li>0 Comparator B can match only on a write cycle</li> <li>1 Comparator B can match only on a read cycle</li> </ul>                                                                                                                                                                                                                                               |

| 0<br>RWBEN | <ul> <li>Enable R/W for Comparator B — Controls whether the level of R/W is considered for a comparator B match.</li> <li>0 R/W is not used in comparison B</li> <li>1 R/W is used in comparison B</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

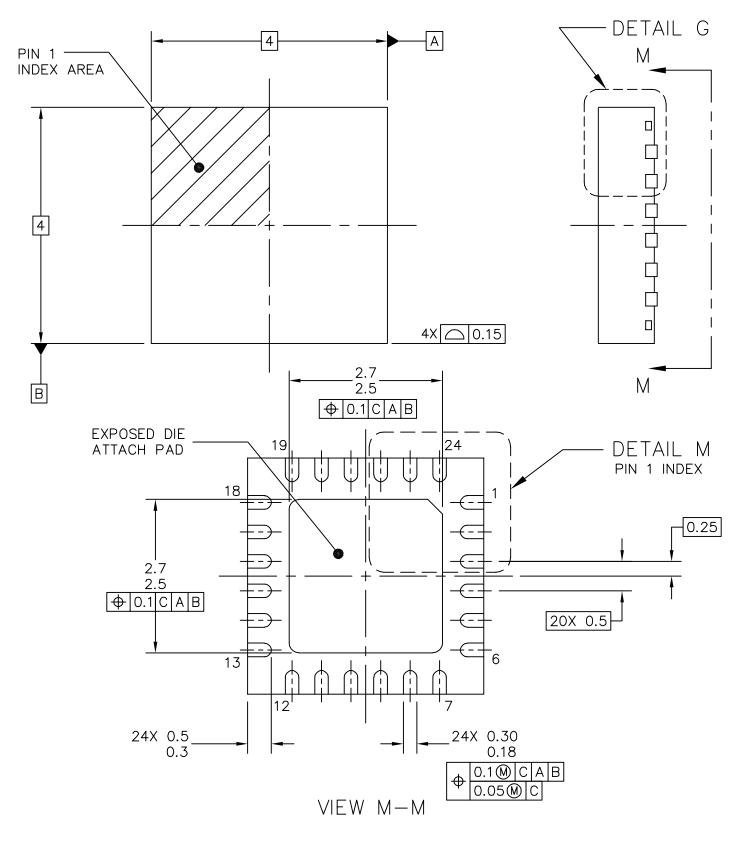

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE             |  | PRINT VERSION NOT TO SCALE |  |  |

|---------------------------------------------------------|--------------------------------|--|----------------------------|--|--|

| TITLE: THERMALLY ENHANCED                               | DOCUMENT NO: 98ARE10714D       |  | REV: O                     |  |  |

| FLAT NON-LEADED PACKA                                   | CASE NUMBER: 1969–01 23 JUL 20 |  |                            |  |  |

| 24 TERMINAL, 0.5 PITCH (4                               | STANDARD: JEDEC M0-220 VGGD-6  |  |                            |  |  |

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- A. THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- 5. THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- 6. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62 mm.

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA            | LOUTLINE                 | PRINT VERSION NO | DT TO SCALE |  |

|---------------------------------------------------------|----------------------|--------------------------|------------------|-------------|--|

| TITLE:                                                  | DOCUMENT NO          | REV: J                   |                  |             |  |

| 20LD SOIC W/B, 1.2<br>CASE OUTLINE                      | CASE NUMBER: 751D-07 |                          | 23 MAR 2005      |             |  |

|                                                         | _                    | STANDARD: JEDEC MS-013AC |                  |             |  |