Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                         |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 13                                                         |

| Program Memory Size        | 8KB (8K x 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 512 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | 16-TSSOP                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08sh8mtgr |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Addendum for Revision 3.0

# 1 Addendum for Revision 3.0

#### Table 1. MC9S08SH8 Rev 3.0 Addendum

| Location               | Description                                                                                                                                                                                                     |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix A "Electrical | In "Control Timing" table, changed minimum value of "Internal low power oscillator period" parameter from 800 $\mu$ s to 700 $\mu$ s. This value is under 5V VDD, -40 °C to 125 °C temperature range condition. |

# 2 Revision History

Table 2 provides a revision history for this document.

#### Table 2. Revision History Table

| Rev. Number | Substantive Changes                                                                                                                                    | Date of Release |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|             | Initial release. Changed minimum value of "Internal low power oscillator period" parameter from 800 $\mu$ s to 700 $\mu$ s, in "Control Timing" table. | 05/2012         |

## **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                                               |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.01               | 3/08/2006        | Initial review copy                                                                                                                                                                                                                                                                                                                                  |

| 1                  | 11/2007          | Updated Electricals and incorporated revisions from Project sync issues: 2394, 2600, 2601, and 2764.                                                                                                                                                                                                                                                 |

| 2                  | 3/2008           | Corrected SPI module to be version 3. Incorporated fixes for Project Sync issues: 2394, 2600, 2601, 2764, 3237, and 3279; as well as, ADC Temperature Sensor issues 3331 and 3335. Adjusted Features page leading and fixed minor grammatical errors. Added 20-SOIC package option for the C temp only. Corrected package drawing number for 24-QFN. |

| 3                  | 6/2008           | Added ICS over Termperature graph to Electricals. Resolved final TBDs.                                                                                                                                                                                                                                                                               |

© Freescale Semiconductor, Inc., 2007-2008. All rights reserved.

This product incorporates SuperFlash® Technology licensed from SST.

### **Section Number**

Title

### Page

|     | 9.4.7 | MCU Stop3 Mode Operation           |     |

|-----|-------|------------------------------------|-----|

|     |       | MCU Stop1 and Stop2 Mode Operation |     |

| 9.5 |       | ation Information                  |     |

|     | 9.5.1 | ADC Module Initialization Example  | 141 |

| 9.6 |       | ition Information                  |     |

|     |       | External Pins and Routing          |     |

|     |       | Sources of Error                   |     |

# Chapter 10 Internal Clock Source (S08ICSV2)

| 10.1 | Introduc | ction                             |     |

|------|----------|-----------------------------------|-----|

|      | 10.1.1   | Module Configuration              |     |

|      | 10.1.2   | Features                          | 151 |

|      | 10.1.3   | Block Diagram                     | 151 |

|      | 10.1.4   | Modes of Operation                |     |

| 10.2 | External | l Signal Description              |     |

| 10.3 | Register | Definition                        |     |

|      |          | ICS Control Register 1 (ICSC1)    |     |

|      | 10.3.2   | ICS Control Register 2 (ICSC2)    |     |

|      | 10.3.3   | ICS Trim Register (ICSTRM)        |     |

|      | 10.3.4   | ICS Status and Control (ICSSC)    |     |

| 10.4 | Function | nal Description                   |     |

|      | 10.4.1   | Operational Modes                 |     |

|      | 10.4.2   | Mode Switching                    |     |

|      |          | Bus Frequency Divider             |     |

|      | 10.4.4   | Low Power Bit Usage               |     |

|      | 10.4.5   | Internal Reference Clock          |     |

|      | 10.4.6   | Optional External Reference Clock |     |

|      | 10.4.7   | Fixed Frequency Clock             | 161 |

# Chapter 11 Inter-Integrated Circuit (S08IICV2)

| 11.1 | Introduction                       | 163 |

|------|------------------------------------|-----|

|      | 11.1.1 Module Configuration        | 163 |

|      | 11.1.2 Features                    | 165 |

|      | 11.1.3 Modes of Operation          | 165 |

|      | 11.1.4 Block Diagram               |     |

| 11.2 | External Signal Description        | 166 |

|      | 11.2.1 SCL — Serial Clock Line     | 166 |

|      | 11.2.2 SDA — Serial Data Line      | 166 |

| 11.3 | Register Definition                | 166 |

|      | 11.3.1 IIC Address Register (IICA) | 167 |

|      |                                    |     |

# Chapter 3 Modes of Operation

# 3.1 Introduction

The operating modes of the MC9S08SH8 are described in this chapter. Entry into each mode, exit from each mode, and functionality while in each of the modes are described.

# 3.2 Features

- Active background mode for code development

- Wait mode CPU shuts down to conserve power; system clocks are running and full regulation is maintained

- Stop modes System clocks are stopped and voltage regulator is in standby

- Stop3 All internal circuits are powered for fast recovery

- Stop2 Partial power down of internal circuits, RAM content is retained

# 3.3 Run Mode

This is the normal operating mode for the MC9S08SH8. This mode is selected upon the MCU exiting reset if the BKGD/MS pin is high. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at 0xFFFE–0xFFFF after reset.

# 3.4 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in the HCS08 core. The BDC, together with the on-chip debug module (DBG), provide the means for analyzing MCU operation during software development.

Active background mode is entered in any of the following ways:

- When the BKGD/MS pin is low during POR or immediately after issuing a background debug force reset (see Section 5.7.3, "System Background Debug Force Reset Register (SBDFR)")

- When a BACKGROUND command is received through the BKGD/MS pin

- When a BGND instruction is executed

- When encountering a BDC breakpoint

- When encountering a DBG breakpoint

After entering active background mode, the CPU is held in a suspended state waiting for serial background commands rather than executing instructions from the user application program.

# Chapter 4 Memory

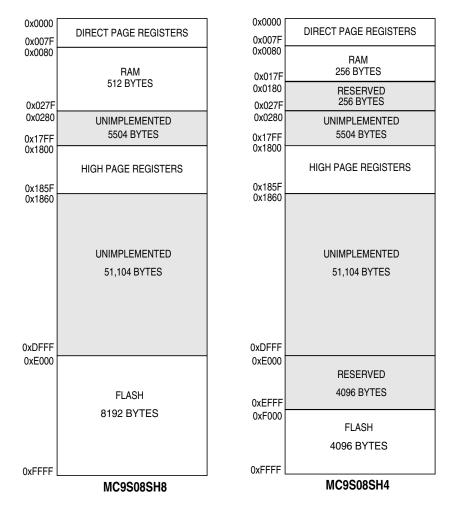

# 4.1 MC9S08SH8 Memory Map

As shown in Figure 4-1, on-chip memory in the MC9S08SH8 series of MCUs consists of RAM, FLASH program memory for nonvolatile data storage, and I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (0x0000 through 0x007F)

- High-page registers (0x1800 through 0x185F)

- Nonvolatile registers (0xFFB0 through 0xFFBF)

MC9S08SH8 MCU Series Data Sheet, Rev. 3

# 5.6 Low-Voltage Detect (LVD) System

The MC9S08SH8 includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and a LVD circuit with trip voltages for warning and detection. The LVD circuit is enabled when LVDE in SPMSC1 is set to 1. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop2, and the current consumption in stop3 with the LVD enabled will be higher.

### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the power-on reset rearm voltage level,  $V_{POR}$ , the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the low voltage detection low threshold,  $V_{LVDL}$ . Both the POR bit and the LVD bit in SRS are set following a POR.

### 5.6.2 Low-Voltage Detection (LVD) Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. The low voltage detection threshold is determined by the LVDV bit. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the low voltage detection threshold. The LVD bit in the SRS register is set following either an LVD reset or POR.

### 5.6.3 Low-Voltage Warning (LVW) Interrupt Operation

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching the low voltage condition. When a low voltage warning condition is detected and is configured for interrupt operation (LVWIE set to 1), LVWF in SPMSC1 will be set and an LVW interrupt request will occur.

# 5.7 Reset, Interrupt, and System Control Registers and Control Bits

One 8-bit register in the direct page register space and eight 8-bit registers in the high-page register space are related to reset and interrupt systems.

Refer to Table 4-2 and Table 4-3 in Chapter 4, "Memory," of this data sheet for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some control bits in the SOPT1 and SPMSC2 registers are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation."

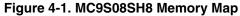

## 5.7.6 System Device Identification Register (SDIDH, SDIDL

These high page read-only registers are included so host development systems can identify the HCS08 derivative and revision number. This allows the development software to recognize where specific memory blocks, registers, and control bits are located in a target MCU.

<sup>1</sup> - Bit 7 is a mask option tie off that is used internally to determine that the device is a MC9S08SH8.

#### Figure 5-7. System Device Identification Register — High (SDIDH

#### Table 5-8. SDIDH Register Field Descriptions

| Field           | Description                                                                                                                                                                               |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7               | t 7 will read as a 0 for the MC9S08SH8 devices; writes have no effect.                                                                                                                    |  |  |  |  |

| 6:4<br>Reserved | Bits 6:4 are reserved. Reading these bits will result in an indeterminate value; writes have no effect.                                                                                   |  |  |  |  |

| 3:0<br>ID[11:8] | <b>Part Identification Numbe</b> — Each derivative in the HCS08 Family has a unique identification number. The MC9S08SH8 is hard coded to the value 0x014. See also ID bits in Table 5-9. |  |  |  |  |

= Unimplemented or Reserved

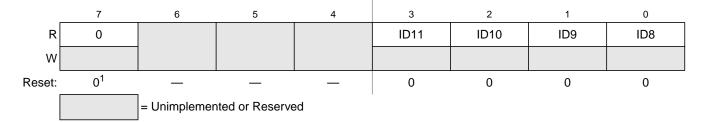

#### Figure 5-8. System Device Identification Register — L w (SDIDL)

#### Table 5-9. SDIDL Register Field Descriptions

| Field          | Description                                                                                                                                                                               |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>ID[7:0] | <b>Part Identification Numbe</b> — Each derivative in the HCS08 Family has a unique identification number. The MC9S08SH8 is hard coded to the value 0x014. See also ID bits in Table 5-8. |

Chapter 6 Parallel Input/Output Control

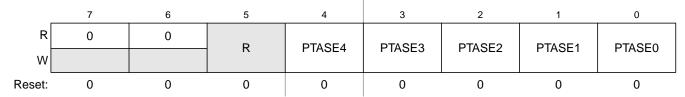

## 6.6.1.4 Port A Slew Rate Enable Register (PTASE)

#### Figure 6-6. Slew Rate Enable for Port A Register (PTASE)

#### Table 6-5. PTASE Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>Reserved | <b>Reserved Bits</b> — These bits are unused on this MCU, writes have no affect and could read as 1s or 0s.                                                                                                                                                                                                                            |

| 4:0           | Output Slew Rate Enable for Port A Bits — Each of these control bits determines if the output slew rate controlis enabled for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.0Output slew rate control disabled for port A bit n.1Output slew rate control enabled for port A bit n. |

### 6.6.1.5 Port A Drive Strength Selection Register (PTADS)

|        | 7 | 6 | 5 | 4       | 3       | 2       | 1      | 0      |

|--------|---|---|---|---------|---------|---------|--------|--------|

| R      | 0 | 0 | P | PTADS4  | PTADS3  | PTADS2  | PTADS1 | PTADS0 |

| w      |   |   | ĸ | F IAD34 | F IAD33 | F IAD32 | FIADST | FIAD30 |

| Reset: | 0 | 0 | 0 | 0       | 0       | 0       | 0      | 0      |

#### Figure 6-7. Drive Strength Selection for Port A Register (PTADS)

#### Table 6-6. PTADS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>Reserved     | <b>Reserved Bits</b> — These bits are unused on this MCU, writes have no affect and could read as 1s or 0s.                                                                                                                                                                                                                                                                       |

| 4:0<br>PTADS[4:0] | <ul> <li>Output Drive Strength Selection for Port A Bits — Each of these control bits selects between low and high output drive for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port A bit n.</li> <li>1 High output drive strength selected for port A bit n.</li> </ul> |

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

## 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

#### MC9S08SH8 MCU Series Data Sheet, Rev. 3

### 8.1.4 Features

The ACMP has the following features:

- Full rail to rail supply operation.

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output.

- Option to compare to fixed internal bandgap reference voltage.

- Option to allow comparator output to be visible on a pin, ACMPO.

- Can operate in stop3 mode

### 8.1.5 Modes of Operation

This section defines the ACMP operation in wait, stop and background debug modes.

### 8.1.5.1 ACMP in Wait Mode

The ACMP continues to run in wait mode if enabled before executing the WAIT instruction. Therefore, the ACMP can be used to bring the MCU out of wait mode if the ACMP interrupt, ACIE is enabled. For lowest possible current consumption, the ACMP should be disabled by software if not required as an interrupt source during wait mode.

### 8.1.5.2 ACMP in Stop Modes

### 8.1.5.2.1 Stop3 Mode Operation

The ACMP continues to operate in Stop3 mode if enabled and compare operation remains active. If ACOPE is enabled, comparator output operates as in the normal operating mode and comparator output is placed onto the external pin. The MCU is brought out of stop when a compare event occurs and ACIE is enabled; ACF flag sets accordingly.

If stop is exited with a reset, the ACMP will be put into its reset state.

### 8.1.5.2.2 Stop2 and Stop1 Mode Operation

During either Stop2 and Stop1 mode, the ACMP module will be fully powered down. Upon wake-up from Stop2 or Stop1 mode, the ACMP module will be in the reset state.

### 8.1.5.3 ACMP in Active Background Mode

When the microcontroller is in active background mode, the ACMP will continue to operate normally.

### 8.1.6 Block Diagram

The block diagram for the Analog Comparator module is shown Figure 8-2.

MC9S08SH8 MCU Series Data Sheet, Rev. 3

#### Chapter 9 Analog-to-Digital Converter (S08ADC10V1)

converter yields the lower code (and vice-versa). However, even very small amounts of system noise can cause the converter to be indeterminate (between two codes) for a range of input voltages around the transition voltage. This range is normally around 1/2LSB and will increase with noise. This error may be reduced by repeatedly sampling the input and averaging the result. Additionally the techniques discussed in Section 9.6.2.3 will reduce this error.

Non-monotonicity is defined as when, except for code jitter, the converter converts to a lower code for a higher input voltage. Missing codes are those values which are never converted for any input value.

In 8-bit or 10-bit mode, the ADC is guaranteed to be monotonic and to have no missing codes.

### 11.1.2 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated start signal generation

- Acknowledge bit generation/detection

- Bus busy detection

- General call recognition

- 10-bit address extension

### 11.1.3 Modes of Operation

A brief description of the IIC in the various MCU modes is given here.

- **Run mode** This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module continues to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- **Stop mode** The IIC is inactive in stop3 mode for reduced power consumption. The stop instruction does not affect IIC register states. Stop2 resets the register contents.

Chapter 14 Serial Communications Interface (S08SCIV4)

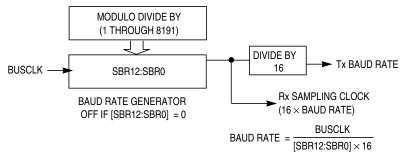

Figure 14-12. SCI Baud Rate Generation

SCI communications require the transmitter and receiver (which typically derive baud rates from independent clock sources) to use the same baud rate. Allowed tolerance on this baud frequency depends on the details of how the receiver synchronizes to the leading edge of the start bit and how bit sampling is performed.

The MCU resynchronizes to bit boundaries on every high-to-low transition, but in the worst case, there are no such transitions in the full 10- or 11-bit time character frame so any mismatch in baud rate is accumulated for the whole character time. For a Freescale Semiconductor SCI system whose bus frequency is driven by a crystal, the allowed baud rate mismatch is about 4.5percent for 8-bit data format and about 4 percent for 9-bit data format. Although baud rate modulo divider settings do not always produce baud rates that exactly match standard rates, it is normally possible to get within a few percent, which is acceptable for reliable communications.

## 14.3.2 Transmitter Functional Description

This section describes the overall block diagram for the SCI transmitter, as well as specialized functions for sending break and idle characters. The transmitter block diagram is shown in Figure 14-2.

The transmitter output (TxD) idle state defaults to logic high (TXINV = 0 following reset). The transmitter output is inverted by setting TXINV = 1. The transmitter is enabled by setting the TE bit in SCIxC2. This queues a preamble character that is one full character frame of the idle state. The transmitter then remains idle until data is available in the transmit data buffer. Programs store data into the transmit data buffer by writing to the SCI data register (SCIxD).

The central element of the SCI transmitter is the transmit shift register that is either 10 or 11 bits long depending on the setting in the M control bit. For the remainder of this section, we will assume M = 0, selecting the normal 8-bit data mode. In 8-bit data mode, the shift register holds a start bit, eight data bits, and a stop bit. When the transmit shift register is available for a new SCI character, the value waiting in the transmit data register is transferred to the shift register (synchronized with the baud rate clock) and the transmit data register empty (TDRE) status flag is set to indicate another character may be written to the transmit data buffer at SCIxD.

If no new character is waiting in the transmit data buffer after a stop bit is shifted out the TxD pin, the transmitter sets the transmit complete flag and enters an idle mode, with TxD high, waiting for more characters to transmit.

Chapter 15 Serial Peripheral Interface (S08SPIV3)

| SPPR2:SPPR1:SPPR0 | Prescaler Divisor |

|-------------------|-------------------|

| 0:0:0             | 1                 |

| 0:0:1             | 2                 |

| 0:1:0             | 3                 |

| 0:1:1             | 4                 |

| 1:0:0             | 5                 |

| 1:0:1             | 6                 |

| 1:1:0             | 7                 |

| 1:1:1             | 8                 |

#### Table 15-5. SPI Baud Rate Prescaler Divisor

#### Table 15-6. SPI Baud Rate Divisor

| SPR2:SPR1:SPR0 | Rate Divisor |  |  |

|----------------|--------------|--|--|

| 0:0:0          | 2            |  |  |

| 0:0:1          | 4            |  |  |

| 0:1:0          | 8            |  |  |

| 0:1:1          | 16           |  |  |

| 1:0:0          | 32           |  |  |

| 1:0:1          | 64           |  |  |

| 1:1:0          | 128          |  |  |

| 1:1:1          | 256          |  |  |

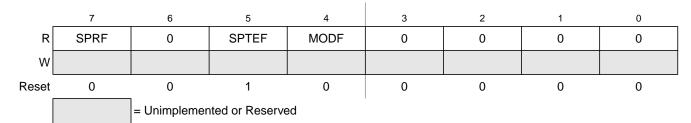

## 15.4.4 SPI Status Register (SPIS)

This register has three read-only status bits. Bits 6, 3, 2, 1, and 0 are not implemented and always read 0. Writes have no meaning or effect.

Figure 15-8. SPI Status Register (SPIS)

#### Chapter 16 Timer/PWM Module (S08TPMV3)

(becomes unlatched) when the TPMxCnSC register is written (whether BDM mode is active or not). Any write to the channel registers will be ignored during the input capture mode.

When BDM is active, the coherency mechanism is frozen (unless reset by writing to TPMxCnSC register) such that the buffer latches remain in the state they were in when the BDM became active, even if one or both halves of the channel register are read while BDM is active. This assures that if the user was in the middle of reading a 16-bit register when BDM became active, it will read the appropriate value from the other half of the 16-bit value after returning to normal execution. The value read from the TPMxCnVH and TPMxCnVL registers in BDM mode is the value of these registers and not the value of their read buffer.

In output compare or PWM modes, writing to either byte (TPMxCnVH or TPMxCnVL) latches the value into a buffer. After both bytes are written, they are transferred as a coherent 16-bit value into the timer-channel registers according to the value of CLKSB:CLKSA bits and the selected mode, so:

- If (CLKSB:CLKSA = 0:0), then the registers are updated when the second byte is written.

- If (CLKSB:CLKSA not = 0:0 and in output compare mode) then the registers are updated after the second byte is written and on the next change of the TPM counter (end of the prescaler counting).

- If (CLKSB:CLKSA not = 0:0 and in EPWM or CPWM modes), then the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL - 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter then the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

The latching mechanism may be manually reset by writing to the TPMxCnSC register (whether BDM mode is active or not). This latching mechanism allows coherent 16-bit writes in either big-endian or little-endian order which is friendly to various compiler implementations.

When BDM is active, the coherency mechanism is frozen such that the buffer latches remain in the state they were in when the BDM became active even if one or both halves of the channel register are written while BDM is active. Any write to the channel registers bypasses the buffer latches and directly write to the channel register while BDM is active. The values written to the channel register while BDM is active are used for PWM & output compare operation once normal execution resumes. Writes to the channel registers while BDM is active do not interfere with partial completion of a coherency sequence. After the coherency mechanism has been fully exercised, the channel registers are updated using the buffered values written (while BDM was not active) by the user.

# 16.4 Functional Description

All TPM functions are associated with a central 16-bit counter which allows flexible selection of the clock source and prescale factor. There is also a 16-bit modulo register associated with the main counter.

The CPWMS control bit chooses between center-aligned PWM operation for all channels in the TPM (CPWMS=1) or general purpose timing functions (CPWMS=0) where each channel can independently be configured to operate in input capture, output compare, or edge-aligned PWM mode. The CPWMS control bit is located in the main TPM status and control register because it affects all channels within the TPM and influences the way the main counter operates. (In CPWM mode, the counter changes to an up/down mode rather than the up-counting mode used for general purpose timer functions.)

Chapter 16 Timer/PWM Module (S08TPMV3)

• Non-intrusive commands can be executed at any time even while the user's program is running. Non-intrusive commands allow a user to read or write MCU memory locations or access status and control registers within the background debug controller.

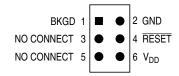

Typically, a relatively simple interface pod is used to translate commands from a host computer into commands for the custom serial interface to the single-wire background debug system. Depending on the development tool vendor, this interface pod may use a standard RS-232 serial port, a parallel printer port, or some other type of communications such as a universal serial bus (USB) to communicate between the host PC and the pod. The pod typically connects to the target system with ground, the BKGD pin, RESET, and sometimes  $V_{DD}$ . An open-drain connection to reset allows the host to force a target system reset, which is useful to regain control of a lost target system or to control startup of a target system before the on-chip nonvolatile memory has been programmed. Sometimes  $V_{DD}$  can be used to allow the pod to use power from the target system to avoid the need for a separate power supply. However, if the pod is powered separately, it can be connected to a running target system without forcing a target system reset or otherwise disturbing the running application program.

Figure 17-1. BDM Tool Connector

### 17.2.1 BKGD Pin Description

BKGD is the single-wire background debug interface pin. The primary function of this pin is for bidirectional serial communication of active background mode commands and data. During reset, this pin is used to select between starting in active background mode or starting the user's application program. This pin is also used to request a timed sync response pulse to allow a host development tool to determine the correct clock frequency for background debug serial communications.

BDC serial communications use a custom serial protocol first introduced on the M68HC12 Family of microcontrollers. This protocol assumes the host knows the communication clock rate that is determined by the target BDC clock rate. All communication is initiated and controlled by the host that drives a high-to-low edge to signal the beginning of each bit time. Commands and data are sent most significant bit first (MSB first). For a detailed description of the communications protocol, refer to Section 17.2.2, "Communication Details."

If a host is attempting to communicate with a target MCU that has an unknown BDC clock rate, a SYNC command may be sent to the target MCU to request a timed sync response signal from which the host can determine the correct communication speed.

BKGD is a pseudo-open-drain pin and there is an on-chip pullup so no external pullup resistor is required. Unlike typical open-drain pins, the external RC time constant on this pin, which is influenced by external capacitance, plays almost no role in signal rise time. The custom protocol provides for brief, actively driven speedup pulses to force rapid rise times on this pin without risking harmful drive level conflicts. Refer to Section 17.2.2, "Communication Details," for more detail.

Chapter 17 Development Support

# 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

## 17.3.6 Hardware Breakpoints

The BRKEN control bit in the DBGC register may be set to 1 to allow any of the trigger conditions described in Section 17.3.5, "Trigger Modes," to be used to generate a hardware breakpoint request to the CPU. TAG in DBGC controls whether the breakpoint request will be treated as a tag-type breakpoint or a force-type breakpoint. A tag breakpoint causes the current opcode to be marked as it enters the instruction queue. If a tagged opcode reaches the end of the pipe, the CPU executes a BGND instruction to go to active background mode rather than executing the tagged opcode. A force-type breakpoint causes the CPU to finish the current instruction and then go to active background mode.

If the background mode has not been enabled (ENBDM = 1) by a serial WRITE\_CONTROL command through the BKGD pin, the CPU will execute an SWI instruction instead of going to active background mode.

# 17.4 Register Definitio

This section contains the descriptions of the BDC and DBG registers and control bits.

Refer to the high-page register summary in the device overview chapter of this data sheet for the absolute address assignments for all DBG registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

# 17.4.1 BDC Registers and Control Bits

The BDC has two registers:

- The BDC status and control register (BDCSCR) is an 8-bit register containing control and status bits for the background debug controller.

- The BDC breakpoint match register (BDCBKPT) holds a 16-bit breakpoint match address.

These registers are accessed with dedicated serial BDC commands and are not located in the memory space of the target MCU (so they do not have addresses and cannot be accessed by user programs).

Some of the bits in the BDCSCR have write limitations; otherwise, these registers may be read or written at any time. For example, the ENBDM control bit may not be written while the MCU is in active background mode. (This prevents the ambiguous condition of the control bit forbidding active background mode while the MCU is already in active background mode.) Also, the four status bits (BDMACT, WS, WSF, and DVF) are read-only status indicators and can never be written by the WRITE\_CONTROL serial BDC command. The clock switch (CLKSW) control bit may be read or written at any time.

NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFN.

4 COPLANARITY APPLIES TO LEADS AND DIE ATTACH PAD.

5. MIN. METAL GAP SHOULD BE 0.2 MM.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                                               | MECHANICAL OUTLINE |                               | PRINT VERSION NOT TO SCALE |             |

|-------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|----------------------------|-------------|

| TITLE: THERMALLY ENHANCED QUAD<br>FLAT NON-LEADED PACKAGE (QFN)<br>24 TERMINAL, 0.5 PITCH (4 X 4 X 1) |                    | DOCUMENT NO                   | ): 98ARE10714D             | REV: O      |

|                                                                                                       |                    | CASE NUMBER                   | 8: 1969–01                 | 23 JUL 2007 |

|                                                                                                       |                    | STANDARD: JEDEC M0-220 VGGD-6 |                            |             |