# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 17                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 20-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh8mwjr |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Section Number**

Title

### Page

| 6.3 | Ganged   | Output                        | 77 |

|-----|----------|-------------------------------|----|

| 6.4 | Pin Inte | rrupts                        | 78 |

|     | 6.4.1    | Edge Only Sensitivity         | 78 |

|     | 6.4.2    | Edge and Level Sensitivity    | 78 |

|     | 6.4.3    | Pull-up/Pull-down Resistors   | 79 |

|     | 6.4.4    | Pin Interrupt Initialization  | 79 |

| 6.5 | Pin Beh  | avior in Stop Modes           | 79 |

| 6.6 | Parallel | I/O and Pin Control Registers | 79 |

|     | 6.6.1    | Port A Registers              | 80 |

|     |          | Port B Registers              |    |

|     | 6.6.3    | Port C Registers              | 89 |

|     |          |                               |    |

## Chapter 7 Central Processor Unit (S08CPUV2)

| 7.1 | Introdu | ction                           | 93  |

|-----|---------|---------------------------------|-----|

|     | 7.1.1   | Features                        |     |

| 7.2 | Program | nmer's Model and CPU Registers  | 94  |

|     | 7.2.1   | Accumulator (A)                 | 94  |

|     | 7.2.2   | Index Register (H:X)            | 94  |

|     | 7.2.3   | Stack Pointer (SP)              | 95  |

|     | 7.2.4   | Program Counter (PC)            | 95  |

|     | 7.2.5   | Condition Code Register (CCR)   | 95  |

| 7.3 | Address | sing Modes                      | 97  |

|     | 7.3.1   | Inherent Addressing Mode (INH)  | 97  |

|     | 7.3.2   | Relative Addressing Mode (REL)  | 97  |

|     | 7.3.3   | Immediate Addressing Mode (IMM) | 97  |

|     | 7.3.4   | Direct Addressing Mode (DIR)    | 97  |

|     | 7.3.5   | Extended Addressing Mode (EXT)  |     |

|     | 7.3.6   | Indexed Addressing Mode         |     |

| 7.4 | Special | Operations                      | 99  |

|     | 7.4.1   | Reset Sequence                  | 99  |

|     | 7.4.2   | Interrupt Sequence              | 99  |

|     | 7.4.3   | Wait Mode Operation             | 100 |

|     | 7.4.4   | Stop Mode Operation             | 100 |

|     | 7.4.5   | BGND Instruction                | 101 |

| 7.5 | HCS08   | Instruction Set Summary         | 102 |

## Chapter 8 Analog Comparator 5-V (S08ACMPV2)

| 8.1 | Introduc | ction                          | 113 |

|-----|----------|--------------------------------|-----|

|     |          | ACMP Configuration Information |     |

|     | 8.1.2    | ACMP in Stop3 Mode             | 113 |

MC9S08SH8 MCU Series Data Sheet, Rev. 3

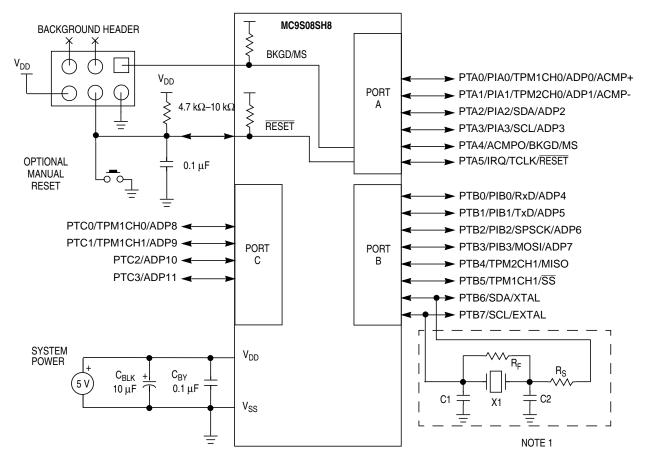

NOTES:

- 1. External crystal circuit not required if using the internal clock option.

- RESET pin can only be used to reset into user mode, you can not enter BDM using RESET pin. BDM can be entered by holding MS low during POR or writing a 1 to BDFR in SBDFR with MS low after issuing BDM command.

- 3. RC filter on RESET pin recommended for noisy environments.

#### Figure 2-5. Basic System Connections

#### 2.2.1 **Power**

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry, ACMP and ADC modules, and to an internal voltage regulator. The internal voltage regulator provides regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a 10- $\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system and a 0.1- $\mu$ F ceramic bypass capacitor located as near to the MCU power pins as practical to suppress high-frequency noise. Each pin must have a bypass capacitor for best noise suppression.

#### **Chapter 3 Modes of Operation**

Background commands are of two types:

- Non-intrusive commands, defined as commands that can be issued while the user program is running. Non-intrusive commands can be issued through the BKGD/MS pin while the MCU is in run mode; non-intrusive commands can also be executed when the MCU is in the active background mode. Non-intrusive commands include:

- Memory access commands

- Memory-access-with-status commands

- BDC register access commands

- The BACKGROUND command

- Active background commands, which can only be executed while the MCU is in active background mode. Active background commands include commands to:

- Read or write CPU registers

- Trace one user program instruction at a time

- Leave active background mode to return to the user application program (GO)

The active background mode is used to program a bootloader or user application program into the FLASH program memory before the MCU is operated in run mode for the first time. When the MC9S08SH8 is shipped from the Freescale Semiconductor factory, the FLASH program memory is erased by default unless specifically noted so there is no program that could be executed in run mode until the FLASH memory is initially programmed. The active background mode can also be used to erase and reprogram the FLASH memory after it has been previously programmed.

For additional information about the active background mode, refer to the Development Support chapter.

## 3.5 Wait Mode

Wait mode is entered by executing a WAIT instruction. Upon execution of the WAIT instruction, the CPU enters a low-power state in which it is not clocked. The I bit in CCR is cleared when the CPU enters the wait mode, enabling interrupts. When an interrupt request occurs, the CPU exits the wait mode and resumes processing, beginning with the stacking operations leading to the interrupt service routine.

While the MCU is in wait mode, there are some restrictions on which background debug commands can be used. Only the BACKGROUND command and memory-access-with-status commands are available when the MCU is in wait mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from wait mode and enter active background mode.

## 3.6 Stop Modes

One of two stop modes is entered upon execution of a STOP instruction when STOPE in SOPT1. In any stop mode, the bus and CPU clocks are halted. The ICS module can be configured to leave the reference clocks running. See Chapter 10, "Internal Clock Source (S08ICSV2)," for more information.

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

| Address            | Register Name | Bit 7   | 6      | 5      | 4       | 3      | 2      | 1       | Bit 0   |

|--------------------|---------------|---------|--------|--------|---------|--------|--------|---------|---------|

| 0x1800             | SRS           | POR     | PIN    | COP    | ILOP    | ILAD   | 0      | LVD     | 0       |

| 0x1801             | SBDFR         | 0       | 0      | 0      | 0       | 0      | 0      | 0       | BDFR    |

| 0x1802             | SOPT1         | СО      | PT     | STOPE  | 0       | 0      | IICPS  | BKGDPE  | RSTPE   |

| 0x1803             | SOPT2         | COPCLKS | COPW   | 0      | ACIC    | 0      | 0      | T1CH1PS | T1CH0PS |

| 0x1804 —<br>0x1805 | Reserved      | _       |        | _      | _       |        | _      | _       | _       |

| 0x1806             | SDIDH         | 0       |        | —      | —       | ID11   | ID10   | ID9     | ID8     |

| 0x1807             | SDIDL         | ID7     | ID6    | ID5    | ID4     | ID3    | ID2    | ID1     | ID0     |

| 0x1808             | Reserved      | —       | _      | —      | —       | _      | —      | —       | —       |

| 0x1809             | SPMSC1        | LVWF    | LVWACK | LVWIE  | LVDRE   | LVDSE  | LVDE   | 0       | BGBE    |

| 0x180A             | SPMSC2        | 0       | 0      | LVDV   | LVWV    | PPDF   | PPDACK | —       | PPDC    |

| 0x180B–<br>0x180F  | Reserved      | _       | _      | _      | _       | _      | _      | _       | _       |

| 0x1810             | DBGCAH        | Bit 15  | 14     | 13     | 12      | 11     | 10     | 9       | Bit 8   |

| 0x1811             | DBGCAL        | Bit 7   | 6      | 5      | 4       | 3      | 2      | 1       | Bit 0   |

| 0x1812             | DBGCBH        | Bit 15  | 14     | 13     | 12      | 11     | 10     | 9       | Bit 8   |

| 0x1813             | DBGCBL        | Bit 7   | 6      | 5      | 4       | 3      | 2      | 1       | Bit 0   |

| 0x1814             | DBGFH         | Bit 15  | 14     | 13     | 12      | 11     | 10     | 9       | Bit 8   |

| 0x1815             | DBGFL         | Bit 7   | 6      | 5      | 4       | 3      | 2      | 1       | Bit 0   |

| 0x1816             | DBGC          | DBGEN   | ARM    | TAG    | BRKEN   | RWA    | RWAEN  | RWB     | RWBEN   |

| 0x1817             | DBGT          | TRGSEL  | BEGIN  | 0      | 0       | TRG3   | TRG2   | TRG1    | TRG0    |

| 0x1818             | DBGS          | AF      | BF     | ARMF   | 0       | CNT3   | CNT2   | CNT1    | CNT0    |

| 0x1819–<br>0x181F  | Reserved      |         |        |        |         |        |        | _       | —       |

| 0x1820             | FCDIV         | DIVLD   | PRDIV8 |        |         | D      | IV     |         |         |

| 0x1821             | FOPT          | KEYEN   | FNORED | 0      | 0       | 0      | 0      | SE      | EC      |

| 0x1822             | Reserved      | —       | —      | _      | —       | _      | _      | —       | —       |

| 0x1823             | FCNFG         | 0       | 0      | KEYACC | 0       | 0      | 0      | 0       | 0       |

| 0x1824             | FPROT         |         |        |        | FPS     |        |        |         | FPDIS   |

| 0x1825             | FSTAT         | FCBEF   | FCCF   | FPVIOL | FACCERR | 0      | FBLANK | 0       | 0       |

| 0x1826             | FCMD          | FCMD    |        |        |         |        |        |         |         |

| 0x1827–<br>0x183F  | Reserved      | _       | _      | _      | _       | _      | _      |         | _       |

| 0x1840             | PTAPE         | 0       | 0      | PTAPE5 | PTAPE4  | PTAPE3 | PTAPE2 | PTAPE1  | PTAPE0  |

| 0x1841             | PTASE         | 0       | 0      | —      | PTASE4  | PTASE3 | PTASE2 | PTASE1  | PTASE0  |

| 0x1842             | PTADS         | 0       | 0      | —      | PTADS4  | PTADS3 | PTADS2 | PTADS1  | PTADS0  |

| 0x1843             | Reserved      | —       | _      | —      |         | —      |        | —       | _       |

| 0x1844             | PTASC         | 0       | 0      | 0      | 0       | PTAIF  | PTAACK | PTAIE   | PTAMOD  |

#### Table 4-3. High-Page Register Summary (Sheet 1 of 2)

MC9S08SH8 MCU Series Data Sheet, Rev. 3

## 5.6 Low-Voltage Detect (LVD) System

The MC9S08SH8 includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and a LVD circuit with trip voltages for warning and detection. The LVD circuit is enabled when LVDE in SPMSC1 is set to 1. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop2, and the current consumption in stop3 with the LVD enabled will be higher.

### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the power-on reset rearm voltage level,  $V_{POR}$ , the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the low voltage detection low threshold,  $V_{LVDL}$ . Both the POR bit and the LVD bit in SRS are set following a POR.

### 5.6.2 Low-Voltage Detection (LVD) Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. The low voltage detection threshold is determined by the LVDV bit. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the low voltage detection threshold. The LVD bit in the SRS register is set following either an LVD reset or POR.

### 5.6.3 Low-Voltage Warning (LVW) Interrupt Operation

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching the low voltage condition. When a low voltage warning condition is detected and is configured for interrupt operation (LVWIE set to 1), LVWF in SPMSC1 will be set and an LVW interrupt request will occur.

## 5.7 Reset, Interrupt, and System Control Registers and Control Bits

One 8-bit register in the direct page register space and eight 8-bit registers in the high-page register space are related to reset and interrupt systems.

Refer to Table 4-2 and Table 4-3 in Chapter 4, "Memory," of this data sheet for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some control bits in the SOPT1 and SPMSC2 registers are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation."

Chapter 6 Parallel Input/Output Control

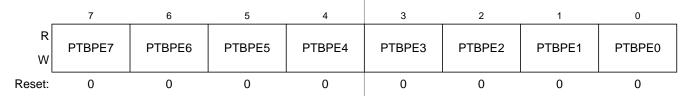

## 6.6.2.3 Port B Pull Enable Register (PTBPE)

Figure 6-13. Internal Pull Enable for Port B Register (PTBPE)

#### Table 6-12. PTBPE Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | Internal Pull Enable for Port B Bits — Each of these control bits determines if the internal pull-up or pull-down                                                                                                                                                                                                                      |

|       | <ul> <li>device is enabled for the associated PTB pin. For port B pins that are configured as outputs, these bits have no effect and the internal pull devices are disabled.</li> <li>0 Internal pull-up/pull-down device disabled for port B bit n.</li> <li>1 Internal pull-up/pull-down device enabled for port B bit n.</li> </ul> |

#### NOTE

Pull-down devices only apply when using pin interrupt functions, when corresponding edge select and pin select functions are configured.

### 6.6.2.4 Port B Slew Rate Enable Register (PTBSE)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBSE7 | PTBSE6 | PTBSE5 | PTBSE4 | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-14. Slew Rate Enable for Port B Register (PTBSE)

#### Table 6-13. PTBSE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBSE[7:0] | <ul> <li>Output Slew Rate Enable for Port B Bits — Each of these control bits determines if the output slew rate control is enabled for the associated PTB pin. For port B pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port B bit n.</li> <li>Output slew rate control enabled for port B bit n.</li> </ul> |

## 8.2 External Signal Description

The ACMP has two analog input pins, ACMP+ and ACMP- and one digital output pin ACMPO. Each of these pins can accept an input voltage that varies across the full operating voltage range of the MCU. As shown in Figure 8-2, the ACMP- pin is connected to the inverting input of the comparator, and the ACMP+ pin is connected to the comparator non-inverting input if ACBGS is a 0. As shown in Figure 8-2, the ACMPO pin can be enabled to drive an external pin.

The signal properties of ACMP are shown in Table 8-1.

| Signal | Function                                                    | I/O |

|--------|-------------------------------------------------------------|-----|

| ACMP-  | Inverting analog input to the ACMP.<br>(Minus input)        | I   |

| ACMP+  | Non-inverting analog input to the ACMP.<br>(Positive input) | I   |

| ACMPO  | Digital output of the ACMP.                                 | 0   |

Table 8-1. Signal Properties

### 8.3 Memory Map

### 8.3.1 Register Descriptions

The ACMP includes one register:

• An 8-bit status and control register

Refer to the direct-page register summary in the memory section of this data sheet for the absolute address assignments for all ACMP registers. This section refers to registers and control bits only by their names .

Some MCUs may have more than one ACMP, so register names include placeholder characters to identify which ACMP is being referenced.

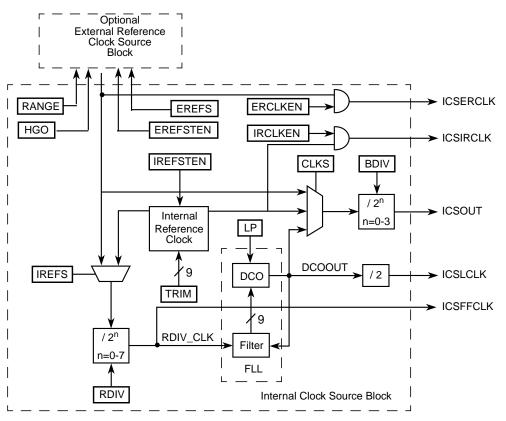

Chapter 10 Internal Clock Source (S08ICSV2)

Figure 10-2. Internal Clock Source (ICS) Block Diagram

### 10.1.4 Modes of Operation

There are seven modes of operation for the ICS: FEI, FEE, FBI, FBILP, FBE, FBELP, and stop.

### 10.1.4.1 FLL Engaged Internal (FEI)

In FLL engaged internal mode, which is the default mode, the ICS supplies a clock derived from the FLL which is controlled by the internal reference clock. The BDC clock is supplied from the FLL.

### 10.1.4.2 FLL Engaged External (FEE)

In FLL engaged external mode, the ICS supplies a clock derived from the FLL which is controlled by an external reference clock. The BDC clock is supplied from the FLL.

### 10.1.4.3 FLL Bypassed Internal (FBI)

In FLL bypassed internal mode, the FLL is enabled and controlled by the internal reference clock, but is bypassed. The ICS supplies a clock derived from the internal reference clock. The BDC clock is supplied from the FLL.

#### Chapter 11 Inter-Integrated Circuit (S08IICV2)

the transition from master to slave mode does not generate a stop condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

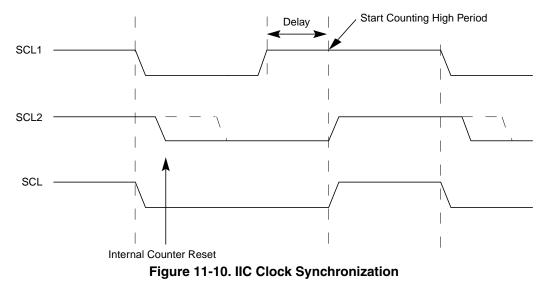

### 11.4.1.7 Clock Synchronization

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 11-10). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

### 11.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such a case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

### 11.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

### 11.4.2 10-bit Address

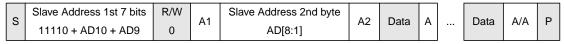

For 10-bit addressing, 0x11110 is used for the first 5 bits of the first address byte. Various combinations of read/write formats are possible within a transfer that includes 10-bit addressing.

### 11.4.2.1 Master-Transmitter Addresses a Slave-Receiver

The transfer direction is not changed (see Table 11-10). When a 10-bit address follows a start condition, each slave compares the first seven bits of the first byte of the slave address (11110XX) with its own address and tests whether the eighth bit ( $R/\overline{W}$  direction bit) is 0. More than one device can find a match and generate an acknowledge (A1). Then, each slave that finds a match compares the eight bits of the second byte of the slave address with its own address. Only one slave finds a match and generates an acknowledge (A2). The matching slave remains addressed by the master until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

Table 11-10. Master-Transmitter Addresses Slave-Receiver with a 10-bit Address

After the master-transmitter has sent the first byte of the 10-bit address, the slave-receiver sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

#### 11.4.2.2 Master-Receiver Addresses a Slave-Transmitter

The transfer direction is changed after the second  $R/\overline{W}$  bit (see Table 11-11). Up to and including acknowledge bit A2, the procedure is the same as that described for a master-transmitter addressing a slave-receiver. After the repeated start condition (Sr), a matching slave remembers that it was addressed before. This slave then checks whether the first seven bits of the first byte of the slave address following Sr are the same as they were after the start condition (S) and tests whether the eighth ( $R/\overline{W}$ ) bit is 1. If there is a match, the slave considers that it has been addressed as a transmitter and generates acknowledge A3. The slave-transmitter remains addressed until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

After a repeated start condition (Sr), all other slave devices also compare the first seven bits of the first byte of the slave address with their own addresses and test the eighth  $(R/\overline{W})$  bit. However, none of them are addressed because  $R/\overline{W} = 1$  (for 10-bit devices) or the 11110XX slave address (for 7-bit devices) does not match.

| s | Slave Address<br>1st 7 bits | R/W | A1 | Slave Address<br>2nd byte | A2 | Sr | Slave Address<br>1st 7 bits | R/W | A3 | Data | A | <br>Data | A | Р |

|---|-----------------------------|-----|----|---------------------------|----|----|-----------------------------|-----|----|------|---|----------|---|---|

|   | 11110 + AD10 + AD9          | 0   |    | AD[8:1]                   |    |    | 11110 + AD10 + AD9          | 1   |    |      |   |          |   |   |

Table 11-11. Master-Receiver Addresses a Slave-Transmitter with a 10-bit Address

After the master-receiver has sent the first byte of the 10-bit address, the slave-transmitter sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

Chapter 11 Inter-Integrated Circuit (S08IICV2)

### 11.4.3 General Call Address

General calls can be requested in 7-bit address or 10-bit address. If the GCAEN bit is set, the IIC matches the general call address as well as its own slave address. When the IIC responds to a general call, it acts as a slave-receiver and the IAAS bit is set after the address cycle. Software must read the IICD register after the first byte transfer to determine whether the address matches is its own slave address or a general call. If the value is 00, the match is a general call. If the GCAEN bit is clear, the IIC ignores any data supplied from a general call address by not issuing an acknowledgement.

## 11.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

## 11.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 11-12 occur, provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a 1 to it in the interrupt routine. You can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | licif | IICIE        |

| Match of received calling address | IAAS   | licif | IICIE        |

| Arbitration Lost                  | ARBL   | licif | IICIE        |

Table 11-12. Interrupt Summary

### 11.6.1 Byte Transfer Interrupt

The TCF (transfer complete flag) bit is set at the falling edge of the ninth clock to indicate the completion of byte transfer.

### 11.6.2 Address Detect Interrupt

When the calling address matches the programmed slave address (IIC address register) or when the GCAEN bit is set and a general call is received, the IAAS bit in the status register is set. The CPU is interrupted, provided the IICIE is set. The CPU must check the SRW bit and set its Tx mode accordingly.

### 11.6.3 Arbitration Lost Interrupt

The IIC is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, the relative priority of the contending masters is determined by a data arbitration procedure. The IIC module asserts this interrupt when it loses the data arbitration process and the ARBL bit in the status register is set.

## Chapter 12 Modulo Timer (S08MTIMV1)

## 12.1 Introduction

The MTIM is a simple 8-bit timer with several software selectable clock sources and a programmable interrupt.

The central component of the MTIM is the 8-bit counter, which can operate as a free-running counter or a modulo counter. A timer overflow interrupt can be enabled to generate periodic interrupts for time-based software loops.

Figure 12-1 shows the MC9S08SH8 block diagram with the MTIM module highlighted.

### **12.1.1 MTIM Configuration In ormation**

The external clock for the MTIM module, TCLK, is selected by setting CLKS = 1:1 or 1:0 in MTIMCLK, which selects the TCLK pin input. The TCLK input on PTA0 can be enabled as external clock inputs to both MTIM and TPM modules simultaneously.

### 12.1.2 Features

Timer system features include:

- 8-bit up-counter

- Free-running or 8-bit modulo limit

- Software controllable interrupt on overflow

- Counter reset bit (TRST)

- Counter stop bit (TSTP)

- Four software selectable clock sources for input to prescaler:

- System bus clock rising edge

- Fixed frequency clock (XCLK) rising edge

- External clock source on the TCLK pin rising edge

- External clock source on the TCLK pin falling edge

- Nine selectable clock prescale values:

- Clock source divide by 1, 2, 4, 8, 16, 32, 64, 128, or 256

### 12.1.3 Modes of Operation

This section defines the MTIM's operation in stop, wait and background debug modes.

### 12.1.3.1 MTIM in Wait Mode

The MTIM continues to run in wait mode if enabled before executing the WAIT instruction. Therefore, the MTIM can be used to bring the MCU out of wait mode if the timer overflow interrupt is enabled. For lowest possible current consumption, the MTIM should be stopped by software if not needed as an interrupt source during wait mode.

### 12.1.3.2 MTIM in Stop Modes

The MTIM is disabled in all stop modes, regardless of the settings before executing the STOP instruction. Therefore, the MTIM cannot be used as a wake up source from stop modes.

Waking from stop1 and stop2 modes, the MTIM will be put into its reset state. If stop3 is exited with a reset, the MTIM will be put into its reset state. If stop3 is exited with an interrupt, the MTIM continues from the state it was in when stop3 was entered. If the counter was active upon entering stop3, the count will resume from the current value.

### 12.1.3.3 MTIM in Active Background Mode

The MTIM suspends all counting until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as an MTIM reset did not occur (TRST written to a 1 or MTIMMOD written).

Chapter 12 Modulo Timer (S08MTIMV1)

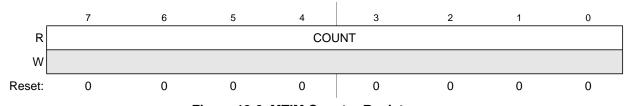

## 12.3.3 MTIM Counter Register (MTIMCNT)

MTIMCNT is the read-only value of the current MTIM count of the 8-bit counter.

Figure 12-6. MTIM Counter Register

| Field | Description                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>MTIM Count</b> — These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset clears the count to \$00. |

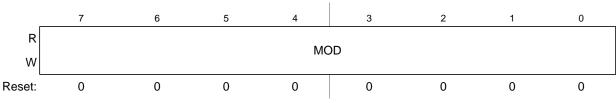

## 12.3.4 MTIM Modulo Register (MTIMMOD)

Figure 12-7. MTIM Modulo Register

#### Table 12-5. MTIM Modulo Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>MOD | <b>MTIM Modulo</b> — These eight read/write bits contain the modulo value used to reset the count and set TOF. A value of \$00 puts the MTIM in free-running mode. Writing to MTIMMOD resets the COUNT to \$00 and clears TOF. Reset sets the modulo to \$00. |

Chapter 12 Modulo Timer (S08MTIMV1)

### 12.4.1 MTIM Operation Example

This section shows an example of the MTIM operation as the counter reaches a matching value from the modulo register.

| selected<br>clock source |      |      |         |      |         |      |  |  |  |

|--------------------------|------|------|---------|------|---------|------|--|--|--|

| MTIM clock<br>(PS=%0010) |      |      | <b></b> |      | <b></b> |      |  |  |  |

| MTIMCNT                  | \$A7 | \$A8 | \$A9    | \$AA | \$00    | \$01 |  |  |  |

| TOF                      |      |      |         |      |         |      |  |  |  |

| MTIMMOD:                 | \$AA |      |         |      |         |      |  |  |  |

#### Figure 12-8. MTIM counter overfl w example

In the example of Figure 12-8, the selected clock source could be any of the five possible choices. The prescaler is set to PS = %0010 or divide-by-4. The modulo value in the MTIMMOD register is set to \$AA. When the counter, MTIMCNT, reaches the modulo value of \$AA, the counter overflows to \$00 and continues counting. The timer overflow flag, TOF, sets when the counter value changes from \$AA to \$00. An MTIM overflow interrupt is generated when TOF is set, if TOIE = 1.

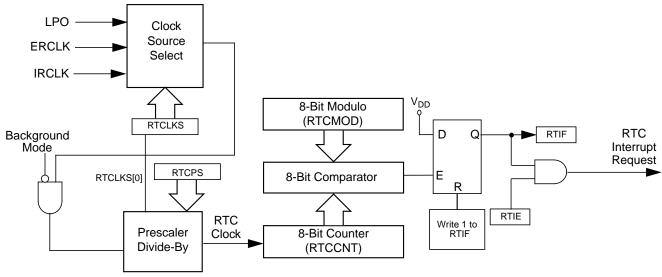

Chapter 13 Real-Time Counter (S08RTCV1)

### 13.1.3 Block Diagram

The block diagram for the RTC module is shown in Figure 13-2.

Figure 13-2. Real-Time Counter (RTC) Block Diagram

## 13.2 External Signal Description

The RTC does not include any off-chip signals.

## 13.3 Register Definitio

The RTC includes a status and control register, an 8-bit counter register, and an 8-bit modulo register.

Refer to the direct-page register summary in the memory section of this document for the absolute address assignments for all RTC registers. This section refers to registers and control bits only by their names and relative address offsets.

Table 13-1 is a summary of RTC registers.

| Name    | 7 | 6      | 5   | 4      | 3       | 2     | 1   | 0 |  |  |

|---------|---|--------|-----|--------|---------|-------|-----|---|--|--|

| RTCSC   | R | RTIF   | PTC | LKS    | RTIE    |       | PTO |   |  |  |

| KT050   | W |        |     | LING   | IXTIE   | RTCPS |     |   |  |  |

| RTCCNT  | R | RTCCNT |     |        |         |       |     |   |  |  |

|         | W |        |     |        |         |       |     |   |  |  |

| RTCMOD  | R |        |     | RTCMOD |         |       |     |   |  |  |

| KTCINOD | W |        |     |        | IXT OIV |       |     |   |  |  |

**Appendix A Electrical Characteristics**

## A.7 Supply Current Characteristics

This section includes information about power supply current in various operating modes.

| Num | с              | Parameter                                                        | Symbol                | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max <sup>2</sup> | Unit |

|-----|----------------|------------------------------------------------------------------|-----------------------|------------------------|------------------|------------------|------|

| 1   | С              | Run supply current <sup>3</sup> measured at                      |                       | 5                      | 1.1              | 1.5              |      |

|     | С              | (CPU clock = 4 MHz, $f_{Bus}$ = 2 MHz)                           | RI <sub>DD</sub>      | 3                      | 1                | 1.5              | mA   |

|     | Р              | Run supply current <sup>3</sup> measured at                      | Ы                     | 5                      | 3.9              | 5                | ^    |

| 2   | С              | (CPU clock = 16 MHz, $f_{Bus} = 8$ MHz)                          | RI <sub>DD</sub>      | 3                      | 3.9              | 5                | - mA |

| 3 – | С              | Run supply current <sup>4</sup> measured at                      | RI <sub>DD</sub>      | 5                      | 7.25             | 7.7              | mA   |

| 0   | С              | (CPU clock = 32 MHz, f <sub>Bus</sub> = 16 MHz)                  |                       | 3                      | 7.15             | 7.6              |      |

|     |                | Stop3 mode supply current                                        |                       |                        |                  |                  |      |

|     | С              | –40 °C (C & M suffix )                                           |                       |                        | 1.1              |                  |      |

|     | Р              | 25 °C (All parts)                                                |                       |                        | 1.5              | —                |      |

|     | P <sup>5</sup> | 85 °C (C suffix only )                                           |                       | 5                      | 9.0              | 26               | μA   |

| 4   | Р <sup>5</sup> | 125 °C (M suffix only)                                           | S3I <sub>DD</sub>     |                        | 45.2             | 130              |      |

|     | С              | C and M suffix –40 °C                                            |                       | 3                      | 1.0              |                  |      |

|     | С              | All parts 25 °C                                                  |                       |                        | 1.4              | —                |      |

|     | с              | C suffix only 85 °C                                              |                       |                        | 7.8              | 19               | μA   |

|     | с              | M suffix only 125 °C                                             |                       |                        | 40.1             | 95               |      |

|     |                | Stop2 mode supply current                                        |                       |                        |                  |                  | •    |

|     | с              | C and M suffix –40 °C                                            |                       |                        | 1.1              |                  |      |

|     | Р              | All parts 25 °C                                                  |                       | 5                      | 1.4              | —                | μA   |

|     | P <sup>5</sup> | C suffix only 85 °C                                              |                       |                        | 6.8              | 22               |      |

| 5   | P <sup>5</sup> | M suffix only 125 °C                                             | S2I <sub>DD</sub>     |                        | 32.7             | 99               |      |

|     | С              | C and M suffix –40 °C                                            |                       |                        | 1.0              |                  |      |

|     | С              | All parts 25 °C                                                  |                       | 3                      | 1.3              | _                | μA   |

|     | с              | C suffix only 85 °C                                              |                       |                        | 5.8              | 16               | μΑ   |

|     | с              | M suffix only 125 °C                                             |                       |                        | 28.3             | 76               |      |

| 6   | с              | RTC adder to stop2 or stop3 <sup>6</sup>                         | S23I <sub>DDRTI</sub> | 5                      | 300              | 500              | nA   |

| 0   |                |                                                                  | DDRTI                 | 3                      | 300              | 500              | nA   |

| 7   | с              | LVD adder to stop3 (LVDE = LVDSE = 1)                            | S3I <sub>DDLVD</sub>  | 5                      | 110              | 180              | μΑ   |

|     |                | ,                                                                |                       | 3                      | 90               | 160              | μΑ   |

| 8   | с              | Adder to stop3 for oscillator enabled <sup>7</sup> (EREFSTEN =1) | S3I <sub>DDOSC</sub>  | 5,<br>3                | 5                | 8                | μA   |

Table A-7. Supply Current Characteristics

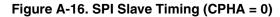

1. Not defined but normally MSB of character just received

MC9S08SH8 MCU Series Data Sheet, Rev. 3

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.

- 4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

| DIM            | MILLIM<br>MIN      | IETERS<br>MAX            | DIM   | INCHES<br>MIN MAX |         | DIM        | DIM MILLIMETERS<br>MIN MAX |            | DIM   | MI         | INCHES<br>IN MAX |  |

|----------------|--------------------|--------------------------|-------|-------------------|---------|------------|----------------------------|------------|-------|------------|------------------|--|

| А              | 24.39              | 24.99                    |       | 0.960             | 0.984   |            |                            |            |       |            |                  |  |

| В              | 6.96               | 7.49                     |       | 0.274             | 0.295   |            |                            |            |       |            |                  |  |

| С              | 3.56               | 5.08                     |       | 0.140             | 0.200   |            |                            |            |       |            |                  |  |

| D              | 0.38               | 0.56                     |       | 0.015             | 0.022   |            |                            |            |       |            |                  |  |

| E 1.27 BSC     |                    |                          | 0.05  | 0 BSC             |         |            |                            |            |       |            |                  |  |

| F              | 1.14               | 1.52                     |       | 0.045             | 0.060   |            |                            |            |       |            |                  |  |

| G              | G 2.54 BSC 0.10    |                          | 0 BSC |                   |         |            |                            |            |       |            |                  |  |

| J              | 0.20               | 0.38                     |       | 0.008             | 0.015   |            |                            |            |       |            |                  |  |

| К              | 2.79               | 3.76                     |       | 0.110             | 0.148   |            |                            |            |       |            |                  |  |

| L              | L 7.62 BSC 0.30    |                          | 0.300 | ) BSC             |         |            |                            |            |       |            |                  |  |

| М              | 0.                 | 15 <b>.</b>              |       | 0.                | 0' 15'  |            |                            |            |       |            |                  |  |

| N              | 0.50               | 1.01                     |       | 0.020             | 0.040   |            |                            |            |       |            |                  |  |

| R              | •••••              | 1.29                     |       |                   | 0.051   |            |                            |            |       |            |                  |  |

|                |                    |                          |       |                   |         |            |                            | l          |       |            |                  |  |

| 0              | FREESCALE<br>ALL R | SEMICONDUC<br>Ights rese |       | NC.               | MECHANI | CAL        | OUTLINE                    | PRINT      | VERS] | [ON NO     | T TO SCALE       |  |

| TITL           | TITLE:             |                          |       |                   |         | I          | DOCUMENT NO                | ]: 98ASB42 | 28991 | 3          | REV: B           |  |

| 20LD .300 PDIP |                    |                          |       |                   | C       | ASE NUMBER | R: 738C-01                 |            |       | 24 MAY 200 | 15               |  |

|                |                    |                          |       |                   |         | S          | STANDARD: NE               | IN-JEDEC   |       |            |                  |  |

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2006-2008. All rights reserved.