Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | 12V1                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 40                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                            |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g128f0clfr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Device Overview MC9S12G-Family

- Interrupt flag register for pin interrupts on ports P, J and AD

- Control register to configure  $\overline{IRQ}$  pin operation

- Routing register to support programmable signal redirection in 20 TSSOP only

- Routing register to support programmable signal redirection in 100 LQFP package only

- Package code register preset by factory related to package in use, writable once after reset. Also includes bit to reprogram routing of API\_EXTCLK in all packages.

- Control register for free-running clock outputs

- •

## 1.3.5 Main External Oscillator (XOSCLCP)

- Loop control Pierce oscillator using a 4 MHz to 16 MHz crystal

- Current gain control on amplitude output

- Signal with low harmonic distortion

- Low power

- Good noise immunity

- Eliminates need for external current limiting resistor

- Transconductance sized for optimum start-up margin for typical crystals

- Oscillator pins can be shared w/ GPIO functionality

### 1.3.6 Internal RC Oscillator (IRC)

- Trimmable internal reference clock.

- Frequency: 1 MHz

- Trimmed accuracy over  $-40^{\circ}$ C to  $+125^{\circ}$ C ambient temperature range:  $\pm 1.0\%$  for temperature option C and V (see Table A-4)

- $\pm 1.3\%$  for temperature option M (see Table A-4)

## 1.3.7 Internal Phase-Locked Loop (IPLL)

- Phase-locked-loop clock frequency multiplier

- No external components required

- Reference divider and multiplier allow large variety of clock rates

- Automatic bandwidth control mode for low-jitter operation

- Automatic frequency lock detector

- Configurable option to spread spectrum for reduced EMC radiation (frequency modulation)

- Reference clock sources:

- External 4–16 MHz resonator/crystal (XOSCLCP)

- Internal 1 MHz RC oscillator (IRC)

**Device Overview MC9S12G-Family**

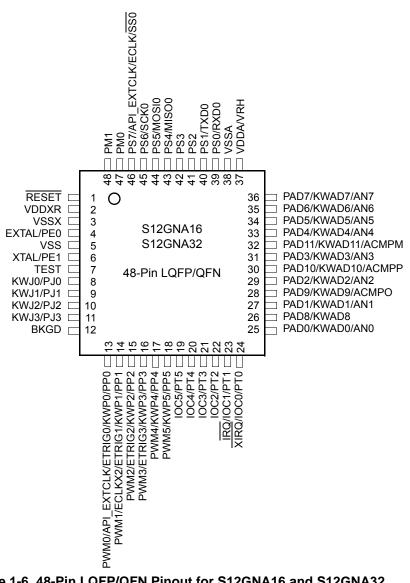

#### 1.8.2 S12GNA16 and S12GNA32

#### 1.8.2.1 Pinout 48-Pin LQFP/QFN

Figure 1-6. 48-Pin LQFP/QFN Pinout for S12GNA16 and S12GNA32

|             | Function<br><lowestpriorityhighest></lowestpriorityhighest> |              |              |             |             |                  | Internal P<br>Resisto |                |

|-------------|-------------------------------------------------------------|--------------|--------------|-------------|-------------|------------------|-----------------------|----------------|

| Package Pin | Pin                                                         | 2nd<br>Func. | 3rd<br>Func. | 4th<br>Func | 5th<br>Func | Supply           | CTRL                  | Reset<br>State |

| 1           | RESET                                                       |              |              | _           | —           | V <sub>DDX</sub> | PULLUP                |                |

# Chapter 5 S12G Memory Map Controller (S12GMMCV1)

| _ | ev. No.<br>m No.) | Date<br>(Submitted By) | Sections<br>Affected | Substantial Change(s)           |

|---|-------------------|------------------------|----------------------|---------------------------------|

| 0 | 1.02              | 20-May 2010            |                      | Updates for S12VR48 and S12VR64 |

### 5.1 Introduction

The S12GMMC module controls the access to all internal memories and peripherals for the CPU12 and S12SBDM module. It regulates access priorities and determines the address mapping of the on-chip resources. Figure 5-1 shows a block diagram of the S12GMMC module.

## 5.1.1 Glossary

| Term                         | Definition                                                   |

|------------------------------|--------------------------------------------------------------|

| Local Addresses              | Address within the CPU12's Local Address Map (Figure 5-11)   |

| Global Address               | Address within the Global Address Map (Figure 5-11)          |

| Aligned Bus Access           | Bus access to an even address.                               |

| Misaligned Bus Access        | Bus access to an odd address.                                |

| NS                           | Normal Single-Chip Mode                                      |

| SS                           | Special Single-Chip Mode                                     |

| Unimplemented Address Ranges | Address ranges which are not mapped to any on-chip resource. |

| NVM                          | Non-volatile Memory; Flash or EEPROM                         |

| IFR                          | NVM Information Row. Refer to FTMRG Block Guide              |

### Table 5-2. Glossary Of Terms

## 5.1.2 Overview

The S12GMMC connects the CPU12's and the S12SBDM's bus interfaces to the MCU's on-chip resources (memories and peripherals). It arbitrates the bus accesses and determines all of the MCU's memory maps. Furthermore, the S12GMMC is responsible for constraining memory accesses on secured devices and for selecting the MCU's functional mode.

• The Internal Reference Clock (IRC1M) provides a1MHz clock.

## 10.1.1 Features

The Pierce Oscillator (XOSCLCP) contains circuitry to dynamically control current gain in the output amplitude. This ensures a signal with low harmonic distortion, low power and good noise immunity.

- Supports quartz crystals or ceramic resonators from 4MHz to 16MHz.

- High noise immunity due to input hysteresis and spike filtering.

- Low RF emissions with peak-to-peak swing limited dynamically

- Transconductance (gm) sized for optimum start-up margin for typical crystals

- Dynamic gain control eliminates the need for external current limiting resistor

- Integrated resistor eliminates the need for external bias resistor.

- Low power consumption: Operates from internal 1.8V (nominal) supply, Amplitude control limits power

The Voltage Regulator (IVREG) has the following features:

- Input voltage range from 3.13V to 5.5V

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR)

- Low-voltage reset (LVR)

The Phase Locked Loop (PLL) has the following features:

- highly accurate and phase locked frequency multiplier

- Configurable internal filter for best stability and lock time.

- Frequency modulation for defined jitter and reduced emission

- Automatic frequency lock detector

- Interrupt request on entry or exit from locked condition

- Reference clock either external (crystal) or internal square wave (1MHz IRC1M) based.

- PLL stability is sufficient for LIN communication, even if using IRC1M as reference clock

The Internal Reference Clock (IRC1M) has the following features:

- Frequency trimming

- (A factory trim value for 1MHz is loaded from Flash Memory into the IRCTRIM register after reset, which can be overwritten by application if required)

- Temperature Coefficient (TC) trimming. (A factory trim value is loaded from Flash Memory into the IRCTRIM register to turned off TC trimming after reset. Application can trim the TC if required by overwriting the IRCTRIM register).

•

Other features of the S12CPMU include

• Clock monitor to detect loss of crystal

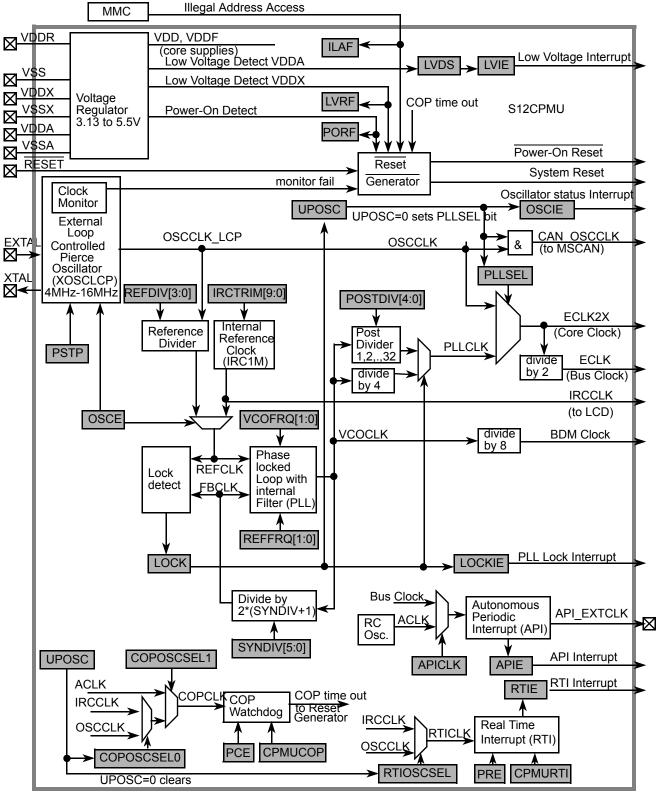

# 10.1.3 S12CPMU Block Diagram

Figure 10-1. Block diagram of S12CPMU

S12 Clock, Reset and Power Management Unit (S12CPMU)

# 10.6 Interrupts

The interrupt/reset vectors requested by the S12CPMU are listed in Table 10-29. Refer to MCU specification for related vector addresses and priorities.

| Interrupt Source                   | CCR<br>Mask | Local Enable      |

|------------------------------------|-------------|-------------------|

| RTI time-out interrupt             | l bit       | CPMUINT (RTIE)    |

| PLL lock interrupt                 | I bit       | CPMUINT (LOCKIE)  |

| Oscillator status<br>interrupt     | l bit       | CPMUINT (OSCIE)   |

| Low voltage interrupt              | I bit       | CPMULVCTL (LVIE)  |

| Autonomous<br>Periodical Interrupt | l bit       | CPMUAPICTL (APIE) |

Table 10-29. S12CPMU Interrupt Vectors

## **10.6.1** Description of Interrupt Operation

### 10.6.1.1 Real Time Interrupt (RTI)

The clock source for the RTI is either IRCCLK or OSCCLK depending on the setting of the RTIOSCSEL bit. In Stop Mode with PSTP=1 (Pseudo Stop Mode), RTIOSCSEL=1 and PRE=1 the RTI continues to run, else the RTI counter halts in Stop Mode.

The RTI can be used to generate hardware interrupts at a fixed periodic rate. If enabled (by setting RTIE=1), this interrupt will occur at the rate selected by the CPMURTI register. At the end of the RTI time-out period the RTIF flag is set to one and a new RTI time-out period starts immediately.

A write to the CPMURTI register restarts the RTI time-out period.

### 10.6.1.2 PLL Lock Interrupt

The S12CPMU generates a PLL Lock interrupt when the lock condition (LOCK status bit) of the PLL changes, either from a locked state to an unlocked state or vice versa. Lock interrupts are locally disabled by setting the LOCKIE bit to zero. The PLL Lock interrupt flag (LOCKIF) is set to 1 when the lock condition has changed, and is cleared to 0 by writing a 1 to the LOCKIF bit.

### 10.6.1.3 Oscillator Status Interrupt

When the OSCE bit is 0, then UPOSC stays 0. When OSCE = 1 the UPOSC bit is set after the LOCK bit is set.

Upon detection of a status change (UPOSC) the OSCIF flag is set. Going into Full Stop Mode or disabling the oscillator can also cause a status change of UPOSC.

#### Analog-to-Digital Converter (ADC10B8CV2)

| Address | Name               |             | Bit 7                                                                                                                            | 6                                                                                                                                                                                                 | 5            | 4             | 3               | 2             | 1      | Bit 0 |

|---------|--------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|-----------------|---------------|--------|-------|

| 0x0003  | ATDCTL3            | R<br>W      | DJM                                                                                                                              | S8C                                                                                                                                                                                               | S4C          | S2C           | S1C             | FIFO          | FRZ1   | FRZ0  |

| 0x0004  | ATDCTL4            | R<br>W      | SMP2                                                                                                                             | SMP1                                                                                                                                                                                              | SMP0         |               |                 | PRS[4:0]      |        |       |

| 0x0005  | ATDCTL5            | R<br>W      | 0                                                                                                                                | SC                                                                                                                                                                                                | SCAN         | MULT          | CD              | СС            | СВ     | CA    |

| 0x0006  | ATDSTAT0           | R<br>W      | SCF                                                                                                                              | 0                                                                                                                                                                                                 | ETORF        | FIFOR         | CC3             | CC2           | CC1    | CC0   |

| 0x0007  | Unimple-<br>mented | R<br>W      | 0                                                                                                                                | 0                                                                                                                                                                                                 | 0            | 0             | 0               | 0             | 0      | 0     |

| 0x0008  | ATDCMPEH           | R<br>W      | 0                                                                                                                                | 0                                                                                                                                                                                                 | 0            | 0             | 0               | 0             | 0      | 0     |

| 0x0009  | ATDCMPEL           | R<br>W      |                                                                                                                                  |                                                                                                                                                                                                   |              | СМ            | PE[7:0]         |               |        |       |

| 0x000A  | ATDSTAT2H          | R<br>W      | 0                                                                                                                                | 0                                                                                                                                                                                                 | 0            | 0             | 0               | 0             | 0      | 0     |

| 0x000B  | ATDSTAT2L          | R           |                                                                                                                                  |                                                                                                                                                                                                   |              | CC            | CF[7:0]         |               |        |       |

| 0x000C  | ATDDIENH           | W<br>R<br>W | 1                                                                                                                                | 1                                                                                                                                                                                                 | 1            | 1             | 1               | 1             | 1      | 1     |

| 0x000D  | ATDDIENL           | R<br>W      | IEN[7:0]                                                                                                                         |                                                                                                                                                                                                   |              |               |                 |               |        |       |

| 0x000E  | ATDCMPHTH          | R<br>W      | 0                                                                                                                                | 0                                                                                                                                                                                                 | 0            | 0             | 0               | 0             | 0      | 0     |

| 0x000F  | ATDCMPHTL          | R<br>W      | CMPHT[7:0]                                                                                                                       |                                                                                                                                                                                                   |              |               |                 |               |        |       |

| 0x0010  | ATDDR0             | R<br>W      |                                                                                                                                  | See Section 11.3.2.12.1, "Left Justified Result Data (DJM=0)"<br>and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)"                                                                   |              |               |                 |               |        |       |

| 0x0012  | ATDDR1             | R<br>W      |                                                                                                                                  | See Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)"<br>and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)"                                                                  |              |               |                 |               |        |       |

| 0x0014  | ATDDR2             | R<br>W      |                                                                                                                                  | See S                                                                                                                                                                                             | Section 11.3 | .2.12.1, "Let | ft Justified Re | esult Data (D | JM=0)" |       |

| 0x0016  | ATDDR3             | R<br>W      |                                                                                                                                  | and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)"<br>See Section 11.3.2.12.1, "Left Justified Result Data (DJM=0)"<br>and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)" |              |               |                 |               |        |       |

| 0x0018  | ATDDR4             | R<br>W      | See Section 11.3.2.12.2, "Right Justified Result Data (DJM=0)"<br>and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)" |                                                                                                                                                                                                   |              |               |                 |               |        |       |

| 0x001A  | ATDDR5             | R<br>W      | See Section 11.3.2.12.2, "Left Justified Result Data (DJM=0)"<br>and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)"  |                                                                                                                                                                                                   |              |               |                 |               |        |       |

| 0x001C  | ATDDR6             | R<br>W      | See Section 11.3.2.12.2, "Left Justified Result Data (DJM=0)"<br>and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)"  |                                                                                                                                                                                                   |              |               |                 |               |        |       |

| 0x001E  | ATDDR7             | R<br>W      | See Section 11.3.2.12.2, "Left Justified Result Data (DJM=0)"<br>and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)"  |                                                                                                                                                                                                   |              |               |                 |               |        |       |

| 0x0020- | Unimple-           | R           | 0                                                                                                                                | 0                                                                                                                                                                                                 | 0            | 0             | 0               | 0             | 0      | 0     |

| 0x002F  | mented             | W           |                                                                                                                                  |                                                                                                                                                                                                   | mented or R  |               |                 |               |        |       |

= Unimplemented or Reserved

Figure 11-2. ADC10B8C Register Summary (Sheet 2 of 2)

Analog-to-Digital Converter (ADC10B16CV2)

## 15.3.2 Register Descriptions

This section describes in address order all the ADC10B16C registers and their individual bits.

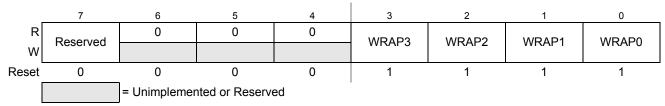

### 15.3.2.1 ATD Control Register 0 (ATDCTL0)

Writes to this register will abort current conversion sequence.

Module Base + 0x0000

### Figure 15-3. ATD Control Register 0 (ATDCTL0)

### Read: Anytime

Write: Anytime, in special modes always write 0 to Reserved Bit 7.

| Field            | Description                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                                                                         |

| 3-0<br>WRAP[3-0] | <b>Wrap Around Channel Select Bits</b> — These bits determine the channel for wrap around when doing multi-channel conversions. The coding is summarized in Table 15-2. |

### Table 15-2. Multi-Channel Wrap Around Coding

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1)<br>Wraparound to AN0 after Converting |

|-------|-------|-------|-------|-------------------------------------------------------------------------------|

| 0     | 0     | 0     | 0     | Reserved <sup>1</sup>                                                         |

| 0     | 0     | 0     | 1     | AN1                                                                           |

| 0     | 0     | 1     | 0     | AN2                                                                           |

| 0     | 0     | 1     | 1     | AN3                                                                           |

| 0     | 1     | 0     | 0     | AN4                                                                           |

| 0     | 1     | 0     | 1     | AN5                                                                           |

| 0     | 1     | 1     | 0     | AN6                                                                           |

| 0     | 1     | 1     | 1     | AN7                                                                           |

| 1     | 0     | 0     | 0     | AN8                                                                           |

| 1     | 0     | 0     | 1     | AN9                                                                           |

| 1     | 0     | 1     | 0     | AN10                                                                          |

| 1     | 0     | 1     | 1     | AN11                                                                          |

| 1     | 1     | 0     | 0     | AN12                                                                          |

| 1     | 1     | 0     | 1     | AN13                                                                          |

| 1     | 1     | 1     | 0     | AN14                                                                          |

| 1     | 1     | 1     | 1     | AN15                                                                          |

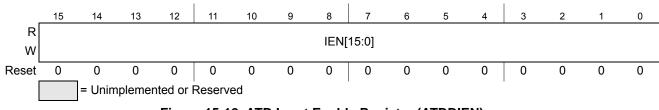

## 15.3.2.10 ATD Input Enable Register (ATDDIEN)

Module Base + 0x000C

Figure 15-12. ATD Input Enable Register (ATDDIEN)

### Read: Anytime

Write: Anytime

### Table 15-19. ATDDIEN Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>IEN[15:0] | <ul> <li>ATD Digital Input Enable on channel x (x= 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) — This bit controls the digital input buffer from the analog input pin (ANx) to the digital data register.</li> <li>0 Disable digital input buffer to ANx pin</li> <li>1 Enable digital input buffer on ANx pin.</li> <li>Note: Setting this bit will enable the corresponding digital input buffer continuously. If this bit is set while simultaneously using it as an analog port, there is potentially increased power consumption because the digital input buffer maybe in the linear region.</li> </ul> |

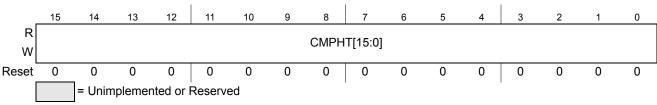

## 15.3.2.11 ATD Compare Higher Than Register (ATDCMPHT)

Writes to this register will abort current conversion sequence.

### Read: Anytime

Write: Anytime

Module Base + 0x000E

Figure 15-13. ATD Compare Higher Than Register (ATDCMPHT)

### Table 15-20. ATDCMPHT Field Descriptions

| Field       | Description                                                                                                                   |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 15–0        | Compare Operation Higher Than Enable for conversion number <i>n</i> ( <i>n</i> = 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5,       |  |  |  |  |

| CMPHT[15:0] | 4, 3, 2, 1, 0) of a Sequence ( <i>n conversion number, NOT channel number!</i> ) — This bit selects the operator              |  |  |  |  |

|             | for comparison of conversion results.                                                                                         |  |  |  |  |

|             | 0 If result of conversion <i>n</i> is <b>lower or same than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2 |  |  |  |  |

|             | 1 If result of conversion <i>n</i> is <b>higher than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2        |  |  |  |  |

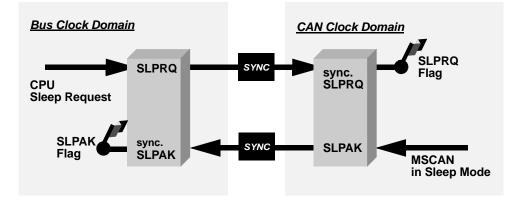

## 18.4.5.5 MSCAN Sleep Mode

The CPU can request the MSCAN to enter this low power mode by asserting the SLPRQ bit in the CANCTL0 register. The time when the MSCAN enters sleep mode depends on a fixed synchronization delay and its current activity:

- If there are one or more message buffers scheduled for transmission (TXEx = 0), the MSCAN will continue to transmit until all transmit message buffers are empty (TXEx = 1, transmitted successfully or aborted) and then goes into sleep mode.

- If the MSCAN is receiving, it continues to receive and goes into sleep mode as soon as the CAN bus next becomes idle.

- If the MSCAN is neither transmitting nor receiving, it immediately goes into sleep mode.

Figure 18-46. Sleep Request / Acknowledge Cycle

### NOTE

The application software must avoid setting up a transmission (by clearing one or more TXEx flag(s)) and immediately request sleep mode (by setting SLPRQ). Whether the MSCAN starts transmitting or goes into sleep mode directly depends on the exact sequence of operations.

If sleep mode is active, the SLPRQ and SLPAK bits are set (Figure 18-46). The application software must use SLPAK as a handshake indication for the request (SLPRQ) to go into sleep mode.

When in sleep mode (SLPRQ = 1 and SLPAK = 1), the MSCAN stops its internal clocks. However, clocks that allow register accesses from the CPU side continue to run.

If the MSCAN is in bus-off state, it stops counting the 128 occurrences of 11 consecutive recessive bits due to the stopped clocks. TXCAN remains in a recessive state. If RXF = 1, the message can be read and RXF can be cleared. Shifting a new message into the foreground buffer of the receiver FIFO (RxFG) does not take place while in sleep mode.

It is possible to access the transmit buffers and to clear the associated TXE flags. No message abort takes place while in sleep mode.

#### Serial Peripheral Interface (S12SPIV5)

A half SCK cycle later, the second edge appears on the SCK pin. This is the latching edge for both the master and slave.

When the third edge occurs, the value previously latched from the serial data input pin is shifted into the LSB or MSB of the SPI shift register, depending on LSBFE bit. After this edge, the next bit of the master data is coupled out of the serial data output pin of the master to the serial input pin on the slave.

This process continues for a total of  $n^1$  edges on the SCK line with data being latched on even numbered edges and shifting taking place on odd numbered edges.

Data reception is double buffered, data is serially shifted into the SPI shift register during the transfer and is transferred to the parallel SPI data register after the last bit is shifted in.

After 2n<sup>1</sup> SCK edges:

- Data that was previously in the SPI data register of the master is now in the data register of the slave, and data that was in the data register of the slave is in the master.

- The SPIF flag bit in SPISR is set indicating that the transfer is complete.

Figure 21-14 shows two clocking variations for CPHA = 1. The diagram may be interpreted as a master or slave timing diagram because the SCK, MISO, and MOSI pins are connected directly between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The  $\overline{SS}$  pin of the master must be either high or reconfigured as a general-purpose output not affecting the SPI.

#### 16 KByte Flash Module (S12FTMRG16K1V1)

All bits in the FRSV6 register read 0 and are not writable.

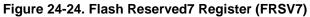

### 24.3.2.19 Flash Reserved7 Register (FRSV7)

This Flash register is reserved for factory testing.

All bits in the FRSV7 register read 0 and are not writable.

#### 16 KByte Flash Module (S12FTMRG16K1V1)

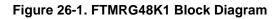

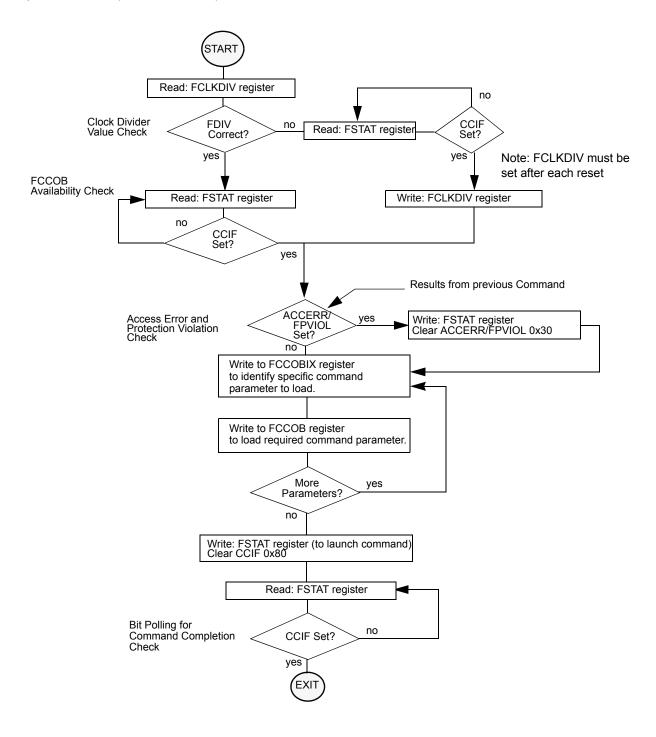

Figure 24-25. Generic Flash Command Write Sequence Flowchart

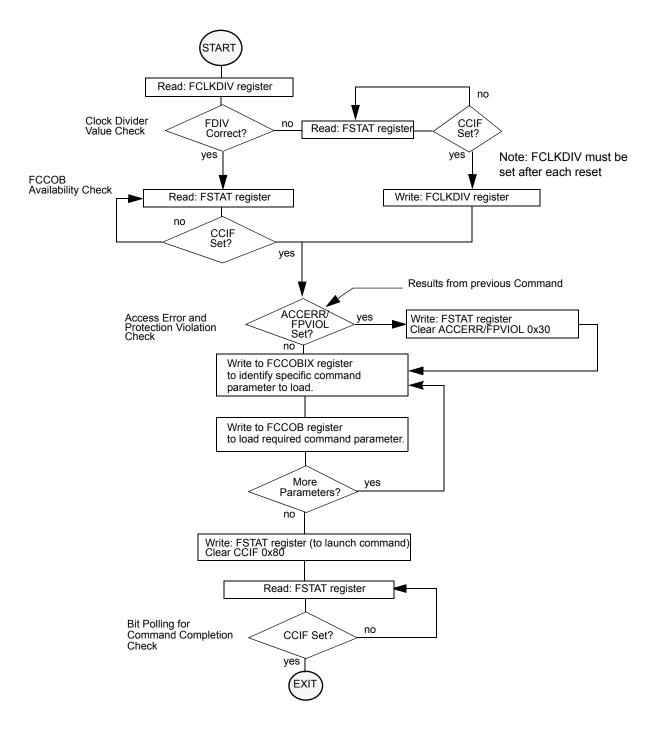

48 KByte Flash Module (S12FTMRG48K1V1)

## 26.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 26-1.

## 26.2 External Signal Description

The Flash module contains no signals that connect off-chip.

## 27.4.6.2 Erase Verify Block Command

The Erase Verify Block command allows the user to verify that an entire P-Flash or EEPROM block has been erased. The FCCOB FlashBlockSelectionCode[1:0] bits determine which block must be verified.

Table 27-33. Erase Verify Block Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |                                                         |  |  |

|-------------|------------------|---------------------------------------------------------|--|--|

| 000         | 0x02             | Flash block<br>selection code [1:0]. See<br>Table 27-34 |  |  |

### Table 27-34. Flash block selection code description

| Selection code[1:0] | Flash block to be verified |

|---------------------|----------------------------|

| 00                  | EEPROM                     |

| 01                  | Invalid (ACCERR)           |

| 10                  | Invalid (ACCERR)           |

| 11                  | P-Flash                    |

Upon clearing CCIF to launch the Erase Verify Block command, the Memory Controller will verify that the selected P-Flash or EEPROM block is erased. The CCIF flag will set after the Erase Verify Block operation has completed. If the block is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 27-35. Erase Verify Block Command Error Handling

| Register | Error Bit | Error Condition                                                                                   |

|----------|-----------|---------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                       |

|          |           | Set if an invalid FlashBlockSelectionCode[1:0] is supplied                                        |

| FSTAT    | FPVIOL    | None                                                                                              |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |

## 27.4.6.3 Erase Verify P-Flash Section Command

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases.

# Chapter 28 96 KByte Flash Module (S12FTMRG96K1V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected                                                                          | Description of Changes                                                                            |

|--------------------|------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| V01.04             | 17 Jun 2010      | 28.4.6.1/28-100<br>2<br>28.4.6.2/28-100<br>3<br>28.4.6.3/28-100<br>4<br>28.4.6.14/28-10<br>13 | Clarify Erase Verify Commands Descriptions related to the bits MGSTAT[1:0] of the register FSTAT. |

| V01.05             | 20 aug 2010      | 28.4.6.2/28-100<br>3<br>28.4.6.12/28-10<br>10<br>28.4.6.13/28-10<br>12                        | Updated description of the commands RD1BLK, MLOADU and MLOADF                                     |

| Rev.1.27           | 31 Jan 2011      | 28.3.2.9/28-985                                                                               | Updated description of protection on Section 28.3.2.9                                             |

### Table 28-1. Revision History

# 28.1 Introduction

The FTMRG96K1 module implements the following:

- 96Kbytes of P-Flash (Program Flash) memory

- 3 Kbytes of EEPROM memory

The Flash memory is ideal for single-supply applications allowing for field reprogramming without requiring external high voltage sources for program or erase operations. The Flash module includes a memory controller that executes commands to modify Flash memory contents. The user interface to the memory controller consists of the indexed Flash Common Command Object (FCCOB) register which is written to with the command, global address, data, and any required command parameters. The memory controller must complete the execution of a command before the FCCOB register can be written to with a new command.

### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

#### 96 KByte Flash Module (S12FTMRG96K1V1)

Figure 28-26. Generic Flash Command Write Sequence Flowchart

#### 96 KByte Flash Module (S12FTMRG96K1V1)

| Field              | Description                                                                                                                                                                                                                                                                                     |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                            |

| 2<br>RSVD          | Reserved Bit — This bit is reserved and always reads 0.                                                                                                                                                                                                                                         |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 29.4.6, "Flash Command Description," and Section 29.6, "Initialization" for details. |

#### Table 29-15. FSTAT Field Descriptions (continued)

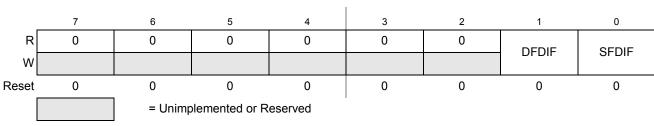

### 29.3.2.8 Flash Error Status Register (FERSTAT)

Offset Module Base + 0x0007

The FERSTAT register reflects the error status of internal Flash operations.

### Figure 29-12. Flash Error Status Register (FERSTAT)

All flags in the FERSTAT register are readable and only writable to clear the flag.

#### Table 29-16. FERSTAT Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIF | <ul> <li>Double Bit Fault Detect Interrupt Flag — The setting of the DFDIF flag indicates that a double bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The DFDIF flag is cleared by writing a 1 to DFDIF. Writing a 0 to DFDIF has no effect on DFDIF.<sup>2</sup></li> <li>0 No double bit fault detected</li> <li>1 Double bit fault detected or a Flash array read operation returning invalid data was attempted while command running</li> </ul>                                                                        |

| 0<br>SFDIF | <ul> <li>Single Bit Fault Detect Interrupt Flag — With the IGNSF bit in the FCNFG register clear, the SFDIF flag indicates that a single bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The SFDIF flag is cleared by writing a 1 to SFDIF. Writing a 0 to SFDIF has no effect on SFDIF.</li> <li>0 No single bit fault detected</li> <li>1 Single bit fault detected and corrected or a Flash array read operation returning invalid data was attempted operation returning invalid data was attempted operation.</li> </ul> |

The single bit fault and double bit fault flags are mutually exclusive for parity errors (an ECC fault occurrence can be either single fault or double fault but never both). A simultaneous access collision (Flash array read operation returning invalid data attempted while command running) is indicated when both SFDIF and DFDIF flags are high.

<sup>2</sup> There is a one cycle delay in storing the ECC DFDIF and SFDIF fault flags in this register. At least one NOP is required after a flash memory read before checking FERSTAT for the occurrence of ECC errors.

# A.12 Electrical Specification for Voltage Regulator

| Num | С | Characteristic                                                                                                                                                                                                                                                                                                                       | Symbol                                 | Min          | Typical      | Мах          | Unit   |

|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|--------------|--------------|--------|

| 1   | Р | Input Voltages                                                                                                                                                                                                                                                                                                                       | V <sub>VDDR,A</sub>                    | 3.13         | _            | 5.5          | V      |

| 2   | Ρ | V <sub>DDA</sub> Low Voltage Interrupt Assert Level <sup>1</sup><br>V <sub>DDA</sub> Low Voltage Interrupt Deassert Level                                                                                                                                                                                                            | V <sub>LVIA</sub><br>V <sub>LVID</sub> | 4.04<br>4.19 | 4.23<br>4.38 | 4.40<br>4.49 | V<br>V |

| 3   | Р | V <sub>DDX</sub> Low Voltage Reset Deassert <sup>2 3 4</sup>                                                                                                                                                                                                                                                                         | V <sub>LVRXD</sub>                     | —            | 3.05         | 3.13         | V      |

| 4   | Р | V <sub>DDX</sub> Low Voltage Reset Assert <sup>2 3 4</sup>                                                                                                                                                                                                                                                                           | V <sub>LVRXA</sub>                     | 2.95         | 3.02         | _            | V      |

| 5   | Т | CPMU ACLK frequency<br>(CPMUACLKTR[5:0] = %000000)                                                                                                                                                                                                                                                                                   | f <sub>ACLK</sub>                      | _            | 10           | _            | KHz    |

| 6   | С | Trimmed ACLK internal clock <sup>5</sup> $\Delta f$ / f <sub>nominal</sub>                                                                                                                                                                                                                                                           | df <sub>ACLK</sub>                     | - 5%         | _            | + 5%         | —      |

| 7   | D | The first period after enabling the counter<br>by APIFE might be reduced by ACLK start<br>up delay                                                                                                                                                                                                                                   | t <sub>sdel</sub>                      | _            | _            | 100          | us     |

| 8   | D | The first period after enabling the COP might be reduced by ACLK start up delay                                                                                                                                                                                                                                                      | t <sub>sdel</sub>                      |              | _            | 100          | us     |

| 9   | Ρ | Output Voltage Flash<br>Full Performance Mode<br>Reduced Power Mode (MCU STOP<br>mode)                                                                                                                                                                                                                                               | V <sub>DDF</sub>                       | 2.6<br>1.1   | 2.82<br>1.6  | 2.9<br>1.98  | V<br>V |

| 10  | С | $\begin{array}{c c} V_{DDF} \text{ Voltage Distribution} \\ \text{over input voltage } V_{DDA}{}^6 \\ 4.5V \leq V_{DDA} \leq 5.5V, \ T_A = 27^{o}C \\ \text{compared to } V_{DDA} = 5.0V \end{array} \qquad $ |                                        | 5            | mV           |              |        |

| 11  | С | $\begin{array}{l} V_{DDF} \text{ Voltage Distribution} \\ \text{over ambient temperature } T_A \\ V_{DDA} = 5V, -40^\circ\text{C} \leq T_A \leq 125^\circ\text{C} \\ \text{compared to } V_{DDF} \text{ production test value} \\ \text{(see A.16, "ADC Conversion Result} \\ \text{Reference")} \end{array}$                        | $\Delta_{VDDF}$                        | -20          | -            | +20          | mV     |

### Table A-47. Voltage Regulator Characteristics (Junction Temperature From –40°C To +150°C)

<sup>1</sup> Monitors VDDA, active only in Full Performance Mode. Indicates I/O & ADC performance degradation due to low supply voltage.

<sup>2</sup> Device functionality is guaranteed on power down to the LVR assert level

<sup>3</sup> Monitors VDDX, active only in Full Performance Mode. MCU is monitored by the POR in RPM (see Figure A-6)

$^{4}$  V<sub>LVRXA</sub> < V<sub>LVRXD</sub>. The hysteresis is unspecified and untested.

<sup>5</sup> The ACLK Trimming CPMUACLKTR[5:0] bits must be set so that f<sub>ACLK</sub>=10KHz.

<sup>6</sup> VDDR  $\geq$  3.13V