Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 40                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g128f0mlf |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 13.2 | Signal Description                  | 459 |

|------|-------------------------------------|-----|

|      | 13.2.1 Detailed Signal Descriptions | 459 |

| 13.3 | Memory Map and Register Definition  | 459 |

|      | 13.3.1 Module Memory Map            | 459 |

|      | 13.3.2 Register Descriptions        | 462 |

| 13.4 | Functional Description              | 477 |

|      | 13.4.1 Analog Sub-Block             | 477 |

|      | 13.4.2 Digital Sub-Block            | 477 |

| 13.5 | Resets                              | 479 |

| 13.6 | Interrupts                          | 479 |

# Chapter 14 Analog-to-Digital Converter (ADC12B12CV2)

| 14.1 | Introduction                        | 482 |

|------|-------------------------------------|-----|

|      | 14.1.1 Features                     | 482 |

|      | 14.1.2 Modes of Operation           | 483 |

|      | 14.1.3 Block Diagram                | 484 |

| 14.2 | Signal Description                  | 485 |

|      | 14.2.1 Detailed Signal Descriptions | 485 |

| 14.3 | Memory Map and Register Definition  | 485 |

|      | 14.3.1 Module Memory Map            | 485 |

|      | 14.3.2 Register Descriptions        |     |

| 14.4 | Functional Description              | 504 |

|      | 14.4.1 Analog Sub-Block             |     |

|      | 14.4.2 Digital Sub-Block            |     |

| 14.5 | Resets                              | 506 |

| 14.6 | Interrupts                          | 506 |

# Chapter 15

# Analog-to-Digital Converter (ADC10B16CV2)

| Introduction                       | 508                                                                                                                                                                                                                                                                                |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.1 Features                    | 508                                                                                                                                                                                                                                                                                |

| 15.1.2 Modes of Operation          | 509                                                                                                                                                                                                                                                                                |

| 15.1.3 Block Diagram               | 510                                                                                                                                                                                                                                                                                |

| Signal Description                 | 511                                                                                                                                                                                                                                                                                |

|                                    |                                                                                                                                                                                                                                                                                    |

| Memory Map and Register Definition | 511                                                                                                                                                                                                                                                                                |

| 15.3.1 Module Memory Map           | 511                                                                                                                                                                                                                                                                                |

| 15.3.2 Register Descriptions       | 514                                                                                                                                                                                                                                                                                |

| Functional Description             | 529                                                                                                                                                                                                                                                                                |

| 15.4.1 Analog Sub-Block            | 529                                                                                                                                                                                                                                                                                |

| 15.4.2 Digital Sub-Block           | 529                                                                                                                                                                                                                                                                                |

| Resets                             | 531                                                                                                                                                                                                                                                                                |

| Interrupts                         | 531                                                                                                                                                                                                                                                                                |

|                                    | 15.1.1 Features15.1.2 Modes of Operation15.1.3 Block DiagramSignal Description15.2.1 Detailed Signal DescriptionsMemory Map and Register Definition15.3.1 Module Memory Map15.3.2 Register DescriptionsFunctional Description15.4.1 Analog Sub-Block15.4.2 Digital Sub-BlockResets |

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Port AD general-purpose input/output data</b> —Data Register<br>When not used with an alternative signal, the associated pin can be used as general-purpose I/O. In general-purpose<br>output mode the port data register bit value is driven to the pin.<br>If the associated data direction bit is set to 1, a read returns the value of the port data register bit, otherwise the<br>buffered pin input state is read if the digital input buffers are enabled (Section 2.3.12, "Pins AD15-0"). |

#### Table 2-76. PT1AD Register Field Descriptions

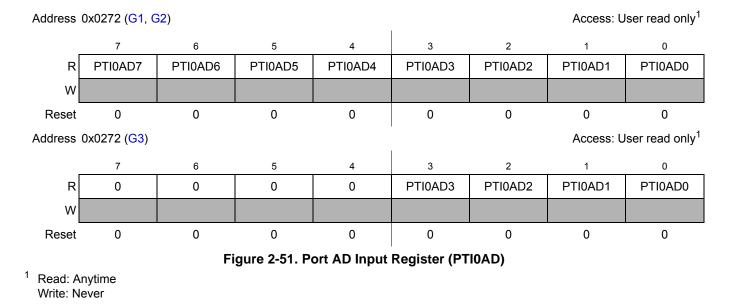

## 2.4.3.51 Port AD Input Register (PTI0AD)

#### Table 2-77. PTI0AD Register Field Descriptions

| Field  | Description                                                                                                                                                                        |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTI0AD | <b>Port AD input data</b> —<br>A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

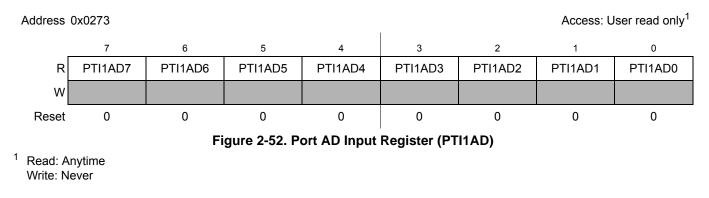

# 2.4.3.52 Port AD Input Register (PTI1AD)

MC9S12G Family Reference Manual Rev.1.27

# Chapter 6 Interrupt Module (S12SINTV1)

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                                                                                                                                    |

|-------------------|------------------|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01.02             | 13 Sep<br>2007   |                   |        | updates for S12P family devices:<br>- re-added XIRQ and IRQ references since this functionality is used<br>on devices without D2D<br>- added low voltage reset as possible source to the pin reset vector |

| 01.03             | 21 Nov<br>2007   |                   |        | added clarification of "Wake-up from STOP or WAIT by XIRQ with X bit set" feature                                                                                                                         |

| 01.04             | 20 May<br>2009   |                   |        | added footnote about availability of "Wake-up from STOP or WAIT by XIRQ with X bit set" feature                                                                                                           |

# 6.1 Introduction

The INT module decodes the priority of all system exception requests and provides the applicable vector for processing the exception to the CPU. The INT module supports:

- I bit and X bit maskable interrupt requests

- A non-maskable unimplemented op-code trap

- A non-maskable software interrupt (SWI) or background debug mode request

- Three system reset vector requests

- A spurious interrupt vector

Each of the I bit maskable interrupt requests is assigned to a fixed priority level.

# 6.1.1 Glossary

Table 6-2 contains terms and abbreviations used in the document.

#### Table 6-2. Terminology

| Term Meaning |                                      |

|--------------|--------------------------------------|

| CCR          | Condition Code Register (in the CPU) |

| ISR          | Interrupt Service Routine            |

| MCU          | Micro-Controller Unit                |

### 6.1.2 Features

- Interrupt vector base register (IVBR)

- One spurious interrupt vector (at address vector base  $^1 + 0x0080$ ).

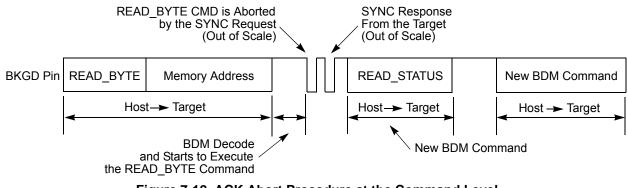

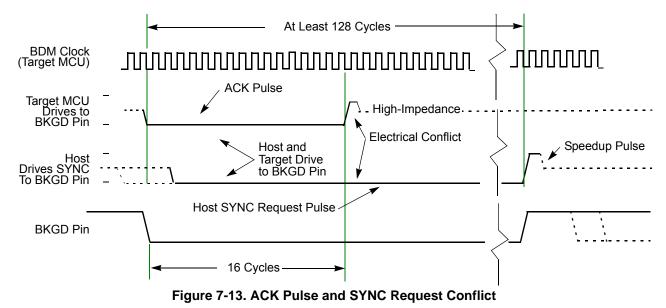

Since the host knows the target serial clock frequency, the SYNC command (used to abort a command) does not need to consider the lower possible target frequency. In this case, the host could issue a SYNC very close to the 128 serial clock cycles length. Providing a small overhead on the pulse length in order to assure the SYNC pulse will not be misinterpreted by the target. See Section 7.4.9, "SYNC — Request Timed Reference Pulse".

Figure 7-12 shows a SYNC command being issued after a READ\_BYTE, which aborts the READ\_BYTE command. Note that, after the command is aborted a new command could be issued by the host computer.

#### NOTE

Figure 7-13 shows a conflict between the ACK pulse and the SYNC request pulse. This conflict could occur if a POD device is connected to the target BKGD pin and the target is already in debug active mode. Consider that the target CPU is executing a pending BDM command at the exact moment the POD is being connected to the BKGD pin. In this case, an ACK pulse is issued along with the SYNC command. In this case, there is an electrical conflict between the ACK speedup pulse and the SYNC pulse. Since this is not a probable situation, the protocol does not prevent this conflict from happening.

MC9S12G Family Reference Manual Rev.1.27

#### S12S Debug Module (S12SDBGV2)

| SC[3:0] | Description (Unspecified matches have no effect)       |  |  |  |

|---------|--------------------------------------------------------|--|--|--|

| 1010    | Reserved                                               |  |  |  |

| 1011    | Reserved                                               |  |  |  |

| 1100    | Reserved                                               |  |  |  |

| 1101    | Either Match0 or Match2 to Final StateMatch1 to State2 |  |  |  |

| 1110    | Reserved                                               |  |  |  |

| 1111    | Reserved                                               |  |  |  |

| Table 8-16. | State1 | Sequencer | Next State | e Selection |

|-------------|--------|-----------|------------|-------------|

|-------------|--------|-----------|------------|-------------|

The priorities described in Table 8-36 dictate that in the case of simultaneous matches, a match leading to final state has priority followed by the match on the lower channel number (0,1,2). Thus with SC[3:0]=1101 a simultaneous match0/match1 transitions to final state.

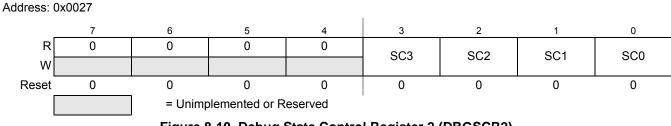

### 8.3.2.7.2 Debug State Control Register 2 (DBGSCR2)

Figure 8-10. Debug State Control Register 2 (DBGSCR2)

Read: If COMRV[1:0] = 01

Write: If COMRV[1:0] = 01 and DBG is not armed.

This register is visible at 0x0027 only with COMRV[1:0] = 01. The state control register 2 selects the targeted next state whilst in State2. The matches refer to the match channels of the comparator match control logic as depicted in Figure 8-1 and described in Section 8.3.2.8.1, "Debug Comparator Control Register (DBGXCTL). Comparators must be enabled by setting the comparator enable bit in the associated DBGXCTL control register.

#### Table 8-17. DBGSCR2 Field Descriptions

| Field          | Description                                                                             |

|----------------|-----------------------------------------------------------------------------------------|

| 3–0<br>SC[3:0] | These bits select the targeted next state whilst in State2, based upon the match event. |

#### Table 8-18. State2 — Sequencer Next State Selection

| SC[3:0] | Description (Unspecified matches have no effect) |  |  |  |

|---------|--------------------------------------------------|--|--|--|

| 0000    | Match0 to State1 Match2 to State3.               |  |  |  |

| 0001    | Match1 to State3                                 |  |  |  |

| 0010    | Match2 to State3                                 |  |  |  |

| 0011    | Match1 to State3 Match0 Final State              |  |  |  |

| 0100    | Match1 to State1 Match2 to State3.               |  |  |  |

#### MC9S12G Family Reference Manual Rev.1.27

### 8.4.5.1.1 Storing with Begin Trigger Alignment

Storing with begin alignment, data is not stored in the Trace Buffer until the Final State is entered. Once the trigger condition is met the DBG module remains armed until 64 lines are stored in the Trace Buffer. If the trigger is at the address of the change-of-flow instruction the change of flow associated with the trigger is stored in the Trace Buffer. Using begin alignment together with tagging, if the tagged instruction is about to be executed then the trace is started. Upon completion of the tracing session the breakpoint is generated, thus the breakpoint does not occur at the tagged instruction boundary.

### 8.4.5.1.2 Storing with End Trigger Alignment

Storing with end alignment, data is stored in the Trace Buffer until the Final State is entered, at which point the DBG module becomes disarmed and no more data is stored. If the trigger is at the address of a change of flow instruction, the trigger event is not stored in the Trace Buffer. If all trace buffer lines have been used before a trigger event occurrs then the trace continues at the first line, overwriting the oldest entries.

### 8.4.5.2 Trace Modes

Four trace modes are available. The mode is selected using the TRCMOD bits in the DBGTCR register. Tracing is enabled using the TSOURCE bit in the DBGTCR register. The modes are described in the following subsections.

### 8.4.5.2.1 Normal Mode

In Normal Mode, change of flow (COF) program counter (PC) addresses are stored.

COF addresses are defined as follows:

- Source address of taken conditional branches (long, short, bit-conditional, and loop primitives)

- Destination address of indexed JMP, JSR, and CALL instruction

- Destination address of RTI, RTS, and RTC instructions

- Vector address of interrupts, except for BDM vectors

LBRA, BRA, BSR, BGND as well as non-indexed JMP, JSR, and CALL instructions are not classified as change of flow and are not stored in the trace buffer.

Stored information includes the full 18-bit address bus and information bits, which contains a source/destination bit to indicate whether the stored address was a source address or destination address.

### NOTE

When a COF instruction with destination address is executed, the destination address is stored to the trace buffer on instruction completion, indicating the COF has taken place. If an interrupt occurs simultaneously then the next instruction carried out is actually from the interrupt service routine. The instruction at the destination address of the original program flow gets executed after the interrupt service routine.

#### Analog-to-Digital Converter (ADC10B8CV2)

| Address | Name               |             | Bit 7                                                                                                                           | 6                                                                                                                               | 5            | 4             | 3               | 2                              | 1      | Bit 0 |

|---------|--------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|-----------------|--------------------------------|--------|-------|

| 0x0003  | ATDCTL3            | R<br>W      | DJM                                                                                                                             | S8C                                                                                                                             | S4C          | S2C           | S1C             | FIFO                           | FRZ1   | FRZ0  |

| 0x0004  | ATDCTL4            | R<br>W      | SMP2                                                                                                                            | SMP1                                                                                                                            | SMP0         |               |                 | PRS[4:0]                       |        |       |

| 0x0005  | ATDCTL5            | R<br>W      | 0                                                                                                                               | SC                                                                                                                              | SCAN         | MULT          | CD              | СС                             | СВ     | CA    |

| 0x0006  | ATDSTAT0           | R<br>W      | SCF                                                                                                                             | 0                                                                                                                               | ETORF        | FIFOR         | CC3             | CC2                            | CC1    | CC0   |

| 0x0007  | Unimple-<br>mented | R<br>W      | 0                                                                                                                               | 0                                                                                                                               | 0            | 0             | 0               | 0                              | 0      | 0     |

| 0x0008  | ATDCMPEH           | R<br>W      | 0                                                                                                                               | 0                                                                                                                               | 0            | 0             | 0               | 0                              | 0      | 0     |

| 0x0009  | ATDCMPEL           | R<br>W      |                                                                                                                                 |                                                                                                                                 |              | СМ            | PE[7:0]         |                                |        |       |

| 0x000A  | ATDSTAT2H          | R<br>W      | 0                                                                                                                               | 0                                                                                                                               | 0            | 0             | 0               | 0                              | 0      | 0     |

| 0x000B  | ATDSTAT2L          | R           |                                                                                                                                 |                                                                                                                                 |              | CC            | CF[7:0]         |                                |        |       |

| 0x000C  | ATDDIENH           | W<br>R<br>W | 1                                                                                                                               | 1                                                                                                                               | 1            | 1             | 1               | 1                              | 1      | 1     |

| 0x000D  | ATDDIENL           | R<br>W      |                                                                                                                                 |                                                                                                                                 |              | IIE           | N[7:0]          |                                |        |       |

| 0x000E  | ATDCMPHTH          | R<br>W      | 0                                                                                                                               | 0                                                                                                                               | 0            | 0             | 0               | 0                              | 0      | 0     |

| 0x000F  | ATDCMPHTL          | R<br>W      | CMPHT[7:0]                                                                                                                      |                                                                                                                                 |              |               |                 |                                |        |       |

| 0x0010  | ATDDR0             | R<br>W      |                                                                                                                                 | See Section 11.3.2.12.1, "Left Justified Result Data (DJM=0)"<br>and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)" |              |               |                 |                                |        |       |

| 0x0012  | ATDDR1             | R<br>W      |                                                                                                                                 | See S                                                                                                                           | Section 11.3 | .2.12.1, "Let | ft Justified Re | esult Data (D<br>esult Data (D | JM=0)" |       |

| 0x0014  | ATDDR2             | R<br>W      |                                                                                                                                 | See S                                                                                                                           | Section 11.3 | .2.12.1, "Let | ft Justified Re | esult Data (D<br>esult Data (D | JM=0)" |       |

| 0x0016  | ATDDR3             | R<br>W      |                                                                                                                                 | See S                                                                                                                           | Section 11.3 | .2.12.1, "Let | ft Justified Re | esult Data (D<br>esult Data (D | JM=0)" |       |

| 0x0018  | ATDDR4             | R<br>W      |                                                                                                                                 | See S                                                                                                                           | Section 11.3 | .2.12.1, "Let | ft Justified Re | esult Data (D<br>esult Data (D | JM=0)" |       |

| 0x001A  | ATDDR5             | R<br>W      |                                                                                                                                 | See S                                                                                                                           | Section 11.3 | .2.12.1, "Let | ft Justified Re | esult Data (D<br>esult Data (D | JM=0)" |       |

| 0x001C  | ATDDR6             | R<br>W      | See Section 11<br>and Section 11.3                                                                                              |                                                                                                                                 |              | .2.12.1, "Let | ft Justified Re | esult Data (D                  | JM=0)" |       |

| 0x001E  | ATDDR7             | R<br>W      | See Section 11.3.2.12.2, "Left Justified Result Data (DJM=0)"<br>and Section 11.3.2.12.2, "Right Justified Result Data (DJM=1)" |                                                                                                                                 |              |               |                 |                                |        |       |

| 0x0020- | Unimple-           | R           | 0                                                                                                                               | 0                                                                                                                               | 0            | 0             | 0               | 0                              | 0      | 0     |

| 0x002F  | mented             | W           |                                                                                                                                 |                                                                                                                                 | mented or R  |               |                 |                                |        |       |

= Unimplemented or Reserved

Figure 11-2. ADC10B8C Register Summary (Sheet 2 of 2)

# 12.1.1 Features

- 8-, 10-, or 12-bit resolution.

- Automatic return to low power after conversion sequence

- Automatic compare with interrupt for higher than or less/equal than programmable value

- Programmable sample time.

- Left/right justified result data.

- External trigger control.

- Sequence complete interrupt.

- Analog input multiplexer for 8 analog input channels.

- Special conversions for VRH, VRL, (VRL+VRH)/2.

- 1-to-8 conversion sequence lengths.

- Continuous conversion mode.

- Multiple channel scans.

- Configurable external trigger functionality on any AD channel or any of four additional trigger inputs. The four additional trigger inputs can be chip external or internal. Refer to device specification for availability and connectivity.

- Configurable location for channel wrap around (when converting multiple channels in a sequence).

# 20.1.2 Features

The SCI includes these distinctive features:

- Full-duplex or single-wire operation

- Standard mark/space non-return-to-zero (NRZ) format

- Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

- 13-bit baud rate selection

- Programmable 8-bit or 9-bit data format

- Separately enabled transmitter and receiver

- Programmable polarity for transmitter and receiver

- Programmable transmitter output parity

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- Interrupt-driven operation with eight flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receive wakeup on active edge

- Transmit collision detect supporting LIN

- Break Detect supporting LIN

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

# 20.1.3 Modes of Operation

The SCI functions the same in normal, special, and emulation modes. It has two low power modes, wait and stop modes.

- Run mode

- Wait mode

- Stop mode

Table 24-34. Erase Verify P-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                         |  |  |

|-------------|----------------------------------------------------------|--|--|

| 000         | 0x03 Global address [17:16]<br>a P-Flash block           |  |  |

| 001         | Global address [15:0] of the first phrase to be verified |  |  |

| 010         | Number of phrases to be verified                         |  |  |

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 24-35. Erase Verify P-Flash Section Command Error Handling

| Register | Error Bit                | Error Condition                                                                                                |

|----------|--------------------------|----------------------------------------------------------------------------------------------------------------|

|          |                          | Set if CCOBIX[2:0] != 010 at command launch                                                                    |

|          |                          | Set if command not available in current mode (see Table 24-25)                                                 |

|          | ACCERR Set if an invalid | Set if an invalid global address [17:0] is supplied see Table 24-3) <sup>1</sup>                               |

|          |                          | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                                   |

| FSTAT    |                          | Set if the requested section crosses a the P-Flash address boundary                                            |

|          | FPVIOL                   | None                                                                                                           |

|          | MGSTAT1                  | Set if any errors have been encountered during the read <sup>2</sup> or if blank check failed.                 |

|          | MGSTAT0                  | Set if any non-correctable errors have been encountered during the read <sup>2</sup> or if blank check failed. |

<sup>1</sup> As defined by the memory map for FTMRG32K1.

$^2$  As found in the memory map for FTMRG32K1.

# 24.4.6.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once command described in Section 24.4.6.6. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| Table 24-3 | 5. Read Once Command FCCOB Requirements |

|------------|-----------------------------------------|

|            |                                         |

| CCOBIX[2:0] | FCCOB Parameters                         |  |  |

|-------------|------------------------------------------|--|--|

| 000         | 0x04 Not Required                        |  |  |

| 001         | Read Once phrase index (0x0000 - 0x0007) |  |  |

| 010         | Read Once word 0 value                   |  |  |

| 011         | Read Once word 1 value                   |  |  |

| 100         | Read Once word 2 value                   |  |  |

#### 32 KByte Flash Module (S12FTMRG32K1V1)

| Register | Error Bit | Error Condition                                                                                   |

|----------|-----------|---------------------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                                                       |

|          |           | Set if command not available in current mode (see Table 25-27)                                    |

|          | ACCERR    | Set if an invalid global address [17:0] is supplied                                               |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)                            |

| FSTAT    |           | Set if the requested section breaches the end of the EEPROM block                                 |

|          | FPVIOL    | None                                                                                              |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |

Table 25-61. Erase Verify EEPROM Section Command Error Handling

## 25.4.6.15 Program EEPROM Command

The Program EEPROM operation programs one to four previously erased words in the EEPROM block. The Program EEPROM operation will confirm that the targeted location(s) were successfully programmed upon completion.

### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

Table 25-62. Program EEPROM Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                               |                                                             |  |

|-------------|------------------------------------------------|-------------------------------------------------------------|--|

| 000         | 0x11                                           | 0x11 Global address [17:16] to<br>identify the EEPROM block |  |

| 001         | Global address [15:0] of word to be programmed |                                                             |  |

| 010         | Word 0 program value                           |                                                             |  |

| 011         | Word 1 program value, if desired               |                                                             |  |

| 100         | Word 2 program value, if desired               |                                                             |  |

| 101         | Word 3 program value, if desired               |                                                             |  |

Upon clearing CCIF to launch the Program EEPROM command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program EEPROM command launch determines how many words will be programmed in the EEPROM block. The CCIF flag is set when the operation has completed.

During the reset sequence, fields DPOPEN and DPS of the EEPROT register are loaded with the contents of the EEPROM protection byte in the Flash configuration field at global address 0x3\_FF0D located in P-Flash memory (see Table 26-4) as indicated by reset condition F in Table 26-23. To change the EEPROM protection that will be loaded during the reset sequence, the P-Flash sector containing the EEPROM protection byte must be unprotected, then the EEPROM protection byte must be programmed. If a double bit fault is detected while reading the P-Flash phrase containing the EEPROM protection byte must be to leave the EEPROM protection byte must be programmed. If a double bit fault is detected while reading the P-Flash phrase containing the EEPROM protection byte must be memory fully protected.

Trying to alter data in any protected area in the EEPROM memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. Block erase of the EEPROM memory is not possible if any of the EEPROM sectors are protected.

| Table 26-22. EEPROT | <b>Field Descriptions</b> |

|---------------------|---------------------------|

|---------------------|---------------------------|

| Field           | Description                                                                                                                                                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DPOPEN     | <ul> <li>EEPROM Protection Control</li> <li>Enables EEPROM memory protection from program and erase with protected address range defined by DPS bits</li> <li>Disables EEPROM memory protection from program and erase</li> </ul> |

| 5–0<br>DPS[5:0] | <b>EEPROM Protection Size</b> — The DPS[5:0] bits determine the size of the protected area in the EEPROM memory as shown in Table 26-23.                                                                                          |

| DPS[5:0]                                                                                         | Global Address Range | Protected Size |  |  |

|--------------------------------------------------------------------------------------------------|----------------------|----------------|--|--|

| 000000                                                                                           | 0x0_0400 – 0x0_041F  | 32 bytes       |  |  |

| 000001                                                                                           | 0x0_0400 - 0x0_043F  | 64 bytes       |  |  |

| 000010                                                                                           | 0x0_0400 – 0x0_045F  | 96 bytes       |  |  |

| 000011                                                                                           | 0x0_0400 – 0x0_047F  | 128 bytes      |  |  |

| 000100                                                                                           | 0x0_0400 - 0x0_049F  | 160 bytes      |  |  |

| 000101                                                                                           | 0x0_0400 – 0x0_04BF  | 192 bytes      |  |  |

| The Protection Size goes on enlarging in step of 32 bytes, for each DPS value increasing of one. |                      |                |  |  |

| 101111 - to - 111111                                                                             | 0x0_0400 – 0x0_09FF  | 1,536 bytes    |  |  |

#### Table 26-23. EEPROM Protection Address Range

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |  |

|-------------|----------------------------------------------------------|----------------------------------------------|--|

| 000         | 0x03                                                     | Global address [17:16] of<br>a P-Flash block |  |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |  |

| 010         | Number of phrases to be verified                         |                                              |  |

Table 27-36. Erase Verify P-Flash Section Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 27-37. Erase Verify P-Flash Section Command Error Handling

| Register | Error Bit Error Condition |                                                                                                   |  |  |

|----------|---------------------------|---------------------------------------------------------------------------------------------------|--|--|

|          |                           | Set if CCOBIX[2:0] != 010 at command launch                                                       |  |  |

|          |                           | Set if command not available in current mode (see Table 27-27)                                    |  |  |

|          | ACCERR                    | Set if an invalid global address [17:0] is supplied see Table 27-3)                               |  |  |

|          |                           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                      |  |  |

| FSTAT    |                           | Set if the requested section crosses a the P-Flash address boundary                               |  |  |

|          | FPVIOL                    | None                                                                                              |  |  |

|          | MGSTAT1                   | Set if any errors have been encountered during the read or if blank check fa                      |  |  |

|          | MGSTAT0                   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |  |  |

# 27.4.6.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once command described in Section 27.4.6.6. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters     |                       |

|-------------|----------------------|-----------------------|

| 000         | 0x04                 | Not Required          |

| 001         | Read Once phrase inc | dex (0x0000 - 0x0007) |

| 010         | Read Once            | word 0 value          |

| 011         | Read Once            | word 1 value          |

| 100         | Read Once            | word 2 value          |

| 101         | Read Once            | word 3 value          |

#### 96 KByte Flash Module (S12FTMRG96K1V1)

| FCMD | Command                         | Function on P-Flash Memory                                                                                                                                                                                                                     |

|------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x02 | Erase Verify Block              | Verify that a P-Flash block is erased.                                                                                                                                                                                                         |

| 0x03 | Erase Verify<br>P-Flash Section | Verify that a given number of words starting at the address provided are erased.                                                                                                                                                               |

| 0x04 | Read Once                       | Read a dedicated 64 byte field in the nonvolatile information register in P-Flash block that was previously programmed using the Program Once command.                                                                                         |

| 0x06 | Program P-Flash                 | Program a phrase in a P-Flash block.                                                                                                                                                                                                           |

| 0x07 | Program Once                    | Program a dedicated 64 byte field in the nonvolatile information register in P-Flash block that is allowed to be programmed only once.                                                                                                         |

| 0x08 | Erase All Blocks                | Erase all P-Flash (and EEPROM) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN<br>bits in the FPROT register and the DPOPEN bit in the EEPROT register are set prior to<br>launching the command. |

| 0x09 | Erase Flash Block               | Erase a P-Flash (or EEPROM) block.<br>An erase of the full P-Flash block is only possible when FPLDIS, FPHDIS and FPOPEN<br>bits in the FPROT register are set prior to launching the command.                                                 |

| 0x0A | Erase P-Flash<br>Sector         | Erase all bytes in a P-Flash sector.                                                                                                                                                                                                           |

| 0x0B | Unsecure Flash                  | Supports a method of releasing MCU security by erasing all P-Flash (and EEPROM) blocks and verifying that all P-Flash (and EEPROM) blocks are erased.                                                                                          |

| 0x0C | Verify Backdoor<br>Access Key   | Supports a method of releasing MCU security by verifying a set of security keys.                                                                                                                                                               |

| 0x0D | Set User Margin<br>Level        | Specifies a user margin read level for all P-Flash blocks.                                                                                                                                                                                     |

| 0x0E | Set Field Margin<br>Level       | Specifies a field margin read level for all P-Flash blocks (special modes only).                                                                                                                                                               |

#### Table 28-28. P-Flash Commands

# 28.4.4.5 EEPROM Commands

Table 28-29 summarizes the valid EEPROM commands along with the effects of the commands on the EEPROM block.

| Table 28-29 | . EEPROM | Commands |

|-------------|----------|----------|

|-------------|----------|----------|

| FCMD | Command                    | Function on EEPROM Memory                               |

|------|----------------------------|---------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks | Verify that all EEPROM (and P-Flash) blocks are erased. |

| 0x02 | Erase Verify Block         | Verify that the EEPROM block is erased.                 |

# 28.4.6 Flash Command Description

This section provides details of all available Flash commands launched by a command write sequence. The ACCERR bit in the FSTAT register will be set during the command write sequence if any of the following illegal steps are performed, causing the command not to be processed by the Memory Controller:

- Starting any command write sequence that programs or erases Flash memory before initializing the FCLKDIV register

- Writing an invalid command as part of the command write sequence

- For additional possible errors, refer to the error handling table provided for each command

If a Flash block is read during execution of an algorithm (CCIF = 0) on that same block, the read operation will return invalid data if both flags SFDIF and DFDIF are set. If the SFDIF or DFDIF flags were not previously set when the invalid read operation occurred, both the SFDIF and DFDIF flags will be set.

If the ACCERR or FPVIOL bits are set in the FSTAT register, the user must clear these bits before starting any command write sequence (see Section 28.3.2.7).

### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

## 28.4.6.1 Erase Verify All Blocks Command

The Erase Verify All Blocks command will verify that all P-Flash and EEPROM blocks have been erased.

Table 28-31. Erase Verify All Blocks Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x01             | Not required |

Upon clearing CCIF to launch the Erase Verify All Blocks command, the Memory Controller will verify that the entire Flash memory space is erased. The CCIF flag will set after the Erase Verify All Blocks operation has completed. If all blocks are not erased, it means blank check failed, both MGSTAT bits will be set.

Table 28-32. Erase Verify All Blocks Command Error Handling

| Register | Error Bit | Error Condition                                                                                                |

|----------|-----------|----------------------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                                    |

|          | FPVIOL    | None                                                                                                           |

| FSTAT    | MGSTAT1   | Set if any errors have been encountered during the read <sup>1</sup> or if blank check failed .                |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read <sup>1</sup> or if blank check failed. |

<sup>1</sup> As found in the memory map for FTMRG96K1.

# 29.4.6.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of the P-Flash or EEPROM block.

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the Table 29-57. Set Field Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |                                                   |

|-------------|------------------|---------------------------------------------------|

| 000         | 0x0E             | Flash block selection code [1:0]. See Table 29-34 |

| 001         | Ма               | rgin level setting.                               |

field margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM field margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash field margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply field margin levels to the P-Flash block only.

Valid margin level settings for the Set Field Margin Level command are defined in Table 29-58.

| CCOB<br>(CCOBIX=001) | Level Description                 |

|----------------------|-----------------------------------|

| 0x0000               | Return to Normal Level            |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |

Table 29-58. Valid Set Field Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### 192 KByte Flash Module (S12FTMRG192K2V1)

# 31.4.6.15 Program EEPROM Command

The Program EEPROM operation programs one to four previously erased words in the EEPROM block. The Program EEPROM operation will confirm that the targeted location(s) were successfully programmed upon completion.

### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

| CCOBIX[2:0] | FCCOB Parameters         |                                                        |

|-------------|--------------------------|--------------------------------------------------------|

| 000         | 0x11                     | Global address [17:16] to<br>identify the EEPROM block |

| 001         | Global address [15:0] of | word to be programmed                                  |

| 010         | Word 0 pro               | gram value                                             |

| 011         | Word 1 program           | value, if desired                                      |

| 100         | Word 2 program           | value, if desired                                      |

| 101         | Word 3 program           | value, if desired                                      |

Table 31-62. Program EEPROM Command FCCOB Requirements

Upon clearing CCIF to launch the Program EEPROM command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program EEPROM command launch determines how many words will be programmed in the EEPROM block. The CCIF flag is set when the operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] < 010 at command launch                                          |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |

|          |           | Set if command not available in current mode (see Table 31-27)                      |

|          |           | Set if an invalid global address [17:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          |           | Set if the requested group of words breaches the end of the EEPROM block            |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

| ٦        | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

# 31.4.6.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

#### Table A-24. ADC Conversion Performance 5V range (Junction Temperature From +150°C To +160°C)

| S12GI            | N16          | , S12GN32                                                                    |                                                      |                                                                |                                                        |                                             |             |        |

|------------------|--------------|------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------|-------------|--------|

| Supply<br>The va | / vo<br>alue | ltage 4.5V < V <sub>DDA</sub> < 5.5 V, 15<br>s are tested to be valid with n | 50°C < T <sub>J</sub> < 160°C<br>to port AD output o | c, V <sub>REF</sub> = V <sub>RH</sub> - V<br>drivers switching | r <sub>RL</sub> = V <sub>DDA</sub> , f<br>simultaneous | <sub>ADCCLK</sub> = 8.0M<br>s with conversi | lHz<br>ons. |        |

| Num              | С            | Rating                                                                       | 1                                                    | Symbol                                                         | Min                                                    | Тур                                         | Max         | Unit   |

| 1                | М            | Resolution                                                                   | 10-Bit                                               | LSB                                                            |                                                        | 5                                           |             | mV     |

| 2                | М            | Differential Nonlinearity                                                    | 10-Bit                                               | DNL                                                            |                                                        | ±0.5                                        |             | counts |

| 3                | М            | Integral Nonlinearity                                                        | 10-Bit                                               | INL                                                            |                                                        | ±1                                          |             | counts |

| 4                | М            | Absolute Error <sup>2</sup>                                                  | 10-Bit <sup>3</sup><br>10-Bit <sup>4</sup>           | AE                                                             |                                                        | ±2<br>±2                                    |             | counts |

| 5                | С            | Resolution                                                                   | 8-Bit                                                | LSB                                                            |                                                        | 20                                          |             | mV     |

| 6                | С            | Differential Nonlinearity                                                    | 8-Bit                                                | DNL                                                            |                                                        | ±0.3                                        |             | counts |

| 7                | С            | Integral Nonlinearity                                                        | 8-Bit                                                | INL                                                            |                                                        | ±0.5                                        |             | counts |

| 8                | С            | Absolute Error <sup>2</sup>                                                  | 8-Bit                                                | AE                                                             |                                                        | ±1                                          |             | counts |

<sup>1</sup> The 8-bit mode operation is structurally tested in production test. Absolute values are tested in 10-bit mode.

<sup>2</sup> These values include the quantization error which is inherently 1/2 count for any A/D converter.

<sup>3</sup> LQFP 48 and bigger

<sup>4</sup> LQFP 32 and smaller

#### S12GNA16, S12GNA32, S12GAS48, S12GA64, S12GA96, S12GA128, S12GA192 and S12GA240 Supply voltage $3.13V < V_{DDA} < 4.5 V$ , $-40^{\circ}C < T_{J} < 150^{\circ}C$ , $V_{REF} = V_{RH} - V_{RL} = V_{DDA}$ , $f_{ADCCLK} = 8.0MHz$ The values are tested to be valid with no port AD output drivers switching simultaneous with conversions. Rating<sup>1</sup> С Num Symbol Min Max Unit Typ P Resolution 12-Bit LSB 0.80 mV 1 **Differential Nonlinearity** 2 Ρ 12-Bit DNL -6 ±3 6 counts Ρ Integral Nonlinearity 12-Bit -7 7 3 INL ±3 counts Absolute Error<sup>2</sup> 4 Р 12-Bit AE -8 ±4 8 counts 5 С Resolution 10-Bit 3.22 LSB mV С **Differential Nonlinearity** 10-Bit DNL 6 -1.5 ±1 1.5 counts 7 -2 С Integral Nonlinearity 10-Bit INL 2 ±1 counts С Absolute Error<sup>2</sup> 8 10-Bit AE -3 ±2 3 counts С Resolution 8-Bit LSB 12.89 mV 9 **Differential Nonlinearity** 10 С 8-Bit DNL -0.5 ±0.3 0.5 counts Integral Nonlinearity 11 С 8-Bit INL -1 $\pm 0.5$ 1 counts Absolute Error<sup>2</sup> 12 С 8-Bit AE -1.5 ±1 1.5 counts

#### Table A-25. ADC Conversion Performance 3.3V range (Junction Temperature From –40°C To +150°C)

The 8-bit and 10-bit mode operation is structurally tested in production test. Absolute values are tested in 12-bit mode.

NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

3. DATUMS B, C AND D TO BE DETERMINED AT DATUM PLANE H.

$\overline{4}$ . The top package body size may be smaller than the bottom package size by a maximum of 0.1 mm.

5. DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSIONS. THE MAXIMUM ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. D1 AND E1 ARE MAXIMUM BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

6. DIMENSION & DOES NOT INCLUDE DAM BAR PROTRUSION. PROTRUSIONS SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.35. MINIMUM SPACE BETWEEN PROTRUSION AND AN ADJACENT LEAD SHALL BE 0.07 MM.

/7. DIMENSIONS D AND E ARE DETERMINED AT THE SEATING PLANE, DATUM A.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE                 | PRINT VERSION NOT TO SCALE |             |  |

|---------------------------------------------------------|-----------|--------------------------|----------------------------|-------------|--|

| TITLE:                                                  |           | DOCUMENT NO: 98ASS23308W |                            | REV: H      |  |

| 100 LEAD LQFP<br>14 X 14, 0.5 PITCH, 1.4                | LTHICK    | CASE NUMBER: 983-02      |                            | 25 MAY 2005 |  |

|                                                         |           | STANDARD: NO             | DN-JEDEC                   |             |  |