# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 86                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g128f0mll |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 13.2 | Signal Description                  | 459 |

|------|-------------------------------------|-----|

|      | 13.2.1 Detailed Signal Descriptions | 459 |

| 13.3 | Memory Map and Register Definition  | 459 |

|      | 13.3.1 Module Memory Map            | 459 |

|      | 13.3.2 Register Descriptions        | 462 |

| 13.4 | Functional Description              | 477 |

|      | 13.4.1 Analog Sub-Block             | 477 |

|      | 13.4.2 Digital Sub-Block            | 477 |

| 13.5 | Resets                              | 479 |

| 13.6 | Interrupts                          | 479 |

# Chapter 14 Analog-to-Digital Converter (ADC12B12CV2)

| 14.1 | Introduction                        | 482 |

|------|-------------------------------------|-----|

|      | 14.1.1 Features                     | 482 |

|      | 14.1.2 Modes of Operation           | 483 |

|      | 14.1.3 Block Diagram                | 484 |

| 14.2 | Signal Description                  | 485 |

|      | 14.2.1 Detailed Signal Descriptions | 485 |

| 14.3 | Memory Map and Register Definition  | 485 |

|      | 14.3.1 Module Memory Map            | 485 |

|      | 14.3.2 Register Descriptions        |     |

| 14.4 | Functional Description              | 504 |

|      | 14.4.1 Analog Sub-Block             |     |

|      | 14.4.2 Digital Sub-Block            |     |

| 14.5 | Resets                              | 506 |

| 14.6 | Interrupts                          | 506 |

# Chapter 15

# Analog-to-Digital Converter (ADC10B16CV2)

| Introduction                       | 508                                                                                                                                                                                                                                                                                |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.1 Features                    | 508                                                                                                                                                                                                                                                                                |

| 15.1.2 Modes of Operation          | 509                                                                                                                                                                                                                                                                                |

| 15.1.3 Block Diagram               | 510                                                                                                                                                                                                                                                                                |

| Signal Description                 | 511                                                                                                                                                                                                                                                                                |

|                                    |                                                                                                                                                                                                                                                                                    |

| Memory Map and Register Definition | 511                                                                                                                                                                                                                                                                                |

| 15.3.1 Module Memory Map           | 511                                                                                                                                                                                                                                                                                |

| 15.3.2 Register Descriptions       | 514                                                                                                                                                                                                                                                                                |

| Functional Description             | 529                                                                                                                                                                                                                                                                                |

| 15.4.1 Analog Sub-Block            | 529                                                                                                                                                                                                                                                                                |

| 15.4.2 Digital Sub-Block           | 529                                                                                                                                                                                                                                                                                |

| Resets                             | 531                                                                                                                                                                                                                                                                                |

| Interrupts                         | 531                                                                                                                                                                                                                                                                                |

|                                    | 15.1.1 Features15.1.2 Modes of Operation15.1.3 Block DiagramSignal Description15.2.1 Detailed Signal DescriptionsMemory Map and Register Definition15.3.1 Module Memory Map15.3.2 Register DescriptionsFunctional Description15.4.1 Analog Sub-Block15.4.2 Digital Sub-BlockResets |

|             | <b>Function</b><br><lowestpriorityhighest></lowestpriorityhighest> |                |              |             |             |                  | Internal Pull<br>Resistor |                |  |

|-------------|--------------------------------------------------------------------|----------------|--------------|-------------|-------------|------------------|---------------------------|----------------|--|

| Package Pin | Pin                                                                | 2nd<br>Func.   | 3rd<br>Func. | 4th<br>Func | 5th<br>Func | Supply           | CTRL                      | Reset<br>State |  |

| 28          | PAD9                                                               | KWAD9          | ACMPO        | _           | _           | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 29          | PAD2                                                               | KWAD2          | AN2          | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 30          | PAD10                                                              | KWAD10         | ACMPP        |             |             | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 31          | PAD3                                                               | KWAD3          | AN3          | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 32          | PAD11                                                              | KWAD11         | ACMPM        |             |             | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 33          | PAD4                                                               | KWAD4          | AN4          | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 34          | PAD5                                                               | KWAD5          | AN5          | _           | _           | V <sub>DDA</sub> | PER1AD/PPS0AD             | Disabled       |  |

| 35          | PAD6                                                               | KWAD6          | AN6          | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 36          | PAD7                                                               | KWAD7          | AN7          | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 37          | VDDA                                                               | VRH            | _            | _           | _           | _                | _                         |                |  |

| 38          | VSSA                                                               | —              | _            | _           | _           | _                | _                         | _              |  |

| 39          | PS0                                                                | RXD0           | _            | _           | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 40          | PS1                                                                | TXD0           | _            | _           | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 41          | PS2                                                                | —              | _            | _           | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 42          | PS3                                                                | —              | _            | _           | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 43          | PS4                                                                | MISO0          | _            | _           | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 44          | PS5                                                                | MOSI0          | _            |             | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 45          | PS6                                                                | SCK0           | _            |             | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 46          | PS7                                                                | API_EXTC<br>LK | ECLK         | SS0         | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 47          | PM0                                                                | —              | _            |             | -           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |  |

| 48          | PM1                                                                | _              | _            | _           | _           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |  |

Table 1-10. 48-Pin LQFP/QFN Pinout for S12GN16 and S12GN32

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

#### S12 Clock, Reset and Power Management Unit (S12CPMU)

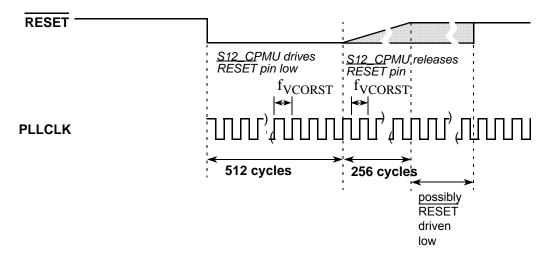

The internal reset of the MCU remains asserted while the reset generator completes the 768 PLLCLK cycles long reset sequence. In case the RESET pin is externally driven low for more than these 768 PLLCLK cycles (External Reset), the internal reset remains asserted longer.

### 10.5.2.1 Clock Monitor Reset

If the external oscillator is enabled (OSCE=1) in case of loss of oscillation or the oscillator frequency is below the failure assert frequency  $f_{CMFA}$  (see device electrical characteristics for values), the S12CPMU generates a Clock Monitor Reset.In Full Stop Mode the external oscillator and the clock monitor are disabled.

### 10.5.2.2 Computer Operating Properly Watchdog (COP) Reset

The COP (free running watchdog timer) enables the user to check that a program is running and sequencing properly. When the COP is being used, software is responsible for keeping the COP from timing out. If the COP times out it is an indication that the software is no longer being executed in the intended sequence; thus COP reset is generated.

The clock source for the COP is either ACLK, IRCCLK or OSCCLK depending on the setting of the COPOSCSEL0 and COPOSCSEL1 bit.

In Stop Mode with PSTP=1 (Pseudo Stop Mode), COPOSCSEL0=1 and COPOSCEL1=0 and PCE=1 the COP continues to run, else the COP counter halts in Stop Mode with COPOSCSEL1 =0. In Pseudo Stop Mode and Full Stop Mode with COPOSCSEL1=1 the COP continues to run.

Table 10-28.gives an overview of the COP condition (run, static) in Stop Mode depending on legal configuration and status bit settings:

# 16.2 Signal Description

This section lists all inputs to the ADC12B16C block.

### 16.2.1 Detailed Signal Descriptions

### 16.2.1.1 ANx (x = 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0)

This pin serves as the analog input Channel *x*. It can also be configured as digital port or external trigger for the ATD conversion.

### 16.2.1.2 ETRIG3, ETRIG2, ETRIG1, ETRIG0

These inputs can be configured to serve as an external trigger for the ATD conversion.

Refer to device specification for availability and connectivity of these inputs!

### 16.2.1.3 VRH, VRL

VRH is the high reference voltage, VRL is the low reference voltage for ATD conversion.

### 16.2.1.4 VDDA, VSSA

These pins are the power supplies for the analog circuitry of the ADC12B16C block.

## 16.3 Memory Map and Register Definition

This section provides a detailed description of all registers accessible in the ADC12B16C.

### 16.3.1 Module Memory Map

Figure 16-2 gives an overview on all ADC12B16C registers.

### NOTE

Register Address = Base Address + Address Offset, where the Base Address is defined at the MCU level and the Address Offset is defined at the module level.

| Address | Name    | Bit 7           | 6     | 5        | 4       | 3        | 2        | 1        | Bit 0    |

|---------|---------|-----------------|-------|----------|---------|----------|----------|----------|----------|

| 0x0000  | ATDCTL0 | R<br>Reserved   | 0     | 0        | 0       | WRAP3    | WRAP2    | WRAP1    | WRAP0    |

| 0x0001  | ATDCTL1 | R<br>W ETRIGSEL | SRES1 | SRES0    | SMP_DIS | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 |

| 0x0002  | ATDCTL2 | R 0<br>W        | AFFC  | Reserved | ETRIGLE | ETRIGP   | ETRIGE   | ASCIE    | ACMPIE   |

|         |         |                 |       |          |         |          |          |          |          |

= Unimplemented or Reserved

Figure 16-2. ADC12B16C Register Summary (Sheet 1 of 3)

### Table 22-13. TRLG1 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field          | Description                                                                                                                                                                                                      |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5:0<br>C[5:0]F | Input Capture/Output Compare Channel "x" Flag — These flags are set when an input capture or output compare event occurs. Clearing requires writing a one to the corresponding flag bit while TEN is set to one. |  |  |  |

|                | <b>Note:</b> When TFFCA bit in TSCR register is set, a read from an input capture or a write into an output compare channel (0x0010–0x001F) will cause the corresponding channel flag CxF to be cleared.         |  |  |  |

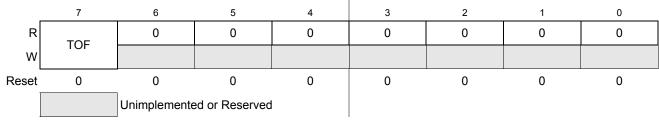

### 22.3.2.11 Main Timer Interrupt Flag 2 (TFLG2)

Module Base + 0x000F

Figure 22-17. Main Timer Interrupt Flag 2 (TFLG2)

TFLG2 indicates when interrupt conditions have occurred. To clear a bit in the flag register, write the bit to one while TEN bit of TSCR1.

Read: Anytime

Write: Used in clearing mechanism (set bits cause corresponding bits to be cleared).

Any access to TCNT will clear TFLG2 register if the TFFCA bit in TSCR register is set.

#### Table 22-14. TRLG2 Field Descriptions

| Field Description |                                                                                                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | <b>Timer Overflow Flag</b> — Set when 16-bit free-running timer overflows from 0xFFFF to 0x0000. Clearing this bit requires writing a one to bit 7 of TFLG2 register while the TEN bit of TSCR1 is set to one. |

| DPS[4:0]                                                                                         | Global Address Range | Protected Size |  |  |

|--------------------------------------------------------------------------------------------------|----------------------|----------------|--|--|

| 00000                                                                                            | 0x0_0400 - 0x0_041F  | 32 bytes       |  |  |

| 00001                                                                                            | 0x0_0400 - 0x0_043F  | 64 bytes       |  |  |

| 00010                                                                                            | 0x0_0400 – 0x0_045F  | 96 bytes       |  |  |

| 00011                                                                                            | 0x0_0400 – 0x0_047F  | 128 bytes      |  |  |

| 00100                                                                                            | 0x0_0400 – 0x0_049F  | 160 bytes      |  |  |

| 00101                                                                                            | 192 bytes            |                |  |  |

| The Protection Size goes on enlarging in step of 32 bytes, for each DPS value increasing of one. |                      |                |  |  |

| 01111 - to - 11111                                                                               | 0x0_0400 – 0x0_05FF  | 512 bytes      |  |  |

Table 24-21. EEPROM Protection Address Range

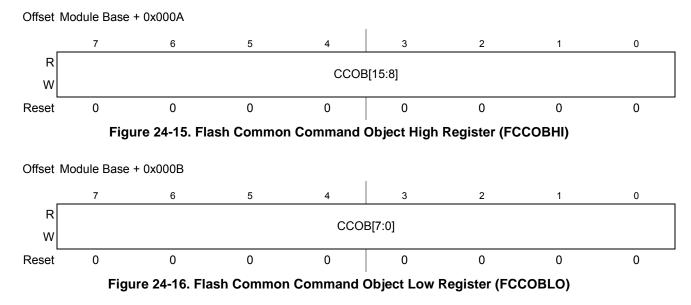

### 24.3.2.11 Flash Common Command Object Register (FCCOB)

The FCCOB is an array of six words addressed via the CCOBIX index found in the FCCOBIX register. Byte wide reads and writes are allowed to the FCCOB register.

### 24.3.2.11.1 FCCOB - NVM Command Mode

NVM command mode uses the indexed FCCOB register to provide a command code and its relevant parameters to the Memory Controller. The user first sets up all required FCCOB fields and then initiates

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          | ACCERR    | Set if command not available in current mode (see Table 24-25)                      |

|          | ACCERK    | Set if an invalid global address [17:16] is supplied see Table 24-3) <sup>1</sup>   |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

| Table 24-47. Erase P-Flash Sector Command Error Handling |

|----------------------------------------------------------|

|----------------------------------------------------------|

<sup>1</sup> As defined by the memory map for FTMRG32K1.

### 24.4.6.10 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and EEPROM memory space and, if the erase is successful, will release security.

### Table 24-48. Unsecure Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |

|-------------|------------------|--------------|--|

| 000         | 0x0B             | Not required |  |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and EEPROM memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security state. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag is set after the Unsecure Flash operation has completed.

| Register | Register Error Bit Error Condition |                                                                                                  |  |  |  |

|----------|------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

|          | ACCERR                             | Set if CCOBIX[2:0] != 000 at command launch                                                      |  |  |  |

|          | ACCERR                             | Set if command not available in current mode (see Table 24-25)                                   |  |  |  |

| FSTAT    | FPVIOL                             | Set if any area of the P-Flash or EEPROM memory is protected                                     |  |  |  |

|          | MGSTAT1                            | Set if any errors have been encountered during the verify operation <sup>1</sup>                 |  |  |  |

|          | MGSTAT0                            | Set if any non-correctable errors have been encountered during the verify operation <sup>1</sup> |  |  |  |

Table 24-49. Unsecure Flash Command Error Handling

<sup>1</sup> As found in the memory map for FTMRG32K1.

48 KByte Flash Module (S12FTMRG48K1V1)

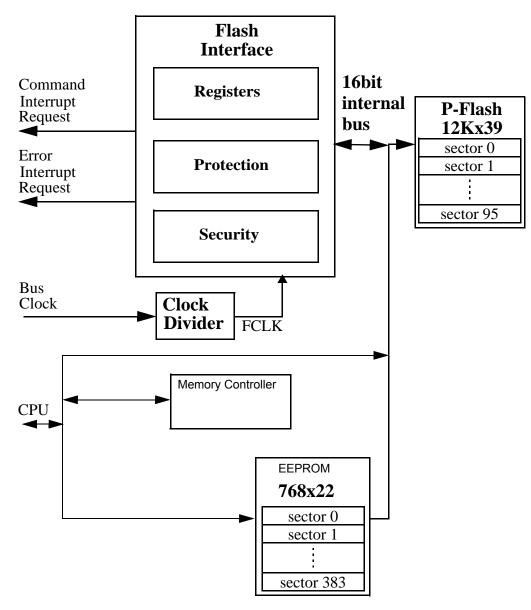

## 26.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 26-1.

# 26.2 External Signal Description

The Flash module contains no signals that connect off-chip.

| CCOBIX[2:0] | FCCOB Parameters                                  |                                                   |  |  |

|-------------|---------------------------------------------------|---------------------------------------------------|--|--|

| 000         | 0x09                                              | Global address [17:16] to<br>identify Flash block |  |  |

| 001         | Global address [15:0] in Flash block to be erased |                                                   |  |  |

Table 26-46. Erase Flash Block Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Flash Block command, the Memory Controller will erase the selected Flash block and verify that it is erased. The CCIF flag will set after the Erase Flash Block operation has completed.

| Register | Error Bit | Error Condition                                                                                        |  |  |

|----------|-----------|--------------------------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                                            |  |  |

|          |           | Set if command not available in current mode (see Table 26-27)                                         |  |  |

|          |           | Set if an invalid global address [17:16] is supplied                                                   |  |  |

| FSTAT    |           | Set if the supplied P-Flash address is not phrase-aligned or if the EEPROM address is not word-aligned |  |  |

|          | FPVIOL    | Set if an area of the selected Flash block is protected                                                |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                    |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation                    |  |  |

Table 26-47. Erase Flash Block Command Error Handling

### 26.4.6.9 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

Table 26-48. Erase P-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                         |                                                                  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| 000         | 0x0A                                                                                                                     | Global address [17:16] to identify<br>P-Flash block to be erased |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 26.1.2.1 for the P-Flash sector size. |                                                                  |  |  |

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

#### 64 KByte Flash Module (S12FTMRG64K1V1)

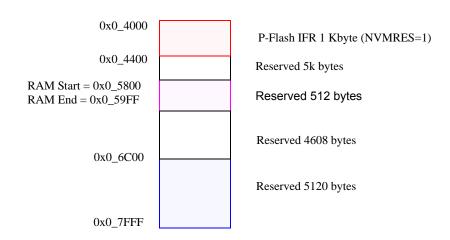

| Global Address      | Size<br>(Bytes) | Description                  |

|---------------------|-----------------|------------------------------|

| 0x0_4000 – 0x040FF  | 256             | P-Flash IFR (see Table 27-5) |

| 0x0_4100 - 0x0_41FF | 256             | Reserved.                    |

| 0x0_4200 – 0x0_57FF |                 | Reserved                     |

| 0x0_5800 - 0x0_59FF | 512             | Reserved                     |

| 0x0_5A00 – 0x0_5FFF | 1,536           | Reserved                     |

| 0x0_6000 – 0x0_6BFF | 3,072           | Reserved                     |

| 0x0_6C00 - 0x0_7FFF | 5,120           | Reserved                     |

<sup>1</sup> NVMRES - See Section 27.4.3 for NVMRES (NVM Resource) detail.

Figure 27-3. Memory Controller Resource Memory Map (NVMRES=1)

### 27.3.2 Register Descriptions

The Flash module contains a set of 20 control and status registers located between Flash module base + 0x0000 and 0x0013.

In the case of the writable registers, the write accesses are forbidden during Fash command execution (for more detail, see Caution note in Section 27.3).

#### 64 KByte Flash Module (S12FTMRG64K1V1)

| CCOBIX[2:0] | Byte | Byte FCCOB Parameter Fields (NVM Command Mode) |  |  |  |

|-------------|------|------------------------------------------------|--|--|--|

| 010         | HI   | Data 0 [15:8]                                  |  |  |  |

| 010         | LO   | Data 0 [7:0]                                   |  |  |  |

| 011         | HI   | Data 1 [15:8]                                  |  |  |  |

| 011         | LO   | Data 1 [7:0]                                   |  |  |  |

| 100         | HI   | Data 2 [15:8]                                  |  |  |  |

| 100         | LO   | Data 2 [7:0]                                   |  |  |  |

| 101         | HI   | Data 3 [15:8]                                  |  |  |  |

| 101         | LO   | Data 3 [7:0]                                   |  |  |  |

Table 27-24. FCCOB - NVM Command Mode (Typical Usage)

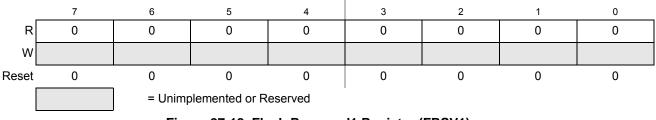

### 27.3.2.12 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000C

Offset Module Base + 0x000D

Figure 27-18. Flash Reserved1 Register (FRSV1)

All bits in the FRSV1 register read 0 and are not writable.

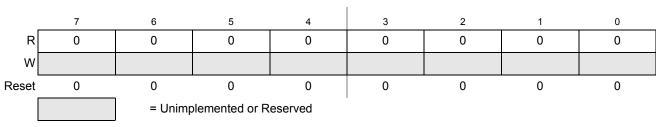

## 27.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

Figure 27-19. Flash Reserved2 Register (FRSV2)

All bits in the FRSV2 register read 0 and are not writable.

### 27.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

• VERNUM: Version number. The first version is number 0b\_0001 with both 0b\_0000 and 0b\_1111 meaning 'none'.

### 28.4.3 Internal NVM resource (NVMRES)

IFR is an internal NVM resource readable by CPU, when NVMRES is active. The IFR fields are shown in Table 28-5.

The NVMRES global address map is shown in Table 28-6.

## 28.4.4 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

- How to write the FCLKDIV register that is used to generate a time base (FCLK) derived from BUSCLK for Flash program and erase command operations

- The command write sequence used to set Flash command parameters and launch execution

- Valid Flash commands available for execution, according to MCU functional mode and MCU security state.

### 28.4.4.1 Writing the FCLKDIV Register

Prior to issuing any Flash program or erase command after a reset, the user is required to write the FCLKDIV register to divide BUSCLK down to a target FCLK of 1 MHz. Table 28-8 shows recommended values for the FDIV field based on BUSCLK frequency.

### NOTE

Programming or erasing the Flash memory cannot be performed if the bus clock runs at less than 0.8 MHz. Setting FDIV too high can destroy the Flash memory due to overstress. Setting FDIV too low can result in incomplete programming or erasure of the Flash memory cells.

When the FCLKDIV register is written, the FDIVLD bit is set automatically. If the FDIVLD bit is 0, the FCLKDIV register has not been written since the last reset. If the FCLKDIV register has not been written, any Flash program or erase command loaded during a command write sequence will not execute and the ACCERR bit in the FSTAT register will set.

### 28.4.4.2 Command Write Sequence

The Memory Controller will launch all valid Flash commands entered using a command write sequence.

Before launching a command, the ACCERR and FPVIOL bits in the FSTAT register must be clear (see Section 28.3.2.7) and the CCIF flag should be tested to determine the status of the current command write sequence. If CCIF is 0, the previous command write sequence is still active, a new command write sequence cannot be started, and all writes to the FCCOB register are ignored.

# 29.1.2 Features

### 29.1.2.1 P-Flash Features

- 128 Kbytes of P-Flash memory composed of one 128 Kbyte Flash block divided into 256 sectors of 512 bytes

- Single bit fault correction and double bit fault detection within a 32-bit double word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and phrase program operation

- Ability to read the P-Flash memory while programming a word in the EEPROM memory

- Flexible protection scheme to prevent accidental program or erase of P-Flash memory

### 29.1.2.2 EEPROM Features

- 4 Kbytes of EEPROM memory composed of one 4 Kbyte Flash block divided into 1024 sectors of 4 bytes

- Single bit fault correction and double bit fault detection within a word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and word program operation

- Protection scheme to prevent accidental program or erase of EEPROM memory

- Ability to program up to four words in a burst sequence

### 29.1.2.3 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

## 29.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 29-1.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                         |  |  |

|          |           | Set if command not available in current mode (see Table 29-27)                      |  |  |

|          |           | Set if an invalid global address [17:0] is supplied (see Table 29-3)                |  |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |  |

|          | FPVIOL    | Set if the global address [17:0] points to a protected area                         |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

Table 29-41. Program P-Flash Command Error Handling

### 29.4.6.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash. The Program Once reserved field can be read using the Read Once command as described in Section 29.4.6.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |  |  |  |  |

|-------------|---------------------------------------------|--|--|--|--|

| 000         | 0x07 Not Required                           |  |  |  |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |  |  |  |  |

| 010         | Program Once word 0 value                   |  |  |  |  |

| 011         | Program Once word 1 value                   |  |  |  |  |

| 100         | Program Once word 2 value                   |  |  |  |  |

| 101         | Program Once word 3 value                   |  |  |  |  |

Table 29-42. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash will return invalid data.

- Single bit fault correction and double bit fault detection within a 32-bit double word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and phrase program operation

- Ability to read the P-Flash memory while programming a word in the EEPROM memory

- Flexible protection scheme to prevent accidental program or erase of P-Flash memory

### 30.1.2.2 EEPROM Features

- 4Kbytes of EEPROM memory composed of one 4 Kbyte Flash block divided into 1024 sectors of 4 bytes

- Single bit fault correction and double bit fault detection within a word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and word program operation

- Protection scheme to prevent accidental program or erase of EEPROM memory

- Ability to program up to four words in a burst sequence

### 30.1.2.3 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

## 30.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 30-1.

| FCMD | Command                        | Function on EEPROM Memory                                                                                                                                                                                                                      |

|------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x08 | Erase All Blocks               | Erase all EEPROM (and P-Flash) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN<br>bits in the FPROT register and the DPOPEN bit in the EEPROT register are set prior to<br>launching the command. |

| 0x09 | Erase Flash Block              | Erase a EEPROM (or P-Flash) block.<br>An erase of the full EEPROM block is only possible when DPOPEN bit in the EEPROT register is set prior to launching the command.                                                                         |

| 0x0B | Unsecure Flash                 | Supports a method of releasing MCU security by erasing all EEPROM (and P-Flash) blocks and verifying that all EEPROM (and P-Flash) blocks are erased.                                                                                          |

| 0x0D | Set User Margin<br>Level       | Specifies a user margin read level for the EEPROM block.                                                                                                                                                                                       |

| 0x0E | Set Field Margin<br>Level      | Specifies a field margin read level for the EEPROM block (special modes only).                                                                                                                                                                 |

| 0x10 | Erase Verify<br>EEPROM Section | Verify that a given number of words starting at the address provided are erased.                                                                                                                                                               |

| 0x11 | Program<br>EEPROM              | Program up to four words in the EEPROM block.                                                                                                                                                                                                  |

| 0x12 | Erase EEPROM<br>Sector         | Erase all bytes in a sector of the EEPROM block.                                                                                                                                                                                               |

#### Table 31-29. EEPROM Commands

## 31.4.5 Allowed Simultaneous P-Flash and EEPROM Operations

Only the operations marked 'OK' in Table 31-30 are permitted to be run simultaneously on the Program Flash and EEPROM blocks. Some operations cannot be executed simultaneously because certain hardware resources are shared by the two memories. The priority has been placed on permitting Program Flash reads while program and erase operations execute on the EEPROM, providing read (P-Flash) while write (EEPROM) functionality.

|                          | EEPROM |                             |         |                 |                            |  |

|--------------------------|--------|-----------------------------|---------|-----------------|----------------------------|--|

| Program Flash            | Read   | Margin<br>Read <sup>1</sup> | Program | Sector<br>Erase | Mass<br>Erase <sup>2</sup> |  |

| Read                     |        | OK                          | OK      | OK              |                            |  |

| Margin Read <sup>1</sup> |        |                             |         |                 |                            |  |

| Program                  |        |                             |         |                 |                            |  |

| Sector Erase             |        |                             |         |                 |                            |  |

| Mass Erase <sup>2</sup>  |        |                             |         |                 | OK                         |  |

Table 31-30. Allowed P-Flash and EEPROM Simultaneous Operations

A 'Margin Read' is any read after executing the margin setting commands 'Set User Margin Level' or 'Set Field Margin Level' with anything but the 'normal' level specified. See the Note on margin settings in Section 31.4.6.12 and Section 31.4.6.13.

<sup>2</sup> The 'Mass Erase' operations are commands 'Erase All Blocks' and 'Erase Flash Block'

1

#### 240 KByte Flash Module (S12FTMRG240K2V1)

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

| Condit | ditions are shown in Table A-4 unless otherwise noted |                                                                                                                               |                     |      |                   |     |        |  |

|--------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------------------|-----|--------|--|

| NUM    | С                                                     | Rating                                                                                                                        |                     | Min  | Тур               | Max | Unit   |  |

|        | Program Flash Arrays                                  |                                                                                                                               |                     |      |                   |     |        |  |

| 1      | С                                                     | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after up to 10,000 program/erase cycles     | t <sub>NVMRET</sub> | 20   | 100 <sup>2</sup>  | _   | Years  |  |

| 2a     | С                                                     | Program Flash number of program/erase cycles (-40°C $\leq$ Tj $\leq$ 150°C)                                                   | n <sub>FLPE</sub>   | 10K  | 100K <sup>3</sup> | _   | Cycles |  |

| 2b     | С                                                     | Program Flash number of program/erase cycles (150°C $\leq$ Tj $\leq$ 160°C)                                                   | n <sub>FLPE</sub>   | 1K   | 100K <sup>3</sup> | _   | Cycles |  |

|        |                                                       | EEPROM Array                                                                                                                  |                     |      |                   |     |        |  |

| 3      | С                                                     | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$<br>after up to 100,000 program/erase cycles | t <sub>NVMRET</sub> | 5    | 100 <sup>2</sup>  | _   | Years  |  |

| 4      | С                                                     | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after up to 10,000 program/erase cycles     | t <sub>NVMRET</sub> | 10   | 100 <sup>2</sup>  | _   | Years  |  |

| 5      | С                                                     | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after less than 100 program/erase cycles    | t <sub>NVMRET</sub> | 20   | 100 <sup>2</sup>  | —   | Years  |  |

| 6a     | С                                                     | EEPROM number of program/erase cycles (-40°C $\leq$ Tj $\leq$ 150°C)                                                          | n <sub>FLPE</sub>   | 100K | 500K <sup>3</sup> | _   | Cycles |  |

| 6b     | С                                                     | EEPROM number of program/erase cycles (150°C $\leq$ Tj $\leq$ 160°C)                                                          | n <sub>FLPE</sub>   | 10K  | 500K <sup>3</sup> | _   | Cycles |  |

#### Table A-39. NVM Reliability Characteristics

<sup>1</sup> T<sub>Javg</sub> does not exceed 85°C in a typical temperature profile over the lifetime of a consumer, industrial or automotive application.

<sup>2</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how NXP defines Typical Data Retention, please refer to Engineering Bulletin EB618

<sup>3</sup> Spec table quotes typical endurance evaluated at 25°C for this product family. For additional information on how NXP defines Typical Endurance, please refer to Engineering Bulletin EB619.

# A.8 Phase Locked Loop

### A.8.1 Jitter Definitions

With each transition of the feedback clock, the deviation from the reference clock is measured and input voltage to the VCO is adjusted accordingly. The adjustment is done continuously with no abrupt changes in the VCOCLK frequency. Noise, voltage, temperature and other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real minimum and maximum clock periods as illustrated in Figure A-4.

# D.7 KGD Information

# **Bondpad Coordinates**

| Bond Post | Die Pad                                                                                                                                    | Die Pad                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | X Coordinate                                                                                                                               | Y Coordinate                                                                                                                                                                                                                                                                                                                                                                                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1         | -1832.06                                                                                                                                   | 1347.5                                                                                                                                                                                                                                                                                                                                                                                      | PJ[6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2         | -1832.06                                                                                                                                   | 1223.5                                                                                                                                                                                                                                                                                                                                                                                      | PJ[5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3         | -1832.06                                                                                                                                   | 1116.5                                                                                                                                                                                                                                                                                                                                                                                      | PJ[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4         | -1832.06                                                                                                                                   | 1009.5                                                                                                                                                                                                                                                                                                                                                                                      | PA[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5         | -1832.06                                                                                                                                   | 902.5                                                                                                                                                                                                                                                                                                                                                                                       | PA[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6         | -1832.06                                                                                                                                   | 795.5                                                                                                                                                                                                                                                                                                                                                                                       | PA[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7         | -1832.06                                                                                                                                   | 688.5                                                                                                                                                                                                                                                                                                                                                                                       | PA[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8         | -1832.06                                                                                                                                   | 603.5                                                                                                                                                                                                                                                                                                                                                                                       | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9         | -1832.06                                                                                                                                   | 496.5                                                                                                                                                                                                                                                                                                                                                                                       | VDDX1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10        | -1832.06                                                                                                                                   | 369                                                                                                                                                                                                                                                                                                                                                                                         | VDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11        | -1832.06                                                                                                                                   | 241.5                                                                                                                                                                                                                                                                                                                                                                                       | VSSX1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12        | -1832.06                                                                                                                                   | 136.5                                                                                                                                                                                                                                                                                                                                                                                       | PE[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13        | -1832.06                                                                                                                                   | 22.5                                                                                                                                                                                                                                                                                                                                                                                        | VSS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14        | -1832.06                                                                                                                                   | -91.5                                                                                                                                                                                                                                                                                                                                                                                       | PE[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15        | -1832.06                                                                                                                                   | -201.5                                                                                                                                                                                                                                                                                                                                                                                      | TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16        | -1832.06                                                                                                                                   | -311.5                                                                                                                                                                                                                                                                                                                                                                                      | PA[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17        | -1832.06                                                                                                                                   | -396.5                                                                                                                                                                                                                                                                                                                                                                                      | PA[5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18        | -1832.06                                                                                                                                   | -483.5                                                                                                                                                                                                                                                                                                                                                                                      | PA[6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 19        | -1832.06                                                                                                                                   | -578.5                                                                                                                                                                                                                                                                                                                                                                                      | PA[7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 20        | -1832.06                                                                                                                                   | -683.5                                                                                                                                                                                                                                                                                                                                                                                      | PJ[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21        | -1832.06                                                                                                                                   | -797.5                                                                                                                                                                                                                                                                                                                                                                                      | PJ[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22        | -1832.06                                                                                                                                   | -921.5                                                                                                                                                                                                                                                                                                                                                                                      | PJ[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23        | -1832.06                                                                                                                                   | -1054.5                                                                                                                                                                                                                                                                                                                                                                                     | PJ[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 24        | -1832.06                                                                                                                                   | -1196.5                                                                                                                                                                                                                                                                                                                                                                                     | BKGD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |