# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 86                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                            |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g128f0mllr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 18.1.1   | Glossary                                 | 570   |

|------|----------|------------------------------------------|-------|

|      | 18.1.2   | Block Diagram                            | 570   |

|      | 18.1.3   | Features                                 | 571   |

|      | 18.1.4   | Modes of Operation                       | 571   |

| 18.2 | External | Signal Description                       | 571   |

|      | 18.2.1   | RXCAN — CAN Receiver Input Pin           | . 571 |

|      | 18.2.2   | TXCAN — CAN Transmitter Output Pin       | . 572 |

|      | 18.2.3   | CAN System                               | . 572 |

| 18.3 | Memory   | <sup>7</sup> Map and Register Definition | . 572 |

|      |          | Module Memory Map                        |       |

|      | 18.3.2   | Register Descriptions                    | 574   |

|      | 18.3.3   | Programmer's Model of Message Storage    | 593   |

| 18.4 |          | nal Description                          |       |

|      | 18.4.1   | General                                  | 603   |

|      |          | Message Storage                          |       |

|      | 18.4.3   | Identifier Acceptance Filter             | 607   |

|      | 18.4.4   | Modes of Operation                       | 613   |

|      |          | Low-Power Options                        |       |

|      |          | Reset Initialization                     |       |

|      | 18.4.7   | Interrupts                               | 619   |

| 18.5 |          | ation/Application Information            |       |

|      |          | MSCAN initialization                     |       |

|      | 18.5.2   | Bus-Off Recovery                         | 621   |

# Chapter 19

# Pulse-Width Modulator (S12PWM8B8CV2)

| 19.1 | Introduction                           |  |

|------|----------------------------------------|--|

|      | 19.1.1 Features                        |  |

|      | 19.1.2 Modes of Operation              |  |

|      | 19.1.3 Block Diagram                   |  |

| 19.2 | External Signal Description            |  |

|      | 19.2.1 PWM7 - PWM0 — PWM Channel 7 - 0 |  |

| 19.3 | Memory Map and Register Definition     |  |

|      | 19.3.1 Module Memory Map               |  |

|      | 19.3.2 Register Descriptions           |  |

| 19.4 | Functional Description                 |  |

|      | 19.4.1 PWM Clock Select                |  |

|      | 19.4.2 PWM Channel Timers              |  |

|      | Resets                                 |  |

| 19.6 | Interrupts                             |  |

|      |                                        |  |

# Chapter 20 Serial Communication Interface (S12SCIV5)

20.1 Introduction .....

| Peripheral | 20 TSSOP | 32 LQFP | 48 QFN | 48 LQFP | 64 LQFP | 100 LQFP | KGD (Die) |

|------------|----------|---------|--------|---------|---------|----------|-----------|

| DAC0       | —        | _       | _      | Yes     | Yes     | Yes      | Yes       |

| DAC1       |          | -       | -      | Yes     | Yes     | Yes      | Yes       |

| ACMP       | Yes      | Yes     | Yes    | Yes     | Yes     | _        | _         |

| Total GPIO | 14       | 26      | 40     | 40      | 54      | 86       | 86        |

Table 1-2. Maximum Peripheral Availability per Package

# 1.2.2 Chip-Level Features

On-chip modules available within the family include the following features:

- S12 CPU core

- Up to 240 Kbyte on-chip flash with ECC

- Up to 4 Kbyte EEPROM with ECC

- Up to 11 Kbyte on-chip SRAM

- Phase locked loop (IPLL) frequency multiplier with internal filter

- 4–16 MHz amplitude controlled Pierce oscillator

- 1 MHz internal RC oscillator

- Timer module (TIM) supporting up to eight channels that provide a range of 16-bit input capture, output compare, counter, and pulse accumulator functions

- Pulse width modulation (PWM) module with up to eight x 8-bit channels

- Up to 16-channel, 10 or 12-bit resolution successive approximation analog-to-digital converter (ADC)

- Up to two 8-bit digital-to-analog converters (DAC)

- Up to one 5V analog comparator (ACMP)

- Up to three serial peripheral interface (SPI) modules

- Up to three serial communication interface (SCI) modules supporting LIN communications

- Up to one multi-scalable controller area network (MSCAN) module (supporting CAN protocol 2.0A/B)

- On-chip voltage regulator (VREG) for regulation of input supply and all internal voltages

- Autonomous periodic interrupt (API)

- Precision fixed voltage reference for ADC conversions

- Optional reference voltage attenuator module to increase ADC accuracy

# **1.3 Module Features**

The following sections provide more details of the modules implemented on the MC9S12G-Family family.

#### Port Integration Module (S12GPIMV1)

This section describes the signals available on each pin.

Although trying to enable multiple signals on a shared pin is not a proper use case in most applications, the resulting pin function will be determined by a predefined priority scheme as defined in 2.2.2 and 2.2.3.

Only enabled signals arbitrate for the pin and the highest priority defines its data direction and output value if used as output. Signals with programmable routing options are assumed to select the appropriate target pin to participate in the arbitration.

The priority is represented for each pin with shared signals from highest to lowest in the following format:

SignalA > SignalB > GPO

Here SignalA has priority over SignalB and general-purpose output function (GPO; represented by related port data register bit). The general-purpose output is always of lowest priority if no other signal is enabled.

Peripheral input signals on shared pins are always connected monitoring the pin level independent of their use.

| Field | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Port AD input data—<br>A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

#### Table 2-78. PTI1AD Register Field Descriptions

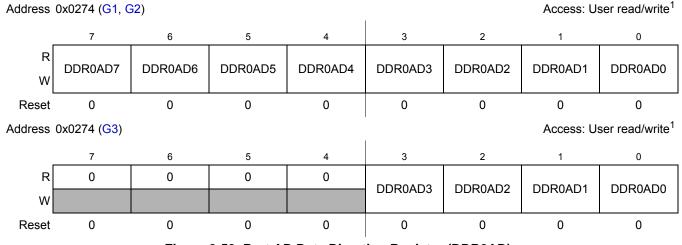

### 2.4.3.53 Port AD Data Direction Register (DDR0AD)

Figure 2-53. Port AD Data Direction Register (DDR0AD)

<sup>1</sup> Read: Anytime

Write: Anytime

#### Table 2-79. DDR0AD Register Field Descriptions

| Field         | Description                                                                                              |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7-0<br>DDR0AD | <b>Port AD data direction</b> —<br>This bit determines whether the associated pin is an input or output. |  |  |  |  |  |

|               | 1 Associated pin configured as output<br>0 Associated pin configured as input                            |  |  |  |  |  |

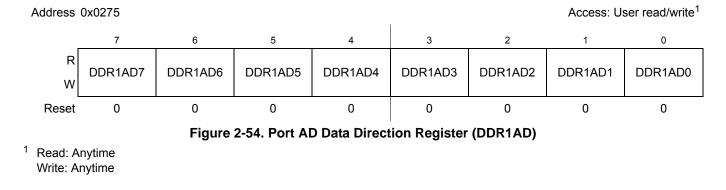

### 2.4.3.54 Port AD Data Direction Register (DDR1AD)

#### MC9S12G Family Reference Manual Rev.1.27

# Chapter 5 S12G Memory Map Controller (S12GMMCV1)

| _ | ev. No.<br>m No.) | Date<br>(Submitted By) | Sections<br>Affected | Substantial Change(s)           |

|---|-------------------|------------------------|----------------------|---------------------------------|

| 0 | 1.02              | 20-May 2010            |                      | Updates for S12VR48 and S12VR64 |

# 5.1 Introduction

The S12GMMC module controls the access to all internal memories and peripherals for the CPU12 and S12SBDM module. It regulates access priorities and determines the address mapping of the on-chip resources. Figure 5-1 shows a block diagram of the S12GMMC module.

# 5.1.1 Glossary

| Term                         | Definition                                                   |

|------------------------------|--------------------------------------------------------------|

| Local Addresses              | Address within the CPU12's Local Address Map (Figure 5-11)   |

| Global Address               | Address within the Global Address Map (Figure 5-11)          |

| Aligned Bus Access           | Bus access to an even address.                               |

| Misaligned Bus Access        | Bus access to an odd address.                                |

| NS                           | Normal Single-Chip Mode                                      |

| SS                           | Special Single-Chip Mode                                     |

| Unimplemented Address Ranges | Address ranges which are not mapped to any on-chip resource. |

| NVM                          | Non-volatile Memory; Flash or EEPROM                         |

| IFR                          | NVM Information Row. Refer to FTMRG Block Guide              |

#### Table 5-2. Glossary Of Terms

# 5.1.2 Overview

The S12GMMC connects the CPU12's and the S12SBDM's bus interfaces to the MCU's on-chip resources (memories and peripherals). It arbitrates the bus accesses and determines all of the MCU's memory maps. Furthermore, the S12GMMC is responsible for constraining memory accesses on secured devices and for selecting the MCU's functional mode.

| Global<br>Address | Register<br>Name |   | Bit 7                                                  | 6                                    | 5        | 4         | 3         | 2      | 1 | Bit 0 |

|-------------------|------------------|---|--------------------------------------------------------|--------------------------------------|----------|-----------|-----------|--------|---|-------|

| 0x3_FF09          | Reserved         | R | 0                                                      | 0                                    | 0        | 0         | 0         | 0      | 0 | 0     |

|                   |                  | W |                                                        |                                      |          |           |           |        |   |       |

| 0x3_FF0A          | Reserved         | R | 0                                                      | 0                                    | 0        | 0         | 0         | 0      | 0 | 0     |

|                   |                  | W |                                                        |                                      |          |           |           |        |   |       |

| 0x3_FF0B          | Reserved         | R | 0                                                      | 0                                    | 0        | 0         | 0         | 0      | 0 | 0     |

|                   |                  | W |                                                        |                                      |          |           |           |        |   |       |

|                   |                  |   | = Unimplemented, Reserved = Implemented (do not alter) |                                      |          |           |           | alter) |   |       |

|                   |                  |   | Х                                                      | = Indeterminate 0 = Always read zero |          |           |           |        |   |       |

|                   |                  |   | Figure                                                 | e 7-2. BDM                           | Register | Summary ( | continued | )      |   |       |

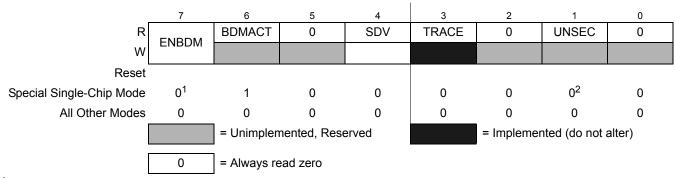

# 7.3.2.1 BDM Status Register (BDMSTS)

Register Global Address 0x3\_FF01

- <sup>1</sup> ENBDM is read as 1 by a debugging environment in special single chip mode when the device is not secured or secured but fully erased (Flash). This is because the ENBDM bit is set by the standard BDM firmware before a BDM command can be fully transmitted and executed.

- <sup>2</sup> UNSEC is read as 1 by a debugging environment in special single chip mode when the device is secured and fully erased, else it is 0 and can only be read if not secure (see also bit description).

#### Figure 7-3. BDM Status Register (BDMSTS)

Read: All modes through BDM operation when not secured

Write: All modes through BDM operation when not secured, but subject to the following:

- ENBDM should only be set via a BDM hardware command if the BDM firmware commands are needed. (This does not apply in special single chip mode).

- BDMACT can only be set by BDM hardware upon entry into BDM. It can only be cleared by the standard BDM firmware lookup table upon exit from BDM active mode.

- All other bits, while writable via BDM hardware or standard BDM firmware write commands, should only be altered by the BDM hardware or standard firmware lookup table as part of BDM command execution.

# 11.4 Functional Description

The ADC10B8C consists of an analog sub-block and a digital sub-block.

# 11.4.1 Analog Sub-Block

The analog sub-block contains all analog electronics required to perform a single conversion. Separate power supplies VDDA and VSSA allow to isolate noise of other MCU circuitry from the analog sub-block.

### 11.4.1.1 Sample and Hold Machine

The Sample and Hold Machine controls the storage and charge of the sample capacitor to the voltage level of the analog signal at the selected ADC input channel.

During the sample process the analog input connects directly to the storage node.

The input analog signals are unipolar and must be within the potential range of VSSA to VDDA.

During the hold process the analog input is disconnected from the storage node.

### 11.4.1.2 Analog Input Multiplexer

The analog input multiplexer connects one of the 8 external analog input channels to the sample and hold machine.

### 11.4.1.3 Analog-to-Digital (A/D) Machine

The A/D Machine performs analog to digital conversions. The resolution is program selectable to be either 8 or 10 bits. The A/D machine uses a successive approximation architecture. It functions by comparing the sampled and stored analog voltage with a series of binary coded discrete voltages.

By following a binary search algorithm, the A/D machine identifies the discrete voltage that is nearest to the sampled and stored voltage.

When not converting the A/D machine is automatically powered down.

Only analog input signals within the potential range of VRL to VRH (A/D reference potentials) will result in a non-railed digital output code.

# 11.4.2 Digital Sub-Block

This subsection describes some of the digital features in more detail. See Section 11.3.2, "Register Descriptions" for all details.

## 11.4.2.1 External Trigger Input

The external trigger feature allows the user to synchronize ATD conversions to an external event rather than relying only on software to trigger the ATD module when a conversion is about to take place. The external trigger signal (out of reset ATD channel 7, configurable in ATDCTL1) is programmable to be edge

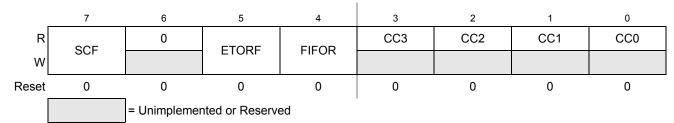

# 16.3.2.7 ATD Status Register 0 (ATDSTAT0)

This register contains the Sequence Complete Flag, overrun flags for external trigger and FIFO mode, and the conversion counter.

Module Base + 0x0006

Figure 16-9. ATD Status Register 0 (ATDSTAT0)

Read: Anytime

Write: Anytime (No effect on (CC3, CC2, CC1, CC0))

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SCF   | Sequence Complete Flag — This flag is set upon completion of a conversion sequence. If conversion sequences are continuously performed (SCAN=1), the flag is set after each one is completed. This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to SCF</li> <li>B) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>C) If AFFC=1 and a result register is read</li> <li>Conversion sequence not completed</li> <li>Conversion sequence has completed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5<br>ETORF | <ul> <li>External Trigger Overrun Flag — While in edge sensitive mode (ETRIGLE=0), if additional active edges are detected while a conversion sequence is in process the overrun flag is set. This flag is cleared when one of the following occurs:         <ul> <li>A) Write "1" to ETORF</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> </li> <li>No External trigger overrun error has occurred</li> <li>1 External trigger overrun error has occurred</li> </ul>                                                                                                                                                                                                                                                                                                                  |

| 4<br>FIFOR | Result Register Overrun Flag — This bit indicates that a result register has been written to before its associated conversion complete flag (CCF) has been cleared. This flag is most useful when using the FIFO mode because the flag potentially indicates that result registers are out of sync with the input channels. However, it is also practical for non-FIFO modes, and indicates that a result register has been overwritten before it has been read (i.e. the old data has been lost). This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to FIFOR</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>No overrun has occurred</li> <li>Overrun condition exists (result register has been written while associated CCFx flag was still set)</li> </ul> |

| Field          | Description                                                                                                                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AC[7:0] | Acceptance Code Bits — AC[7:0] comprise a user-defined sequence of bits with which the corresponding bits of the related identifier register (IDRn) of the receive message buffer are compared. The result of this comparison is then masked with the corresponding identifier mask register. |

#### Table 18-23. CANIDAR4–CANIDAR7 Register Field Descriptions

### 18.3.2.18 MSCAN Identifier Mask Registers (CANIDMR0–CANIDMR7)

The identifier mask register specifies which of the corresponding bits in the identifier acceptance register are relevant for acceptance filtering. To receive standard identifiers in 32 bit filter mode, it is required to program the last three bits (AM[2:0]) in the mask registers CANIDMR1 and CANIDMR5 to "don't care." To receive standard identifiers in 16 bit filter mode, it is required to program the last three bits (AM[2:0]) in the mask registers CANIDMR1 and CANIDMR5 to "don't care." To receive standard identifiers in 16 bit filter mode, it is required to program the last three bits (AM[2:0]) in the mask registers CANIDMR5, and CANIDMR7 to "don't care."

Module Base + 0x0014 to Module Base + 0x0017

Access: User read/write<sup>1</sup>

|        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AM7 | AM6 | AM5 | AM4 | AM3 | AM2 | AM1 | AM0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 18-22. MSCAN Identifier Mask Registers (First Bank) — CANIDMR0–CANIDMR3

#### <sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 18-24. CANIDMR0–CANIDMR3 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AM[7:0] | <ul> <li>Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.</li> <li>Match corresponding acceptance code register and identifier bits</li> <li>Ignore corresponding acceptance code register bit</li> </ul> |

#### Module Base + 0x001C to Module Base + 0x001F

|        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AM7 | AM6 | AM5 | AM4 | AM3 | AM2 | AM1 | AM0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 18-23. MSCAN Identifier Mask Registers (Second Bank) — CANIDMR4–CANIDMR7

MC9S12G Family Reference Manual Rev.1.27

Access: User read/write<sup>1</sup>

Scalable Controller Area Network (S12MSCANV3)

# 18.4.2 Message Storage

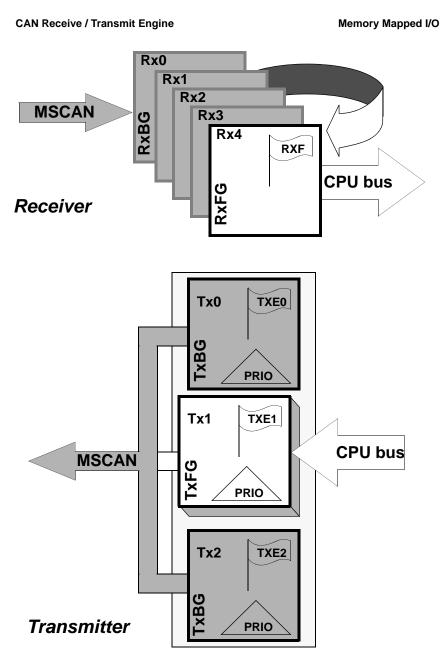

Figure 18-39. User Model for Message Buffer Organization

The MSCAN facilitates a sophisticated message storage system which addresses the requirements of a broad range of network applications.

### 18.4.2.1 Message Transmit Background

Modern application layer software is built upon two fundamental assumptions:

# 18.4.3.1 Protocol Violation Protection

The MSCAN protects the user from accidentally violating the CAN protocol through programming errors. The protection logic implements the following features:

- The receive and transmit error counters cannot be written or otherwise manipulated.

- All registers which control the configuration of the MSCAN cannot be modified while the MSCAN is on-line. The MSCAN has to be in Initialization Mode. The corresponding INITRQ/INITAK handshake bits in the CANCTL0/CANCTL1 registers (see Section 18.3.2.1, "MSCAN Control Register 0 (CANCTL0)") serve as a lock to protect the following registers:

- MSCAN control 1 register (CANCTL1)

- MSCAN bus timing registers 0 and 1 (CANBTR0, CANBTR1)

- MSCAN identifier acceptance control register (CANIDAC)

- MSCAN identifier acceptance registers (CANIDAR0–CANIDAR7)

- MSCAN identifier mask registers (CANIDMR0–CANIDMR7)

- The TXCAN is immediately forced to a recessive state when the MSCAN goes into the power down mode or initialization mode (see Section 18.4.5.6, "MSCAN Power Down Mode," and Section 18.4.4.5, "MSCAN Initialization Mode").

- The MSCAN enable bit (CANE) is writable only once in normal system operation modes, which provides further protection against inadvertently disabling the MSCAN.

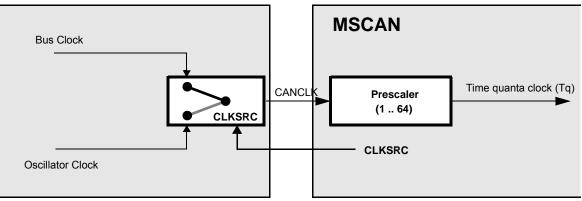

# 18.4.3.2 Clock System

Figure 18-43 shows the structure of the MSCAN clock generation circuitry.

Figure 18-43. MSCAN Clocking Scheme

The clock source bit (CLKSRC) in the CANCTL1 register (18.3.2.2/18-576) defines whether the internal CANCLK is connected to the output of a crystal oscillator (oscillator clock) or to the bus clock.

The clock source has to be chosen such that the tight oscillator tolerance requirements (up to 0.4%) of the CAN protocol are met. Additionally, for high CAN bus rates (1 Mbps), a 45% to 55% duty cycle of the clock is required.

If the bus clock is generated from a PLL, it is recommended to select the oscillator clock rather than the bus clock due to jitter considerations, especially at the faster CAN bus rates.

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 20-18 summarizes the results of the data bit samples.

| RT8, RT9, and RT10 Samples | Data Bit Determination | Noise Flag |

|----------------------------|------------------------|------------|

| 000                        | 0                      | 0          |

| 001                        | 0                      | 1          |

| 010                        | 0                      | 1          |

| 011                        | 1                      | 1          |

| 100                        | 0                      | 1          |

| 101                        | 1                      | 1          |

| 110                        | 1                      | 1          |

| 111                        | 1                      | 0          |

Table 20-18. Data Bit Recovery

### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are logic 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit (logic 0).

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 20-19 summarizes the results of the stop bit samples.

| RT8, RT9, and RT10 Samples | Framing Error Flag | Noise Flag |

|----------------------------|--------------------|------------|

| 000                        | 1                  | 0          |

| 001                        | 1                  | 1          |

| 010                        | 1                  | 1          |

| 011                        | 0                  | 1          |

| 100                        | 1                  | 1          |

| 101                        | 0                  | 1          |

| 110                        | 0                  | 1          |

| 111                        | 0                  | 0          |

Table 20-19. Stop Bit Recovery

In Figure 20-22 the verification samples RT3 and RT5 determine that the first low detected was noise and not the beginning of a start bit. The RT clock is reset and the start bit search begins again. The noise flag is not set because the noise occurred before the start bit was found.

# Chapter 23 Timer Module (TIM16B8CV3)

| V03.00 | Jan. 28, 2009 |                                                      | Initial version                                                                                                                                                                                                                                                                                                                               |

|--------|---------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V03.01 | Aug. 26, 2009 | 23.3.2.2/23-744,<br>23.3.2.3/23-744,                 | <ul> <li>Correct typo: TSCR -&gt;TSCR1;</li> <li>Correct typo: ECTxxx-&gt;TIMxxx</li> <li>Correct reference: Figure 23-25 -&gt; Figure 23-30</li> <li>Add description, "a counter overflow when TTOV[7] is set", to be the condition of channel 7 override event.</li> <li>Phrase the description of OC7M to make it more explicit</li> </ul> |

| V03.02 | Apri,12,2010  | 23.3.2.8/23-748<br>23.3.2.11/23-751<br>23.4.3/23-760 | -Add Table 23-10<br>-update TCRE bit description<br>-add Figure 23-31                                                                                                                                                                                                                                                                         |

| V03.03 | Jan,14,2013   |                                                      | -single source generate different channel guide                                                                                                                                                                                                                                                                                               |

#### Table 23-1. Revision History

# 23.1 Introduction

The basic scalable timer consists of a 16-bit, software-programmable counter driven by a flexible programmable prescaler.

This timer can be used for many purposes, including input waveform measurements while simultaneously generating an output waveform. Pulse widths can vary from microseconds to many seconds.

This timer could contain up to 8 input capture/output compare channels with one pulse accumulator available only on channel 7. The input capture function is used to detect a selected transition edge and record the time. The output compare function is used for generating output signals or for timer software delays. The 16-bit pulse accumulator is used to operate as a simple event counter or a gated time accumulator. The pulse accumulator shares timer channel 7 when the channel is available and when in event mode.

A full access for the counter registers or the input capture/output compare registers should take place in one clock cycle. Accessing high byte and low byte separately for all of these registers may not yield the same result as accessing them in one word.

## 23.1.1 Features

The TIM16B8CV3 includes these distinctive features:

- Up to 8 channels available. (refer to device specification for exact number)

- All channels have same input capture/output compare functionality.

#### 16 KByte Flash Module (S12FTMRG16K1V1)

All bits in the FRSV6 register read 0 and are not writable.

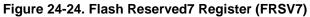

### 24.3.2.19 Flash Reserved7 Register (FRSV7)

This Flash register is reserved for factory testing.

All bits in the FRSV7 register read 0 and are not writable.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 26-27)                      |

|          |           | Set if an invalid global address [17:16] is supplied see Table 26-3)                |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 26-49. Erase P-Flash Sector Command Error Handling

## 26.4.6.10 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and EEPROM memory space and, if the erase is successful, will release security.

Table 26-50. Unsecure Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |

|-------------|------------------|--------------|--|

| 000         | 0x0B             | Not required |  |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and EEPROM memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security state. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag is set after the Unsecure Flash operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 26-27)                      |

| FSTAT    | FPVIOL    | Set if any area of the P-Flash or EEPROM memory is protected                        |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 26-51. Unsecure Flash Command Error Handling

### 26.4.6.11 Verify Backdoor Access Key Command

The Verify Backdoor Access Key command will only execute if it is enabled by the KEYEN bits in the FSEC register (see Table 26-10). The Verify Backdoor Access Key command releases security if user-supplied keys match those stored in the Flash security bytes of the Flash configuration field (see

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 27-55.

| CCOB<br>(CCOBIX=001) | Level Description                |

|----------------------|----------------------------------|

| 0x0000               | Return to Normal Level           |

| 0x0001               | User Margin-1 Level <sup>1</sup> |

| 0x0002               | User Margin-0 Level <sup>2</sup> |

### Table 27-55. Valid Set User Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### Table 27-56. Set User Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                              |

|----------|-----------|------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                  |

|          |           | Set if command not available in current mode (see Table 27-27)               |

|          |           | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 27-34) |

| FSTAT    |           | Set if an invalid margin level setting is supplied                           |

|          | FPVIOL    | None                                                                         |

|          | MGSTAT1   | None                                                                         |

|          | MGSTAT0   | None                                                                         |

### NOTE

User margin levels can be used to check that Flash memory contents have adequate margin for normal level read operations. If unexpected results are encountered when checking Flash memory contents at user margin levels, a potential loss of information has been detected.

| Register | Error Bit | Error Condition                                                             |  |  |  |  |  |

|----------|-----------|-----------------------------------------------------------------------------|--|--|--|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                 |  |  |  |  |  |

|          |           | Set if command not available in current mode (see Table 27-27)              |  |  |  |  |  |

|          |           | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 27-3- |  |  |  |  |  |

| FSTAT    |           | Set if an invalid margin level setting is supplied                          |  |  |  |  |  |

|          | FPVIOL    | None                                                                        |  |  |  |  |  |

|          | MGSTAT1   | None                                                                        |  |  |  |  |  |

|          | MGSTAT0   | None                                                                        |  |  |  |  |  |

Table 27-59. Set Field Margin Level Command Error Handling

### CAUTION

Field margin levels must only be used during verify of the initial factory programming.

### NOTE

Field margin levels can be used to check that Flash memory contents have adequate margin for data retention at the normal level setting. If unexpected results are encountered when checking Flash memory contents at field margin levels, the Flash memory contents should be erased and reprogrammed.

# 27.4.6.14 Erase Verify EEPROM Section Command

The Erase Verify EEPROM Section command will verify that a section of code in the EEPROM is erased. The Erase Verify EEPROM Section command defines the starting point of the data to be verified and the number of words.

| CCOBIX[2:0] | FCCOB Parameters                                       |                                                           |  |  |  |

|-------------|--------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| 000         | 0x10                                                   | Global address [17:16] to<br>identify the EEPROM<br>block |  |  |  |

| 001         | Global address [15:0] of the first word to be verified |                                                           |  |  |  |

| 010         | Number of words to be verified                         |                                                           |  |  |  |

Table 27-60. Erase Verify EEPROM Section Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Verify EEPROM Section command, the Memory Controller will verify the selected section of EEPROM memory is erased. The CCIF flag will set after the Erase Verify EEPROM Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

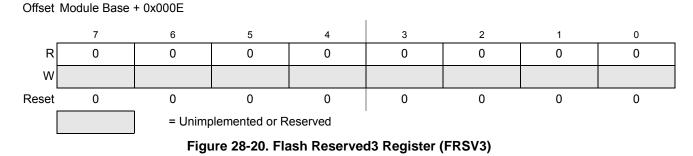

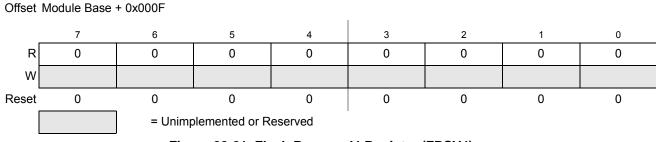

All bits in the FRSV3 register read 0 and are not writable.

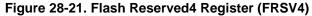

### 28.3.2.15 Flash Reserved4 Register (FRSV4)

This Flash register is reserved for factory testing.

All bits in the FRSV4 register read 0 and are not writable.

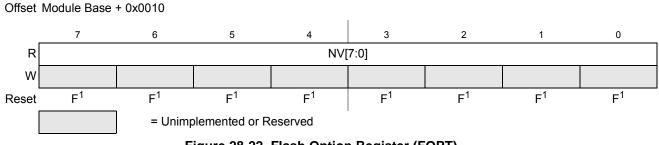

# 28.3.2.16 Flash Option Register (FOPT)

The FOPT register is the Flash option register.

<sup>1</sup> Loaded from IFR Flash configuration field, during reset sequence.

All bits in the FOPT register are readable but are not writable.

During the reset sequence, the FOPT register is loaded from the Flash nonvolatile byte in the Flash configuration field at global address  $0x_3$ \_FF0E located in P-Flash memory (see Table 28-4) as indicated by reset condition F in Figure 28-22. If a double bit fault is detected while reading the P-Flash phrase containing the Flash nonvolatile byte during the reset sequence, all bits in the FOPT register will be set.

#### 240 KByte Flash Module (S12FTMRG240K2V1)

| Address<br>& Name |                             | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|-------------------|-----------------------------|--------|--------|--------|--------|--------|--------|-------|-------|

| 0x000A<br>FCCOBHI | R<br>W                      | CCOB15 | CCOB14 | CCOB13 | CCOB12 | CCOB11 | CCOB10 | CCOB9 | CCOB8 |

| 0x000B<br>FCCOBLO | R<br>W                      | CCOB7  | CCOB6  | CCOB5  | CCOB4  | CCOB3  | CCOB2  | CCOB1 | CCOB0 |

| 0x000C            | R                           | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| FRSV1             | W                           |        |        |        |        |        |        |       |       |

| 0x000D<br>FRSV2   | R                           | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

|                   | W                           |        |        |        |        |        |        |       |       |

| 0x000E<br>FRSV3   | R                           | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

|                   | W                           |        |        |        |        |        |        |       |       |

| 0x000F            | R                           | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| FRSV4             | W                           |        |        |        |        |        |        |       |       |

| 0x0010            | R                           | NV7    | NV6    | NV5    | NV4    | NV3    | NV2    | NV1   | NV0   |

| FOPT              | W                           |        |        |        |        |        |        |       |       |

| 0x0011            | R                           | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| FRSV5             | W                           |        |        |        |        |        |        |       |       |

| 0x0012            | R                           | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| FRSV6             | W                           |        |        |        |        |        |        |       |       |

| 0x0013            | R                           | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| FRSV7             | W                           |        |        |        |        |        |        |       |       |

|                   | = Unimplemented or Reserved |        |        |        |        |        |        |       |       |

## 31.3.2.1 Flash Clock Divider Register (FCLKDIV)

The FCLKDIV register is used to control timed events in program and erase algorithms.

MC9S12G Family Reference Manual Rev.1.27

**Electrical Characteristics**

# A.14 MSCAN

| Conditions are shown in Table A-4 unless otherwise noted |   |                                      |                  |     |     |     |      |  |

|----------------------------------------------------------|---|--------------------------------------|------------------|-----|-----|-----|------|--|

| Num                                                      | С | Rating                               | Symbol           | Min | Тур | Max | Unit |  |

| 1                                                        | Ρ | MSCAN wakeup dominant pulse filtered | t <sub>WUP</sub> | _   | —   | 1.5 | μS   |  |

| 2                                                        | Ρ | MSCAN wakeup dominant pulse pass     | t <sub>WUP</sub> | 5   |     |     | μS   |  |