# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 54                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g128f0vlh |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| PP3-PP2 | <ul> <li>Except 20 TSSOP: The PWM channels 3 and 2 signal are mapped to these pins when used with the PWM function. The enabled PWM channel forces the I/O state to be an output.</li> <li>Except 20 TSSOP: The ADC ETRIG 3 and 2 signal are mapped to these pins when used with the ADC function. The enabled external trigger function has no effect on the I/O state. Refer to Section 2.6.4, "ADC External Triggers ETRIG3-0".</li> <li>Except 20 TSSOP: Pin interrupts can be generated if enabled in input or output mode.</li> <li>Signal priority: Except 20 TSSOP: PWM &gt; GPO</li> </ul>                                                                                                                                                                                                                                                                                   |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PP1     | <ul> <li>Except 20 TSSOP: The PWM channel 1 signal is mapped to this pin when used with the PWM function.<br/>The enabled PWM channel forces the I/O state to be an output.</li> <li>Except 100 LQFP and 20 TSSOP: The ECLKX2 signal is mapped to this pin when used with the external clock function. The enabled ECLKX2 forces the I/O state to an output.</li> <li>Except 20 TSSOP: The ADC ETRIG1 signal is mapped to this pin when used with the ADC function.<br/>The enabled external trigger function has no effect on the I/O state. Refer to Section 2.6.4, "ADC External Triggers ETRIG3-0".</li> <li>Except 20 TSSOP: Pin interrupts can be generated if enabled in input or output mode.</li> <li>Signal priority:<br/>Except 100 LQFP and 20 TSSOP: PWM1 &gt; ECLKX2 &gt; GPO 100 LQFP: PWM1 &gt; GPO</li> </ul>                                                        |

| PP0     | <ul> <li>Except 20 TSSOP: The PWM channel 0 signal is mapped to this pin when used with the PWM function.<br/>The enabled PWM channel forces the I/O state to be an output.</li> <li>Except 100 LQFP and 20 TSSOP: The API_EXTCLK signal is mapped to this pin when used with the external clock function. If the Autonomous Periodic Interrupt clock is enabled and routed here the I/O state is forced to output.</li> <li>Except 20 TSSOP: The ADC ETRIGO signal is mapped to this pin when used with the ADC function. The enabled external trigger function has no effect on the I/O state. Refer to Section 2.6.4, "ADC External Triggers ETRIG3-0".</li> <li>Except 20 TSSOP: Pin interrupts can be generated if enabled in input or output mode.</li> <li>Signal priority:<br/>Except 100 LQFP and 20 TSSOP: PWM0 &gt; API_EXTCLK &gt; GPO 100 LQFP: PWM0 &gt; GPO</li> </ul> |

### Table 2-14. Port P Pins PP7-0 (continued)

#### S12G Memory Map Controller (S12GMMCV1)

#### Interrupt Module (S12SINTV1)

- 2-58 I bit maskable interrupt vector requests (at addresses vector base + 0x0082-0x00F2).

- I bit maskable interrupts can be nested.

- One X bit maskable interrupt vector request (at address vector base + 0x00F4).

- One non-maskable software interrupt request (SWI) or background debug mode vector request (at address vector base + 0x00F6).

- One non-maskable unimplemented op-code trap (TRAP) vector (at address vector base + 0x00F8).

- Three system reset vectors (at addresses 0xFFFA–0xFFFE).

- Determines the highest priority interrupt vector requests, drives the vector to the bus on CPU request

- Wakes up the system from stop or wait mode when an appropriate interrupt request occurs.

### 6.1.3 Modes of Operation

• Run mode

This is the basic mode of operation.

• Wait mode

In wait mode, the clock to the INT module is disabled. The INT module is however capable of waking-up the CPU from wait mode if an interrupt occurs. Please refer to Section 6.5.3, "Wake Up from Stop or Wait Mode" for details.

• Stop Mode

In stop mode, the clock to the INT module is disabled. The INT module is however capable of waking-up the CPU from stop mode if an interrupt occurs. Please refer to Section 6.5.3, "Wake Up from Stop or Wait Mode" for details.

• Freeze mode (BDM active)

In freeze mode (BDM active), the interrupt vector base register is overridden internally. Please refer to Section 6.3.1.1, "Interrupt Vector Base Register (IVBR)" for details.

# 6.1.4 Block Diagram

Figure 6-1 shows a block diagram of the INT module.

<sup>1.</sup> The vector base is a 16-bit address which is accumulated from the contents of the interrupt vector base register (IVBR, used as upper byte) and 0x00 (used as lower byte).

If the X bit maskable interrupt request is used to wake-up the MCU with the X bit in the CCR set, the associated ISR is not called. The CPU then resumes program execution with the instruction following the WAI or STOP instruction. This features works following the same rules like any interrupt request, that is care must be taken that the X interrupt request used for wake-up remains active at least until the system begins execution of the instruction following the WAI or STOP instruction; otherwise, wake-up may not occur.

#### S12S Debug Module (S12SDBGV2)

If the comparator register contents coincide with the SWI/BDM vector address then an SWI in user code could coincide with a DBG breakpoint. The CPU ensures that BDM requests have a higher priority than SWI requests. Returning from the BDM/SWI service routine care must be taken to avoid a repeated breakpoint at the same address.

Should a tagged or forced breakpoint coincide with a BGND in user code, then the instruction that follows the BGND instruction is the first instruction executed when normal program execution resumes.

### NOTE

When program control returns from a tagged breakpoint using an RTI or BDM GO command without program counter modification it returns to the instruction whose tag generated the breakpoint. To avoid a repeated breakpoint at the same location reconfigure the DBG module in the SWI routine, if configured for an SWI breakpoint, or over the BDM interface by executing a TRACE command before the GO to increment the program flow past the tagged instruction.

# 8.5 Application Information

### 8.5.1 State Machine scenarios

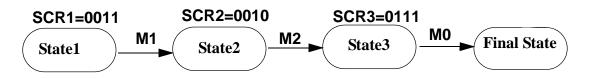

Defining the state control registers as SCR1,SCR2, SCR3 and M0,M1,M2 as matches on channels 0,1,2 respectively. SCR encoding supported by S12SDBGV1 are shown in black. SCR encoding supported only in S12SDBGV2 are shown in red. For backwards compatibility the new scenarios use a 4th bit in each SCR register. Thus the existing encoding for SCRx[2:0] is not changed.

# 8.5.2 Scenario 1

A trigger is generated if a given sequence of 3 code events is executed.

Figure 8-27. Scenario 1

Scenario 1 is possible with S12SDBGV1 SCR encoding

### NOTE

Care should be taken to ensure that the bus frequency does not exceed the specified maximum when frequency modulation is enabled.

### Table 10-7. CPMUPLL Field Descriptions

| Field | Description                                                                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | PLL <b>Frequency Modulation Enable Bits</b> — FM1 and FM0 enable frequency modulation on the VCOCLK. This is to reduce noise emission. The modulation frequency is $f_{ref}$ divided by 16. See Table 10-8 for coding. |

| FM1 | FM0 | FM Amplitude /<br>f <sub>VCO</sub> Variation |  |  |  |

|-----|-----|----------------------------------------------|--|--|--|

| 0   | 0   | FM off                                       |  |  |  |

| 0   | 1   | ±1%                                          |  |  |  |

| 1   | 0   | ±2%                                          |  |  |  |

| 1   | 1   | ±4%                                          |  |  |  |

### Table 10-8. FM Amplitude selection

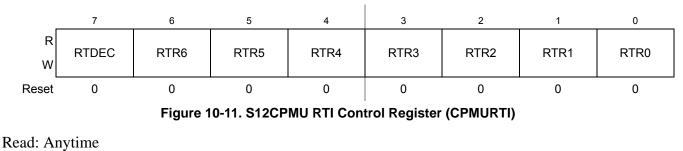

### 10.3.2.8 S12CPMU RTI Control Register (CPMURTI)

This register selects the time-out period for the Real Time Interrupt.

The clock source for the RTI is either IRCCLK or OSCCLK depending on the setting of the RTIOSCSEL bit. In Stop Mode with PSTP=1 (Pseudo Stop Mode) and RTIOSCSEL=1 the RTI continues to run, else the RTI counter halts in Stop Mode.

0x003B

Write: Anytime

# 14.5 Resets

At reset the ADC12B12C is in a power down state. The reset state of each individual bit is listed within the Register Description section (see Section 14.3.2, "Register Descriptions") which details the registers and their bit-field.

# 14.6 Interrupts

The interrupts requested by the ADC12B12C are listed in Table 14-24. Refer to MCU specification for related vector address and priority.

| Interrupt Source            | CCR<br>Mask | Local Enable      |  |  |

|-----------------------------|-------------|-------------------|--|--|

| Sequence Complete Interrupt | l bit       | ASCIE in ATDCTL2  |  |  |

| Compare Interrupt           | l bit       | ACMPIE in ATDCTL2 |  |  |

### Table 14-24. ATD Interrupt Vectors

See Section 14.3.2, "Register Descriptions" for further details.

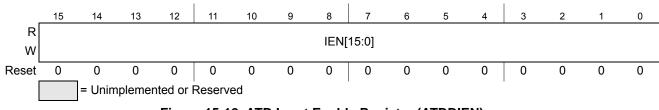

# 15.3.2.10 ATD Input Enable Register (ATDDIEN)

Module Base + 0x000C

Figure 15-12. ATD Input Enable Register (ATDDIEN)

### Read: Anytime

Write: Anytime

### Table 15-19. ATDDIEN Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>IEN[15:0] | <ul> <li>ATD Digital Input Enable on channel x (x= 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) — This bit controls the digital input buffer from the analog input pin (ANx) to the digital data register.</li> <li>0 Disable digital input buffer to ANx pin</li> <li>1 Enable digital input buffer on ANx pin.</li> <li>Note: Setting this bit will enable the corresponding digital input buffer continuously. If this bit is set while simultaneously using it as an analog port, there is potentially increased power consumption because the digital input buffer maybe in the linear region.</li> </ul> |

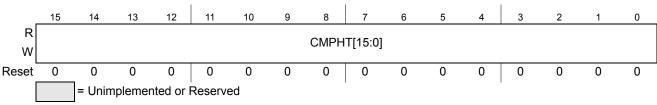

# 15.3.2.11 ATD Compare Higher Than Register (ATDCMPHT)

Writes to this register will abort current conversion sequence.

### Read: Anytime

Write: Anytime

Module Base + 0x000E

Figure 15-13. ATD Compare Higher Than Register (ATDCMPHT)

### Table 15-20. ATDCMPHT Field Descriptions

| Field       | Description                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

| 15–0        | Compare Operation Higher Than Enable for conversion number <i>n</i> ( <i>n</i> = 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5,       |

| CMPHT[15:0] | 4, 3, 2, 1, 0) of a Sequence ( <i>n conversion number, NOT channel number!</i> ) — This bit selects the operator              |

|             | for comparison of conversion results.                                                                                         |

|             | 0 If result of conversion <i>n</i> is <b>lower or same than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2 |

|             | 1 If result of conversion <i>n</i> is <b>higher than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2        |

#### MC9S12G Family Reference Manual Rev.1.27

#### Scalable Controller Area Network (S12MSCANV3)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>SLPAK  | <ul> <li>Sleep Mode Acknowledge — This flag indicates whether the MSCAN module has entered sleep mode (see Section 18.4.5.5, "MSCAN Sleep Mode"). It is used as a handshake flag for the SLPRQ sleep mode request. Sleep mode is active when SLPRQ = 1 and SLPAK = 1. Depending on the setting of WUPE, the MSCAN will clear the flag if it detects activity on the CAN bus while in sleep mode.</li> <li>0 Running — The MSCAN operates normally</li> <li>1 Sleep mode active — The MSCAN has entered sleep mode</li> </ul>                                                                                                  |

| 0<br>INITAK | <ul> <li>Initialization Mode Acknowledge — This flag indicates whether the MSCAN module is in initialization mode (see Section 18.4.4.5, "MSCAN Initialization Mode"). It is used as a handshake flag for the INITRQ initialization mode request. Initialization mode is active when INITRQ = 1 and INITAK = 1. The registers CANCTL1, CANBTR0, CANBTR1, CANIDAC, CANIDAR0–CANIDAR7, and CANIDMR0–CANIDMR7 can be written only by the CPU when the MSCAN is in initialization mode.</li> <li>Running — The MSCAN operates normally</li> <li>Initialization mode active — The MSCAN has entered initialization mode</li> </ul> |

#### Table 18-4. CANCTL1 Register Field Descriptions (continued)

# 18.3.2.3 MSCAN Bus Timing Register 0 (CANBTR0)

The CANBTR0 register configures various CAN bus timing parameters of the MSCAN module.

Module Base + 0x0002

Access: User read/write<sup>1</sup>

|        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

| R<br>W | SJW1 | SJW0 | BRP5 | BRP4 | BRP3 | BRP2 | BRP1 | BRP0 |

| Reset: | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### Figure 18-6. MSCAN Bus Timing Register 0 (CANBTR0)

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 18-5. CANBTR0 Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                           |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6<br>SJW[1:0] | <b>Synchronization Jump Width</b> — The synchronization jump width defines the maximum number of time quanta (Tq) clock cycles a bit can be shortened or lengthened to achieve resynchronization to data transitions on the CAN bus (see Table 18-6). |

| 5-0<br>BRP[5:0] | <b>Baud Rate Prescaler</b> — These bits determine the time quanta (Tq) clock which is used to build up the bit timing (see Table 18-7).                                                                                                               |

#### Table 18-6. Synchronization Jump Width

| SJW1 | SJW0 | Synchronization Jump Width |

|------|------|----------------------------|

| 0    | 0    | 1 Tq clock cycle           |

| 0    | 1    | 2 Tq clock cycles          |

| 1    | 0    | 3 Tq clock cycles          |

| 1    | 1    | 4 Tq clock cycles          |

#### Scalable Controller Area Network (S12MSCANV3)

| Module Base + 0x00XF Access: User read/write <sup>1</sup> |      |      |      |      |      |      |      | er read/write <sup>1</sup> |  |  |

|-----------------------------------------------------------|------|------|------|------|------|------|------|----------------------------|--|--|

|                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0                          |  |  |

| R                                                         | TSR7 | TSR6 | TSR5 | TSR4 | TSR3 | TSR2 | TSR1 | TSR0                       |  |  |

| W                                                         |      |      |      |      |      |      |      |                            |  |  |

| Reset:                                                    | х    | х    | х    | х    | х    | х    | х    | х                          |  |  |

|                                                           |      |      |      |      |      |      |      |                            |  |  |

Figure 18-38. Time Stamp Register — Low Byte (TSRL)

<sup>1</sup> Read: or transmit buffers: Anytime when TXEx flag is set (see Section 18.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 18.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). For receive buffers: Anytime when RXF is set. Write: Unimplemented

# 18.4 Functional Description

### 18.4.1 General

This section provides a complete functional description of the MSCAN.

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>FE | <ul> <li>Framing Error Flag — FE is set when a logic 0 is accepted as the stop bit. FE bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. FE inhibits further data reception until it is cleared. Clear FE by reading SCI status register 1 (SCISR1) with FE set and then reading the SCI data register low (SCIDRL).</li> <li>0 No framing error</li> <li>1 Framing error</li> </ul> |

| 0<br>PF | <ul> <li>Parity Error Flag — PF is set when the parity enable bit (PE) is set and the parity of the received data does not match the parity type bit (PT). PF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear PF by reading SCI status register 1 (SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No parity error</li> <li>1 Parity error</li> </ul>   |

# 20.3.2.8 SCI Status Register 2 (SCISR2)

Module Base + 0x0005

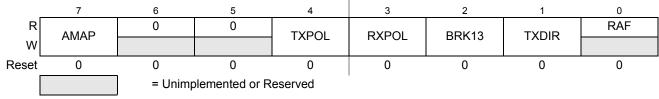

Figure 20-11. SCI Status Register 2 (SCISR2)

Read: Anytime

Write: Anytime

### Table 20-12. SCISR2 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>AMAP  | Alternative Map — This bit controls which registers sharing the same address space are accessible. In the reset condition the SCI behaves as previous versions. Setting AMAP=1 allows the access to another set of control and status registers and hides the baud rate and SCI control Register 1.<br>0 The registers labelled SCIBDH (0x0000),SCIBDL (0x0001), SCICR1 (0x0002) are accessible<br>1 The registers labelled SCIASR1 (0x0000),SCIACR1 (0x0001), SCIACR2 (0x00002) are accessible                                                                                                      |

| 4<br>TXPOL | <ul> <li>Transmit Polarity — This bit control the polarity of the transmitted data. In NRZ format, a one is represented by a mark and a zero is represented by a space for normal polarity, and the opposite for inverted polarity. In IrDA format, a zero is represented by short high pulse in the middle of a bit time remaining idle low for a one for normal polarity, and a zero is represented by short low pulse in the middle of a bit time remaining idle high for a one for inverted polarity.</li> <li>Normal polarity.</li> <li>Inverted polarity</li> <li>Inverted polarity</li> </ul> |

# Chapter 23 Timer Module (TIM16B8CV3)

| V03.00 | Jan. 28, 2009 |                                                      | Initial version                                                                                                                                                                                                                                                                                                                               |

|--------|---------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V03.01 | Aug. 26, 2009 | 23.3.2.2/23-744,<br>23.3.2.3/23-744,                 | <ul> <li>Correct typo: TSCR -&gt;TSCR1;</li> <li>Correct typo: ECTxxx-&gt;TIMxxx</li> <li>Correct reference: Figure 23-25 -&gt; Figure 23-30</li> <li>Add description, "a counter overflow when TTOV[7] is set", to be the condition of channel 7 override event.</li> <li>Phrase the description of OC7M to make it more explicit</li> </ul> |

| V03.02 | Apri,12,2010  | 23.3.2.8/23-748<br>23.3.2.11/23-751<br>23.4.3/23-760 | -Add Table 23-10<br>-update TCRE bit description<br>-add Figure 23-31                                                                                                                                                                                                                                                                         |

| V03.03 | Jan,14,2013   |                                                      | -single source generate different channel guide                                                                                                                                                                                                                                                                                               |

### Table 23-1. Revision History

# 23.1 Introduction

The basic scalable timer consists of a 16-bit, software-programmable counter driven by a flexible programmable prescaler.

This timer can be used for many purposes, including input waveform measurements while simultaneously generating an output waveform. Pulse widths can vary from microseconds to many seconds.

This timer could contain up to 8 input capture/output compare channels with one pulse accumulator available only on channel 7. The input capture function is used to detect a selected transition edge and record the time. The output compare function is used for generating output signals or for timer software delays. The 16-bit pulse accumulator is used to operate as a simple event counter or a gated time accumulator. The pulse accumulator shares timer channel 7 when the channel is available and when in event mode.

A full access for the counter registers or the input capture/output compare registers should take place in one clock cycle. Accessing high byte and low byte separately for all of these registers may not yield the same result as accessing them in one word.

# 23.1.1 Features

The TIM16B8CV3 includes these distinctive features:

- Up to 8 channels available. (refer to device specification for exact number)

- All channels have same input capture/output compare functionality.

# Chapter 25 32 KByte Flash Module (S12FTMRG32K1V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected                                                          | Description of Changes                                                                            |

|--------------------|------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| V01.04             | 17 Jun 2010      | 25.4.6.1/25-846<br>25.4.6.2/25-847<br>25.4.6.3/25-847<br>25.4.6.14/25-85<br>7 | Clarify Erase Verify Commands Descriptions related to the bits MGSTAT[1:0] of the register FSTAT. |

| V01.05             | 20 aug 2010      | 25.4.6.2/25-847<br>25.4.6.12/25-85<br>4<br>25.4.6.13/25-85<br>6               | Updated description of the commands RD1BLK, MLOADU and MLOADF                                     |

| Rev.1.27           | 31 Jan 2011      | 25.3.2.9/25-829                                                               | Updated description of protection on Section 25.3.2.9                                             |

### Table 25-1. Revision History

# 25.1 Introduction

The FTMRG32K1 module implements the following:

- 32Kbytes of P-Flash (Program Flash) memory

- 1 Kbytes of EEPROM memory

The Flash memory is ideal for single-supply applications allowing for field reprogramming without requiring external high voltage sources for program or erase operations. The Flash module includes a memory controller that executes commands to modify Flash memory contents. The user interface to the memory controller consists of the indexed Flash Common Command Object (FCCOB) register which is written to with the command, global address, data, and any required command parameters. The memory controller must complete the execution of a command before the FCCOB register can be written to with a new command.

### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

The Flash memory may be read as bytes and aligned words. Read access time is one bus cycle for bytes and aligned words. For misaligned words access, the CPU has to perform twice the byte read access command. For Flash memory, an erased bit reads 1 and a programmed bit reads 0.

| Field              | Description                                                                                                                                                                                                                                                                                     |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                            |  |  |

| 2<br>RSVD          | <b>Reserved Bit</b> — This bit is reserved and always reads 0.                                                                                                                                                                                                                                  |  |  |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 30.4.6, "Flash Command Description," and Section 30.6, "Initialization" for details. |  |  |

#### Table 30-15. FSTAT Field Descriptions (continued)

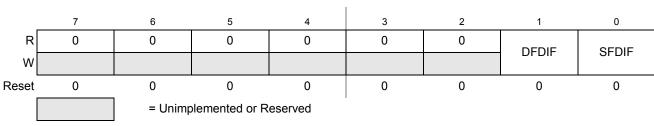

# 30.3.2.8 Flash Error Status Register (FERSTAT)

Offset Module Base + 0x0007

The FERSTAT register reflects the error status of internal Flash operations.

#### Figure 30-12. Flash Error Status Register (FERSTAT)

All flags in the FERSTAT register are readable and only writable to clear the flag.

#### Table 30-16. FERSTAT Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIF | <ul> <li>Double Bit Fault Detect Interrupt Flag — The setting of the DFDIF flag indicates that a double bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The DFDIF flag is cleared by writing a 1 to DFDIF. Writing a 0 to DFDIF has no effect on DFDIF.<sup>2</sup></li> <li>0 No double bit fault detected</li> <li>1 Double bit fault detected or a Flash array read operation returning invalid data was attempted while command running</li> </ul>                                                                        |

| 0<br>SFDIF | <ul> <li>Single Bit Fault Detect Interrupt Flag — With the IGNSF bit in the FCNFG register clear, the SFDIF flag indicates that a single bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The SFDIF flag is cleared by writing a 1 to SFDIF. Writing a 0 to SFDIF has no effect on SFDIF.</li> <li>0 No single bit fault detected</li> <li>1 Single bit fault detected and corrected or a Flash array read operation returning invalid data was attempted operation returning invalid data was attempted operation.</li> </ul> |

The single bit fault and double bit fault flags are mutually exclusive for parity errors (an ECC fault occurrence can be either single fault or double fault but never both). A simultaneous access collision (Flash array read operation returning invalid data attempted while command running) is indicated when both SFDIF and DFDIF flags are high.

<sup>2</sup> There is a one cycle delay in storing the ECC DFDIF and SFDIF fault flags in this register. At least one NOP is required after a flash memory read before checking FERSTAT for the occurrence of ECC errors.

#### 192 KByte Flash Module (S12FTMRG192K2V1)

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|------|-------------------------------------------|

| 010         | HI   | Data 0 [15:8]                             |

| 010         | LO   | Data 0 [7:0]                              |

| 011         | HI   | Data 1 [15:8]                             |

| 011         | LO   | Data 1 [7:0]                              |

| 100         | HI   | Data 2 [15:8]                             |

| 100         | LO   | Data 2 [7:0]                              |

| 101         | HI   | Data 3 [15:8]                             |

| 101         | LO   | Data 3 [7:0]                              |

Table 30-24. FCCOB - NVM Command Mode (Typical Usage)

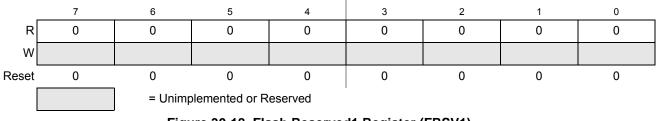

### 30.3.2.12 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000C

Offset Module Base + 0x000D

Figure 30-18. Flash Reserved1 Register (FRSV1)

All bits in the FRSV1 register read 0 and are not writable.

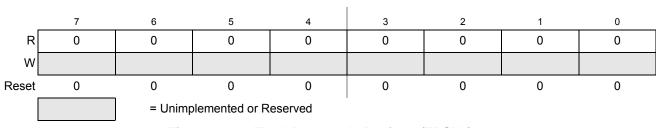

# 30.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

Figure 30-19. Flash Reserved2 Register (FRSV2)

All bits in the FRSV2 register read 0 and are not writable.

### 30.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

#### 192 KByte Flash Module (S12FTMRG192K2V1)

Table 30-4). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters |              |  |

|-------------|------------------|--------------|--|

| 000         | 0x0C             | Not required |  |

| 001         | Key 0            |              |  |

| 010         | Key 1            |              |  |

| 011         | Key 2            |              |  |

| 100         | Key 3            |              |  |

Table 30-52. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

Table 30-53. Verify Backdoor Access Key Command Error Handling

| Register | Error Bit | Error Condition                                                                          |

|----------|-----------|------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 100 at command launch                                              |

|          |           | Set if an incorrect backdoor key is supplied                                             |

|          |           | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 30.3.2.2) |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                              |

|          | FPVIOL    | None                                                                                     |

|          | MGSTAT1   | None                                                                                     |

|          | MGSTAT0   | None                                                                                     |

### 30.4.6.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

| CCOBIX[2:0] | FCCOB Parameters      |                                                   |  |

|-------------|-----------------------|---------------------------------------------------|--|

| 000         | 0x0D                  | Flash block selection code [1:0]. See Table 30-34 |  |

| 001         | Margin level setting. |                                                   |  |

| CCOBIX[2:0] | FCCOB Parameters                                       |  |  |  |  |  |  |  |

|-------------|--------------------------------------------------------|--|--|--|--|--|--|--|

| 000         | 0x0E Flash block selection code [1:0]. See Table 30-34 |  |  |  |  |  |  |  |

| 001         | Margin level setting.                                  |  |  |  |  |  |  |  |

| Table 30-57. | Set Field Margin Level Command FCCOB Requirements |

|--------------|---------------------------------------------------|

|--------------|---------------------------------------------------|

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the field margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM field margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash field margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply field margin levels to the P-Flash block only.

Valid margin level settings for the Set Field Margin Level command are defined in Table 30-58.

| CCOB<br>(CCOBIX=001) | Level Description                 |

|----------------------|-----------------------------------|

| 0x0000               | Return to Normal Level            |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |

Table 30-58. Valid Set Field Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

### Table 30-59. Set Field Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                 |

|----------|-----------|-----------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 001 at command launch.                    |

|          | ACCERR    | Set if command not available in current mode (see Table 30-27). |

| FSTAT    |           | Set if an invalid margin level setting is supplied.             |

| FSTAT    | FPVIOL    | None                                                            |

|          | MGSTAT1   | None                                                            |

|          | MGSTAT0   | None                                                            |

| Condit | nditions are shown in Table A-4 unless otherwise noted |                                                                                                                               |                     |      |                   |     |        |  |  |  |

|--------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------------------|-----|--------|--|--|--|

| NUM    | С                                                      | Rating                                                                                                                        | Symbol              | Min  | Тур               | Max | Unit   |  |  |  |

|        |                                                        | Program Flash Arrays                                                                                                          |                     |      |                   |     |        |  |  |  |

| 1      | С                                                      | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after up to 10,000 program/erase cycles     | t <sub>NVMRET</sub> | 20   | 100 <sup>2</sup>  | _   | Years  |  |  |  |

| 2a     | С                                                      | Program Flash number of program/erase cycles (-40°C $\leq$ Tj $\leq$ 150°C)                                                   | n <sub>FLPE</sub>   | 10K  | 100K <sup>3</sup> | _   | Cycles |  |  |  |

| 2b     | С                                                      | Program Flash number of program/erase cycles (150°C $\leq$ Tj $\leq$ 160°C)                                                   | n <sub>FLPE</sub>   | 1K   | 100K <sup>3</sup> | _   | Cycles |  |  |  |

|        |                                                        | EEPROM Array                                                                                                                  |                     |      |                   |     |        |  |  |  |

| 3      | С                                                      | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$<br>after up to 100,000 program/erase cycles | t <sub>NVMRET</sub> | 5    | 100 <sup>2</sup>  | _   | Years  |  |  |  |

| 4      | С                                                      | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after up to 10,000 program/erase cycles     | t <sub>NVMRET</sub> | 10   | 100 <sup>2</sup>  | _   | Years  |  |  |  |

| 5      | С                                                      | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after less than 100 program/erase cycles    | t <sub>NVMRET</sub> | 20   | 100 <sup>2</sup>  | —   | Years  |  |  |  |

| 6a     | С                                                      | EEPROM number of program/erase cycles (-40°C $\leq$ Tj $\leq$ 150°C)                                                          | n <sub>FLPE</sub>   | 100K | 500K <sup>3</sup> | _   | Cycles |  |  |  |

| 6b     | С                                                      | EEPROM number of program/erase cycles (150°C $\leq$ Tj $\leq$ 160°C)                                                          | n <sub>FLPE</sub>   | 10K  | 500K <sup>3</sup> | _   | Cycles |  |  |  |

#### Table A-39. NVM Reliability Characteristics

<sup>1</sup> T<sub>Javg</sub> does not exceed 85°C in a typical temperature profile over the lifetime of a consumer, industrial or automotive application.

<sup>2</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how NXP defines Typical Data Retention, please refer to Engineering Bulletin EB618

<sup>3</sup> Spec table quotes typical endurance evaluated at 25°C for this product family. For additional information on how NXP defines Typical Endurance, please refer to Engineering Bulletin EB619.

# A.8 Phase Locked Loop

# A.8.1 Jitter Definitions

With each transition of the feedback clock, the deviation from the reference clock is measured and input voltage to the VCO is adjusted accordingly. The adjustment is done continuously with no abrupt changes in the VCOCLK frequency. Noise, voltage, temperature and other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real minimum and maximum clock periods as illustrated in Figure A-4.

### 0x00C8–0x0CF Serial Communication Interface (SCI0)

| 0x00CC         | SCI0SR1        | R        | TDRE | TC | RDRF | IDLE  | OR    | NF    | FE      | PF    |  |

|----------------|----------------|----------|------|----|------|-------|-------|-------|---------|-------|--|

| 0,0000 30103K1 |                | W        |      |    |      |       |       |       |         |       |  |

| 0x00CD         | SCI0SR2        | R        | AMAP | 0  | 0    | TXPOL | RXPOL | BRK13 | TXDIR   | RAF   |  |

| 000000         | 000000 3010342 | 30103112 | W    |    |      |       |       |       | DIVIVIO | INDIN |  |

| 0x00CE         | <b>SCI0DRH</b> | R        | R8   | Т8 | 0    | 0     | 0     | 0     | 0       | 0     |  |

| UXUUCE SCIUDRH | W              |          | 10   |    |      |       |       |       |         |       |  |

|                | SCIODRI        | R        | R7   | R6 | R5   | R4    | R3    | R2    | R1      | R0    |  |

| 0x00CF SCI0DRL |                | W        | Τ7   | T6 | T5   | T4    | Т3    | T2    | T1      | Т0    |  |

### 0x00D0–0x0D7 Serial Communication Interface (SCI1)

| Address     | Name       |               | Bit 7        | Bit 6      | Bit 5    | Bit 4      | Bit 3     | Bit 2    | Bit 1     | Bit 0     |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

|-------------|------------|---------------|--------------|------------|----------|------------|-----------|----------|-----------|-----------|------------|-------------|----------|----------|--------|--------|----------|-------|------|--|--|-------|-------|-------|-------|--|

| 0x00D0      | SCI1BDH    | R<br>W        | IREN         | TNP1       | TNP0     | SBR12      | SBR11     | SBR10    | SBR9      | SBR8      |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 0x00D0      | SCI1ASR1   | R<br>W        |              | 0          | 0        | 0          | 0         | BERRV    | BERRIF    | BKDIF     |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 0x00D1      | SCI1BDL    | R<br>W        | SBR/         | SBR6       | SBR5     | SBR4       | SBR3      | SBR2     | SBR1      | SBR0      |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 0x00D1      | SCI1ACR1   | R             |              | 0          | 0        | 0          | 0         | 0        | BERRIE    | BKDIE     |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

|             |            | W             |              |            |          |            |           |          |           |           |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 0x00D2      | SCI1CR1    | R<br>W        | LLOOPS       | SCISWAI    | RSRC     | М          | WAKE      | ILT      | PE        | PT        |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 0,000.00    | 2 SCI1ACR2 | 10D2 SCI1ACR2 | 1D2 SCI1ACR2 | 2 SCI1ACR2 | SCI1ACR2 | 2 SCI1ACR2 | SCI1ACR2  | SCI1ACR2 | R         | 0         | 0          | 0           | 0        | 0        | BERRM1 | BERRM0 | BKDFE    |       |      |  |  |       |       |       |       |  |

| 0X00D2      |            |               |              |            |          |            |           |          | SCHACKZ   | W         | ſ          |             |          |          |        |        | DERRIVIU | DRUFE |      |  |  |       |       |       |       |  |

| 0x00D3      | SCI1CR2    | R<br>W        | 1 111-       | TCIE       | RIE      | ILIE       | TE        | RE       | RWU       | SBK       |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

|             | SCI15D1    | R             | TDRE         | TC         | RDRF     | IDLE       | OR        | NF       | FE        | PF        |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 0x00D4      | SCI1SR1    | W             |              |            |          |            |           |          |           |           |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

|             | 0014002    | R             | AMAP         | 0          | 0        | TXPOL      | RXPOL     |          | סומעד     | RAF       |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 0x00D5      | DO SCHERZ  | UD5 SCHSRZ V  | 00 SCHSRZ W  | SCHSRZ V   | SCHSRZ V | SCHSRZ V   | N SUIISKZ | SCHSRZ   | DO GUIJAZ | JS SCHORZ | 5 SCHSRZ V | 5 SCI1SR2 V | V SCHERZ | SCHSRZ V | W      | W      | W W      | W     | AWAP |  |  | TAPUL | RAPUL | BRK13 | TXDIR |  |

| 0,00006     |            |               | R8           | то         | 0        | 0          | 0         | 0        | 0         | 0         |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 0x00D6 SCI1 | SCI1DRH    | W             |              | Т8         |          |            |           |          |           |           |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 0x00D7      | SCI1DRL    | R             | R7           | R6         | R5       | R4         | R3        | R2       | R1        | R0        |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

| 020007      | JUIDRE     | W             | T7           | T6         | T5       | T4         | Т3        | T2       | T1        | Т0        |            |             |          |          |        |        |          |       |      |  |  |       |       |       |       |  |

### 0x00D8–0x0DF Serial Peripheral Interface (SPI0)

| Address         | Name     |          | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2   | Bit 1   | Bit 0 |  |       |

|-----------------|----------|----------|----------|-------|-------|--------|---------|---------|---------|-------|--|-------|

| 0x00D8          | SPI0CR1  | R<br>W   | SPIE     | SPE   | SPTIE | MSTR   | CPOL    | CPHA    | SSOE    | LSBFE |  |       |

| 0x00D9          | SPI0CR2  | R        | 0        | XFRW  | 0     | MODFEN | BIDIROE | 0       | SPISWAI | SPC0  |  |       |

| 0,00000         | 01100112 | 01100112 | 01100112 | W     |       |        |         | MODI LI | DIDINOL |       |  | 01 00 |

| 0x00DA          | SPI0BR   | R        | 0        | SPPR2 | SPPR1 | SPPR0  | 0       | SPR2    | SPR1    | SPR0  |  |       |

| UXUUDA SI IUDIA |          | W        |          |       | OFTR  | 01110  |         | 01112   | OFICE   | 0110  |  |       |

| 0x00DB          | SPI0SR   | R        | SPIF     | 0     | SPTEF | MODF   | 0       | 0       | 0       | 0     |  |       |

| UNUUDD          | 37105K   | W        |          |       |       |        |         |         |         |       |  |       |

MC9S12G Family Reference Manual Rev.1.27

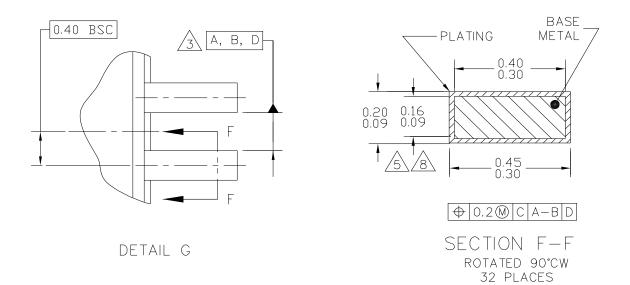

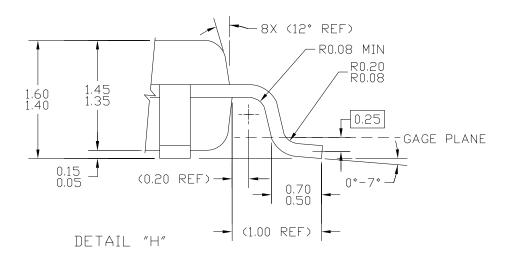

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE                       | PRINT VERSION NOT TO SCALE |  |  |

|---------------------------------------------------------|-----------|---------------------------------|----------------------------|--|--|

| TITLE:                                                  |           | D□CUMENT N□: 98ASH70029A REV: D |                            |  |  |

| LOW PROFILE QUAD FLAT PA                                |           | CASE NUMBER: 873A-03 19 MAY 200 |                            |  |  |

| 32 LEAD, 0.8 PITCH (7 X                                 | / X 1.4)  | STANDARD: JE                    | DEC MS-026 BBA             |  |  |

MC9S12G Family Reference Manual Rev.1.27