Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 86                                                                     |

| Program Memory Size        | 192KB (192K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 11K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g192f0vll |

| 23.5         | Resets                                                          | 762 |

|--------------|-----------------------------------------------------------------|-----|

| 23.6         | Interrupts                                                      | 762 |

|              | 23.6.1 Channel [7:0] Interrupt (C[7:0]F)                        | 763 |

|              | 23.6.2 Pulse Accumulator Input Interrupt (PAOVI)                | 763 |

|              | 23.6.3 Pulse Accumulator Overflow Interrupt (PAOVF)             |     |

|              | 23.6.4 Timer Overflow Interrupt (TOF)                           |     |

|              |                                                                 |     |

|              | Chapter 24                                                      |     |

|              | 16 KByte Flash Module (S12FTMRG16K1V1)                          |     |

| 24.1         | Introduction                                                    | 765 |

| <b>4.</b> 1  | 24.1.1 Glossary                                                 |     |

|              | 24.1.2 Features                                                 |     |

|              | 24.1.3 Block Diagram                                            |     |

| 24.2         | External Signal Description                                     |     |

|              | Memory Map and Registers                                        |     |

| <b>4-</b>    | 24.3.1 Module Memory Map                                        |     |

|              | 24.3.2 Register Descriptions                                    |     |

| 24.4         | Functional Description                                          |     |

| 27.7         | 24.4.1 Modes of Operation                                       |     |

|              | 24.4.2 IFR Version ID Word                                      |     |

|              | 24.4.3 Internal NVM resource (NVMRES)                           |     |

|              | 24.4.4 Flash Command Operations                                 |     |

|              | 24.4.5 Allowed Simultaneous P-Flash and EEPROM Operations       |     |

|              | 24.4.6 Flash Command Description                                |     |

|              | 24.4.7 Interrupts                                               |     |

|              | 24.4.8 Wait Mode                                                |     |

|              | 24.4.9 Stop Mode                                                |     |

| 24.5         | •                                                               |     |

| 2110         | 24.5.1 Unsecuring the MCU using Backdoor Key Access             |     |

|              | 24.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM |     |

|              | 24.5.3 Mode and Security Effects on Flash Command Availability  |     |

| 24.6         | Initialization                                                  |     |

|              |                                                                 |     |

|              | Chapter 25                                                      |     |

|              | 32 KByte Flash Module (S12FTMRG32K1V1)                          |     |

| 25 1         | Introduction                                                    | Q12 |

| 23.1         | 25.1.1 Glossary                                                 |     |

|              | 25.1.1 Glossary                                                 |     |

|              | 25.1.3 Block Diagram                                            |     |

| 25.2         | External Signal Description                                     |     |

|              | Memory Map and Registers                                        |     |

| 43.3         |                                                                 |     |

|              | 25.3.1 Module Memory Map                                        |     |

| 25.4         | Functional Description                                          |     |

| <i>4</i> 3.4 | Tuncuonai Description                                           | 039 |

|              |                                                                 |     |

Table 1-18. 48-Pin LQFP Pinout for S12GA48 and S12GA64

|             | Function <lowestpriorityhighest></lowestpriorityhighest> |              |              | >              | Power       | Internal Pull<br>Resistor |               |                |

|-------------|----------------------------------------------------------|--------------|--------------|----------------|-------------|---------------------------|---------------|----------------|

| Package Pin | Pin                                                      | 2nd<br>Func. | 3rd<br>Func. | 4th<br>Func    | 5th<br>Func | Supply                    | CTRL          | Reset<br>State |

| 2           | VDDXR                                                    | _            | _            | _              | _           | _                         | _             | _              |

| 3           | VSSX                                                     | _            | _            | _              | _           | _                         | _             | _              |

| 4           | PE0 <sup>1</sup>                                         | EXTAL        | _            | _              | _           | V <sub>DDX</sub>          | PUCR/PDPEE    | Down           |

| 5           | VSS                                                      | _            | _            | _              | _           | _                         | _             | _              |

| 6           | PE1 <sup>1</sup>                                         | XTAL         | _            | _              | _           | V <sub>DDX</sub>          | PUCR/PDPEE    | Down           |

| 7           | TEST                                                     | _            | _            | _              | _           | N.A.                      | RESET pin     | Down           |

| 8           | PJ0                                                      | KWJ0         | _            | MISO1          | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 9           | PJ1                                                      | KWJ1         | _            | MOSI1          | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 10          | PJ2                                                      | KWJ2         | _            | SCK1           | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 11          | PJ3                                                      | KWJ3         | _            | SS1            | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 12          | BKGD                                                     | MODC         | _            | _              | _           | V <sub>DDX</sub>          | PUCR/BKPUE    | Up             |

| 13          | PP0                                                      | KWP0         | ETRIG0       | API_EXTC<br>LK | PWM0        | $V_{DDX}$                 | PERP/PPSP     | Disabled       |

| 14          | PP1                                                      | KWP1         | ETRIG1       | ECLKX2         | PWM1        | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 15          | PP2                                                      | KWP2         | ETRIG2       | PWM2           | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 16          | PP3                                                      | KWP3         | ETRIG3       | PWM3           | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 17          | PP4                                                      | KWP4         | PWM4         | _              | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 18          | PP5                                                      | KWP5         | PWM5         | _              | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 19          | PT5                                                      | IOC5         | _            | _              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 20          | PT4                                                      | IOC4         | _            | _              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 21          | PT3                                                      | IOC3         | _            | _              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 22          | PT2                                                      | IOC2         | _            | _              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 23          | PT1                                                      | IOC1         | ĪRQ          | _              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 24          | PT0                                                      | IOC0         | XIRQ         | _              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 25          | PAD0                                                     | KWAD0        | AN0          | _              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 26          | PAD8                                                     | KWAD8        | AN8          | _              | _           | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 27          | PAD1                                                     | KWAD1        | AN1          | _              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 28          | PAD9                                                     | KWAD9        | AN9          | ACMPO          | _           | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 29          | PAD2                                                     | KWAD2        | AN2          | _              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

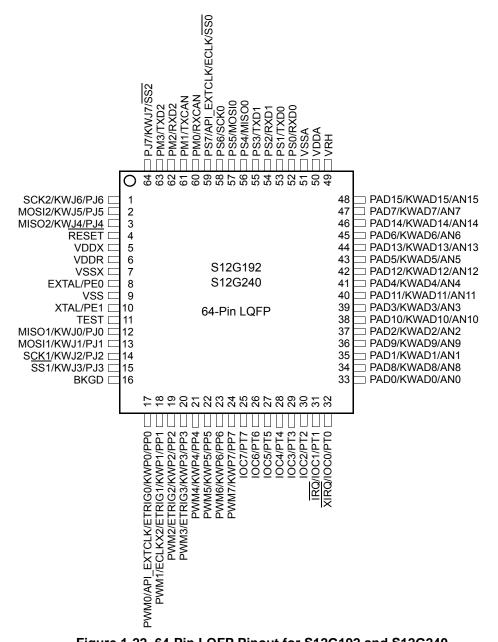

## 1.8.8.2 **Pinout 64-Pin LQFP**

Figure 1-22. 64-Pin LQFP Pinout for S12G192 and S12G240

handshake protocol is enabled, the time out between a read command and the data retrieval is disabled. Therefore, the host could wait for more then 512 serial clock cycles and still be able to retrieve the data from an issued read command. However, once the handshake pulse (ACK pulse) is issued, the time-out feature is re-activated, meaning that the target will time out after 512 clock cycles. Therefore, the host needs to retrieve the data within a 512 serial clock cycles time frame after the ACK pulse had been issued. After that period, the read command is discarded and the data is no longer available for retrieval. Any negative edge in the BKGD pin after the time-out period is considered to be a new command or a SYNC request.

Note that whenever a partially issued command, or partially retrieved data, has occurred the time out in the serial communication is active. This means that if a time frame higher than 512 serial clock cycles is observed between two consecutive negative edges and the command being issued or data being retrieved is not complete, a soft-reset will occur causing the partially received command or data retrieved to be disregarded. The next negative edge in the BKGD pin, after a soft-reset has occurred, is considered by the target as the start of a new BDM command, or the start of a SYNC request pulse.

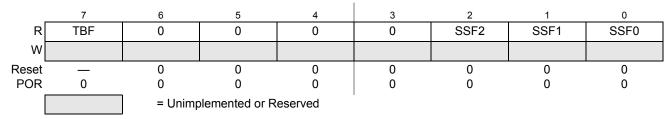

Address: 0x0021

Figure 8-4. Debug Status Register (DBGSR)

Read: Anytime Write: Never

**Table 8-5. DBGSR Field Descriptions**

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TBF        | Trace Buffer Full — The TBF bit indicates that the trace buffer has stored 64 or more lines of data since it was last armed. If this bit is set, then all 64 lines will be valid data, regardless of the value of DBGCNT bits. The TBF bit is cleared when ARM in DBGC1 is written to a one. The TBF is cleared by the power on reset initialization. Other system generated resets have no affect on this bit This bit is also visible at DBGCNT[7]                                                                                                                                                                                                            |

| 2–0<br>SSF[2:0] | State Sequencer Flag Bits — The SSF bits indicate in which state the State Sequencer is currently in. During a debug session on each transition to a new state these bits are updated. If the debug session is ended by software clearing the ARM bit, then these bits retain their value to reflect the last state of the state sequencer before disarming. If a debug session is ended by an internal event, then the state sequencer returns to state0 and these bits are cleared to indicate that state0 was entered during the session. On arming the module the state sequencer enters state1 and these bits are forced to SSF[2:0] = 001. See Table 8-6. |

Table 8-6. SSF[2:0] — State Sequence Flag Bit Encoding

| SSF[2:0]    | Current State     |

|-------------|-------------------|

| 000         | State0 (disarmed) |

| 001         | State1            |

| 010         | State2            |

| 011         | State3            |

| 100         | Final State       |

| 101,110,111 | Reserved          |

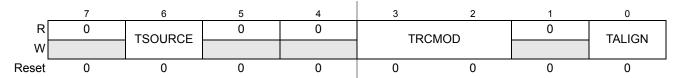

#### 8.3.2.3 **Debug Trace Control Register (DBGTCR)**

Address: 0x0022

Figure 8-5. Debug Trace Control Register (DBGTCR)

MC9S12G Family Reference Manual Rev.1.27 **NXP Semiconductors** 311

Table 8-14. State Control Register Access Encoding

| COMRV | Visible State Control Register |

|-------|--------------------------------|

| 01    | DBGSCR2                        |

| 10    | DBGSCR3                        |

| 11    | DBGMFR                         |

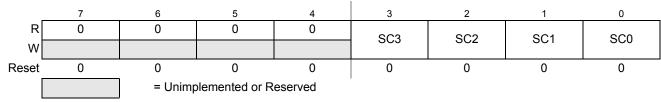

## 8.3.2.7.1 Debug State Control Register 1 (DBGSCR1)

Address: 0x0027

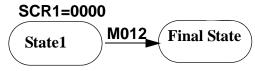

Figure 8-9. Debug State Control Register 1 (DBGSCR1)

Read: If COMRV[1:0] = 00

Write: If COMRV[1:0] = 00 and DBG is not armed.

This register is visible at 0x0027 only with COMRV[1:0] = 00. The state control register 1 selects the targeted next state whilst in State1. The matches refer to the match channels of the comparator match control logic as depicted in Figure 8-1 and described in Section 8.3.2.8.1, "Debug Comparator Control Register (DBGXCTL). Comparators must be enabled by setting the comparator enable bit in the associated DBGXCTL control register.

Table 8-15. DBGSCR1 Field Descriptions

| Field          | Description                                                                             |

|----------------|-----------------------------------------------------------------------------------------|

| 3–0<br>SC[3:0] | These bits select the targeted next state whilst in State1, based upon the match event. |

Table 8-16. State1 Sequencer Next State Selection

| SC[3:0] | Description (Unspecified matches have no effect) |  |  |  |  |  |  |

|---------|--------------------------------------------------|--|--|--|--|--|--|

| 0000    | Any match to Final State                         |  |  |  |  |  |  |

| 0001    | Match1 to State3                                 |  |  |  |  |  |  |

| 0010    | Match2 to State2                                 |  |  |  |  |  |  |

| 0011    | Match1 to State2                                 |  |  |  |  |  |  |

| 0100    | Match0 to State2 Match1 to State3                |  |  |  |  |  |  |

| 0101    | Match1 to State3Match0 to Final State            |  |  |  |  |  |  |

| 0110    | Match0 to State2 Match2 to State3                |  |  |  |  |  |  |

| 0111    | Either Match0 or Match1 to State2                |  |  |  |  |  |  |

| 1000    | Reserved                                         |  |  |  |  |  |  |

| 1001    | Match0 to State3                                 |  |  |  |  |  |  |

#### MC9S12G Family Reference Manual Rev.1.27

## 8.5.3 Scenario 2

A trigger is generated if a given sequence of 2 code events is executed.

Figure 8-28. Scenario 2a

A trigger is generated if a given sequence of 2 code events is executed, whereby the first event is entry into a range (COMPA,COMPB configured for range mode). M1 is disabled in range modes.

Figure 8-29. Scenario 2b

A trigger is generated if a given sequence of 2 code events is executed, whereby the second event is entry into a range (COMPA,COMPB configured for range mode)

Figure 8-30. Scenario 2c

All 3 scenarios 2a,2b,2c are possible with the S12SDBGV1 SCR encoding

#### 8.5.4 Scenario 3

A trigger is generated immediately when one of up to 3 given events occurs

Figure 8-31. Scenario 3

Scenario 3 is possible with S12SDBGV1 SCR encoding

#### 8.5.5 Scenario 4

Trigger if a sequence of 2 events is carried out in an incorrect order. Event A must be followed by event B and event B must be followed by event A. 2 consecutive occurrences of event A without an intermediate

This method requires that:

- The application software previously programmed into the microcontroller has been designed to have the capability to erase and program the Flash options/security byte, or security is first disabled using the backdoor key method, allowing BDM to be used to issue commands to erase and program the Flash options/security byte.

- The Flash sector containing the Flash options/security byte is not protected.

# 9.1.7 Complete Memory Erase (Special Modes)

The microcontroller can be unsecured in special modes by erasing the entire EEPROM and Flash memory contents.

When a secure microcontroller is reset into special single chip mode (SS), the BDM firmware verifies whether the EEPROM and Flash memory are erased. If any EEPROM or Flash memory address is not erased, only BDM hardware commands are enabled. BDM hardware commands can then be used to write to the EEPROM and Flash registers to mass erase the EEPROM and all Flash memory blocks.

When next reset into special single chip mode, the BDM firmware will again verify whether all EEPROM and Flash memory are erased, and this being the case, will enable all BDM commands, allowing the Flash options/security byte to be programmed to the unsecured value. The security bits SEC[1:0] in the Flash security register will indicate the unsecure state following the next reset.

| Address            | Name               |        | Bit 7                       | 6                                                                                                                            | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|--------------------|--------------------|--------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|-------|

| 0x0024             | ATDDR10            | R<br>W |                             | See Section 14.3.2.12.1, "Left Justified Result Data (DJM=0)" and Section 14.3.2.12.2, "Right Justified Result Data (DJM=1)" |   |   |   |   |   |       |

| 0x0026             | ATDDR11            | R<br>W |                             | See Section 14.3.2.12.1, "Left Justified Result Data (DJM=0)" and Section 14.3.2.12.2, "Right Justified Result Data (DJM=1)" |   |   |   |   |   |       |

| 0x0028 -<br>0x002F | Unimple-<br>mented | R<br>W | 0                           | 0                                                                                                                            | 0 | 0 | 0 | 0 | 0 | 0     |

|                    |                    | Г      | = Unimplemented or Reserved |                                                                                                                              |   |   |   |   |   |       |

Figure 14-2. ADC12B12C Register Summary (Sheet 3 of 3)

0

0

1

1

1

1

1

1

Module Base + 0x0002

| ETRIGSEL | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 | External trigger source is |

|----------|----------|----------|----------|----------|----------------------------|

| 0        | 0        | 0        | 0        | 0        | AN0                        |

| 0        | 0        | 0        | 0        | 1        | AN1                        |

| 0        | 0        | 0        | 1        | 0        | AN2                        |

| 0        | 0        | 0        | 1        | 1        | AN3                        |

| 0        | 0        | 1        | 0        | 0        | AN4                        |

| 0        | 0        | 1        | 0        | 1        | AN5                        |

| 0        | 0        | 1        | 1        | 0        | AN6                        |

| 0        | 0        | 1        | 1        | 1        | AN7                        |

| 0        | 1        | 0        | 0        | 0        | AN8                        |

| 0        | 1        | 0        | 0        | 1        | AN9                        |

| 0        | 1        | 0        | 1        | 0        | AN10                       |

| 0        | 1        | 0        | 1        | 1        | AN11                       |

| 0        | 1        | 1        | 0        | 0        | AN11                       |

| 0        | 1        | 1        | 0        | 1        | AN11                       |

1

1

0

0

1

1

Χ

Χ

0

1

0

1

0

1

Χ

Χ

AN11

AN11

ETRIG0<sup>1</sup>

ETRIG1<sup>1</sup>

ETRIG2<sup>1</sup>

ETRIG3<sup>1</sup>

Reserved

Reserved

**Table 14-5. External Trigger Channel Select Coding**

# 14.3.2.3 ATD Control Register 2 (ATDCTL2)

1

1

0

0

0

0

0

1

1

1

0

0

0

0

1

Χ

Writes to this register will abort current conversion sequence.

6 3 2 0 5 0 R **AFFC** Reserved **ETRIGLE ETRIGP ETRIGE ASCIE ACMPIE** W 0 0 0 0 0 0 0 0 Reset = Unimplemented or Reserved

Figure 14-5. ATD Control Register 2 (ATDCTL2)

Read: Anytime Write: Anytime

Only if ETRIG3-0 input option is available (see device specification), else ETRISEL is ignored, that means external trigger source is still on one of the AD channels selected by ETRIGCH3-0

# Chapter 16 Analog-to-Digital Converter (ADC12B16CV2)

# **Revision History**

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                                                                                                                                                                                                                                                                           |

|-------------------|------------------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V02.00            | 18 June 2009     | 18 June 2009      |        | Initial version copied 12 channel block guide                                                                                                                                                                                                                                                                                                    |

| V02.01            | 09 Feb 2010      | 09 Feb 2010       |        | Updated Table 16-15 Analog Input Channel Select Coding - description of internal channels. Updated register ATDDR (left/right justified result) description in section 16.3.2.12.1/16-554 and 16.3.2.12.2/16-555 and added Table 16-21 to improve feature description. Fixed typo in Table 16-9 - conversion result for 3mV and 10bit resolution |

| V02.03            | 26 Feb 2010      | 26 Feb 2010       |        | Corrected Table 16-15 Analog Input Channel Select Coding - description of internal channels.                                                                                                                                                                                                                                                     |

| V02.04            | 26 Mar 2010      | 16 Mar 2010       |        | Corrected typo: Reset value of ATDDIEN register                                                                                                                                                                                                                                                                                                  |

| V02.05            | 14 Apr 2010      | 14 Apr 2010       |        | Corrected typos to be in-line with SoC level pin naming conventions for VDDA, VSSA, VRL and VRH.                                                                                                                                                                                                                                                 |

| V02.06            | 25 Aug 2010      | 25 Aug 2010       |        | Removed feature of conversion during STOP and general wording clean up done in Section 16.4, "Functional Description                                                                                                                                                                                                                             |

| v02.07            | 09 Sep 2010      | 09 Sep 2010       |        | Update of internal only information.                                                                                                                                                                                                                                                                                                             |

| V02.08            | 11 Feb 2011      | 11 Feb 2011       |        | Connectivity Information regarding internal channel_6 added to Table 16-15.                                                                                                                                                                                                                                                                      |

| V02.09            | 29 Mar 2011      | 29 Mar 2011       |        | Fixed typo in bit description field Table 16-14 for bits CD, CC, CB, CA. Last sentence contained a wrong highest channel number (it is not AN7 to AN0 instead it is AN15 to AN0).                                                                                                                                                                |

| V02.10            | 22. Jun 2012     | 22. Jun 2012      |        | Updated register wirte access information in section 16.3.2.9/16-552                                                                                                                                                                                                                                                                             |

| V02.11            | 29. Jun 2012     | 29. Jun 2012      |        | Removed IP name in block diagram Figure 16-1                                                                                                                                                                                                                                                                                                     |

| V02.12            | 02 Oct 2012      | 02 Oct 2012       |        | Added user information to avoid maybe false external trigger events when enabling the external trigger mode (Section 16.4.2.1, "External Trigger Input).                                                                                                                                                                                         |

Analog-to-Digital Converter (ADC12B16CV2)

## 16.5 Resets

At reset the ADC12B16C is in a power down state. The reset state of each individual bit is listed within the Register Description section (see Section 16.3.2, "Register Descriptions") which details the registers and their bit-field.

# 16.6 Interrupts

The interrupts requested by the ADC12B16C are listed in Table 16-24. Refer to MCU specification for related vector address and priority.

Table 16-24. ATD Interrupt Vectors

| Interrupt Source            | CCR<br>Mask | Local Enable      |

|-----------------------------|-------------|-------------------|

| Sequence Complete Interrupt | I bit       | ASCIE in ATDCTL2  |

| Compare Interrupt           | I bit       | ACMPIE in ATDCTL2 |

See Section 16.3.2, "Register Descriptions" for further details.

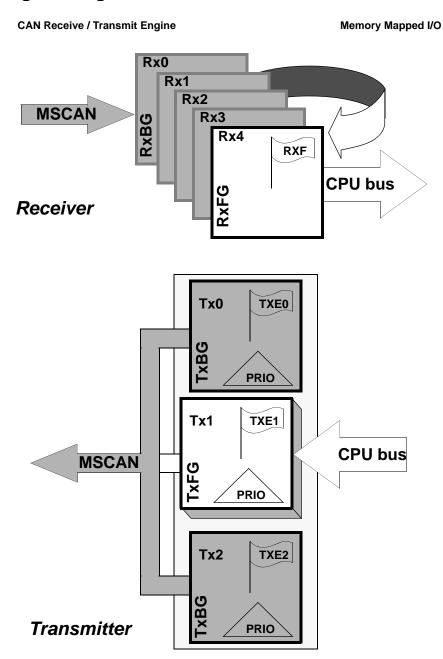

# 18.4.2 Message Storage

Figure 18-39. User Model for Message Buffer Organization

The MSCAN facilitates a sophisticated message storage system which addresses the requirements of a broad range of network applications.

# 18.4.2.1 Message Transmit Background

Modern application layer software is built upon two fundamental assumptions:

MC9S12G Family Reference Manual Rev.1.27

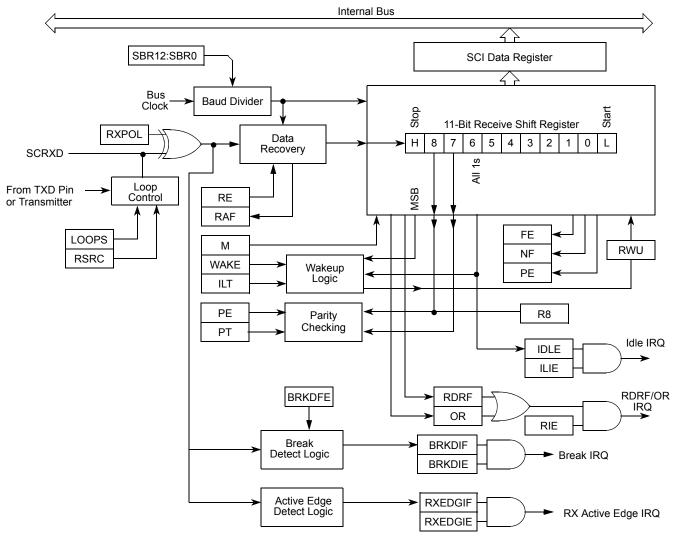

## 20.4.6 Receiver

Figure 20-20. SCI Receiver Block Diagram

# 20.4.6.1 Receiver Character Length

The SCI receiver can accommodate either 8-bit or 9-bit data characters. The state of the M bit in SCI control register 1 (SCICR1) determines the length of data characters. When receiving 9-bit data, bit R8 in SCI data register high (SCIDRH) is the ninth bit (bit 8).

# 20.4.6.2 Character Reception

During an SCI reception, the receive shift register shifts a frame in from the RXD pin. The SCI data register is the read-only buffer between the internal data bus and the receive shift register.

After a complete frame shifts into the receive shift register, the data portion of the frame transfers to the SCI data register. The receive data register full flag, RDRF, in SCI status register 1 (SCISR1) becomes set,

Timer Module (TIM16B8CV3)

#### **Prescaler** 23.4.1

The prescaler divides the Bus clock by 1, 2, 4, 8, 16, 32, 64 or 128. The prescaler select bits, PR[2:0], select the prescaler divisor. PR[2:0] are in timer system control register 2 (TSCR2).

The prescaler divides the Bus clock by a prescalar value. Prescaler select bits PR[2:0] of in timer system control register 2 (TSCR2) are set to define a prescalar value that generates a divide by 1, 2, 4, 8, 16, 32, 64 and 128 when the PRNT bit in TSCR1 is disabled.

By enabling the PRNT bit of the TSCR1 register, the performance of the timer can be enhanced. In this case, it is possible to set additional prescaler settings for the main timer counter in the present timer by using PTPSR[7:0] bits of PTPSR register generating divide by 1, 2, 3, 4,....20, 21, 22, 23,......255, or 256.

#### 23.4.2 **Input Capture**

Clearing the I/O (input/output) select bit, IOSx, configures channel x as an input capture channel. The input capture function captures the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the timer transfers the value in the timer counter into the timer channel registers, TCx.

The minimum pulse width for the input capture input is greater than two Bus clocks.

An input capture on channel x sets the CxF flag. The CxI bit enables the CxF flag to generate interrupt requests. Timer module or Pulse Accumulator must stay enabled (TEN bit of TSCR1 or PAEN bit of PACTL register must be set to one) while clearing CxF (writing one to CxF).

#### 23.4.3 **Output Compare**

Setting the I/O select bit, IOSx, configures channel x when available as an output compare channel. The output compare function can generate a periodic pulse with a programmable polarity, duration, and frequency. When the timer counter reaches the value in the channel registers of an output compare channel, the timer can set, clear, or toggle the channel pin if the corresponding OCPDx bit is set to zero. An output compare on channel x sets the CxF flag. The CxI bit enables the CxF flag to generate interrupt requests. Timer module or Pulse Accumulator must stay enabled (TEN bit of TSCR1 or PAEN bit of PACTL register must be set to one) while clearing CxF (writing one to CxF).

The output mode and level bits, OMx and OLx, select set, clear, toggle on output compare. Clearing both OMx and OLx results in no output compare action on the output compare channel pin.

Setting a force output compare bit, FOCx, causes an output compare on channel x. A forced output compare does not set the channel flag.

A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides output compares on all other output compare channels. The output compare 7 mask register masks the bits in the output compare 7 data register. The timer counter reset enable bit, TCRE, enables channel 7 output compares to reset the timer counter. A channel 7 output compare can reset the timer counter even if the IOC7 pin is being used as the pulse accumulator input.

MC9S12G Family Reference Manual Rev.1.27 760 **NXP Semiconductors**

Table 24-61. Program EEPROM Command Error Handling

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                          |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |

|          | ACCERR    | Set if command not available in current mode (see Table 24-25)                      |

|          | ACCERR    | Set if an invalid global address [17:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

| . •      |           | Set if the requested group of words breaches the end of the EEPROM block            |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

## 24.4.6.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

Table 24-62. Erase EEPROM Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                               |                                                 |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|--|

| 000         | 0x12                                                                                                           | Global address [17:16] to identify EEPROM block |  |  |  |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 24.1.2.2 for EEPROM sector size. |                                                 |  |  |  |  |  |

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

Table 24-63. Erase EEPROM Sector Command Error Handling

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          | ACCERR    | Set if command not available in current mode (see Table 24-25)                      |

|          | ACCERR    | Set if an invalid global address [17:0] is suppliedsee Table 24-3)                  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

MC9S12G Family Reference Manual Rev.1.27

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|------|-------------------------------------------|

| 010         | HI   | Data 0 [15:8]                             |

| 010         | LO   | Data 0 [7:0]                              |

| 011         | HI   | Data 1 [15:8]                             |

| 011         | LO   | Data 1 [7:0]                              |

| 100         | HI   | Data 2 [15:8]                             |

| 100         | LO   | Data 2 [7:0]                              |

| 101         | HI   | Data 3 [15:8]                             |

| 101         |      |                                           |

Data 3 [7:0]

Table 26-24. FCCOB - NVM Command Mode (Typical Usage)

## 26.3.2.12 Flash Reserved1 Register (FRSV1)

LO

This Flash register is reserved for factory testing.

Offset Module Base + 0x000C

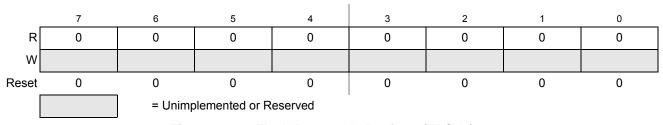

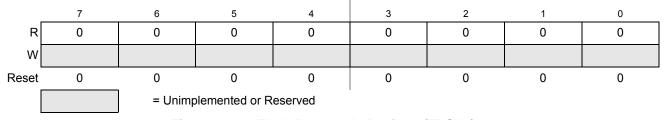

Figure 26-18. Flash Reserved1 Register (FRSV1)

All bits in the FRSV1 register read 0 and are not writable.

# 26.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000D

Figure 26-19. Flash Reserved2 Register (FRSV2)

All bits in the FRSV2 register read 0 and are not writable.

# 26.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

MC9S12G Family Reference Manual Rev.1.27 **NXP Semiconductors** 889

Table 28-54. Set User Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters      |                                                   |  |  |  |  |  |  |

|-------------|-----------------------|---------------------------------------------------|--|--|--|--|--|--|

| 000         | 0x0D                  | Flash block selection code [1:0]. See Table 28-34 |  |  |  |  |  |  |

| 001         | Margin level setting. |                                                   |  |  |  |  |  |  |

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

#### **NOTE**

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 28-55.

Table 28-55. Valid Set User Margin Level Settings

| CCOB<br>(CCOBIX=001) | Level Description                |

|----------------------|----------------------------------|

| 0x0000               | Return to Normal Level           |

| 0x0001               | User Margin-1 Level <sup>1</sup> |

| 0x0002               | User Margin-0 Level <sup>2</sup> |

Read margin to the erased state

Table 28-56. Set User Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                              |

|----------|-----------|------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                  |

|          | ACCEPP    | Set if command not available in current mode (see Table 28-27)               |

|          | ACCERR    | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 28-34) |

| FSTAT    |           | Set if an invalid margin level setting is supplied                           |

|          | FPVIOL    | None                                                                         |

| -        | MGSTAT1   | None                                                                         |

|          | MGSTAT0   | None                                                                         |

MC9S12G Family Reference Manual Rev.1.27 1011 **NXP Semiconductors**

<sup>&</sup>lt;sup>2</sup> Read margin to the programmed state

## 0x001A-0x001B Device ID Register (PARTIDH/PARTIDL)

| Address      | Name         |   | Bit 7 | Bit 6 | Bit 5 | Bit 4            | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------|--------------|---|-------|-------|-------|------------------|-------|-------|-------|-------|

| 0x001A       | 1A PARTIDH . |   |       |       |       | PAR <sup>*</sup> | TIDH  |       |       |       |

| 0,00174      | TARTIBIT     | W |       |       |       |                  |       |       |       |       |

| 0x001B PARTI | PARTIDL      | R |       |       |       | PAR              | TIDL  |       |       |       |

|              |              | W |       |       |       |                  |       |       |       |       |

# 0x001C-0x001F Port Integration Module (PIM) Map 3 of 6

| Address | Name            |        | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------------|--------|---------|--------|-------|-------|-------|-------|-------|-------|

| 0x001C  | ECLKCTL         | R<br>W | I NFCLK | NCLKX2 | DIV16 | EDIV4 | EDIV3 | EDIV2 | EDIV1 | EDIV0 |

| 0x001D  | Descried        | R      | 0       | 0      | 0     | 0     | 0     | 0     | 0     | 0     |

| UXUUTD  | 0x001D Reserved | W      |         |        |       |       |       |       |       |       |

| 0x001E  | IRQCR           | R      | IRQE    | IRQEN  | 0     | 0     | 0     | 0     | 0     | 0     |

| UXUUTE  | WOLE INGCR      |        | INQL    | INQLIN |       |       |       |       |       |       |

| 0x001F  | Reserved        | R      | 0       | 0      | 0     | 0     | 0     | 0     | 0     | 0     |

| 0,00011 | Reserved        | W      |         |        |       |       |       |       |       |       |

# 0x0020-0x002F Debug Module (DBG)

| Address | Name     |   | Bit 7            | Bit 6   | Bit 5  | Bit 4         | Bit 3   | Bit 2  | Bit 1 | Bit 0                                 |  |

|---------|----------|---|------------------|---------|--------|---------------|---------|--------|-------|---------------------------------------|--|

| 0x0020  | DBGC1    | R | ARM              | 0       | 0      | BDM           | DBGBRK  | 0      | CON   | /IRV                                  |  |

| 0,10020 | 2200.    | W | 7 11 1111        | TRIG    |        | <i>BB</i> 141 | BBOBIAR |        | 00.   |                                       |  |

| 0x0021  | DBGSR    | R | TBF              | 0       | 0      | 0             | 0       | SSF2   | SSF1  | SSF0                                  |  |

| 0,0021  | DBGSIX   | W |                  |         |        |               |         |        |       |                                       |  |

| 0x0022  | DBGTCR   | R | 0                | TSOURCE | 0      | 0             | TRCI    | MOD    | 0     | TALIGN                                |  |

| 000022  | DBGTCK   | W |                  | ISOURCE |        |               | ING     | VIOD   |       | IALIGN                                |  |

| 0x0023  | DBGC2    | R | 0                | 0       | 0      | 0             | 0       | 0      | ΛD    | <b>~</b> M                            |  |

| 00023   | DBGC2    | W |                  |         |        |               |         |        | Abi   | BCM                                   |  |

| 0x0024  | DBGTBH   | R | Bit 15           | Bit 14  | Bit 13 | Bit 12        | Bit 11  | Bit 10 | Bit 9 | Bit 8                                 |  |

| 0,0024  | DBGTBIT  | W |                  |         |        |               |         |        |       |                                       |  |

| 0x0025  | DBGTBL   | R | Bit 7            | Bit 6   | Bit 5  | Bit 4         | Bit 3   | Bit 2  | Bit 1 | Bit 0                                 |  |

| 00025   | DBGTBL   | W |                  |         |        |               |         |        |       |                                       |  |

| 0x0026  | DBGCNT   | R | <sup>1</sup> TBF | 0       | CNT    |               |         |        |       |                                       |  |

| 00020   | DBGCN1   | W |                  |         |        |               |         |        |       |                                       |  |

|         | DBGSCRX  | R | 0                | 0       | 0      | 0             | SC3     | SC2    | SC1   | SC0                                   |  |

| 0x0027  | DBGGCKX  | W |                  |         |        |               |         | 302    | 301   | 300                                   |  |

| 00027   | DBGMFR   | R | 0                | 0       | 0      | 0             | 0       | MC2    | MC1   | MC0                                   |  |

|         | DEGIVIER | W |                  |         |        |               |         |        |       |                                       |  |

|         | DBGACTL  | R | SZE              | SZ      | TAG    | BRK           | RW      | RWE    | NDB   | COMPE                                 |  |

|         | DDOMOTE  | W | OZL              | 02      | 17.0   | DIVIC         | 1777    | 1700   | NOD   | OOWII L                               |  |

| 0x0028  | DBGBCTL  | R | SZE              | SZ      | TAG    | BRK           | RW      | RWE    | 0     | COMPE                                 |  |

| 0,0020  | 22020.2  | W |                  |         | ., .   | DIXIX IXW     |         |        |       | J J J J J J J J J J J J J J J J J J J |  |

|         | DBGCCTL  | R | 0                | 0       | TAG    | BRK           | RW      | RWE    | 0     | COMPE                                 |  |

|         | 220001L  | W |                  |         | .,.0   | DIXIX         | IXVV    | IVVL   |       | JOINI L                               |  |

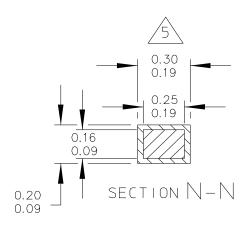

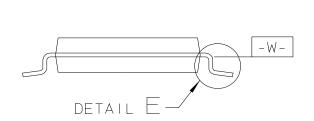

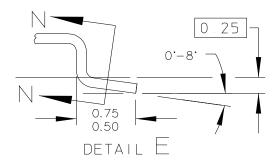

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |              | PRINT VERSION NOT TO SCALE |             |  |

|---------------------------------------------------------|--------------------|--------------|----------------------------|-------------|--|

| TITLE:                                                  |                    | DOCUMENT NO  | ]: 98ASH70169A             | REV: C      |  |

| 20 LD ISSOP, PITCH                                      | N 65MM             | CASE NUMBER  | 948E-02                    | 25 MAY 2005 |  |

|                                                         | 0.00.111           | STANDARD: JE | DEC                        |             |  |

MC9S12G Family Reference Manual Rev.1.27