Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 12V1                                                                  |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 40                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1.5K x 8                                                              |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g48f0clf |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Port Integration Module (S12GPIMV1)

<sup>1</sup> Read: Anytime

Write:

IRQE: Once in normal mode, anytime in special mode IRQEN: Anytime

#### Table 2-34. IRQCR Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IRQE  | <ul> <li>IRQ select edge sensitive only—</li> <li>1 IRQ pin configured to respond only to falling edges. Falling edges on the IRQ pin are detected anytime when IRQE=1 and will be cleared only upon a reset or the servicing of the IRQ interrupt.</li> <li>0 IRQ pin configured for low level recognition</li> </ul> |

| 6<br>IRQEN | IRQ enable—<br>1 IRQ pin is connected to interrupt logic<br>0 IRQ pin is disconnected from interrupt logic                                                                                                                                                                                                             |

### NOTE

If the input is driven to active level (IRQ=0) a write access to set either IRQCR[IRQEN] and IRQCR[IRQE] to 1 simultaneously or to set IRQCR[IRQEN] to 1 when IRQCR[IRQE]=1 causes an IRQ interrupt to be generated if the I-bit is cleared. Refer to Section 2.6.3, "Enabling IRQ edge-sensitive mode".

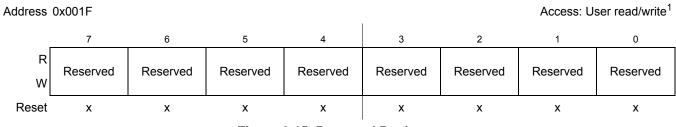

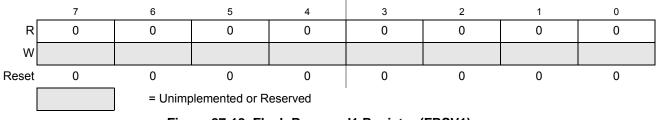

### 2.4.3.14 Reserved Register

Figure 2-15. Reserved Register

<sup>1</sup> Read: Anytime

Write: Only in special mode

These reserved registers are designed for factory test purposes only and are not intended for general user access. Writing to these registers when in special mode can alter the module's functionality.

## 2.4.3.18 Port T Pull Device Enable Register (PERT)

Figure 2-19. Port T Pull Device Enable Register (PERT)

<sup>1</sup> Read: Anytime

Write: Anytime

### Table 2-38. PERT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-2<br>PERT | <b>Port T pull device enable</b> —Enable pull device on input pin<br>This bit controls whether a pull device on the associated port input pin is active. If a pin is used as output this bit has<br>no effect. The polarity is selected by the related polarity select register bit.               |

|             | 1 Pull device enabled<br>0 Pull device disabled                                                                                                                                                                                                                                                    |

| 1<br>PERT   | <b>Port T pull device enable</b> —Enable pull device on input pin<br>This bit controls whether a pull device on the associated port input pin is active. The polarity is selected by the related<br>polarity select register bit. If this pin is used as IRQ only a pullup device can be enabled.  |

|             | 1 Pull device enabled<br>0 Pull device disabled                                                                                                                                                                                                                                                    |

| 0<br>PERT   | <b>Port T pull device enable</b> —Enable pull device on input pin<br>This bit controls whether a pull device on the associated port input pin is active. The polarity is selected by the related<br>polarity select register bit. If this pin is used as XIRQ only a pullup device can be enabled. |

|             | 1 Pull device enabled<br>0 Pull device disabled                                                                                                                                                                                                                                                    |

# Chapter 5 S12G Memory Map Controller (S12GMMCV1)

| _ | ev. No.<br>m No.) | Date<br>(Submitted By) | Sections<br>Affected | Substantial Change(s)           |

|---|-------------------|------------------------|----------------------|---------------------------------|

| 0 | 1.02              | 20-May 2010            |                      | Updates for S12VR48 and S12VR64 |

## 5.1 Introduction

The S12GMMC module controls the access to all internal memories and peripherals for the CPU12 and S12SBDM module. It regulates access priorities and determines the address mapping of the on-chip resources. Figure 5-1 shows a block diagram of the S12GMMC module.

## 5.1.1 Glossary

| Term                         | Definition                                                   |

|------------------------------|--------------------------------------------------------------|

| Local Addresses              | Address within the CPU12's Local Address Map (Figure 5-11)   |

| Global Address               | Address within the Global Address Map (Figure 5-11)          |

| Aligned Bus Access           | Bus access to an even address.                               |

| Misaligned Bus Access        | Bus access to an odd address.                                |

| NS                           | Normal Single-Chip Mode                                      |

| SS                           | Special Single-Chip Mode                                     |

| Unimplemented Address Ranges | Address ranges which are not mapped to any on-chip resource. |

| NVM                          | Non-volatile Memory; Flash or EEPROM                         |

| IFR                          | NVM Information Row. Refer to FTMRG Block Guide              |

### Table 5-2. Glossary Of Terms

## 5.1.2 Overview

The S12GMMC connects the CPU12's and the S12SBDM's bus interfaces to the MCU's on-chip resources (memories and peripherals). It arbitrates the bus accesses and determines all of the MCU's memory maps. Furthermore, the S12GMMC is responsible for constraining memory accesses on secured devices and for selecting the MCU's functional mode.

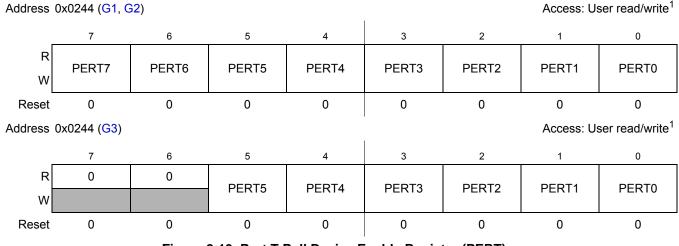

### Read: Anytime

Write: Never

#### Table 8-5. DBGSR Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TBF        | <b>Trace Buffer Full</b> — The TBF bit indicates that the trace buffer has stored 64 or more lines of data since it was last armed. If this bit is set, then all 64 lines will be valid data, regardless of the value of DBGCNT bits. The TBF bit is cleared when ARM in DBGC1 is written to a one. The TBF is cleared by the power on reset initialization. Other system generated resets have no affect on this bit This bit is also visible at DBGCNT[7]                                                                                                                                                                                                            |

| 2–0<br>SSF[2:0] | <b>State Sequencer Flag Bits</b> — The SSF bits indicate in which state the State Sequencer is currently in. During a debug session on each transition to a new state these bits are updated. If the debug session is ended by software clearing the ARM bit, then these bits retain their value to reflect the last state of the state sequencer before disarming. If a debug session is ended by an internal event, then the state sequencer returns to state0 and these bits are cleared to indicate that state0 was entered during the session. On arming the module the state sequencer enters state1 and these bits are forced to SSF[2:0] = 001. See Table 8-6. |

### Table 8-6. SSF[2:0] — State Sequence Flag Bit Encoding

| SSF[2:0]    | Current State     |

|-------------|-------------------|

| 000         | State0 (disarmed) |

| 001         | State1            |

| 010         | State2            |

| 011         | State3            |

| 100         | Final State       |

| 101,110,111 | Reserved          |

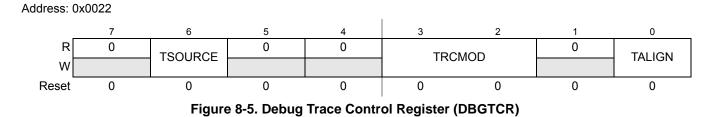

### 8.3.2.3 Debug Trace Control Register (DBGTCR)

MC9S12G Family Reference Manual Rev.1.27

- 4. Clear all flags in the CPMUFLG register to be able to detect any future status bit change.

- 5. Optionally status interrupts can be enabled (CPMUINT register).

Loosing PLL lock status (LOCK=0) means loosing the oscillator status information as well (UPOSC=0).

The impact of loosing the oscillator status (UPOSC=0) in PEE mode is as follows:

- The PLLCLK is derived from the VCO clock (with its actual frequency) divided by four until the PLL locks again.

- The OSCCLK provided to the MSCAN module is off.

Application software needs to be prepared to deal with the impact of loosing the oscillator status at any time.

# 10.4.6.3 PLL Bypassed External Mode (PBE)

In this mode, the Bus Clock is based on the external oscillator clock. The reference clock for the PLL is based on the external oscillator.

The clock sources for COP and RTI can be based on the internal reference clock generator or on the external oscillator clock or the RC-Oscillator (ACLK).

This mode can be entered from default mode PEI by performing the following steps:

- 1. Make sure the PLL configuration is valid.

- 2. Enable the external oscillator (OSCE bit)

- 3. Wait for the oscillator to start-up and the PLL being locked (LOCK = 1) and (UPOSC = 1).

- 4. Clear all flags in the CPMUFLG register to be able to detect any status bit change.

- 5. Optionally status interrupts can be enabled (CPMUINT register).

- 6. Select the Oscillator Clock (OSCCLK) as Bus Clock (PLLSEL=0)

Loosing PLL lock status (LOCK=0) means loosing the oscillator status information as well (UPOSC=0).

The impact of loosing the oscillator status (UPOSC=0) in PBE mode is as follows:

- PLLSEL is set automatically and the Bus Clock is switched back to the PLLCLK.

- The PLLCLK is derived from the VCO clock (with its actual frequency) divided by four until the PLL locks again.

- The OSCCLK provided to the MSCAN module is off.

Application software needs to be prepared to deal with the impact of loosing the oscillator status at any time.

# 11.2 Signal Description

This section lists all inputs to the ADC10B8C block.

## 11.2.1 Detailed Signal Descriptions

### 11.2.1.1 ANx (x = 7, 6, 5, 4, 3, 2, 1, 0)

This pin serves as the analog input Channel *x*. It can also be configured as digital port or external trigger for the ATD conversion.

## 11.2.1.2 ETRIG3, ETRIG2, ETRIG1, ETRIG0

These inputs can be configured to serve as an external trigger for the ATD conversion.

Refer to device specification for availability and connectivity of these inputs!

### 11.2.1.3 VRH, VRL

VRH is the high reference voltage, VRL is the low reference voltage for ATD conversion.

### 11.2.1.4 VDDA, VSSA

These pins are the power supplies for the analog circuitry of the ADC10B8C block.

## 11.3 Memory Map and Register Definition

This section provides a detailed description of all registers accessible in the ADC10B8C.

### 11.3.1 Module Memory Map

Figure 11-2 gives an overview on all ADC10B8C registers.

### NOTE

Register Address = Base Address + Address Offset, where the Base Address is defined at the MCU level and the Address Offset is defined at the module level.

| Address | Name    | Bit 7           | 6     | 5        | 4       | 3        | 2        | 1        | Bit 0    |

|---------|---------|-----------------|-------|----------|---------|----------|----------|----------|----------|

| 0x0000  | ATDCTL0 | R<br>Reserved   | 0     | 0        | 0       | WRAP3    | WRAP2    | WRAP1    | WRAP0    |

| 0x0001  | ATDCTL1 | R<br>W ETRIGSEL | SRES1 | SRES0    | SMP_DIS | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 |

| 0x0002  | ATDCTL2 | R 0<br>W        | AFFC  | Reserved | ETRIGLE | ETRIGP   | ETRIGE   | ASCIE    | ACMPIE   |

|         |         |                 |       |          |         |          |          |          |          |

= Unimplemented or Reserved

Figure 11-2. ADC10B8C Register Summary (Sheet 1 of 2)

MC9S12G Family Reference Manual Rev.1.27

This buffer can be turned on or off with the ATDDIEN register for each ATD input pin. This is important so that the buffer does not draw excess current when an ATD input pin is selected as analog input to the ADC12B8C.

# 12.5 Resets

At reset the ADC12B8C is in a power down state. The reset state of each individual bit is listed within the Register Description section (see Section 12.3.2, "Register Descriptions") which details the registers and their bit-field.

# 12.6 Interrupts

The interrupts requested by the ADC12B8C are listed in Table 12-24. Refer to MCU specification for related vector address and priority.

| Interrupt Source            | CCR<br>Mask | Local Enable      |  |  |

|-----------------------------|-------------|-------------------|--|--|

| Sequence Complete Interrupt | l bit       | ASCIE in ATDCTL2  |  |  |

| Compare Interrupt           | l bit       | ACMPIE in ATDCTL2 |  |  |

### Table 12-24. ATD Interrupt Vectors

See Section 12.3.2, "Register Descriptions" for further details.

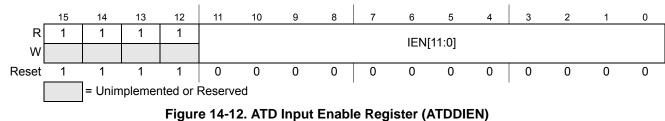

## 14.3.2.10 ATD Input Enable Register (ATDDIEN)

Module Base + 0x000C

### Read: Anytime

Write: Anytime

Table 14-19. ATDDIEN Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11–0<br>IEN[11:0] | <ul> <li>ATD Digital Input Enable on channel x (x= 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) — This bit controls the digital input buffer from the analog input pin (ANx) to the digital data register.</li> <li>0 Disable digital input buffer to ANx pin</li> <li>1 Enable digital input buffer on ANx pin.</li> <li>Note: Setting this bit will enable the corresponding digital input buffer continuously. If this bit is set while simultaneously using it as an analog port, there is potentially increased power consumption because the digital input buffer maybe in the linear region.</li> </ul> |

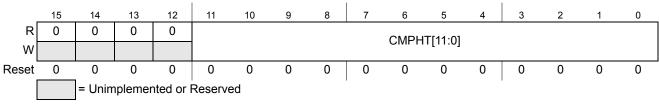

## 14.3.2.11 ATD Compare Higher Than Register (ATDCMPHT)

Writes to this register will abort current conversion sequence.

### Read: Anytime

Write: Anytime

Module Base + 0x000E

### Figure 14-13. ATD Compare Higher Than Register (ATDCMPHT)

#### Table 14-20. ATDCMPHT Field Descriptions

| Field       | Description                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

| 11–0        | Compare Operation Higher Than Enable for conversion number <i>n</i> ( <i>n</i> = 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) of     |

| CMPHT[11:0] | a Sequence (n conversion number, NOT channel number!) — This bit selects the operator for comparison                          |

|             | of conversion results.                                                                                                        |

|             | 0 If result of conversion <i>n</i> is <b>lower or same than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2 |

|             | 1 If result of conversion <i>n</i> is <b>higher than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2        |

#### MC9S12G Family Reference Manual Rev.1.27

Scalable Controller Area Network (S12MSCANV3)

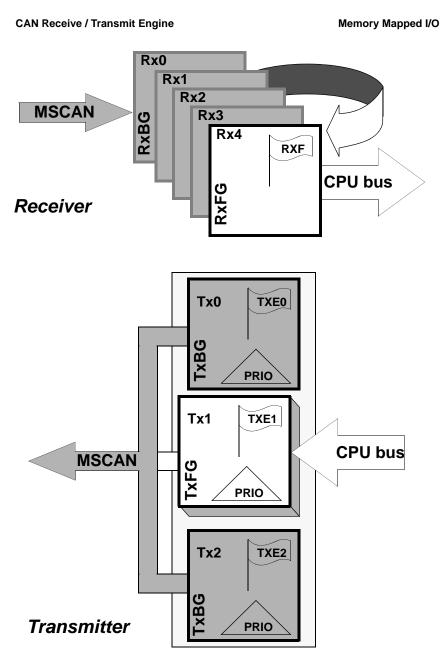

## 18.4.2 Message Storage

Figure 18-39. User Model for Message Buffer Organization

The MSCAN facilitates a sophisticated message storage system which addresses the requirements of a broad range of network applications.

### 18.4.2.1 Message Transmit Background

Modern application layer software is built upon two fundamental assumptions:

### NOTE

Changing the PWM output mode from left aligned to center aligned output (or vice versa) while channels are operating can cause irregularities in the PWM output. It is recommended to program the output mode before enabling the PWM channel.

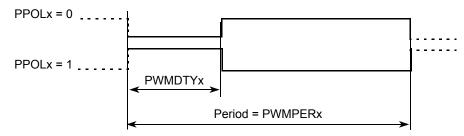

Figure 19-17. PWM Left Aligned Output Waveform

To calculate the output frequency in left aligned output mode for a particular channel, take the selected clock source frequency for the channel (A, B, SA, or SB) and divide it by the value in the period register for that channel.

- PWMx Frequency = Clock (A, B, SA, or SB) / PWMPERx

- PWMx Duty Cycle (high time as a% of period):

Polarity = 0 (PPOLx = 0) Duty Cycle = [(PWMPERx-PWMDTYx)/PWMPERx] \* 100%

Polarity = 1 (PPOLx = 1) Duty Cycle = [PWMDTYx / PWMPERx] \* 100%

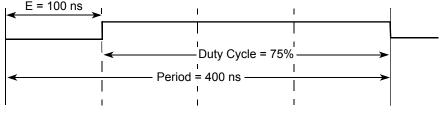

As an example of a left aligned output, consider the following case:

```

Clock Source = E, where E = 10 MHz (100 ns period)

PPOLx = 0

PWMPERx = 4

PWMDTYx = 1

PWMx Frequency = 10 MHz/4 = 2.5 MHz

PWMx Period = 400 ns

PWMx Duty Cycle = 3/4 *100% = 75%

```

The output waveform generated is shown in Figure 19-18.

Figure 19-18. PWM Left Aligned Output Example Waveform

| Field                             | Description                                                                                                                                                               |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCIDRH<br>7<br>R8                 | <b>Received Bit 8</b> — R8 is the ninth data bit received when the SCI is configured for 9-bit data format (M = 1).                                                       |

| SCIDRH<br>6<br>T8                 | <b>Transmit Bit 8</b> — T8 is the ninth data bit transmitted when the SCI is configured for 9-bit data format (M = 1).                                                    |

| SCIDRL<br>7:0<br>R[7:0]<br>T[7:0] | <ul> <li>R7:R0 — Received bits seven through zero for 9-bit or 8-bit data formats</li> <li>T7:T0 — Transmit bits seven through zero for 9-bit or 8-bit formats</li> </ul> |

#### Table 20-13. SCIDRH and SCIDRL Field Descriptions

### NOTE

If the value of T8 is the same as in the previous transmission, T8 does not have to be rewritten. The same value is transmitted until T8 is rewritten

In 8-bit data format, only SCI data register low (SCIDRL) needs to be accessed.

When transmitting in 9-bit data format and using 8-bit write instructions, write first to SCI data register high (SCIDRH), then SCIDRL.

## 20.4 Functional Description

This section provides a complete functional description of the SCI block, detailing the operation of the design from the end user perspective in a number of subsections.

Figure 20-14 shows the structure of the SCI module. The SCI allows full duplex, asynchronous, serial communication between the CPU and remote devices, including other CPUs. The SCI transmitter and receiver operate independently, although they use the same baud rate generator. The CPU monitors the status of the SCI, writes the data to be transmitted, and processes received data.

### Table 22-16. PTPSR Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Precision Timer Prescaler Select Bits</b> — These eight bits specify the division rate of the main Timer prescaler. These are effective only when the PRNT bit of TSCR1 is set to 1. Table 22-17 shows some selection examples in this case. The newly selected prescale factor will not take effect until the next synchronized edge where all prescale counter stages equal zero. |

The Prescaler can be calculated as follows depending on logical value of the PTPS[7:0] and PRNT bit:

PRNT = 1 : Prescaler = PTPS[7:0] + 1

| PTPS7 | PTPS6 | PTPS5 | PTPS4 | PTPS3 | PTPS2 | PTPS1 | PTPS0 | Prescale<br>Factor |

|-------|-------|-------|-------|-------|-------|-------|-------|--------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 2                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 3                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 4                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| 0     | 0     | 0     | 1     | 0     | 0     | 1     | 1     | 20                 |

| 0     | 0     | 0     | 1     | 0     | 1     | 0     | 0     | 21                 |

| 0     | 0     | 0     | 1     | 0     | 1     | 0     | 1     | 22                 |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 253                |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1     | 254                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 255                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 256                |

Table 22-17. Precision Timer Prescaler Selection Examples when PRNT = 1

# 22.4 Functional Description

This section provides a complete functional description of the timer TIM16B6CV3 block. Please refer to the detailed timer block diagram in Figure 22-22 as necessary.

16 KByte Flash Module (S12FTMRG16K1V1)

## 24.4.8 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 24.4.7, "Interrupts").

## 24.4.9 Stop Mode

If a Flash command is active (CCIF = 0) when the MCU requests stop mode, the current Flash operation will be completed before the MCU is allowed to enter stop mode.

# 24.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 24-11). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x3\_FF0F. The security state out of reset can be permanently changed by programming the security byte assuming that the MCU is starting from a mode where the necessary P-Flash erase and program commands are available and that the upper region of the P-Flash is unprotected. If the Flash security byte is successfully programmed, its new value will take affect after the next MCU reset.

The following subsections describe these security-related subjects:

- Unsecuring the MCU using Backdoor Key Access

- Unsecuring the MCU in Special Single Chip Mode using BDM

- Mode and Security Effects on Flash Command Availability

# 24.5.1 Unsecuring the MCU using Backdoor Key Access

The MCU may be unsecured by using the backdoor key access feature which requires knowledge of the contents of the backdoor keys (four 16-bit words programmed at addresses 0x3\_FF00-0x3\_FF07). If the KEYEN[1:0] bits are in the enabled state (see Section 24.3.2.2), the Verify Backdoor Access Key command (see Section 24.4.6.11) allows the user to present four prospective keys for comparison to the keys stored in the Flash memory via the Memory Controller. If the keys presented in the Verify Backdoor Access Key command match the backdoor keys stored in the Flash memory, the SEC bits in the FSEC register (see Table 24-11) will be changed to unsecure the MCU. Key values of 0x0000 and 0xFFFF are not permitted as backdoor keys. While the Verify Backdoor Access Key command is active, P-Flash memory and EEPROM memory will not be available for read access and will return invalid data.

Table 26-36. Erase Verify P-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |  |  |

|-------------|----------------------------------------------------------|----------------------------------------------|--|--|

| 000         | 0x03                                                     | Global address [17:16] of<br>a P-Flash block |  |  |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |  |  |

| 010         | Number of phrases to be verified                         |                                              |  |  |

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 26-37. Erase Verify P-Flash Section Command Error Handling

| Register | Error Bit | Error Condition                                                                                   |  |  |  |

|----------|-----------|---------------------------------------------------------------------------------------------------|--|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                                                       |  |  |  |

|          |           | Set if command not available in current mode (see Table 26-27)                                    |  |  |  |

|          |           | Set if an invalid global address [17:0] is supplied see Table 26-3)                               |  |  |  |

|          |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                      |  |  |  |

| FSTAT    |           | Set if the requested section crosses a the P-Flash address boundary                               |  |  |  |

|          | FPVIOL    | None                                                                                              |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check faile                   |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |  |  |  |

### 26.4.6.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once command described in Section 26.4.6.6. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

Table 26-38. Read Once Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                         |  |  |  |

|-------------|------------------------------------------|--|--|--|

| 000         | 0x04 Not Required                        |  |  |  |

| 001         | Read Once phrase index (0x0000 - 0x0007) |  |  |  |

| 010         | Read Once word 0 value                   |  |  |  |

| 011         | Read Once word 1 value                   |  |  |  |

| 100         | Read Once word 2 value                   |  |  |  |

| 101         | Read Once word 3 value                   |  |  |  |

#### 64 KByte Flash Module (S12FTMRG64K1V1)

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|------|-------------------------------------------|

| 010         | HI   | Data 0 [15:8]                             |

| 010         | LO   | Data 0 [7:0]                              |

| 011         | HI   | Data 1 [15:8]                             |

| 011         | LO   | Data 1 [7:0]                              |

| 100         | HI   | Data 2 [15:8]                             |

| 100         | LO   | Data 2 [7:0]                              |

| 101         | HI   | Data 3 [15:8]                             |

| 101         | LO   | Data 3 [7:0]                              |

Table 27-24. FCCOB - NVM Command Mode (Typical Usage)

### 27.3.2.12 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000C

Offset Module Base + 0x000D

Figure 27-18. Flash Reserved1 Register (FRSV1)

All bits in the FRSV1 register read 0 and are not writable.

## 27.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

Figure 27-19. Flash Reserved2 Register (FRSV2)

All bits in the FRSV2 register read 0 and are not writable.

### 27.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

#### 96 KByte Flash Module (S12FTMRG96K1V1)

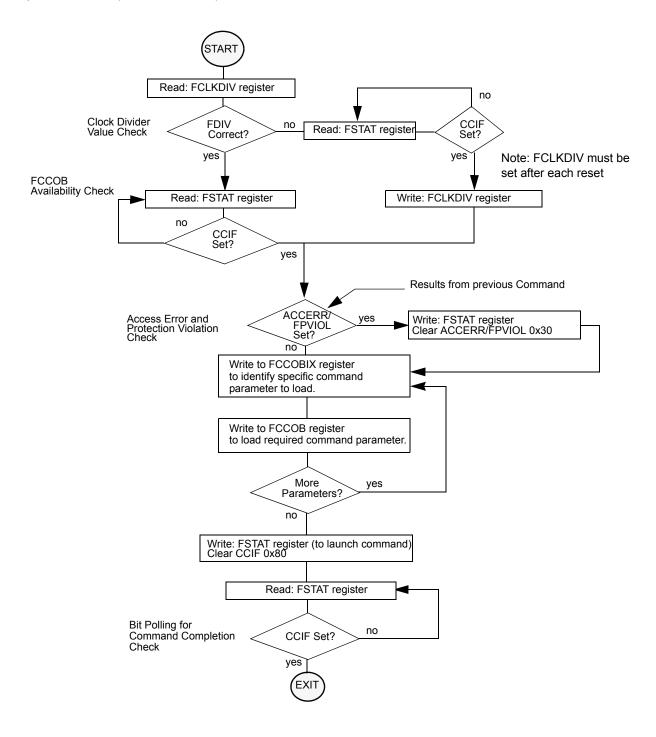

Figure 28-26. Generic Flash Command Write Sequence Flowchart

MC9S12G Family Reference Manual Rev.1.27

#### 96 KByte Flash Module (S12FTMRG96K1V1)

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 28.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 28.4.6.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0x3\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x3\_FF00-0x3\_FF07 are unaffected by the Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired. In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses 0x3\_FF00-0x3\_FF07 in the Flash configuration field.

## 28.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

A secured MCU can be unsecured in special single chip mode by using the following method to erase the P-Flash and EEPROM memory:

- 1. Reset the MCU into special single chip mode

- 2. Delay while the BDM executes the Erase Verify All Blocks command write sequence to check if the P-Flash and EEPROM memories are erased

- 3. Send BDM commands to disable protection in the P-Flash and EEPROM memory

- 4. Execute the Erase All Blocks command write sequence to erase the P-Flash and EEPROM memory. Alternatively the Unsecure Flash command can be executed, if so the steps 5 and 6 below are skeeped.

- 5. After the CCIF flag sets to indicate that the Erase All Blocks operation has completed, reset the MCU into special single chip mode

- 6. Delay while the BDM executes the Erase Verify All Blocks command write sequence to verify that the P-Flash and EEPROM memory are erased

If the P-Flash and EEPROM memory are verified as erased, the MCU will be unsecured. All BDM commands will now be enabled and the Flash security byte may be programmed to the unsecure state by continuing with the following steps:

7. Send BDM commands to execute the Program P-Flash command write sequence to program the Flash security byte to the unsecured state

#### 192 KByte Flash Module (S12FTMRG192K2V1)

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 31-55.

| CCOB<br>(CCOBIX=001) | Level Description                |  |

|----------------------|----------------------------------|--|

| 0x0000               | Return to Normal Level           |  |

| 0x0001               | User Margin-1 Level <sup>1</sup> |  |

| 0x0002               | User Margin-0 Level <sup>2</sup> |  |

### Table 31-55. Valid Set User Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

### Table 31-56. Set User Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                 |

|----------|-----------|-----------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 001 at command launch.                    |

|          | ACCERR    | Set if command not available in current mode (see Table 31-27). |

| FSTAT    |           | Set if an invalid margin level setting is supplied.             |

| FSTAT    | FPVIOL    | None                                                            |

|          | MGSTAT1   | None                                                            |

|          | MGSTAT0   | None                                                            |

### NOTE

User margin levels can be used to check that Flash memory contents have adequate margin for normal level read operations. If unexpected results are encountered when checking Flash memory contents at user margin levels, a potential loss of information has been detected.

### 31.4.6.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of the P-Flash or EEPROM block.

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

/4 dimensions to be determined at seating plane c.

5. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 mm AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm.

A THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

$/\overline{2}$  exact shape of each corner is optional.

A. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 mm AND 0.25 mm FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--------------|------------------|-------------|

| TITLE: 64LD LQFP,                                       | DOCUMENT NO  | : 98ASS23234W    | REV: E      |

| 10 X 10 X 1.4 P                                         | CASE NUMBER  | : 840F-02        | 11 AUG 2006 |

| 0.5 PITCH, CASE OU                                      | STANDARD: JE | DEC MS-026 BCD   |             |