Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 40                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1.5K x 8                                                               |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g48f0clfr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.3.15 Reference Voltage Attenuator (RVA)

• Attenuation of ADC reference voltage with low long-term drift

### 1.3.16 Digital-to-Analog Converter Module (DAC)

- 1 digital-analog converter channel (per module) with:

- 8 bit resolution

- full and reduced output voltage range

- buffered or unbuffered analog output voltage usable

- operational amplifier stand alone usable

### 1.3.17 Analog Comparator (ACMP)

- Low offset, low long-term offset drift

- Selectable interrupt on rising, falling, or rising and falling edges of comparator output

- Option to output comparator signal on an external pin

- Option to trigger timer input capture events

### 1.3.18 On-Chip Voltage Regulator (VREG)

- Linear voltage regulator with bandgap reference

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR) circuit

- Low-voltage reset (LVR)

### 1.3.19 Background Debug (BDM)

- Non-intrusive memory access commands

- Supports in-circuit programming of on-chip nonvolatile memory

### 1.3.20 Debugger (DBG)

- Trace buffer with depth of 64 entries

- Three comparators (A, B and C)

- Access address comparisons with optional data comparisons

- Program counter comparisons

- Exact address or address range comparisons

- Two types of comparator matches

- Tagged This matches just before a specific instruction begins execution

- Force This is valid on the first instruction boundary after a match occurs

- Four trace modes

# 1.8.9.4 Known Good Die Option (KGD)

|                      | Function <lowestpriorityhighest></lowestpriorityhighest> |                |              | Power        | Internal Pull<br>Resistor |            |                |

|----------------------|----------------------------------------------------------|----------------|--------------|--------------|---------------------------|------------|----------------|

| Wire Bond<br>Die Pad | Pin                                                      | 2nd<br>Func.   | 3rd<br>Func. | 4th<br>Func. | Supply                    | CTRL       | Reset<br>State |

| 1                    | PJ6                                                      | KWJ6           | SCK2         | _            | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

| 2                    | PJ5                                                      | KWJ5           | MOSI2        | —            | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

| 3                    | PJ4                                                      | KWJ4           | MISO2        | —            | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

| 4                    | PA0                                                      | —              | _            | —            | V <sub>DDX</sub>          | PUCR/PUPAE | Disabled       |

| 5                    | PA1                                                      | _              |              | _            | V <sub>DDX</sub>          | PUCR/PUPAE | Disabled       |

| 6                    | PA2                                                      | _              | _            | —            | V <sub>DDX</sub>          | PUCR/PUPAE | Disabled       |

| 7                    | PA3                                                      | _              |              | _            | V <sub>DDX</sub>          | PUCR/PUPAE | Disabled       |

| 8                    | RESET                                                    | _              | _            | —            | V <sub>DDX</sub>          | PULLU      | P              |

| 9                    | VDDX1                                                    | _              | _            | —            | _                         | _          | _              |

| 10                   | VDDR                                                     | _              |              | _            | _                         | _          | _              |

| 11                   | VSSX1                                                    | _              | _            | —            | _                         | _          | _              |

| 12                   | PE0 <sup>1</sup>                                         | EXTAL          | _            | —            | V <sub>DDX</sub>          | PUCR/PDPEE | Down           |

| 13                   | VSS                                                      | _              | _            | —            | _                         | _          | _              |

| 14                   | PE1 <sup>1</sup>                                         | XTAL           | _            | —            | V <sub>DDX</sub>          | PUCR/PDPEE | Down           |

| 15                   | TEST                                                     | _              |              | _            | N.A.                      | RESET pin  | Down           |

| 16                   | PA4                                                      | _              |              | _            | V <sub>DDX</sub>          | PUCR/PUPAE | Disabled       |

| 17                   | PA5                                                      | _              |              | _            | V <sub>DDX</sub>          | PUCR/PUPAE | Disabled       |

| 18                   | PA6                                                      | _              | _            | —            | V <sub>DDX</sub>          | PUCR/PUPAE | Disabled       |

| 19                   | PA7                                                      | _              |              | _            | V <sub>DDX</sub>          | PUCR/PUPAE | Disabled       |

| 20                   | PJ0                                                      | KWJ0           | MISO1        | —            | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

| 21                   | PJ1                                                      | KWJ1           | MOSI1        | _            | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

| 22                   | PJ2                                                      | KWJ2           | SCK1         | _            | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

| 23                   | PJ3                                                      | KWJ3           | SS1          | _            | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

| 24                   | BKGD                                                     | MODC           |              | _            | V <sub>DDX</sub>          | PUCR/BKPUE | Up             |

| 25                   | PB0                                                      | ECLK           |              | _            | V <sub>DDX</sub>          | PUCR/PUPBE | Disabled       |

| 26                   | PB1                                                      | API_EXTC<br>LK |              | —            | V <sub>DDX</sub>          | PUCR/PUPBE | Disabled       |

Table 1-32. KGD Option for S12GA192 and S12GA240

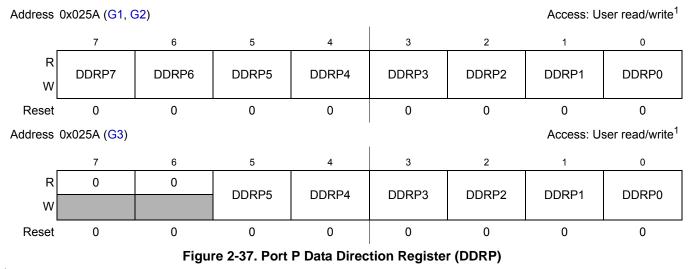

# 2.4.3.36 Port P Data Direction Register (DDRP)

<sup>1</sup> Read: Anytime

Write: Anytime

#### Table 2-63. DDRP Register Field Descriptions

| Field       | Description                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------|

| 7-0<br>DDRP | <b>Port P data direction</b> —<br>This bit determines whether the associated pin is an input or output. |

|             | 1 Associated pin configured as output<br>0 Associated pin configured as input                           |

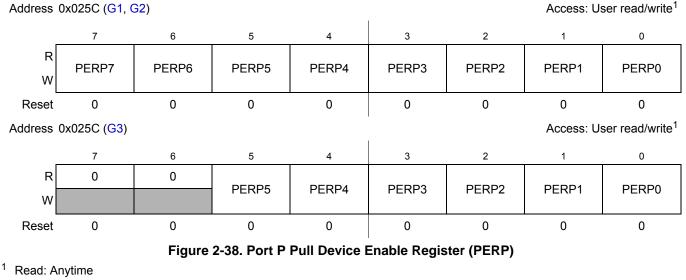

### 2.4.3.37 Port P Pull Device Enable Register (PERP)

Write: Anytime

MC9S12G Family Reference Manual Rev.1.27

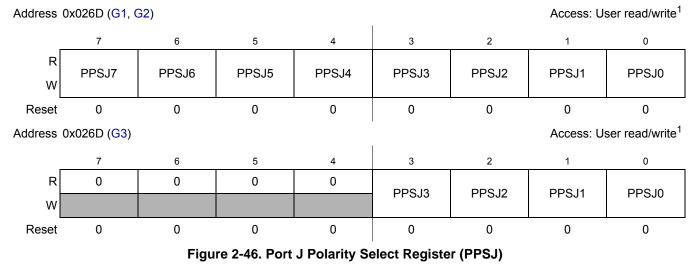

### 2.4.3.46 Port J Polarity Select Register (PPSJ)

<sup>1</sup> Read: Anytime

Write: Anytime

#### Table 2-72. PPSJ Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PPSJ | <b>Port J pull device select</b> —Configure pull device and pin interrupt edge polarity on input pin<br>This bit selects a pullup or a pulldown device if enabled on the associated port input pin.<br>This bit also selects the polarity of the active pin interrupt edge. |

|             | 1 Pulldown device selected; rising edge selected<br>0 Pullup device selected; falling edge selected                                                                                                                                                                         |

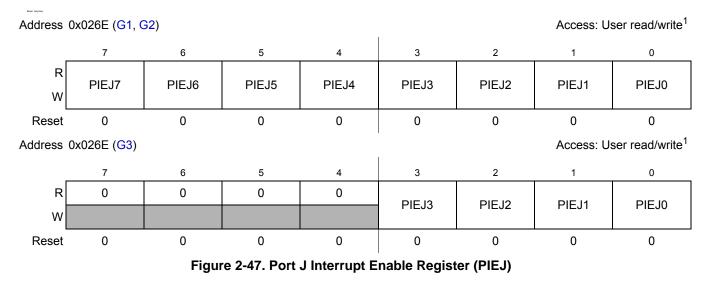

### 2.4.3.47 Port J Interrupt Enable Register (PIEJ)

| RWE Bit | RW Bit | RW Signal | Comment                   |

|---------|--------|-----------|---------------------------|

| 0       | х      | 0         | RW not used in comparison |

| 0       | х      | 1         | RW not used in comparison |

| 1       | 0      | 0         | Write data bus            |

| 1       | 0      | 1         | No match                  |

| 1       | 1      | 0         | No match                  |

| 1       | 1      | 1         | Read data bus             |

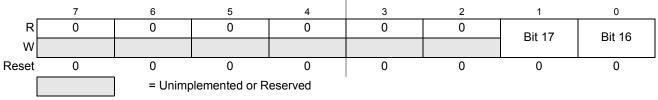

### 8.3.2.8.2 Debug Comparator Address High Register (DBGXAH)

Address: 0x0029

The DBGC1\_COMRV bits determine which comparator address registers are visible in the 8-byte window from 0x0028 to 0x002F as shown in Section Table 8-24., "Comparator Address Register Visibility

Table 8-24. Comparator Address Register Visibility

| COMRV | Visible Comparator     |

|-------|------------------------|

| 00    | DBGAAH, DBGAAM, DBGAAL |

| 01    | DBGBAH, DBGBAM, DBGBAL |

| 10    | DBGCAH, DBGCAM, DBGCAL |

| 11    | None                   |

Read: Anytime. See Table 8-24 for visible register encoding.

Write: If DBG not armed. See Table 8-24 for visible register encoding.

#### Table 8-25. DBGXAH Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Comparator Address High Compare Bits — The Comparator address high compare bits control whether the selected comparator compares the address bus bits [17:16] to a logic one or logic zero.</li> <li>Compare corresponding address bit to a logic zero</li> <li>Compare corresponding address bit to a logic one</li> </ul> |

Analog-to-Digital Converter (ADC10B12CV2)

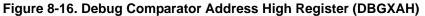

# 13.3.2.7 ATD Status Register 0 (ATDSTAT0)

This register contains the Sequence Complete Flag, overrun flags for external trigger and FIFO mode, and the conversion counter.

Module Base + 0x0006

Figure 13-9. ATD Status Register 0 (ATDSTAT0)

Read: Anytime

Write: Anytime (No effect on (CC3, CC2, CC1, CC0))

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SCF   | Sequence Complete Flag — This flag is set upon completion of a conversion sequence. If conversion sequences are continuously performed (SCAN=1), the flag is set after each one is completed. This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to SCF</li> <li>B) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>C) If AFFC=1 and a result register is read</li> <li>Conversion sequence not completed</li> <li>Conversion sequence has completed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5<br>ETORF | <ul> <li>External Trigger Overrun Flag — While in edge sensitive mode (ETRIGLE=0), if additional active edges are detected while a conversion sequence is in process the overrun flag is set. This flag is cleared when one of the following occurs:         <ul> <li>A) Write "1" to ETORF</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> </li> <li>No External trigger overrun error has occurred</li> <li>External trigger overrun error has occurred</li> </ul>                                                                                                                                                                                                                                                                                                                    |

| 4<br>FIFOR | Result Register Overrun Flag — This bit indicates that a result register has been written to before its associated conversion complete flag (CCF) has been cleared. This flag is most useful when using the FIFO mode because the flag potentially indicates that result registers are out of sync with the input channels. However, it is also practical for non-FIFO modes, and indicates that a result register has been overwritten before it has been read (i.e. the old data has been lost). This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to FIFOR</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> <li>No overrun has occurred</li> <li>Overrun condition exists (result register has been written while associated CCFx flag was still set)</li> |

Analog-to-Digital Converter (ADC10B16CV2)

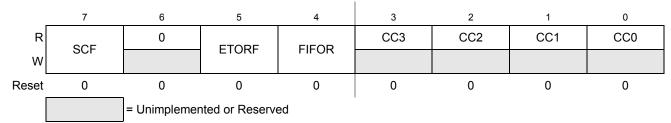

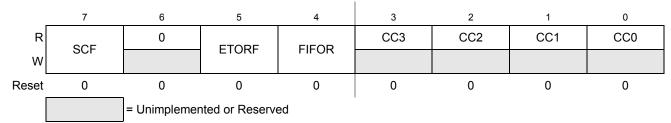

# 15.3.2.7 ATD Status Register 0 (ATDSTAT0)

This register contains the Sequence Complete Flag, overrun flags for external trigger and FIFO mode, and the conversion counter.

Module Base + 0x0006

Figure 15-9. ATD Status Register 0 (ATDSTAT0)

Read: Anytime

Write: Anytime (No effect on (CC3, CC2, CC1, CC0))

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SCF   | Sequence Complete Flag — This flag is set upon completion of a conversion sequence. If conversion sequences are continuously performed (SCAN=1), the flag is set after each one is completed. This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to SCF</li> <li>B) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>C) If AFFC=1 and a result register is read</li> </ul> <li>O Conversion sequence not completed</li> <li>1 Conversion sequence has completed</li>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5<br>ETORF | <ul> <li>External Trigger Overrun Flag — While in edge sensitive mode (ETRIGLE=0), if additional active edges are detected while a conversion sequence is in process the overrun flag is set. This flag is cleared when one of the following occurs:         <ul> <li>A) Write "1" to ETORF</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> </li> <li>No External trigger overrun error has occurred</li> <li>External trigger overrun error has occurred</li> </ul>                                                                                                                                                                                                                                                                                                                    |

| 4<br>FIFOR | Result Register Overrun Flag — This bit indicates that a result register has been written to before its associated conversion complete flag (CCF) has been cleared. This flag is most useful when using the FIFO mode because the flag potentially indicates that result registers are out of sync with the input channels. However, it is also practical for non-FIFO modes, and indicates that a result register has been overwritten before it has been read (i.e. the old data has been lost). This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to FIFOR</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> <li>No overrun has occurred</li> <li>Overrun condition exists (result register has been written while associated CCFx flag was still set)</li> |

# 15.5 Resets

At reset the ADC10B16C is in a power down state. The reset state of each individual bit is listed within the Register Description section (see Section 15.3.2, "Register Descriptions") which details the registers and their bit-field.

# 15.6 Interrupts

The interrupts requested by the ADC10B16C are listed in Table 15-24. Refer to MCU specification for related vector address and priority.

| Interrupt Source            | CCR<br>Mask | Local Enable      |

|-----------------------------|-------------|-------------------|

| Sequence Complete Interrupt | I bit       | ASCIE in ATDCTL2  |

| Compare Interrupt           | l bit       | ACMPIE in ATDCTL2 |

#### Table 15-24. ATD Interrupt Vectors

See Section 15.3.2, "Register Descriptions" for further details.

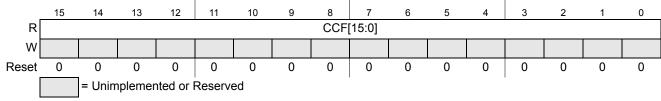

### 16.3.2.9 ATD Status Register 2 (ATDSTAT2)

This read-only register contains the Conversion Complete Flags CCF[15:0].

Module Base + 0x000A

#### Read: Anytime

Write: Anytime (for details see Table 16-18 below)

#### Table 16-18. ATDSTAT2 Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>CCF[15:0] | <b>Conversion Complete Flag n (n= 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) (n conversion number, NOT channel number!)</b> — A conversion complete flag is set at the end of each conversion in a sequence. The flags are associated with the conversion position in a sequence (and also the result register number). Therefore in non-fifo mode, CCF[4] is set when the fifth conversion in a sequence is complete and the result is available in result register ATDDR4; CCF[5] is set when the sixth conversion in a sequence is complete and the result is available in ATDDR5, and so forth.                                                                                                                                                |

|                   | If automatic compare of conversion results is enabled (CMPE[ <i>n</i> ]=1 in ATDCMPE), the conversion complete flag<br>is only set if comparison with ATDDR <i>n</i> is true. If ACMPIE=1 a compare interrupt will be requested. In this case,<br>as the ATDDR <i>n</i> result register is used to hold the compare value, the result will not be stored there at the end of<br>the conversion but is lost.<br>A flag CCF[ <i>n</i> ] is cleared when one of the following occurs:<br>A) Write to ATDCTL5 (a new conversion sequence is started)<br>B) If AFFC=0, write "1" to CCF[ <i>n</i> ]<br>C) If AFFC=1 and CMPE[ <i>n</i> ]=0, read of result register ATDDR <i>n</i><br>D) If AFFC=1 and CMPE[ <i>n</i> ]=1, write to result register ATDDR <i>n</i> |

|                   | <ul> <li>In case of a concurrent set and clear on CCF[<i>n</i>]: The clearing by method A) will overwrite the set. The clearing by methods B) or C) or D) will be overwritten by the set.</li> <li>Conversion number <i>n</i> not completed or successfully compared</li> <li>If (CMPE[<i>n</i>]=0): Conversion number <i>n</i> has completed. Result is ready in ATDDR<i>n</i>. If (CMPE[<i>n</i>]=1): Compare for conversion result number <i>n</i> with compare value in ATDDR<i>n</i>, using compare operator CMPGT[<i>n</i>] is true. (No result available in ATDDR<i>n</i>)</li> </ul>                                                                                                                                                                  |

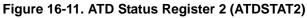

### 16.3.2.12 ATD Conversion Result Registers (ATDDR*n*)

The A/D conversion results are stored in 16 result registers. Results are always in unsigned data representation. Left and right justification is selected using the DJM control bit in ATDCTL3.

If automatic compare of conversions results is enabled (CMPE[n]=1 in ATDCMPE), these registers must be written with the compare values in left or right justified format depending on the actual value of the DJM bit. In this case, as the ATDDRn register is used to hold the compare value, the result will not be stored there at the end of the conversion but is lost.

#### Attention, n is the conversion number, NOT the channel number!

Read: Anytime

Write: Anytime

#### NOTE

For conversions not using automatic compare, results are stored in the result registers after each conversion. In this case avoid writing to ATDDRn except for initial values, because an A/D result might be overwritten.

#### 16.3.2.12.1 Left Justified Result Data (DJM=0)

```

Module Base +

```

```

0x0010 = ATDDR0, 0x0012 = ATDDR1, 0x0014 = ATDDR2, 0x0016 = ATDDR3

0x0018 = ATDDR4, 0x001A = ATDDR5, 0x001C = ATDDR6, 0x001E = ATDDR7

0x0020 = ATDDR8, 0x0022 = ATDDR9, 0x0024 = ATDDR10, 0x0026 = ATDDR11

0x0028 = ATDDR12, 0x002A = ATDDR13, 0x002C = ATDDR14, 0x002E = ATDDR15

```

#### Figure 16-14. Left justified ATD conversion result register (ATDDRn)

Table 16-21 shows how depending on the A/D resolution the conversion result is transferred to the ATD result registers for left justified data. Compare is always done using all 12 bits of both the conversion result and the compare value in ATDDRn.

| A/D<br>resolution | DJM | conversion result mapping to ATDDR <i>n</i>                   |

|-------------------|-----|---------------------------------------------------------------|

| 8-bit data        | 0   | Result-Bit[11:4] = conversion result,<br>Result-Bit[3:0]=0000 |

| 10-bit data       | 0   | Result-Bit[11:2] = conversion result,<br>Result-Bit[1:0]=00   |

| 12-bit data       | 0   | Result-Bit[11:0] = result                                     |

#### Table 16-21. Conversion result mapping to ATDDRn

| Field            | Description                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6–4<br>PCKB[2:0] | <b>Prescaler Select for Clock B</b> — Clock B is one of two clock sources which can be used for all channels. These three bits determine the rate of clock B, as shown in Table 19-8. |

| 2–0<br>PCKA[2:0] | <b>Prescaler Select for Clock A</b> — Clock A is one of two clock sources which can be used for all channels. These three bits determine the rate of clock A, as shown in Table 19-8. |

#### Table 19-7. PWMPRCLK Field Descriptions

# Table 19-8. Clock A or Clock B Prescaler Selects

| PCKA/B2 | PCKA/B1 | PCKA/B0 | Value of Clock A/B |

|---------|---------|---------|--------------------|

| 0       | 0       | 0       | Bus clock          |

| 0       | 0       | 1       | Bus clock / 2      |

| 0       | 1       | 0       | Bus clock / 4      |

| 0       | 1       | 1       | Bus clock / 8      |

| 1       | 0       | 0       | Bus clock / 16     |

| 1       | 0       | 1       | Bus clock / 32     |

| 1       | 1       | 0       | Bus clock / 64     |

| 1       | 1       | 1       | Bus clock / 128    |

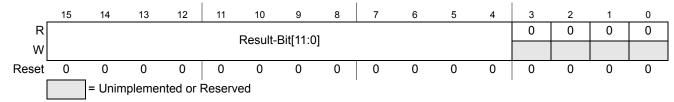

### 19.3.2.5 PWM Center Align Enable Register (PWMCAE)

The PWMCAE register contains eight control bits for the selection of center aligned outputs or left aligned outputs for each PWM channel. If the CAEx bit is set to a one, the corresponding PWM output will be center aligned. If the CAEx bit is cleared, the corresponding PWM output will be left aligned. See Section 19.4.2.5, "Left Aligned Outputs" and Section 19.4.2.6, "Center Aligned Outputs" for a more detailed description of the PWM output modes.

Module Base + 0x0004

Figure 19-7. PWM Center Align Enable Register (PWMCAE)

Read: Anytime

Write: Anytime

#### NOTE

Write these bits only when the corresponding channel is disabled.

| APPRO APPRO APPRO APPRO APPRO Baud Rate |       |       |      |      |      |         |                |

|-----------------------------------------|-------|-------|------|------|------|---------|----------------|

| SPPR2                                   | SPPR1 | SPPR0 | SPR2 | SPR1 | SPR0 | Divisor | Baud Rate      |

| 0                                       | 0     | 1     | 0    | 1    | 0    | 16      | 1.5625 Mbit/s  |

| 0                                       | 0     | 1     | 0    | 1    | 1    | 32      | 781.25 kbit/s  |

| 0                                       | 0     | 1     | 1    | 0    | 0    | 64      | 390.63 kbit/s  |

| 0                                       | 0     | 1     | 1    | 0    | 1    | 128     | 195.31 kbit/s  |

| 0                                       | 0     | 1     | 1    | 1    | 0    | 256     | 97.66 kbit/s   |

| 0                                       | 0     | 1     | 1    | 1    | 1    | 512     | 48.83 kbit/s   |

| 0                                       | 1     | 0     | 0    | 0    | 0    | 6       | 4.16667 Mbit/s |

| 0                                       | 1     | 0     | 0    | 0    | 1    | 12      | 2.08333 Mbit/s |

| 0                                       | 1     | 0     | 0    | 1    | 0    | 24      | 1.04167 Mbit/s |

| 0                                       | 1     | 0     | 0    | 1    | 1    | 48      | 520.83 kbit/s  |

| 0                                       | 1     | 0     | 1    | 0    | 0    | 96      | 260.42 kbit/s  |

| 0                                       | 1     | 0     | 1    | 0    | 1    | 192     | 130.21 kbit/s  |

| 0                                       | 1     | 0     | 1    | 1    | 0    | 384     | 65.10 kbit/s   |

| 0                                       | 1     | 0     | 1    | 1    | 1    | 768     | 32.55 kbit/s   |

| 0                                       | 1     | 1     | 0    | 0    | 0    | 8       | 3.125 Mbit/s   |

| 0                                       | 1     | 1     | 0    | 0    | 1    | 16      | 1.5625 Mbit/s  |

| 0                                       | 1     | 1     | 0    | 1    | 0    | 32      | 781.25 kbit/s  |

| 0                                       | 1     | 1     | 0    | 1    | 1    | 64      | 390.63 kbit/s  |

| 0                                       | 1     | 1     | 1    | 0    | 0    | 128     | 195.31 kbit/s  |

| 0                                       | 1     | 1     | 1    | 0    | 1    | 256     | 97.66 kbit/s   |

| 0                                       | 1     | 1     | 1    | 1    | 0    | 512     | 48.83 kbit/s   |

| 0                                       | 1     | 1     | 1    | 1    | 1    | 1024    | 24.41 kbit/s   |

| 1                                       | 0     | 0     | 0    | 0    | 0    | 10      | 2.5 Mbit/s     |

| 1                                       | 0     | 0     | 0    | 0    | 1    | 20      | 1.25 Mbit/s    |

| 1                                       | 0     | 0     | 0    | 1    | 0    | 40      | 625 kbit/s     |

| 1                                       | 0     | 0     | 0    | 1    | 1    | 80      | 312.5 kbit/s   |

| 1                                       | 0     | 0     | 1    | 0    | 0    | 160     | 156.25 kbit/s  |

| 1                                       | 0     | 0     | 1    | 0    | 1    | 320     | 78.13 kbit/s   |

| 1                                       | 0     | 0     | 1    | 1    | 0    | 640     | 39.06 kbit/s   |

| 1                                       | 0     | 0     | 1    | 1    | 1    | 1280    | 19.53 kbit/s   |

| 1                                       | 0     | 1     | 0    | 0    | 0    | 12      | 2.08333 Mbit/s |

| 1                                       | 0     | 1     | 0    | 0    | 1    | 24      | 1.04167 Mbit/s |

| 1                                       | 0     | 1     | 0    | 1    | 0    | 48      | 520.83 kbit/s  |

| 1                                       | 0     | 1     | 0    | 1    | 1    | 96      | 260.42 kbit/s  |

| 1                                       | 0     | 1     | 1    | 0    | 0    | 192     | 130.21 kbit/s  |

| 1                                       | 0     | 1     | 1    | 0    | 1    | 384     | 65.10 kbit/s   |

| 1                                       | 0     | 1     | 1    | 1    | 0    | 768     | 32.55 kbit/s   |

| 1                                       | 0     | 1     | 1    | 1    | 1    | 1536    | 16.28 kbit/s   |

| 1                                       | 1     | 0     | 0    | 0    | 0    | 14      | 1.78571 Mbit/s |

Table 21-6. Example SPI Baud Rate Selection (25 MHz Bus Clock)

MC9S12G Family Reference Manual Rev.1.27

#### Table 22-13. TRLG1 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field          | Description                                                                                                                                                                                                      |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5:0<br>C[5:0]F | Input Capture/Output Compare Channel "x" Flag — These flags are set when an input capture or output compare event occurs. Clearing requires writing a one to the corresponding flag bit while TEN is set to one. |  |  |

|                | <b>Note:</b> When TFFCA bit in TSCR register is set, a read from an input capture or a write into an output compare channel (0x0010–0x001F) will cause the corresponding channel flag CxF to be cleared.         |  |  |

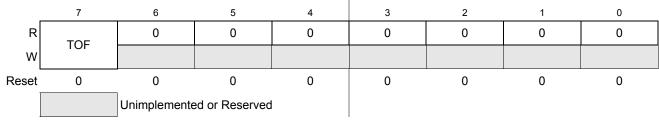

### 22.3.2.11 Main Timer Interrupt Flag 2 (TFLG2)

Module Base + 0x000F

Figure 22-17. Main Timer Interrupt Flag 2 (TFLG2)

TFLG2 indicates when interrupt conditions have occurred. To clear a bit in the flag register, write the bit to one while TEN bit of TSCR1.

Read: Anytime

Write: Used in clearing mechanism (set bits cause corresponding bits to be cleared).

Any access to TCNT will clear TFLG2 register if the TFFCA bit in TSCR register is set.

#### Table 22-14. TRLG2 Field Descriptions

| Field | Description                                                                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Timer Overflow Flag</b> — Set when 16-bit free-running timer overflows from 0xFFFF to 0x0000. Clearing this bit requires writing a one to bit 7 of TFLG2 register while the TEN bit of TSCR1 is set to one. |

#### Table 23-4. OC7M Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7:0<br>OC7M[7:0] | <ul> <li>Output Compare 7 Mask — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. For each OC7M bit that is set, the output compare action reflects the corresponding OC7D bit.</li> <li>0 The corresponding OC7Dx bit in the output compare 7 data register will not be transferred to the timer port on a channel 7 event, even if the corresponding pin is setup for output compare.</li> <li>1 The corresponding OC7Dx bit in the output compare 7 data register will be transferred to the timer port on a channel 7 event.</li> <li>Note: The corresponding channel must also be setup for output compare (IOSx = 1 and OCPDx = 0) for data to be transferred from the output compare 7 data register to the timer port.</li> </ul> |  |  |

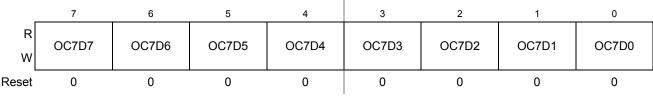

### 23.3.2.4 Output Compare 7 Data Register (OC7D)

1.

Module Base + 0x0003

Figure 23-9. Output Compare 7 Data Register (OC7D)

Read: Anytime

Write: Anytime

#### Table 23-5. OC7D Field Descriptions

| Field | Description                                                                                                                                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Output Compare 7 Data</b> — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a                                                                                |

|       | successful output compare on channel 7, can cause bits in the output compare 7 data register to transfer to the timer port data register depending on the output compare 7 mask register. |

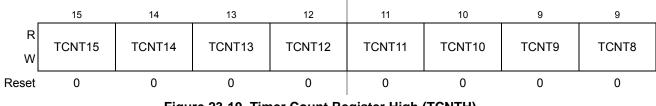

### 23.3.2.5 Timer Count Register (TCNT)

Module Base + 0x0004

Figure 23-10. Timer Count Register High (TCNTH)

MC9S12G Family Reference Manual Rev.1.27

### 24.4.6.11 Verify Backdoor Access Key Command

The Verify Backdoor Access Key command will only execute if it is enabled by the KEYEN bits in the FSEC register (see Table 24-10). The Verify Backdoor Access Key command releases security if user-supplied keys match those stored in the Flash security bytes of the Flash configuration field (see Table 24-4). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters  |  |  |

|-------------|-------------------|--|--|

| 000         | 0x0C Not required |  |  |

| 001         | Key 0             |  |  |

| 010         | Key 1             |  |  |

| 011         | Key 2             |  |  |

| 100         | Key 3             |  |  |

Table 24-50. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

| Register | Error Bit | Error Condition                                                                          |

|----------|-----------|------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 100 at command launch                                              |

|          |           | Set if an incorrect backdoor key is supplied                                             |

|          |           | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 24.3.2.2) |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                              |

|          | FPVIOL    | None                                                                                     |

|          | MGSTAT1   | None                                                                                     |

|          | MGSTAT0   | None                                                                                     |

### 24.4.6.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

16 KByte Flash Module (S12FTMRG16K1V1)

### 24.4.8 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 24.4.7, "Interrupts").

### 24.4.9 Stop Mode

If a Flash command is active (CCIF = 0) when the MCU requests stop mode, the current Flash operation will be completed before the MCU is allowed to enter stop mode.

# 24.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 24-11). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x3\_FF0F. The security state out of reset can be permanently changed by programming the security byte assuming that the MCU is starting from a mode where the necessary P-Flash erase and program commands are available and that the upper region of the P-Flash is unprotected. If the Flash security byte is successfully programmed, its new value will take affect after the next MCU reset.

The following subsections describe these security-related subjects:

- Unsecuring the MCU using Backdoor Key Access

- Unsecuring the MCU in Special Single Chip Mode using BDM

- Mode and Security Effects on Flash Command Availability

# 24.5.1 Unsecuring the MCU using Backdoor Key Access

The MCU may be unsecured by using the backdoor key access feature which requires knowledge of the contents of the backdoor keys (four 16-bit words programmed at addresses 0x3\_FF00-0x3\_FF07). If the KEYEN[1:0] bits are in the enabled state (see Section 24.3.2.2), the Verify Backdoor Access Key command (see Section 24.4.6.11) allows the user to present four prospective keys for comparison to the keys stored in the Flash memory via the Memory Controller. If the keys presented in the Verify Backdoor Access Key command match the backdoor keys stored in the Flash memory, the SEC bits in the FSEC register (see Table 24-11) will be changed to unsecure the MCU. Key values of 0x0000 and 0xFFFF are not permitted as backdoor keys. While the Verify Backdoor Access Key command is active, P-Flash memory and EEPROM memory will not be available for read access and will return invalid data.

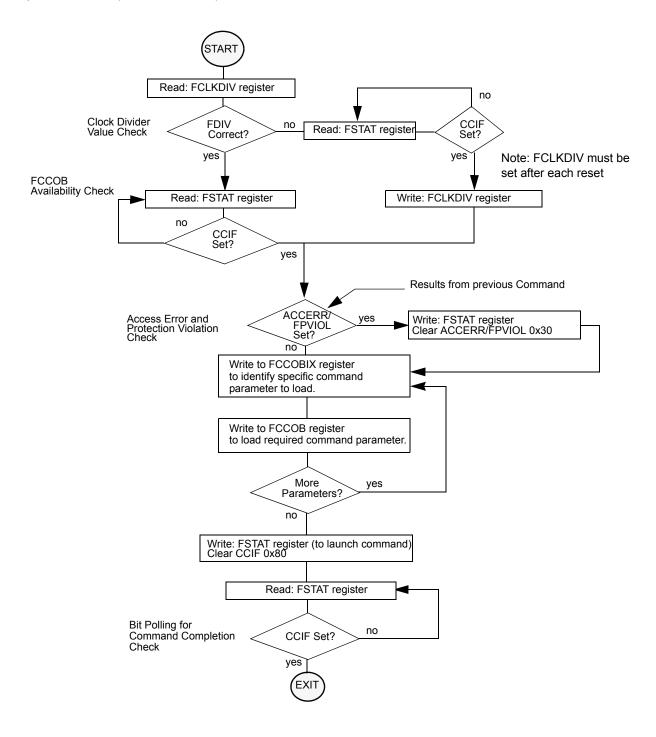

#### 32 KByte Flash Module (S12FTMRG32K1V1)

Figure 25-26. Generic Flash Command Write Sequence Flowchart

MC9S12G Family Reference Manual Rev.1.27

8. Reset the MCU

# 27.5.3 Mode and Security Effects on Flash Command Availability

The availability of Flash module commands depends on the MCU operating mode and security state as shown in Table 27-27.

# 27.6 Initialization

On each system reset the flash module executes an initialization sequence which establishes initial values for the Flash Block Configuration Parameters, the FPROT and EEPROT protection registers, and the FOPT and FSEC registers. The initialization routine reverts to built-in default values that leave the module in a fully protected and secured state if errors are encountered during execution of the reset sequence. If a double bit fault is detected during the reset sequence, both MGSTAT bits in the FSTAT register will be set.

CCIF is cleared throughout the initialization sequence. The Flash module holds off all CPU access for a portion of the initialization sequence. Flash reads are allowed once the hold is removed. Completion of the initialization sequence is marked by setting CCIF high which enables user commands.

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 28-27)                      |

|          |           | Set if an invalid global address [17:16] is supplied see Table 28-3) <sup>1</sup>   |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 28-49. Erase P-Flash Sector Command Error Handling

As defined by the memory map for FTMRG96K1.

### 28.4.6.10 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and EEPROM memory space and, if the erase is successful, will release security.

#### Table 28-50. Unsecure Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x0B             | Not required |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and EEPROM memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security state. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag is set after the Unsecure Flash operation has completed.

| Register | Error Bit | Error Condition                                                                                  |

|----------|-----------|--------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                      |

|          |           | Set if command not available in current mode (see Table 28-27)                                   |

| FSTAT    | FPVIOL    | Set if any area of the P-Flash or EEPROM memory is protected                                     |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation <sup>1</sup>                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation <sup>1</sup> |

Table 28-51. Unsecure Flash Command Error Handling

<sup>1</sup> As found in the memory map for FTMRG96K1.

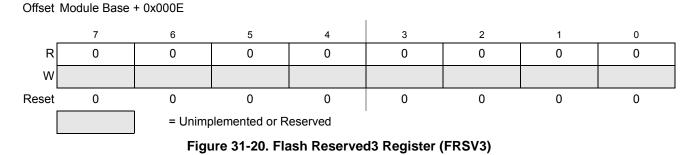

All bits in the FRSV3 register read 0 and are not writable.

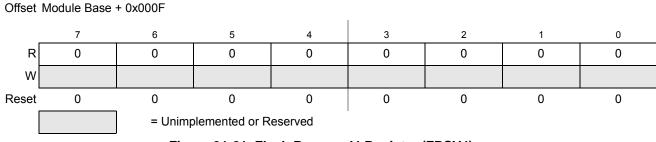

### 31.3.2.15 Flash Reserved4 Register (FRSV4)

This Flash register is reserved for factory testing.

All bits in the FRSV4 register read 0 and are not writable.

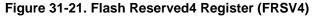

### 31.3.2.16 Flash Option Register (FOPT)

The FOPT register is the Flash option register.

<sup>1</sup> Loaded from IFR Flash configuration field, during reset sequence.

All bits in the FOPT register are readable but are not writable.

During the reset sequence, the FOPT register is loaded from the Flash nonvolatile byte in the Flash configuration field at global address  $0x_3$ \_FF0E located in P-Flash memory (see Table 31-4) as indicated by reset condition F in Figure 31-22. If a double bit fault is detected while reading the P-Flash phrase containing the Flash nonvolatile byte during the reset sequence, all bits in the FOPT register will be set.