Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 40                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1.5K x 8                                                               |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g48f0mlfr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 1 Device Overview MC9S12G-Family

# **Revision History**

| Version<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                                 |

|-------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 0.27          | 1-Apr-2011       | Typos and formatting                                                                                                                                                                                                                                                                                                                   |

| Rev 0.28          | 11-May-2011      | •                                                                                                                                                                                                                                                                                                                                      |

| Rev 0.29          | 10-Jan-2011      | Corrected Figure 1-4                                                                                                                                                                                                                                                                                                                   |

| Rev 0.30          | 10-Feb-2012      | <ul> <li>Updated Table 1-5(added mask set 1N75C)</li> <li>Typos and formatting</li> </ul>                                                                                                                                                                                                                                              |

| Rev 0.31          | 15-Mar-2012      | <ul> <li>Updated Table 1-1 (added S12GSA devices)</li> <li>Updated Figure 1-1</li> <li>Updated Table 1-5 (added S12GA devices)</li> <li>Added Section 1.8.2, "S12GNA16 and S12GNA32"</li> <li>Added Section 1.8.5, "S12GA48 and S12GA64"</li> <li>Added Section 1.8.7, "S12GA96 and S12GA128"</li> <li>Typos and formatting</li> </ul> |

| Rev 0.32          | 07-May-2012      | <ul> <li>Updated Section 1.19, "BDM Clock Source Connectivity"</li> <li>Typos and formatting</li> </ul>                                                                                                                                                                                                                                |

| Rev 0.33          | 27-Sep-2012      | Corrected Figure 1-4     Corrected Figure 1-5     Corrected Figure 1-6                                                                                                                                                                                                                                                                 |

| Rev 0.34          | 25-Jan-2013      | Added KGD option for the S12GA192 and the S12GA240 <ul> <li>Updated Table 1-1</li> <li>Corrected Table 1-2</li> <li>Corrected Table 1-6</li> </ul>                                                                                                                                                                                     |

| Rev 0.35          | 02-Jul-2014      | Corrected Table 1-2                                                                                                                                                                                                                                                                                                                    |

| Rev 0.36          | 14-Jun-2017      | Extended Table 1-5                                                                                                                                                                                                                                                                                                                     |

# 1.1 Introduction

The MC9S12G-Family is an optimized, automotive, 16-bit microcontroller product line focused on low-cost, high-performance, and low pin-count. This family is intended to bridge between high-end 8-bit microcontrollers and high-performance 16-bit microcontrollers, such as the MC9S12XS-Family. The MC9S12G-Family is targeted at generic automotive applications requiring CAN or LIN/J2602 communication. Typical examples of these applications include body controllers, occupant detection, door modules, seat controllers, RKE receivers, smart actuators, lighting modules, and smart junction boxes.

The MC9S12G-Family uses many of the same features found on the MC9S12XS- and MC9S12P-Family, including error correction code (ECC) on flash memory, a fast analog-to-digital converter (ADC) and a frequency modulated phase locked loop (IPLL) that improves the EMC performance.

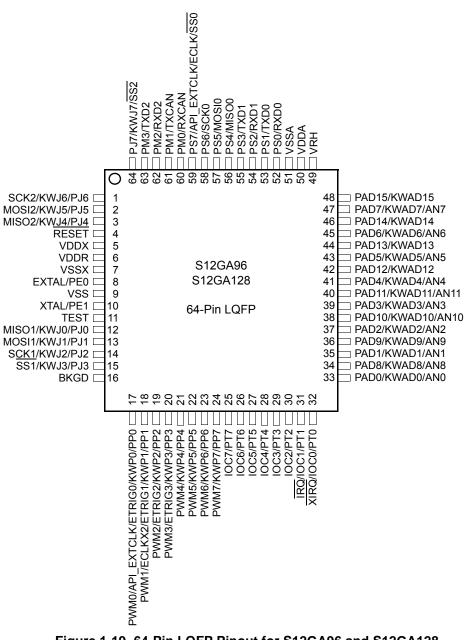

## 1.8.7.2 Pinout 64-Pin LQFP

Figure 1-19. 64-Pin LQFP Pinout for S12GA96 and S12GA128

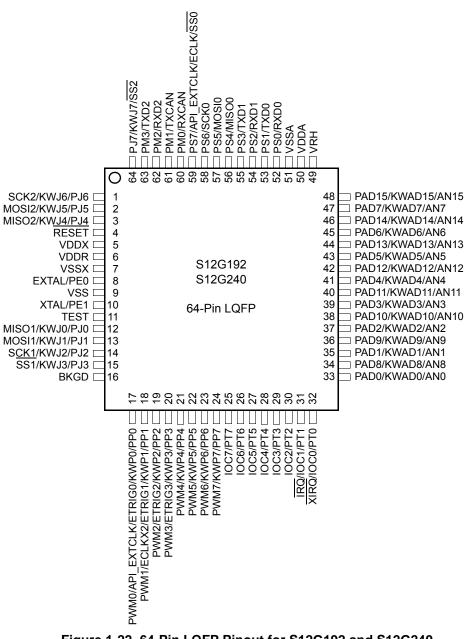

### 1.8.8.2 Pinout 64-Pin LQFP

Figure 1-22. 64-Pin LQFP Pinout for S12G192 and S12G240

# 1.17 ADC Result Reference

MCUs of the S12G-Family are able to measure the internal reference voltage  $V_{DDF}$  (see Table 1-38).  $V_{DDF}$  is a constant voltage with a narrow distribution over temperature and external voltage supply (see Table A-47).

A 12-bit left justified<sup>1</sup> ADC conversion result of  $V_{DDF}$  is provided at address  $0x0_4022/0x0_4023$  in the NVM's IFR for reference. The measurement conditions of the reference conversion are listed in Section A.16, "ADC Conversion Result Reference". By measuring the voltage  $V_{DDF}$  (see Table 1-38) and comparing the result to the reference value in the IFR, it is possible to determine the ADC's reference voltage  $V_{RH}$  in the application environment:

$V_{RH} = \frac{StoredReference}{ConvertedReference} \bullet 5V$

The exact absolute value of an analog conversion can be determined as follows:

$Result = ConvertedADInput \bullet \frac{StoredReference \bullet 5V}{ConvertedReference \bullet 2^{n}}$

With:

ConvertedADInput:Result of the analog to digital conversion of the desired pinConvertedReference:Result of channel "Internal\_0" conversionStoredReference:Value in IFR locatio 0x0\_4022/0x0\_4023n:ADC resolution (10 bit)

#### **CAUTION**

To assure high accuracy of the  $V_{DDF}$  reference conversion, the NVMs must not be programmed, erased, or read while the conversion takes place. This implies that code must be executed from RAM. The "ConvertedReference" value must be the average of eight consecutive conversions.

#### CAUTION

The ADC's reference voltage  $V_{RH}$  must remain at a constant level throughout the conversion process.

# 1.18 ADC VRH/VRL Signal Connection

On all S12G devices except for the S12GA192 and the S12GA240 the external VRH signal is directly connected to the ADC's VRH signal input. The ADC's VRL input is connected to VSSA. (see Figure 1-27).

1. The format of the stored  $\mathsf{V}_{\mathsf{DDF}}$  reference value is still subject to change.

#### Port Integration Module (S12GPIMV1)

This section describes the signals available on each pin.

Although trying to enable multiple signals on a shared pin is not a proper use case in most applications, the resulting pin function will be determined by a predefined priority scheme as defined in 2.2.2 and 2.2.3.

Only enabled signals arbitrate for the pin and the highest priority defines its data direction and output value if used as output. Signals with programmable routing options are assumed to select the appropriate target pin to participate in the arbitration.

The priority is represented for each pin with shared signals from highest to lowest in the following format:

SignalA > SignalB > GPO

Here SignalA has priority over SignalB and general-purpose output function (GPO; represented by related port data register bit). The general-purpose output is always of lowest priority if no other signal is enabled.

Peripheral input signals on shared pins are always connected monitoring the pin level independent of their use.

Write: All modes through BDM operation when not secured

#### NOTE

When BDM is made active, the CPU stores the content of its CCR register in the BDMCCR register. However, out of special single-chip reset, the BDMCCR is set to 0xD8 and not 0xD0 which is the reset value of the CCR register in this CPU mode. Out of reset in all other modes the BDMCCR register is read zero.

When entering background debug mode, the BDM CCR holding register is used to save the condition code register of the user's program. It is also used for temporary storage in the standard BDM firmware mode. The BDM CCR holding register can be written to modify the CCR value.

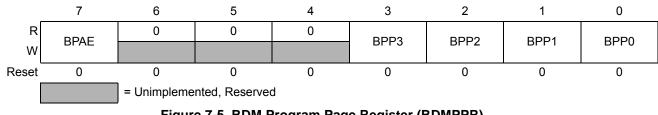

## 7.3.2.2 BDM Program Page Index Register (BDMPPR)

Register Global Address 0x3\_FF08

Figure 7-5. BDM Program Page Register (BDMPPR)

Read: All modes through BDM operation when not secured

Write: All modes through BDM operation when not secured

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>BPAE       | <ul> <li>BDM Program Page Access Enable Bit — BPAE enables program page access for BDM hardware and firmware read/write instructions The BDM hardware commands used to access the BDM registers (READ_BD and WRITE_BD) can not be used for program page accesses even if the BPAE bit is set.</li> <li>0 BDM Program Paging disabled</li> <li>1 BDM Program Paging enabled</li> </ul> |

| 3–0<br>BPP[3:0] | <b>BDM Program Page Index Bits 3–0</b> — These bits define the selected program page. For more detailed information regarding the program page window scheme, please refer to the S12S_MMC Block Guide.                                                                                                                                                                               |

# 7.3.3 Family ID Assignment

The family ID is an 8-bit value located in the BDM ROM in active BDM (at global address: 0x3\_FF0F). The read-only value is a unique family ID which is 0xC2 for devices with an HCS12S core.

# 7.4 Functional Description

The BDM receives and executes commands from a host via a single wire serial interface. There are two types of BDM commands: hardware and firmware commands.

#### Table 8-10. ABCM Encoding

| ABCM | Description                                                               |

|------|---------------------------------------------------------------------------|

| 00   | Match0 mapped to comparator A match: Match1 mapped to comparator B match. |

| 01   | Match 0 mapped to comparator A/B inside range: Match1 disabled.           |

| 10   | Match 0 mapped to comparator A/B outside range: Match1 disabled.          |

| 11   | Reserved <sup>1</sup>                                                     |

<sup>1</sup> Currently defaults to Comparator A, Comparator B disabled

## 8.3.2.5 Debug Trace Buffer Register (DBGTBH:DBGTBL)

Address: 0x0024, 0x0025

| _               | 15     | 14     | 13     | 12     | 11     | 10     | 9     | 8     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-----------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W          | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| POR             | Х      | Х      | Х      | Х      | Х      | Х      | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| Other<br>Resets |        |        |        |        |        |        |       |       |       |       |       |       |       |       |       |       |

|                 |        |        |        |        |        |        |       |       |       |       |       |       |       |       |       |       |

Figure 8-7. Debug Trace Buffer Register (DBGTB)

Read: Only when unlocked AND unsecured AND not armed AND TSOURCE set.

Write: Aligned word writes when disarmed unlock the trace buffer for reading but do not affect trace buffer contents.

| Table 8-11 | . DBGTB | Field | Descriptions |

|------------|---------|-------|--------------|

|------------|---------|-------|--------------|

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>Bit[15:0] | <b>Trace Buffer Data Bits</b> — The Trace Buffer Register is a window through which the 20-bit wide data lines of the Trace Buffer may be read 16 bits at a time. Each valid read of DBGTB increments an internal trace buffer pointer which points to the next address to be read. When the ARM bit is set the trace buffer is locked to prevent reading. The trace buffer can only be unlocked for reading by writing to DBGTB with an aligned word write when the module is disarmed. The DBGTB register can be read only as an aligned word, any byte reads or misaligned access of these registers return 0 and do not cause the trace buffer pointer to increment to the next trace buffer address. Similarly reads while the debugger is armed or with the TSOURCE bit clear, return 0 and do not affect the trace buffer pointer. The POR state is undefined. Other resets do not affect the trace buffer contents. |

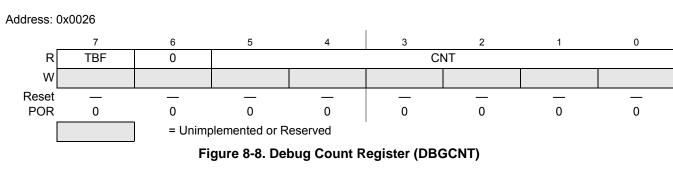

## 8.3.2.6 Debug Count Register (DBGCNT)

# 10.2.7 VDD — Internal Regulator Output Supply (Core Logic)

Node VDD is a device internal supply output of the voltage regulator that provides the power supply for the core logic.

This supply domain is monitored by the Low Voltage Reset circuit.

## 10.2.8 VDDF — Internal Regulator Output Supply (NVM Logic)

Node VDDF is a device internal supply output of the voltage regulator that provides the power supply for the NVM logic.

This supply domain is monitored by the Low Voltage Reset circuit

### 10.2.9 API EXTCLK — API external clock output pin

This pin provides the signal selected via APIES and is enabled with APIEA bit. See device specification to which pin it connects.

## 10.3 Memory Map and Registers

This section provides a detailed description of all registers accessible in the S12CPMU.

#### 10.3.1 Module Memory Map

The S12CPMU registers are shown in Figure 10-3.

| Addres<br>s | Name                  |           | Bit 7   | 6                           | 5    | 4           | 3           | 2    | 1       | Bit 0   |              |  |    |  |

|-------------|-----------------------|-----------|---------|-----------------------------|------|-------------|-------------|------|---------|---------|--------------|--|----|--|

| 0x0034      | CPMU<br>SYNR          | R<br>W    | VCOFF   | RQ[1:0]                     |      | SYNDIV[5:0] |             |      |         |         |              |  |    |  |

| 0x0035      | CPMU                  | R         | REFFR   | 0[1.0]                      | 0    | 0           | REFDIV[3:0] |      |         |         |              |  |    |  |

| 0,0000      | REFDIV                | W         | KEI I K |                             |      |             |             |      | 10[0.0] |         |              |  |    |  |

| 0x0036      | 036 CPMU<br>POSTDIV γ |           | 6       |                             | CPMU |             | 0           | 0    | 0       |         | POSTDIV[4:0] |  | 01 |  |

| 0,0000      |                       |           |         |                             |      |             |             |      | FUSIDIN |         | [4.0]        |  |    |  |

| 0x0037      | 37 CPMUFLG            | R         | RTIF    | PORF                        | LVRF | LOCKIF      | LOCK        | ILAF | OSCIF   | UPOSC   |              |  |    |  |

| 0x0007      |                       | WINDELG W |         | TON                         |      | LOOKI       |             |      | 0001    |         |              |  |    |  |

| 0x0038      | 0038 CPMUINT          | R         | RTIE    | 0                           | 0    | LOCKIE      | 0           | 0    | OSCIE   | 0       |              |  |    |  |

| 0,0000      |                       | W         | IXIIL   |                             |      | LOOKIL      |             |      | OOOIL   |         |              |  |    |  |

| 0x0039      | CPMUCLKS              | R         | PLLSEL  | PSTP                        | 0    | COP         | PRE         | PCE  | RTI     | COP     |              |  |    |  |

| 0x0039      | CI MOCENS             | W W       |         | 1.011                       |      | OSCSEL1     |             | I OL | OSCSEL  | OSCSEL0 |              |  |    |  |

| 0x003A      | CPMUPLL               | R         | 0       | 0                           | FM1  | FM0         | 0           | 0    | 0       | 0       |              |  |    |  |

| UNUUJA      | CFIVIUPLL             | W         |         |                             |      |             |             |      |         |         |              |  |    |  |

|             |                       |           |         | = Unimplemented or Reserved |      |             |             |      |         |         |              |  |    |  |

Figure 10-3. CPMU Register Summary

MC9S12G Family Reference Manual Rev.1.27

# 11.4 Functional Description

The ADC10B8C consists of an analog sub-block and a digital sub-block.

## 11.4.1 Analog Sub-Block

The analog sub-block contains all analog electronics required to perform a single conversion. Separate power supplies VDDA and VSSA allow to isolate noise of other MCU circuitry from the analog sub-block.

### 11.4.1.1 Sample and Hold Machine

The Sample and Hold Machine controls the storage and charge of the sample capacitor to the voltage level of the analog signal at the selected ADC input channel.

During the sample process the analog input connects directly to the storage node.

The input analog signals are unipolar and must be within the potential range of VSSA to VDDA.

During the hold process the analog input is disconnected from the storage node.

### 11.4.1.2 Analog Input Multiplexer

The analog input multiplexer connects one of the 8 external analog input channels to the sample and hold machine.

#### 11.4.1.3 Analog-to-Digital (A/D) Machine

The A/D Machine performs analog to digital conversions. The resolution is program selectable to be either 8 or 10 bits. The A/D machine uses a successive approximation architecture. It functions by comparing the sampled and stored analog voltage with a series of binary coded discrete voltages.

By following a binary search algorithm, the A/D machine identifies the discrete voltage that is nearest to the sampled and stored voltage.

When not converting the A/D machine is automatically powered down.

Only analog input signals within the potential range of VRL to VRH (A/D reference potentials) will result in a non-railed digital output code.

## 11.4.2 Digital Sub-Block

This subsection describes some of the digital features in more detail. See Section 11.3.2, "Register Descriptions" for all details.

### 11.4.2.1 External Trigger Input

The external trigger feature allows the user to synchronize ATD conversions to an external event rather than relying only on software to trigger the ATD module when a conversion is about to take place. The external trigger signal (out of reset ATD channel 7, configurable in ATDCTL1) is programmable to be edge

- Any CAN node is able to send out a stream of scheduled messages without releasing the CAN bus between the two messages. Such nodes arbitrate for the CAN bus immediately after sending the previous message and only release the CAN bus in case of lost arbitration.

- The internal message queue within any CAN node is organized such that the highest priority message is sent out first, if more than one message is ready to be sent.

The behavior described in the bullets above cannot be achieved with a single transmit buffer. That buffer must be reloaded immediately after the previous message is sent. This loading process lasts a finite amount of time and must be completed within the inter-frame sequence (IFS) to be able to send an uninterrupted stream of messages. Even if this is feasible for limited CAN bus speeds, it requires that the CPU reacts with short latencies to the transmit interrupt.

A double buffer scheme de-couples the reloading of the transmit buffer from the actual message sending and, therefore, reduces the reactiveness requirements of the CPU. Problems can arise if the sending of a message is finished while the CPU re-loads the second buffer. No buffer would then be ready for transmission, and the CAN bus would be released.

At least three transmit buffers are required to meet the first of the above requirements under all circumstances. The MSCAN has three transmit buffers.

The second requirement calls for some sort of internal prioritization which the MSCAN implements with the "local priority" concept described in Section 18.4.2.2, "Transmit Structures."

## 18.4.2.2 Transmit Structures

The MSCAN triple transmit buffer scheme optimizes real-time performance by allowing multiple messages to be set up in advance. The three buffers are arranged as shown in Figure 18-39.

All three buffers have a 13-byte data structure similar to the outline of the receive buffers (see Section 18.3.3, "Programmer's Model of Message Storage"). An additional Transmit Buffer Priority Register (TBPR) contains an 8-bit local priority field (PRIO) (see Section 18.3.3.4, "Transmit Buffer Priority Register (TBPR)"). The remaining two bytes are used for time stamping of a message, if required (see Section 18.3.3.5, "Time Stamp Register (TSRH–TSRL)").

To transmit a message, the CPU must identify an available transmit buffer, which is indicated by a set transmitter buffer empty (TXEx) flag (see Section 18.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)"). If a transmit buffer is available, the CPU must set a pointer to this buffer by writing to the CANTBSEL register (see Section 18.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). This makes the respective buffer accessible within the CANTXFG address space (see Section 18.3.3, "Programmer's Model of Message Storage"). The algorithmic feature associated with the CANTBSEL register simplifies the transmit buffer selection. In addition, this scheme makes the handler software simpler because only one address area is applicable for the transmit process, and the required address space is minimized.

The CPU then stores the identifier, the control bits, and the data content into one of the transmit buffers. Finally, the buffer is flagged as ready for transmission by clearing the associated TXE flag.

#### Internal Bus $\langle \rangle$ SBR12:SBR0 SCI Data Register Ζ Bus Baud Divider Clock Start Stop 11-Bit Receive Shift Register **RXPOL** Data Н 8 7 6 5 4 3 2 L 1 0 Recovery SCRXD S ₹ Loop Control From TXD Pin MSB RE or Transmitter RAF FE LOOPS Μ RWU NF RSRC WAKE Wakeup ΡE Logic ILT PE R8 Parity Checking PT Idle IRQ IDI F ILIE BRKDFE **RDRF/OR** RDRF IRQ OR RIE Break BRKDIF Detect Logic Break IRQ BRKDIE Active Edge RXEDGIF Detect Logic RX Active Edge IRQ RXEDGIE

# 20.4.6 Receiver

Figure 20-20. SCI Receiver Block Diagram

### 20.4.6.1 Receiver Character Length

The SCI receiver can accommodate either 8-bit or 9-bit data characters. The state of the M bit in SCI control register 1 (SCICR1) determines the length of data characters. When receiving 9-bit data, bit R8 in SCI data register high (SCIDRH) is the ninth bit (bit 8).

## 20.4.6.2 Character Reception

During an SCI reception, the receive shift register shifts a frame in from the RXD pin. The SCI data register is the read-only buffer between the internal data bus and the receive shift register.

After a complete frame shifts into the receive shift register, the data portion of the frame transfers to the SCI data register. The receive data register full flag, RDRF, in SCI status register 1 (SCISR1) becomes set,

#### 16 KByte Flash Module (S12FTMRG16K1V1)

#### Table 24-5. Program IFR Fields

| Global Address      | Size<br>(Bytes) | Field Description                                                       |

|---------------------|-----------------|-------------------------------------------------------------------------|

| 0x0_4000 - 0x0_4007 | 8               | Reserved                                                                |

| 0x0_4008 - 0x0_40B5 | 174             | Reserved                                                                |

| 0x0_40B6 - 0x0_40B7 | 2               | Version ID <sup>1</sup>                                                 |

| 0x0_40B8 - 0x0_40BF | 8               | Reserved                                                                |

| 0x0_40C0 - 0x0_40FF | 64              | Program Once Field<br>Refer to Section 24.4.6.6, "Program Once Command" |

<sup>1</sup> Used to track firmware patch versions, see Section 24.4.2

#### Table 24-6. Memory Controller Resource Fields (NVMRES<sup>1</sup>=1)

| Global Address      | Size<br>(Bytes) | Description                  |

|---------------------|-----------------|------------------------------|

| 0x0_4000 – 0x040FF  | 256             | P-Flash IFR (see Table 24-5) |

| 0x0_4100 - 0x0_41FF | 256             | Reserved.                    |

| 0x0_4200 - 0x0_57FF |                 | Reserved                     |

| 0x0_5800 - 0x0_59FF | 512             | Reserved                     |

| 0x0_5A00 - 0x0_5FFF | 1,536           | Reserved                     |

| 0x0_6000 - 0x0_6BFF | 3,072           | Reserved                     |

| 0x0_6C00 - 0x0_7FFF | 5,120           | Reserved                     |

<sup>1</sup> NVMRES - See Section 24.4.3 for NVMRES (NVM Resource) detail.

16 KByte Flash Module (S12FTMRG16K1V1)

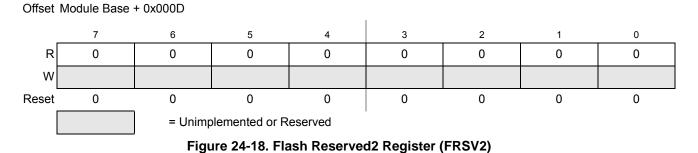

### 24.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

All bits in the FRSV2 register read 0 and are not writable.

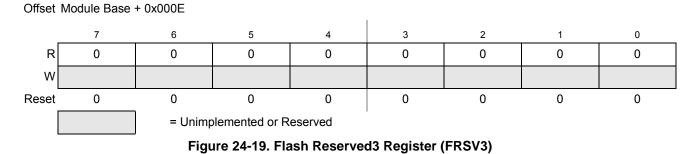

### 24.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

All bits in the FRSV3 register read 0 and are not writable.

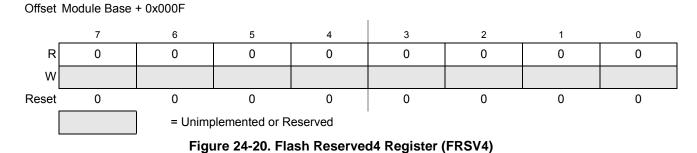

### 24.3.2.15 Flash Reserved4 Register (FRSV4)

This Flash register is reserved for factory testing.

All bits in the FRSV4 register read 0 and are not writable.

MC9S12G Family Reference Manual Rev.1.27

#### 64 KByte Flash Module (S12FTMRG64K1V1)

| Address<br>& Name |   | 7   | 6                           | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-------------------|---|-----|-----------------------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| 0x000D            | R | 0   | 0                           | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| FRSV2             | W |     |                             |     |     |     |     |     |     |  |  |  |  |

| 0x000E            | R | 0   | 0                           | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| FRSV3             | W |     |                             |     |     |     |     |     |     |  |  |  |  |

| 0x000F<br>FRSV4   | R | 0   | 0                           | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

|                   | W |     |                             |     |     |     |     |     |     |  |  |  |  |

| 0x0010            | R | NV7 | NV6                         | NV5 | NV4 | NV3 | NV2 | NV1 | NV0 |  |  |  |  |

| FOPT              | W |     |                             |     |     |     |     |     |     |  |  |  |  |

| 0x0011            | R | 0   | 0                           | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| FRSV5             | W |     |                             |     |     |     |     |     |     |  |  |  |  |

| 0x0012            | R | 0   | 0                           | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| FRSV6             | W |     |                             |     |     |     |     |     |     |  |  |  |  |

| 0x0013            | R | 0   | 0                           | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| FRSV7             | w |     |                             |     |     |     |     |     |     |  |  |  |  |

|                   | Γ |     | = Unimplemented or Reserved |     |     |     |     |     |     |  |  |  |  |

Figure 27-4. FTMRG64K1 Register Summary (continued)

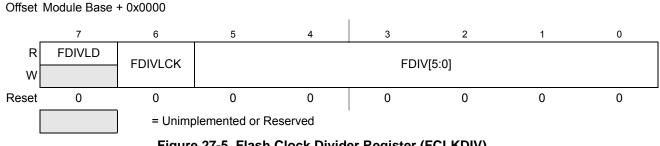

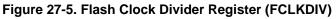

#### Flash Clock Divider Register (FCLKDIV) 27.3.2.1

The FCLKDIV register is used to control timed events in program and erase algorithms.

All bits in the FCLKDIV register are readable, bit 7 is not writable, bit 6 is write-once-hi and controls the writability of the FDIV field in normal mode. In special mode, bits 6-0 are writable any number of times but bit 7 remains unwritable.

| CCOBIX[2:0] | FCCOB Parameters |                                                   |  |  |  |  |

|-------------|------------------|---------------------------------------------------|--|--|--|--|

| 000         | 0x0D             | Flash block selection code [1:0]. See Table 28-34 |  |  |  |  |

| 001         | Març             | gin level setting.                                |  |  |  |  |

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

#### NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 28-55.

| Table 28-55. | Valid Set User Margin Level Settings |

|--------------|--------------------------------------|

|              |                                      |

| CCOB<br>(CCOBIX=001) | Level Description                |

|----------------------|----------------------------------|

| 0x0000               | Return to Normal Level           |

| 0x0001               | User Margin-1 Level <sup>1</sup> |

| 0x0002               | User Margin-0 Level <sup>2</sup> |

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

| Register | Error Bit | Error Condition                                                              |  |  |  |  |  |  |

|----------|-----------|------------------------------------------------------------------------------|--|--|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                  |  |  |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 28-27)               |  |  |  |  |  |  |

|          | ACCERR    | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 28-34) |  |  |  |  |  |  |

| FSTAT    |           | Set if an invalid margin level setting is supplied                           |  |  |  |  |  |  |

|          | FPVIOL    | None                                                                         |  |  |  |  |  |  |

|          | MGSTAT1   | None                                                                         |  |  |  |  |  |  |

|          | MGSTAT0   | None                                                                         |  |  |  |  |  |  |

Figure 29-1. FTMRG128K1 Block Diagram

# 29.2 External Signal Description

The Flash module contains no signals that connect off-chip.

MC9S12G Family Reference Manual Rev.1.27

**Electrical Characteristics**

#### A.4.3.1 ADC Accuracy Definitions

For the following definitions see also Figure A-1. Differential non-linearity (DNL) is defined as the difference between two adjacent switching steps.

$$\mathsf{DNL}(i) = \frac{\mathsf{V}_i - \mathsf{V}_{i-1}}{\mathsf{1LSB}} - 1$$

The integral non-linearity (INL) is defined as the sum of all DNLs:

$$INL(n) = \sum_{i=1}^{n} DNL(i) = \frac{V_n - V_0}{1LSB} - n$$

#### 0x0277–0x027F Port Integration Module (PIM) Map 6 of 6

| Address | Name   |        | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|--------|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| 0x027C  | PIE0AD | R<br>W | PIE0AD7 | PIE0AD6 | PIE0AD5 | PIE0AD4 | PIE0AD3 | PIE0AD2 | PIE0AD1 | PIE0AD0 |

| 0x027D  | PIE1AD | R<br>W | PIE1AD7 | PIE1AD6 | PIE1AD5 | PIE1AD4 | PIE1AD3 | PIE1AD2 | PIE1AD1 | PIE1AD0 |

| 0x027E  | PIF0AD | R<br>W | PIF0AD7 | PIF0AD6 | PIF0AD5 | PIF0AD4 | PIF0AD3 | PIF0AD2 | PIF0AD1 | PIF0AD0 |

| 0x027F  | PIF1AD | R<br>W | PIF1AD7 | PIF1AD6 | PIF1AD5 | PIF1AD4 | PIF1AD3 | PIF1AD2 | PIF1AD1 | PIF1AD0 |

#### 0x0280–0x2EF Reserved

| Address | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0280- | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x02EF  | Reserveu | W |       |       |       |       |       |       |       |       |

#### 0x02F0–0x02FF Clock and Power Management (CPMU) Map 2 of 2

| Address  | Name             |        | Bit 7             | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0 |

|----------|------------------|--------|-------------------|---------|---------|---------|---------|---------|---------|-------|

| 0x02F0   | Reserved         | R      | 0                 | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| 07021.0  | Reserved         | W      |                   |         |         |         |         |         |         |       |

| 0x02F1   | CPMULVCTL        | R      | 0                 | 0       | 0       | 0       | 0       | LVDS    | LVIE    | LVIF  |

| 0,021 1  |                  | W      |                   |         |         |         |         |         |         | 2011  |

| 0x02F2   | CPMUAPICTL       | R<br>W | APICLK            | 0       | 0       | APIES   | APIEA   | APIFE   | APIE    | APIF  |

| 0x02F3   | CPMUACLKT<br>R   | R<br>W | ACLKTR5           | ACLKTR4 | ACLKTR3 | ACLKTR2 | ACLKTR1 | ACLKTR0 | 0       | 0     |

| 0x02F4   | CPMUAPIRH        | R<br>W | APIR15            | APIR14  | APIR13  | APIR12  | APIR11  | APIR10  | APIR9   | APIR8 |

| 0x02F5   | CPMUAPIRL        | R<br>W | APIR7             | APIR6   | APIR5   | APIR4   | APIR3   | APIR2   | APIR1   | APIR0 |

| 0x02F6   | Reserved         | R      | 0                 | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| 00021 0  | Reserved         | W      |                   |         |         |         |         |         |         |       |

| 0x02F7   | Reserved         | R      | 0                 | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| UNUEL 1  | Received         | W      |                   |         |         |         |         |         |         |       |

| 0x02F8   | CPMU             | R      | R TCTRIM[3:0] 0 0 |         |         |         |         | IRCTR   | IM[9:81 |       |

| 0/(02) 0 | IRCTRIMH         | W      | W                 |         |         |         |         |         |         | [0.0] |

| 0x02F9   | CPMU<br>IRCTRIML | R<br>W | IRCTRIM[7:0]      |         |         |         |         |         |         |       |

| 0x02FA   | CPMUOSC          | R<br>W | OSCE Reserved     |         |         |         |         |         |         |       |

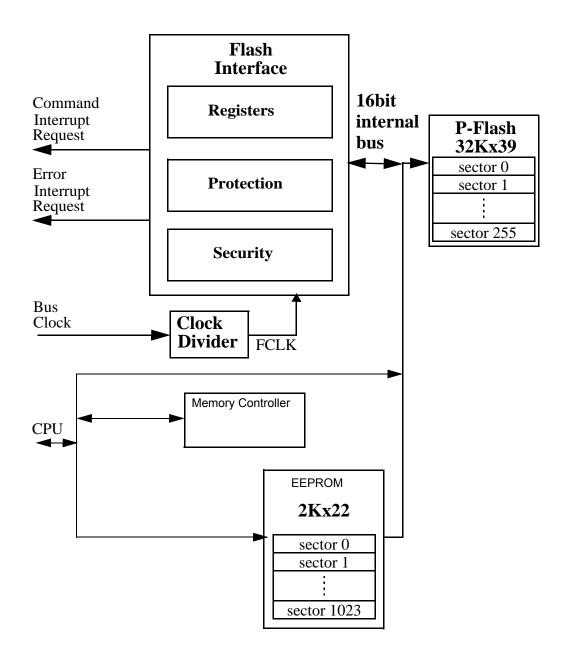

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE                        | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|---------------------------------|------------------|-------------|

| TITLE: 64LD LQFP,                                       |           | DOCUMENT NO: 98ASS23234W REV: E |                  |             |

| 10 X 10 X 1.4 P                                         | ,         | CASE NUMBER                     | R: 840F-02       | 11 AUG 2006 |

| 0.5 PITCH, CASE OU                                      | JTLINE    | STANDARD: JE                    | DEC MS-026 BCD   |             |

MC9S12G Family Reference Manual Rev.1.27

NOTES:

1. CONTROLLING DIMENSION: MILLIMETER

2. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M-1982.

<u>B</u> DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE

DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE.

5 DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

7 dimensions are to be determined at datum plane [-W-]

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE                       | PRINT VERSION NE | IT TO SCALE |

|---------------------------------------------------------|-----------|---------------------------------|------------------|-------------|

| TITLE:                                                  |           | D□CUMENT N□: 98ASH70169A REV: C |                  |             |

| 20 LD TSSOP, PITCH 0                                    | .65MM     | CASE NUMBER: 948E-02 25 MAY 200 |                  |             |

|                                                         |           | STANDARD: JE                    | DEC              |             |