# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 12V1                                                                  |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 48KB (48K × 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1.5K x 8                                                              |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g48f0mlh |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 13.2 | Signal Description                  | 459 |

|------|-------------------------------------|-----|

|      | 13.2.1 Detailed Signal Descriptions | 459 |

| 13.3 | Memory Map and Register Definition  | 459 |

|      | 13.3.1 Module Memory Map            | 459 |

|      | 13.3.2 Register Descriptions        | 462 |

| 13.4 | Functional Description              | 477 |

|      | 13.4.1 Analog Sub-Block             | 477 |

|      | 13.4.2 Digital Sub-Block            | 477 |

| 13.5 | Resets                              | 479 |

| 13.6 | Interrupts                          | 479 |

### Chapter 14 Analog-to-Digital Converter (ADC12B12CV2)

| 14.1 | Introduction                        | 482 |

|------|-------------------------------------|-----|

|      | 14.1.1 Features                     | 482 |

|      | 14.1.2 Modes of Operation           | 483 |

|      | 14.1.3 Block Diagram                | 484 |

| 14.2 | Signal Description                  | 485 |

|      | 14.2.1 Detailed Signal Descriptions | 485 |

| 14.3 | Memory Map and Register Definition  | 485 |

|      | 14.3.1 Module Memory Map            | 485 |

|      | 14.3.2 Register Descriptions        |     |

| 14.4 | Functional Description              | 504 |

|      | 14.4.1 Analog Sub-Block             |     |

|      | 14.4.2 Digital Sub-Block            |     |

| 14.5 | Resets                              | 506 |

| 14.6 | Interrupts                          | 506 |

### Chapter 15

## Analog-to-Digital Converter (ADC10B16CV2)

| Introduction                       | 508                                                                                                                                                                                                                                                                                |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.1 Features                    | 508                                                                                                                                                                                                                                                                                |

| 15.1.2 Modes of Operation          | 509                                                                                                                                                                                                                                                                                |

| 15.1.3 Block Diagram               | 510                                                                                                                                                                                                                                                                                |

| Signal Description                 | 511                                                                                                                                                                                                                                                                                |

|                                    |                                                                                                                                                                                                                                                                                    |

| Memory Map and Register Definition | 511                                                                                                                                                                                                                                                                                |

| 15.3.1 Module Memory Map           | 511                                                                                                                                                                                                                                                                                |

| 15.3.2 Register Descriptions       | 514                                                                                                                                                                                                                                                                                |

| Functional Description             | 529                                                                                                                                                                                                                                                                                |

| 15.4.1 Analog Sub-Block            | 529                                                                                                                                                                                                                                                                                |

| 15.4.2 Digital Sub-Block           | 529                                                                                                                                                                                                                                                                                |

| Resets                             | 531                                                                                                                                                                                                                                                                                |

| Interrupts                         | 531                                                                                                                                                                                                                                                                                |

|                                    | 15.1.1 Features15.1.2 Modes of Operation15.1.3 Block DiagramSignal Description15.2.1 Detailed Signal DescriptionsMemory Map and Register Definition15.3.1 Module Memory Map15.3.2 Register DescriptionsFunctional Description15.4.1 Analog Sub-Block15.4.2 Digital Sub-BlockResets |

Device Overview MC9S12G-Family

|             | Function<br><lowestpriorityhighest></lowestpriorityhighest> |                |              |             |             |                  |               | Internal Pull<br>Resistor |  |

|-------------|-------------------------------------------------------------|----------------|--------------|-------------|-------------|------------------|---------------|---------------------------|--|

| Package Pin | Pin                                                         | 2nd<br>Func.   | 3rd<br>Func. | 4th<br>Func | 5th<br>Func | Supply           | CTRL          | Reset<br>State            |  |

| 28          | PAD9                                                        | KWAD9          | AN9          | ACMPO       |             | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled                  |  |

| 29          | PAD2                                                        | KWAD2          | AN2          | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled                  |  |

| 30          | PAD10                                                       | KWAD10         | AN10         | ACMPP       |             | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled                  |  |

| 31          | PAD3                                                        | KWAD3          | AN3          | _           |             | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled                  |  |

| 32          | PAD11                                                       | KWAD11         | AN11         | ACMPM       |             | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled                  |  |

| 33          | PAD4                                                        | KWAD4          | AN4          | _           |             | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled                  |  |

| 34          | PAD5                                                        | KWAD5          | AN5          | _           |             | V <sub>DDA</sub> | PER1AD/PPS0AD | Disabled                  |  |

| 35          | PAD6                                                        | KWAD6          | AN6          | _           |             | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled                  |  |

| 36          | PAD7                                                        | KWAD7          | AN7          | _           |             | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled                  |  |

| 37          | VDDA                                                        | VRH            | _            | _           | _           | _                | _             |                           |  |

| 38          | VSSA                                                        | _              |              | _           |             |                  |               |                           |  |

| 39          | PS0                                                         | RXD0           |              | _           |             | V <sub>DDX</sub> | PERS/PPSS     | Up                        |  |

| 40          | PS1                                                         | TXD0           |              | _           |             | V <sub>DDX</sub> | PERS/PPSS     | Up                        |  |

| 41          | PS2                                                         | RXD1           | _            | _           |             | V <sub>DDX</sub> | PERS/PPSS     | Up                        |  |

| 42          | PS3                                                         | TXD1           | _            | _           |             | V <sub>DDX</sub> | PERS/PPSS     | Up                        |  |

| 43          | PS4                                                         | MISO0          | _            | —           | _           | V <sub>DDX</sub> | PERS/PPSS     | Up                        |  |

| 44          | PS5                                                         | MOSI0          | _            | _           |             | V <sub>DDX</sub> | PERS/PPSS     | Up                        |  |

| 45          | PS6                                                         | SCK0           | _            | _           | —           | V <sub>DDX</sub> | PERS/PPSS     | Up                        |  |

| 46          | PS7                                                         | API_EXTC<br>LK | ECLK         | SS0         | _           | V <sub>DDX</sub> | PERS/PPSS     | Up                        |  |

| 47          | PM0                                                         | —              | _            | —           | —           | V <sub>DDX</sub> | PERM/PPSM     | Disabled                  |  |

| 48          | PM1                                                         | —              |              | _           | _           | V <sub>DDX</sub> | PERM/PPSM     | Disabled                  |  |

| Table 1-13. 48-Pin LQFP Pinout for | S12GN48 |

|------------------------------------|---------|

|------------------------------------|---------|

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

#### Port Integration Module (S12GPIMV1)

| Global Address<br>Register Name |        | Bit 7    | 6          | 5            | 4      | 3     | 2      | 1      | Bit 0  |

|---------------------------------|--------|----------|------------|--------------|--------|-------|--------|--------|--------|

| 0x0255<br>PPSM                  | R<br>W | 0        | 0          | 0            | 0      | PPSM3 | PPSM2  | PPSM1  | PPSM0  |

| 0x0256<br>WOMM                  | R<br>W | 0        | 0          | 0            | 0      | WOMM3 | WOMM2  | WOMM1  | WOMM0  |

| 0x0257<br>PKGCR                 | R<br>W | APICLKS7 | 0          | 0            | 0      | 0     | PKGCR2 | PKGCR1 | PKGCR0 |

| 0x0258<br>PTP                   | R<br>W | PTP7     | PTP6       | PTP5         | PTP4   | PTP3  | PTP2   | PTP1   | PTP0   |

| 0x0259<br>PTIP                  | R<br>W | PTIP7    | PTIP6      | PTIP5        | PTIP4  | PTIP3 | PTIP2  | PTIP1  | PTIP0  |

| 0x025A<br>DDRP                  | R<br>W | DDRP7    | DDRP6      | DDRP5        | DDRP4  | DDRP3 | DDRP2  | DDRP1  | DDRP0  |

| 0x025B<br>Reserved              | R<br>W | 0        | 0          | 0            | 0      | 0     | 0      | 0      | 0      |

| 0x025C<br>PERP                  | R<br>W | PERP7    | PERP6      | PERP5        | PERP4  | PERP3 | PERP2  | PERP1  | PERP0  |

| 0x025D<br>PPSP                  | R<br>W | PPSP7    | PPSP6      | PPSP5        | PPSP4  | PPSP3 | PPSP2  | PPSP1  | PPSP0  |

| 0x025E<br>PIEP                  | R<br>W | PIEP7    | PIEP6      | PIEP5        | PIEP4  | PIEP3 | PIEP2  | PIEP1  | PIEP0  |

| 0x025F<br>PIFP                  | R<br>W | PIFP7    | PIFP6      | PIFP5        | PIFP4  | PIFP3 | PIFP2  | PIFP1  | PIFP0  |

| 0x0260–0x0267<br>Reserved       | R<br>W |          | 0          | 0            | 0      | 0     | 0      | 0      | 0      |

| 0x0268<br>PTJ                   | R<br>W | PTJ7     | PTJ6       | PTJ5         | PTJ4   | PTJ3  | PTJ2   | PTJ1   | PTJ0   |

| 0x0269<br>PTIJ                  | R<br>W | PTIJ7    | PTIJ6      | PTIJ5        | PTIJ4  | PTIJ3 | PTIJ2  | PTIJ1  | PTIJ0  |

| 0x026A<br>DDRJ                  | R<br>W | DDRJ7    | DDRJ6      | DDRJ5        | DDRJ4  | DDRJ3 | DDRJ2  | DDRJ1  | DDRJ0  |

|                                 | [      |          | = Unimplem | nented or Re | served |       |        |        |        |

### Table 2-19. Block Register Map (G1) (continued)

MC9S12G Family Reference Manual Rev.1.27

### NOTE

This information is being provided so that the MCU integrator will be aware that such a conflict could occur.

The hardware handshake protocol is enabled by the ACK\_ENABLE and disabled by the ACK\_DISABLE BDM commands. This provides backwards compatibility with the existing POD devices which are not able to execute the hardware handshake protocol. It also allows for new POD devices, that support the hardware handshake protocol, to freely communicate with the target device. If desired, without the need for waiting for the ACK pulse.

The commands are described as follows:

- ACK\_ENABLE enables the hardware handshake protocol. The target will issue the ACK pulse when a CPU command is executed by the CPU. The ACK\_ENABLE command itself also has the ACK pulse as a response.

- ACK\_DISABLE disables the ACK pulse protocol. In this case, the host needs to use the worst case delay time at the appropriate places in the protocol.

The default state of the BDM after reset is hardware handshake protocol disabled.

All the read commands will ACK (if enabled) when the data bus cycle has completed and the data is then ready for reading out by the BKGD serial pin. All the write commands will ACK (if enabled) after the data has been received by the BDM through the BKGD serial pin and when the data bus cycle is complete. See Section 7.4.3, "BDM Hardware Commands" and Section 7.4.4, "Standard BDM Firmware Commands" for more information on the BDM commands.

The ACK\_ENABLE sends an ACK pulse when the command has been completed. This feature could be used by the host to evaluate if the target supports the hardware handshake protocol. If an ACK pulse is issued in response to this command, the host knows that the target supports the hardware handshake protocol. If the target does not support the hardware handshake protocol the ACK pulse is not issued. In this case, the ACK\_ENABLE command is ignored by the target since it is not recognized as a valid command.

The BACKGROUND command will issue an ACK pulse when the CPU changes from normal to background mode. The ACK pulse related to this command could be aborted using the SYNC command.

The GO command will issue an ACK pulse when the CPU exits from background mode. The ACK pulse related to this command could be aborted using the SYNC command.

The GO\_UNTIL command is equivalent to a GO command with exception that the ACK pulse, in this case, is issued when the CPU enters into background mode. This command is an alternative to the GO command and should be used when the host wants to trace if a breakpoint match occurs and causes the CPU to enter active background mode. Note that the ACK is issued whenever the CPU enters BDM, which could be caused by a breakpoint match or by a BGND instruction being executed. The ACK pulse related to this command could be aborted using the SYNC command.

The TRACE1 command has the related ACK pulse issued when the CPU enters background active mode after one instruction of the application program is executed. The ACK pulse related to this command could be aborted using the SYNC command.

S12 Clock, Reset and Power Management Unit (S12CPMU)

### 10.6 Interrupts

The interrupt/reset vectors requested by the S12CPMU are listed in Table 10-29. Refer to MCU specification for related vector addresses and priorities.

| Interrupt Source                   | CCR<br>Mask | Local Enable      |

|------------------------------------|-------------|-------------------|

| RTI time-out interrupt I bit       |             | CPMUINT (RTIE)    |

| PLL lock interrupt                 | I bit       | CPMUINT (LOCKIE)  |

| Oscillator status<br>interrupt     | l bit       | CPMUINT (OSCIE)   |

| Low voltage interrupt              | I bit       | CPMULVCTL (LVIE)  |

| Autonomous<br>Periodical Interrupt | l bit       | CPMUAPICTL (APIE) |

Table 10-29. S12CPMU Interrupt Vectors

### **10.6.1** Description of Interrupt Operation

### 10.6.1.1 Real Time Interrupt (RTI)

The clock source for the RTI is either IRCCLK or OSCCLK depending on the setting of the RTIOSCSEL bit. In Stop Mode with PSTP=1 (Pseudo Stop Mode), RTIOSCSEL=1 and PRE=1 the RTI continues to run, else the RTI counter halts in Stop Mode.

The RTI can be used to generate hardware interrupts at a fixed periodic rate. If enabled (by setting RTIE=1), this interrupt will occur at the rate selected by the CPMURTI register. At the end of the RTI time-out period the RTIF flag is set to one and a new RTI time-out period starts immediately.

A write to the CPMURTI register restarts the RTI time-out period.

### 10.6.1.2 PLL Lock Interrupt

The S12CPMU generates a PLL Lock interrupt when the lock condition (LOCK status bit) of the PLL changes, either from a locked state to an unlocked state or vice versa. Lock interrupts are locally disabled by setting the LOCKIE bit to zero. The PLL Lock interrupt flag (LOCKIF) is set to 1 when the lock condition has changed, and is cleared to 0 by writing a 1 to the LOCKIF bit.

### 10.6.1.3 Oscillator Status Interrupt

When the OSCE bit is 0, then UPOSC stays 0. When OSCE = 1 the UPOSC bit is set after the LOCK bit is set.

Upon detection of a status change (UPOSC) the OSCIF flag is set. Going into Full Stop Mode or disabling the oscillator can also cause a status change of UPOSC.

| Table 15-16. ATDSTAT0 Field Descriptions (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Field                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 3–0<br>CC[3:0]                                       | <b>Conversion Counter</b> — These 4 read-only bits are the binary value of the conversion counter. The conversion counter points to the result register that will receive the result of the current conversion. E.g. CC3=0, CC2=1, CC1=1, CC0=0 indicates that the result of the current conversion will be in ATD Result Register 6. If in non-FIFO mode (FIFO=0) the conversion counter is initialized to zero at the beginning and end of the conversion sequence. If in FIFO mode (FIFO=1) the register counter is not initialized. The conversion counter wraps around when its maximum value is reached. |  |  |  |

#### Aborting a conversion or starting a new conversion clears the conversion counter even if FIFO=1.

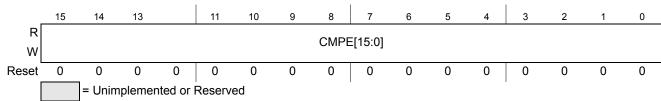

#### 15.3.2.8 **ATD Compare Enable Register (ATDCMPE)**

Writes to this register will abort current conversion sequence.

Read: Anytime

Write: Anytime

Module Base + 0x0008

#### Figure 15-10. ATD Compare Enable Register (ATDCMPE)

#### Table 15-17. ATDCMPE Field Descriptions

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>CMPE[15:0] | <b>Compare Enable for Conversion Number</b> <i>n</i> ( <i>n</i> = 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) of a Sequence ( <i>n conversion number, NOT channel number!</i> ) — These bits enable automatic compare of conversion results individually for conversions of a sequence. The sense of each comparison is determined by the CMPHT[ <i>n</i> ] bit in the ATDCMPHT register. |

|                    | <ul> <li>For each conversion number with CMPE[n]=1 do the following:</li> <li>1) Write compare value to ATDDRn result register</li> <li>2) Write compare operator with CMPHT[n] in ATDCPMHT register</li> </ul>                                                                                                                                                                                     |

|                    | <ul> <li>CCF[<i>n</i>] in ATDSTAT2 register will flag individual success of any comparison.</li> <li>0 No automatic compare</li> <li>1 Automatic compare of results for conversion <i>n</i> of a sequence is enabled.</li> </ul>                                                                                                                                                                    |

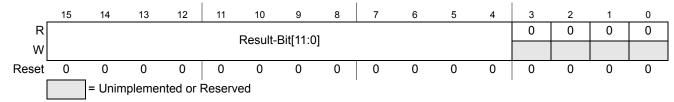

### 16.3.2.12 ATD Conversion Result Registers (ATDDR*n*)

The A/D conversion results are stored in 16 result registers. Results are always in unsigned data representation. Left and right justification is selected using the DJM control bit in ATDCTL3.

If automatic compare of conversions results is enabled (CMPE[n]=1 in ATDCMPE), these registers must be written with the compare values in left or right justified format depending on the actual value of the DJM bit. In this case, as the ATDDRn register is used to hold the compare value, the result will not be stored there at the end of the conversion but is lost.

### Attention, n is the conversion number, NOT the channel number!

Read: Anytime

Write: Anytime

#### NOTE

For conversions not using automatic compare, results are stored in the result registers after each conversion. In this case avoid writing to ATDDRn except for initial values, because an A/D result might be overwritten.

### 16.3.2.12.1 Left Justified Result Data (DJM=0)

```

Module Base +

```

```

0x0010 = ATDDR0, 0x0012 = ATDDR1, 0x0014 = ATDDR2, 0x0016 = ATDDR3

0x0018 = ATDDR4, 0x001A = ATDDR5, 0x001C = ATDDR6, 0x001E = ATDDR7

0x0020 = ATDDR8, 0x0022 = ATDDR9, 0x0024 = ATDDR10, 0x0026 = ATDDR11

0x0028 = ATDDR12, 0x002A = ATDDR13, 0x002C = ATDDR14, 0x002E = ATDDR15

```

#### Figure 16-14. Left justified ATD conversion result register (ATDDRn)

Table 16-21 shows how depending on the A/D resolution the conversion result is transferred to the ATD result registers for left justified data. Compare is always done using all 12 bits of both the conversion result and the compare value in ATDDRn.

| A/D<br>resolution | DJM | conversion result mapping to ATDDR <i>n</i>                   |

|-------------------|-----|---------------------------------------------------------------|

| 8-bit data        | 0   | Result-Bit[11:4] = conversion result,<br>Result-Bit[3:0]=0000 |

| 10-bit data       | 0   | Result-Bit[11:2] = conversion result,<br>Result-Bit[1:0]=00   |

| 12-bit data       | 0   | Result-Bit[11:0] = result                                     |

#### Table 16-21. Conversion result mapping to ATDDRn

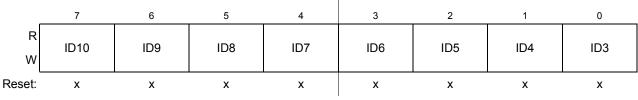

### 18.3.3.1.2 IDR0–IDR3 for Standard Identifier Mapping

Module Base + 0x00X0

Figure 18-30. Identifier Register 0 — Standard Mapping

| Table 18-31. IDR0 Register Field | Descriptions — Standard |

|----------------------------------|-------------------------|

|----------------------------------|-------------------------|

| Field           | Description                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>ID[10:3] | <b>Standard Format Identifier</b> — The identifiers consist of 11 bits (ID[10:0]) for the standard format. ID10 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. See also ID bits in Table 18-32. |

#### Module Base + 0x00X1

| _      | 7   | 6   | 5              | 4   | 3        | 2 | 1 | 0 |

|--------|-----|-----|----------------|-----|----------|---|---|---|

| R<br>W | ID2 | ID1 | ID0            | RTR | IDE (=0) |   |   |   |

| Reset: | х   | х   | х              | х   | х        | х | х | х |

|        |     |     | always read 'y | ,   |          |   |   |   |

T.

= Unused; always read 'x'

#### Figure 18-31. Identifier Register 1 — Standard Mapping

#### Table 18-32. IDR1 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5<br>ID[2:0] | <b>Standard Format Identifier</b> — The identifiers consist of 11 bits (ID[10:0]) for the standard format. ID10 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. See also ID bits in Table 18-31.                                                                                                        |

| 4<br>RTR       | <ul> <li>Remote Transmission Request — This flag reflects the status of the Remote Transmission Request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.</li> <li>0 Data frame</li> <li>1 Remote frame</li> </ul>                    |

| 3<br>IDE       | <ul> <li>ID Extended — This flag indicates whether the extended or standard identifier format is applied in this buffer. In the case of a receive buffer, the flag is set as received and indicates to the CPU how to process the buffer identifier registers. In the case of a transmit buffer, the flag indicates to the MSCAN what type of identifier to send.</li> <li>0 Standard format (11 bit)</li> <li>1 Extended format (29 bit)</li> </ul> |

<sup>3</sup> SPIDRH can be written repeatedly without any effect on SPTEF. SPTEF Flag is cleared only by writing to SPIDRL after reading SPISR with SPTEF == 1.

### 21.3.2.5 SPI Data Register (SPIDR = SPIDRH:SPIDRL)

Module Base +0x0004

|       | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|-------|-----|-----|-----|-----|-----|-----|----|----|

| R     | R15 | R14 | R13 | R12 | R11 | R10 | R9 | R8 |

| W     | T15 | T14 | T13 | T12 | T11 | T10 | Т9 | Т8 |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  |

Figure 21-7. SPI Data Register High (SPIDRH)

Module Base +0x0005

|       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|----|----|

| R     | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| W     | T7 | T6 | T5 | T4 | Т3 | T2 | T1 | Т0 |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Figure 21-8. SPI Data Register Low (SPIDRL)

Read: Anytime; read data only valid when SPIF is set

Write: Anytime

The SPI data register is both the input and output register for SPI data. A write to this register allows data to be queued and transmitted. For an SPI configured as a master, queued data is transmitted immediately after the previous transmission has completed. The SPI transmitter empty flag SPTEF in the SPISR register indicates when the SPI data register is ready to accept new data.

Received data in the SPIDR is valid when SPIF is set.

If SPIF is cleared and data has been received, the received data is transferred from the receive shift register to the SPIDR and SPIF is set.

If SPIF is set and not serviced, and a second data value has been received, the second received data is kept as valid data in the receive shift register until the start of another transmission. The data in the SPIDR does not change.

If SPIF is set and valid data is in the receive shift register, and SPIF is serviced before the start of a third transmission, the data in the receive shift register is transferred into the SPIDR and SPIF remains set (see Figure 21-9).

If SPIF is set and valid data is in the receive shift register, and SPIF is serviced after the start of a third transmission, the data in the receive shift register has become invalid and is not transferred into the SPIDR (see Figure 21-10).

### 24.4.6.11 Verify Backdoor Access Key Command

The Verify Backdoor Access Key command will only execute if it is enabled by the KEYEN bits in the FSEC register (see Table 24-10). The Verify Backdoor Access Key command releases security if user-supplied keys match those stored in the Flash security bytes of the Flash configuration field (see Table 24-4). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters |                   |  |  |  |  |  |

|-------------|------------------|-------------------|--|--|--|--|--|

| 000         | 0x0C             | 0x0C Not required |  |  |  |  |  |

| 001         | Ke               | y 0               |  |  |  |  |  |

| 010         | Key 1            |                   |  |  |  |  |  |

| 011         | Key 2            |                   |  |  |  |  |  |

| 100         | Ke               | Key 3             |  |  |  |  |  |

Table 24-50. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

| Register | Error Bit | Error Condition                                                                          |

|----------|-----------|------------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 100 at command launch                                              |

|          |           | Set if an incorrect backdoor key is supplied                                             |

|          | ACCERR    | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 24.3.2.2) |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                              |

|          | FPVIOL    | None                                                                                     |

|          | MGSTAT1   | None                                                                                     |

|          | MGSTAT0   | None                                                                                     |

### 24.4.6.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

| Address<br>& Name |   | 7   | 6        | 5             | 4        | 3   | 2   | 1   | 0   |

|-------------------|---|-----|----------|---------------|----------|-----|-----|-----|-----|

| 0x000D            | R | 0   | 0        | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV2             | W |     |          |               |          |     |     |     |     |

| 0x000E            | R | 0   | 0        | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV3             | W |     |          |               |          |     |     |     |     |

| 0x000F            | R | 0   | 0        | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV4             | W |     |          |               |          |     |     |     |     |

| 0x0010            | R | NV7 | NV6      | NV5           | NV4      | NV3 | NV2 | NV1 | NV0 |

| FOPT              | W |     |          |               |          |     |     |     |     |

| 0x0011            | R | 0   | 0        | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV5             | W |     |          |               |          |     |     |     |     |

| 0x0012            | R | 0   | 0        | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV6             | W |     |          |               |          |     |     |     |     |

| 0x0013            | R | 0   | 0        | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV7             | W |     |          |               |          |     |     |     |     |

|                   |   |     | = Unimpl | lemented or F | Reserved |     |     |     |     |

Figure 26-4. FTMRG48K1 Register Summary (continued)

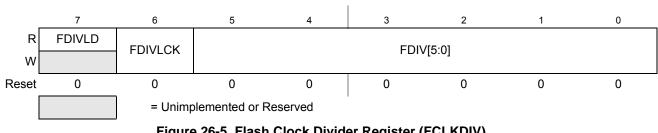

#### Flash Clock Divider Register (FCLKDIV) 26.3.2.1

The FCLKDIV register is used to control timed events in program and erase algorithms.

All bits in the FCLKDIV register are readable, bit 7 is not writable, bit 6 is write-once-hi and controls the writability of the FDIV field in normal mode. In special mode, bits 6-0 are writable any number of times but bit 7 remains unwritable.

Offset Module Base + 0x0000

### 26.4.6.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of the P-Flash or EEPROM block.

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the Table 26-57. Set Field Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters      |                                                        |  |  |  |  |  |

|-------------|-----------------------|--------------------------------------------------------|--|--|--|--|--|

| 000         | 0x0E                  | 0x0E Flash block selection code [1:0]. See Table 26-34 |  |  |  |  |  |

| 001         | Margin level setting. |                                                        |  |  |  |  |  |

field margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM field margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash field margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply field margin levels to the P-Flash block only.

Valid margin level settings for the Set Field Margin Level command are defined in Table 26-58.

| CCOB<br>(CCOBIX=001) | Level Description                 |

|----------------------|-----------------------------------|

| 0x0000               | Return to Normal Level            |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |

Table 26-58. Valid Set Field Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

| Register | Error Bit | Error Condition                                                              |  |  |  |  |  |

|----------|-----------|------------------------------------------------------------------------------|--|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                  |  |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 26-27)               |  |  |  |  |  |

|          | AUCERR    | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 26-34) |  |  |  |  |  |

| FSTAT    |           | Set if an invalid margin level setting is supplied                           |  |  |  |  |  |

|          | FPVIOL    | None                                                                         |  |  |  |  |  |

|          | MGSTAT1   | None                                                                         |  |  |  |  |  |

|          | MGSTAT0   | None                                                                         |  |  |  |  |  |

#### Table 26-59. Set Field Margin Level Command Error Handling

### CAUTION

Field margin levels must only be used during verify of the initial factory programming.

### NOTE

Field margin levels can be used to check that Flash memory contents have adequate margin for data retention at the normal level setting. If unexpected results are encountered when checking Flash memory contents at field margin levels, the Flash memory contents should be erased and reprogrammed.

### 26.4.6.14 Erase Verify EEPROM Section Command

The Erase Verify EEPROM Section command will verify that a section of code in the EEPROM is erased. The Erase Verify EEPROM Section command defines the starting point of the data to be verified and the number of words.

| CCOBIX[2:0] | FCCOB Parameters                                       |                                                           |

|-------------|--------------------------------------------------------|-----------------------------------------------------------|

| 000         | 0x10                                                   | Global address [17:16] to<br>identify the EEPROM<br>block |

| 001         | Global address [15:0] of the first word to be verified |                                                           |

| 010         | Number of words to be verified                         |                                                           |

Table 26-60. Erase Verify EEPROM Section Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Verify EEPROM Section command, the Memory Controller will verify the selected section of EEPROM memory is erased. The CCIF flag will set after the Erase Verify EEPROM Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

#### 64 KByte Flash Module (S12FTMRG64K1V1)

The FPROT register, described in Section 27.3.2.9, can be set to protect regions in the Flash memory from accidental program or erase. Three separate memory regions, one growing upward from global address 0x3\_8000 in the Flash memory (called the lower region), one growing downward from global address 0x3\_FFFF in the Flash memory (called the higher region), and the remaining addresses in the Flash memory, can be activated for protection. The Flash memory addresses covered by these protectable regions are shown in the P-Flash memory map. The higher address region is mainly targeted to hold the boot loader code since it covers the vector space. Default protection settings as well as security information that allows the MCU to restrict access to the Flash module are stored in the Flash configuration field as described in Table 27-4.

| Global Address                 | Size<br>(Bytes) | Description                                                                                                                                                        |

|--------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x3_FF00-0x3_FF07              | 8               | Backdoor Comparison Key<br>Refer to Section 27.4.6.11, "Verify Backdoor Access Key Command," and<br>Section 27.5.1, "Unsecuring the MCU using Backdoor Key Access" |

| 0x3_FF08-0x3_FF0B <sup>1</sup> | 4               | Reserved                                                                                                                                                           |

| 0x3_FF0C <sup>1</sup>          | 1               | P-Flash Protection byte.<br>Refer to Section 27.3.2.9, "P-Flash Protection Register (FPROT)"                                                                       |

| 0x3_FF0D <sup>1</sup>          | 1               | EEPROM Protection byte.<br>Refer to Section 27.3.2.10, "EEPROM Protection Register (EEPROT)"                                                                       |

| 0x3_FF0E <sup>1</sup>          | 1               | Flash Nonvolatile byte<br>Refer to Section 27.3.2.16, "Flash Option Register (FOPT)"                                                                               |

| 0x3_FF0F <sup>1</sup>          | 1               | Flash Security byte<br>Refer to Section 27.3.2.2, "Flash Security Register (FSEC)"                                                                                 |

#### Table 27-4. Flash Configuration Field

<sup>1</sup> 0x3FF08-0x3\_FF0F form a Flash phrase and must be programmed in a single command write sequence. Each byte in the 0x3\_FF08 - 0x3\_FF0B reserved field should be programmed to 0xFF.

| Register | Error Bit | Error Condition                                                                     |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|

|          |           | Set if CCOBIX[2:0] != 101 at command launch                                         |  |

|          | ACCERR    | Set if command not available in current mode (see Table 27-27)                      |  |

|          | ACCERK    | Set if an invalid global address [17:0] is supplied see Table 27-3)                 |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |

|          | FPVIOL    | Set if the global address [17:0] points to a protected area                         |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |

Table 27-41. Program P-Flash Command Error Handling

### 27.4.6.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash. The Program Once reserved field can be read using the Read Once command as described in Section 27.4.6.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |              |

|-------------|---------------------------------------------|--------------|

| 000         | 0x07                                        | Not Required |

| 001         | Program Once phrase index (0x0000 - 0x0007) |              |

| 010         | Program Once word 0 value                   |              |

| 011         | Program Once word 1 value                   |              |

| 100         | Program Once word 2 value                   |              |

| 101         | Program Once word 3 value                   |              |

Table 27-42. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash will return invalid data.

All bits in the FCLKDIV register are readable, bit 7 is not writable, bit 6 is write-once-hi and controls the writability of the FDIV field in normal mode. In special mode, bits 6-0 are writable any number of times but bit 7 remains unwritable.

### CAUTION

The FCLKDIV register should never be written while a Flash command is executing (CCIF=0).

| Table 29-7 | . FCLKDIV | Field | Descriptions |

|------------|-----------|-------|--------------|

|------------|-----------|-------|--------------|

| Field            | Description                                                                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written since the last reset<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                   |

| 6<br>FDIVLCK     | <ul> <li>Clock Divider Locked</li> <li>FDIV field is open for writing</li> <li>FDIV value is locked and cannot be changed. Once the lock bit is set high, only reset can clear this bit and restore writability to the FDIV field in normal mode.</li> </ul>                                                                       |

| 5–0<br>FDIV[5:0] | <b>Clock Divider Bits</b> — FDIV[5:0] must be set to effectively divide BUSCLK down to 1 MHz to control timed events during Flash program and erase algorithms. Table 29-8 shows recommended values for FDIV[5:0] based on the BUSCLK frequency. Please refer to Section 29.4.4, "Flash Command Operations," for more information. |

| Field            | Description                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>FPLDIS      | Flash Protection Lower Address Range Disable — The FPLDIS bit determines whether there is a<br>protected/unprotected area in a specific region of the P-Flash memory beginning with global address 0x3_8000.0Protection/Unprotection enabled<br>11Protection/Unprotection disabled |

| 1–0<br>FPLS[1:0] | Flash Protection Lower Address Size — The FPLS bits determine the size of the protected/unprotected area in P-Flash memory as shown in Table 29-20. The FPLS bits can only be written to while the FPLDIS bit is set.                                                              |

#### Table 29-17. FPROT Field Descriptions (continued)

| FPOPEN | FPHDIS | FPLDIS | Function <sup>1</sup>           |

|--------|--------|--------|---------------------------------|

| 1      | 1      | 1      | No P-Flash Protection           |

| 1      | 1      | 0      | Protected Low Range             |

| 1      | 0      | 1      | Protected High Range            |

| 1      | 0      | 0      | Protected High and Low Ranges   |

| 0      | 1      | 1      | Full P-Flash Memory Protected   |

| 0      | 1      | 0      | Unprotected Low Range           |

| 0      | 0      | 1      | Unprotected High Range          |

| 0      | 0      | 0      | Unprotected High and Low Ranges |

#### Table 29-18. P-Flash Protection Function

<sup>1</sup> For range sizes, refer to Table 29-19 and Table 29-20.

#### Table 29-19. P-Flash Protection Higher Address Range

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_F800-0x3_FFFF    | 2 Kbytes       |

| 01        | 0x3_F000-0x3_FFFF    | 4 Kbytes       |

| 10        | 0x3_E000-0x3_FFFF    | 8 Kbytes       |

| 11        | 0x3_C000-0x3_FFFF    | 16 Kbytes      |

#### Table 29-20. P-Flash Protection Lower Address Range

| FPLS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_8000-0x3_83FF    | 1 Kbyte        |

| 01        | 0x3_8000-0x3_87FF    | 2 Kbytes       |

| 10        | 0x3_8000-0x3_8FFF    | 4 Kbytes       |

| 11        | 0x3_8000-0x3_9FFF    | 8 Kbytes       |

All possible P-Flash protection scenarios are shown in Figure 29-14. Although the protection scheme is loaded from the Flash memory at global address 0x3\_FF0C during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

### 30.4.6.15 Program EEPROM Command

The Program EEPROM operation programs one to four previously erased words in the EEPROM block. The Program EEPROM operation will confirm that the targeted location(s) were successfully programmed upon completion.

### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

| CCOBIX[2:0] | FCCOB Parameters                               |                                                     |

|-------------|------------------------------------------------|-----------------------------------------------------|

| 000         | 0x11                                           | Global address [17:16] to identify the EEPROM block |

| 001         | Global address [15:0] of word to be programmed |                                                     |

| 010         | Word 0 program value                           |                                                     |

| 011         | Word 1 program value, if desired               |                                                     |

| 100         | Word 2 program value, if desired               |                                                     |

| 101         | Word 3 program value, if desired               |                                                     |

Table 30-62. Program EEPROM Command FCCOB Requirements

Upon clearing CCIF to launch the Program EEPROM command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program EEPROM command launch determines how many words will be programmed in the EEPROM block. The CCIF flag is set when the operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] < 010 at command launch                                          |  |  |  |

| FSTAT    |           | Set if CCOBIX[2:0] > 101 at command launch                                          |  |  |  |

|          |           | Set if command not available in current mode (see Table 30-27)                      |  |  |  |

|          |           | Set if an invalid global address [17:0] is supplied                                 |  |  |  |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |  |

|          |           | Set if the requested group of words breaches the end of the EEPROM block            |  |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |

### 30.4.6.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

#### 240 KByte Flash Module (S12FTMRG240K2V1)

.

| Global Address      | Size<br>(Bytes) | Field Description                                                       |  |  |  |

|---------------------|-----------------|-------------------------------------------------------------------------|--|--|--|

| 0x0_40B8 - 0x0_40BF | 8               | Reserved                                                                |  |  |  |

| 0x0_40C0 - 0x0_40FF | 64              | Program Once Field<br>Refer to Section 31.4.6.6, "Program Once Command" |  |  |  |

Table 31-5. Program IFR Fields

<sup>1</sup> Used to track firmware patch versions, see Section 31.4.2

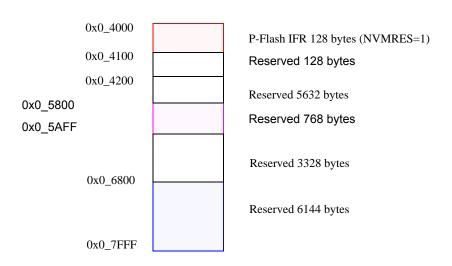

| Global Address         | Size<br>(Bytes) | Description                  |

|------------------------|-----------------|------------------------------|

| 0x0_4000 - 0x040FF 256 |                 | P-Flash IFR (see Table 31-5) |

| 0x0_4100 - 0x0_41FF    | 256             | Reserved.                    |

| 0x0_4200 - 0x0_57FF    |                 | Reserved                     |

| 0x0_5800 - 0x0_5AFF    | 768             | Reserved                     |

| 0x0_5B00 - 0x0_5FFF    | 1,280           | Reserved                     |

| 0x0_6000 - 0x0_67FF    | 2,048           | Reserved                     |

| 0x0_6800 - 0x0_7FFF    | 6,144           | Reserved                     |

<sup>1</sup> NVMRES - See Section 31.4.3 for NVMRES (NVM Resource) detail.

Figure 31-3. Memory Controller Resource Memory Map (NVMRES=1)

MC9S12G Family Reference Manual Rev.1.27

**Electrical Characteristics**

| Num          | С | Rating                                                                                      | Symbol               | S12GN32,<br>S12GNA32,<br>S12GN16,<br>S12GNA16 | S12G64,<br>S12GA64,<br>S12G48,<br>S12GN48,<br>S12GA64 | S12G128,<br>S12GA128,<br>S12G96,<br>S12GA96 | S12G240,<br>S12GA240,<br>S12G192,<br>S12GA192 | Unit |  |  |  |

|--------------|---|---------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------|-------------------------------------------------------|---------------------------------------------|-----------------------------------------------|------|--|--|--|

| 20-pin TSSOP |   |                                                                                             |                      |                                               |                                                       |                                             |                                               |      |  |  |  |

| 1            | D | Thermal resistance single sided PCB, natural convection <sup>2</sup>                        | $\theta_{JA}$        | 91                                            |                                                       |                                             |                                               | °C/W |  |  |  |

| 2            | D | Thermal resistance single sided PCB @ 200 ft/min <sup>3</sup>                               | $\theta_{JMA}$       | 72                                            |                                                       |                                             |                                               | °C/W |  |  |  |

| 3            | D | Thermal resistance double sided PCB with 2 internal planes, natural convection <sup>3</sup> | $\theta_{JA}$        | 58                                            |                                                       |                                             |                                               | °C/W |  |  |  |

| 4            | D | Thermal resistance double sided PCB with 2 internal planes @ 200 ft/min <sup>3</sup>        | θ <sub>JMA</sub>     | 51                                            |                                                       |                                             |                                               | °C/W |  |  |  |

| 5            | D | Junction to Board <sup>4</sup>                                                              | $\theta_{JB}$        | 29                                            |                                                       |                                             |                                               | °C/W |  |  |  |

| 6            | D | Junction to Case <sup>5</sup>                                                               | $\theta_{\text{JC}}$ | 20                                            |                                                       |                                             |                                               | °C/W |  |  |  |

| 7            | D | Junction to Package Top <sup>6</sup>                                                        | $\Psi_{JT}$          | 4                                             |                                                       |                                             |                                               | °C/W |  |  |  |

|              |   |                                                                                             | 32-pin LQF           | -P                                            | •                                                     |                                             |                                               |      |  |  |  |

| 8            | D | Thermal resistance single sided PCB, natural convection <sup>2</sup>                        | θ <sub>JA</sub>      | 81                                            | 84                                                    |                                             |                                               | °C/W |  |  |  |

| 9            | D | Thermal resistance single sided PCB @ 200 ft/min <sup>3</sup>                               | θ <sub>JMA</sub>     | 68                                            | 70                                                    |                                             |                                               | °C/W |  |  |  |

| 10           | D | Thermal resistance double sided PCB with 2 internal planes, natural convection <sup>3</sup> | $\theta_{JA}$        | 57                                            | 56                                                    |                                             |                                               | °C/W |  |  |  |

| 11           | D | Thermal resistance double sided PCB with 2 internal planes @ 200 ft/min <sup>3</sup>        | $\theta_{JMA}$       | 50                                            | 49                                                    |                                             |                                               | °C/W |  |  |  |

| 12           | D | Junction to Board <sup>4</sup>                                                              | $\theta_{JB}$        | 35                                            | 32                                                    |                                             |                                               | °C/W |  |  |  |

| 13           | D | Junction to Case <sup>5</sup>                                                               | $\theta_{JC}$        | 25                                            | 23                                                    |                                             |                                               | °C/W |  |  |  |

| 14           | D | Junction to Package Top <sup>6</sup>                                                        | $\Psi_{JT}$          | 8                                             | 6                                                     |                                             |                                               | °C/W |  |  |  |

|              |   |                                                                                             | 48-pin LQF           | =P                                            |                                                       |                                             |                                               |      |  |  |  |

| 15           | D | Thermal resistance single sided PCB, natural convection <sup>2</sup>                        | $\theta_{JA}$        | 81                                            | 80                                                    | 79                                          | 75                                            | °C/W |  |  |  |

| 16           | D | Thermal resistance single sided PCB @ 200 ft/min <sup>3</sup>                               | θ <sub>JMA</sub>     | 68                                            | 67                                                    | 66                                          | 62                                            | °C/W |  |  |  |

| 17           | D | Thermal resistance double sided PCB with 2 internal planes, natural convection <sup>3</sup> | $\theta_{JA}$        | 57                                            | 56                                                    | 56                                          | 51                                            | °C/W |  |  |  |

| 18           | D | Thermal resistance double sided PCB with 2 internal planes @ 200 ft/min <sup>3</sup>        | θ <sub>JMA</sub>     | 50                                            | 50                                                    | 49                                          | 45                                            | °C/W |  |  |  |

| 19           | D | Junction to Board <sup>4</sup>                                                              | θ <sub>JB</sub>      | 35                                            | 34                                                    | 33                                          | 30                                            | °C/W |  |  |  |

| 20           | D | Junction to Case <sup>5</sup>                                                               | θ <sub>JC</sub>      | 25                                            | 24                                                    | 21                                          | 19                                            | °C/W |  |  |  |

| 21           | D | Junction to Package Top <sup>6</sup>                                                        | $\Psi_{JT}$          | 8                                             | 6                                                     | 4                                           | N/A                                           | °C/W |  |  |  |

### Table A-5. Thermal Package Characteristics<sup>1</sup>