Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 12V1                                                                  |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 40                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1.5K x 8                                                              |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g48f0wlf |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 21.4.4 SPI Baud Rate Generation | 712 |

|---------------------------------|-----|

| 21.4.5 Special Features         | 713 |

| 21.4.6 Error Conditions         | 714 |

| 21.4.7 Low Power Mode Options   | 715 |

# Chapter 22 Timer Module (TIM16B6CV3)

| 22.1 | Introduction                                                      |  |

|------|-------------------------------------------------------------------|--|

|      | 22.1.1 Features                                                   |  |

|      | 22.1.2 Modes of Operation                                         |  |

|      | 22.1.3 Block Diagrams                                             |  |

| 22.2 | External Signal Description                                       |  |

|      | 22.2.1 IOC5 - IOC0 — Input Capture and Output Compare Channel 5-0 |  |

| 22.3 | Memory Map and Register Definition                                |  |

|      | 22.3.1 Module Memory Map                                          |  |

|      | 22.3.2 Register Descriptions                                      |  |

| 22.4 | Functional Description                                            |  |

|      | 22.4.1 Prescaler                                                  |  |

|      | 22.4.2 Input Capture                                              |  |

|      | 22.4.3 Output Compare                                             |  |

| 22.5 | Resets                                                            |  |

| 22.6 | Interrupts                                                        |  |

|      | 22.6.1 Channel [5:0] Interrupt (C[5:0]F)                          |  |

|      | 22.6.2 Timer Overflow Interrupt (TOF)                             |  |

# Chapter 23 Timer Module (TIM16B8CV3)

| Introduction                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23.1.1 Features                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.1.2 Modes of Operation                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.1.3 Block Diagrams                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| External Signal Description                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.2.1 IOC7 — Input Capture and Output Compare Channel 7          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.2.2 IOC6 - IOC0 — Input Capture and Output Compare Channel 6-0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Memory Map and Register Definition                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.3.1 Module Memory Map                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.3.2 Register Descriptions                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Functional Description                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.4.1 Prescaler                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.4.2 Input Capture                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.4.3 Output Compare                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.4.4 Pulse Accumulator                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.4.5 Event Counter Mode                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23.4.6 Gated Time Accumulation Mode                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                   | <ul> <li>23.1.1 Features</li> <li>23.1.2 Modes of Operation</li> <li>23.1.3 Block Diagrams</li> <li>External Signal Description</li> <li>23.2.1 IOC7 — Input Capture and Output Compare Channel 7</li> <li>23.2.2 IOC6 - IOC0 — Input Capture and Output Compare Channel 6-0</li> <li>Memory Map and Register Definition</li> <li>23.3.1 Module Memory Map</li> <li>23.3.2 Register Descriptions</li> <li>Functional Description</li> <li>23.4.1 Prescaler</li> <li>23.4.2 Input Capture</li> <li>23.4.3 Output Compare</li> <li>23.4.4 Pulse Accumulator</li> <li>23.4.5 Event Counter Mode</li> </ul> |

# 1.3.8 System Integrity Support

- Power-on reset (POR)

- System reset generation

- Illegal address detection with reset

- Low-voltage detection with interrupt or reset

- Real time interrupt (RTI)

- Computer operating properly (COP) watchdog

- Configurable as window COP for enhanced failure detection

- Initialized out of reset using option bits located in flash memory

- Clock monitor supervising the correct function of the oscillator

## 1.3.9 Timer (TIM)

- Up to eight x 16-bit channels for input capture or output compare

- 16-bit free-running counter with 7-bit precision prescaler

- In case of eight channel timer Version an additional 16-bit pulse accumulator is available

## 1.3.10 Pulse Width Modulation Module (PWM)

- Up to eight channel x 8-bit or up to four channel x 16-bit pulse width modulator

- Programmable period and duty cycle per channel

- Center-aligned or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

### 1.3.11 Controller Area Network Module (MSCAN)

- 1 Mbit per second, CAN 2.0 A, B software compatible

- Standard and extended data frames

- 0–8 bytes data length

- Programmable bit rate up to 1 Mbps

- Five receive buffers with FIFO storage scheme

- Three transmit buffers with internal prioritization

- Flexible identifier acceptance filter programmable as:

- 2 x 32-bit

- 4 x 16-bit

- 8 x 8-bit

- Wakeup with integrated low pass filter option

- Loop back for self test

- Listen-only mode to monitor CAN bus

# 7.4.9 SYNC — Request Timed Reference Pulse

The SYNC command is unlike other BDM commands because the host does not necessarily know the correct communication speed to use for BDM communications until after it has analyzed the response to the SYNC command. To issue a SYNC command, the host should perform the following steps:

- 1. Drive the BKGD pin low for at least 128 cycles at the lowest possible BDM serial communication frequency (The lowest serial communication frequency is determined by the settings for the VCO clock (CPMUSYNR). The BDM clock frequency is always VCO clock frequency divided by 8.)

- 2. Drive BKGD high for a brief speedup pulse to get a fast rise time (this speedup pulse is typically one cycle of the host clock.)

- 3. Remove all drive to the BKGD pin so it reverts to high impedance.

- 4. Listen to the BKGD pin for the sync response pulse.

Upon detecting the SYNC request from the host, the target performs the following steps:

- 1. Discards any incomplete command received or bit retrieved.

- 2. Waits for BKGD to return to a logic one.

- 3. Delays 16 cycles to allow the host to stop driving the high speedup pulse.

- 4. Drives BKGD low for 128 cycles at the current BDM serial communication frequency.

- 5. Drives a one-cycle high speedup pulse to force a fast rise time on BKGD.

- 6. Removes all drive to the BKGD pin so it reverts to high impedance.

The host measures the low time of this 128 cycle SYNC response pulse and determines the correct speed for subsequent BDM communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

As soon as the SYNC request is detected by the target, any partially received command or bit retrieved is discarded. This is referred to as a soft-reset, equivalent to a time-out in the serial communication. After the SYNC response, the target will consider the next negative edge (issued by the host) as the start of a new BDM command or the start of new SYNC request.

Another use of the SYNC command pulse is to abort a pending ACK pulse. The behavior is exactly the same as in a regular SYNC command. Note that one of the possible causes for a command to not be acknowledged by the target is a host-target synchronization problem. In this case, the command may not have been understood by the target and so an ACK response pulse will not be issued.

# 7.4.10 Instruction Tracing

When a TRACE1 command is issued to the BDM in active BDM, the CPU exits the standard BDM firmware and executes a single instruction in the user code. Once this has occurred, the CPU is forced to return to the standard BDM firmware and the BDM is active and ready to receive a new command. If the TRACE1 command is issued again, the next user instruction will be executed. This facilitates stepping or tracing through the user code one instruction at a time.

| Address | Name      | Bit 7       | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 |

|---------|-----------|-------------|----|----|----|----|----|---|-------|

| 0x002C  | DBGADH V  | R<br>Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

| 0x002D  | DBGADL F  | R Bit 7     | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 |

| 0x002E  | DBGADHM V | R<br>Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

| 0x002F  | DBGADLM V |             | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 |

<sup>1</sup> This bit is visible at DBGCNT[7] and DBGSR[7]

<sup>2</sup> This represents the contents if the Comparator A control register is blended into this address.

<sup>3</sup> This represents the contents if the Comparator B control register is blended into this address

<sup>4</sup> This represents the contents if the Comparator C control register is blended into this address

Figure 8-2. Quick Reference to DBG Registers

### 8.3.2 Register Descriptions

This section consists of the DBG control and trace buffer register descriptions in address order. Each comparator has a bank of registers that are visible through an 8-byte window between 0x0028 and 0x002F in the DBG module register address map. When ARM is set in DBGC1, the only bits in the DBG module registers that can be written are ARM, TRIG, and COMRV[1:0].

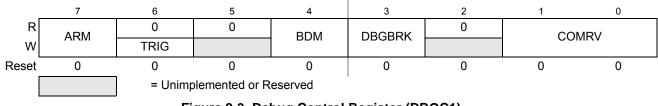

### 8.3.2.1 Debug Control Register 1 (DBGC1)

Address: 0x0020

Figure 8-3. Debug Control Register (DBGC1)

Read: Anytime

Write: Bits 7, 1, 0 anytime Bit 6 can be written anytime but always reads back as 0. Bits 4:3 anytime DBG is not armed.

### NOTE

When disarming the DBG by clearing ARM with software, the contents of bits[4:3] are not affected by the write, since up until the write operation, ARM = 1 preventing these bits from being written. These bits must be cleared using a second write if required.

Analog-to-Digital Converter (ADC10B12CV2)

# 13.3.2 Register Descriptions

This section describes in address order all the ADC10B12C registers and their individual bits.

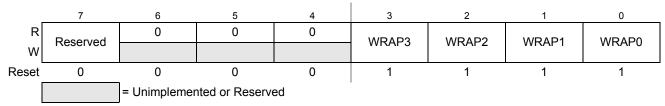

# 13.3.2.1 ATD Control Register 0 (ATDCTL0)

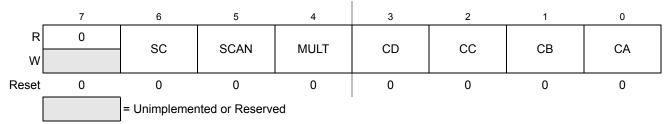

Writes to this register will abort current conversion sequence.

Module Base + 0x0000

### Figure 13-3. ATD Control Register 0 (ATDCTL0)

### Read: Anytime

Write: Anytime, in special modes always write 0 to Reserved Bit 7.

| Field            | Description                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                                                                         |

| 3-0<br>WRAP[3-0] | <b>Wrap Around Channel Select Bits</b> — These bits determine the channel for wrap around when doing multi-channel conversions. The coding is summarized in Table 13-2. |

#### Table 13-2. Multi-Channel Wrap Around Coding

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1)<br>Wraparound to AN0 after Converting |

|-------|-------|-------|-------|-------------------------------------------------------------------------------|

| 0     | 0     | 0     | 0     | Reserved <sup>1</sup>                                                         |

| 0     | 0     | 0     | 1     | AN1                                                                           |

| 0     | 0     | 1     | 0     | AN2                                                                           |

| 0     | 0     | 1     | 1     | AN3                                                                           |

| 0     | 1     | 0     | 0     | AN4                                                                           |

| 0     | 1     | 0     | 1     | AN5                                                                           |

| 0     | 1     | 1     | 0     | AN6                                                                           |

| 0     | 1     | 1     | 1     | AN7                                                                           |

| 1     | 0     | 0     | 0     | AN8                                                                           |

| 1     | 0     | 0     | 1     | AN9                                                                           |

| 1     | 0     | 1     | 0     | AN10                                                                          |

| 1     | 0     | 1     | 1     | AN11                                                                          |

| 1     | 1     | 0     | 0     | AN11                                                                          |

| 1     | 1     | 0     | 1     | AN11                                                                          |

| 1     | 1     | 1     | 0     | AN11                                                                          |

| 1     | 1     | 1     | 1     | AN11                                                                          |

Analog-to-Digital Converter (ADC12B12CV2)

# 14.3.2 Register Descriptions

This section describes in address order all the ADC12B12C registers and their individual bits.

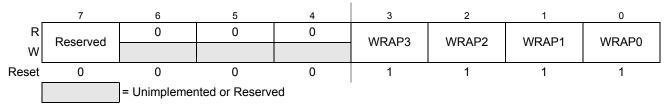

# 14.3.2.1 ATD Control Register 0 (ATDCTL0)

Writes to this register will abort current conversion sequence.

Module Base + 0x0000

### Figure 14-3. ATD Control Register 0 (ATDCTL0)

### Read: Anytime

Write: Anytime, in special modes always write 0 to Reserved Bit 7.

| Field            | Description                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                                                                         |

| 3-0<br>WRAP[3-0] | <b>Wrap Around Channel Select Bits</b> — These bits determine the channel for wrap around when doing multi-channel conversions. The coding is summarized in Table 14-2. |

#### Table 14-2. Multi-Channel Wrap Around Coding

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1)<br>Wraparound to AN0 after Converting |

|-------|-------|-------|-------|-------------------------------------------------------------------------------|

| 0     | 0     | 0     | 0     | Reserved <sup>1</sup>                                                         |

| 0     | 0     | 0     | 1     | AN1                                                                           |

| 0     | 0     | 1     | 0     | AN2                                                                           |

| 0     | 0     | 1     | 1     | AN3                                                                           |

| 0     | 1     | 0     | 0     | AN4                                                                           |

| 0     | 1     | 0     | 1     | AN5                                                                           |

| 0     | 1     | 1     | 0     | AN6                                                                           |

| 0     | 1     | 1     | 1     | AN7                                                                           |

| 1     | 0     | 0     | 0     | AN8                                                                           |

| 1     | 0     | 0     | 1     | AN9                                                                           |

| 1     | 0     | 1     | 0     | AN10                                                                          |

| 1     | 0     | 1     | 1     | AN11                                                                          |

| 1     | 1     | 0     | 0     | AN11                                                                          |

| 1     | 1     | 0     | 1     | AN11                                                                          |

| 1     | 1     | 1     | 0     | AN11                                                                          |

| 1     | 1     | 1     | 1     | AN11                                                                          |

| SMP2 | SMP1 | SMP0 | Sample Time<br>in Number of<br>ATD Clock Cycles |

|------|------|------|-------------------------------------------------|

| 1    | 1    | 1    | 24                                              |

#### Table 14-13. Sample Time Select

# 14.3.2.6 ATD Control Register 5 (ATDCTL5)

Writes to this register will abort current conversion sequence and start a new conversion sequence. If the external trigger function is enabled (ETRIGE=1) an initial write to ATDCTL5 is required to allow starting of a conversion sequence which will then occur on each trigger event. Start of conversion means the beginning of the sampling phase.

Module Base + 0x0005

### Figure 14-8. ATD Control Register 5 (ATDCTL5)

Read: Anytime

Write: Anytime

### Table 14-14. ATDCTL5 Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>SC   | <ul> <li>Special Channel Conversion Bit — If this bit is set, then special channel conversion can be selected using CD, CC, CB and CA of ATDCTL5. Table 14-15 lists the coding.</li> <li>O Special channel conversions disabled</li> <li>1 Special channel conversions enabled</li> </ul>                                                                                                                  |

| 5<br>SCAN | <ul> <li>Continuous Conversion Sequence Mode — This bit selects whether conversion sequences are performed continuously or only once. If the external trigger function is enabled (ETRIGE=1) setting this bit has no effect, thus the external trigger always starts a single conversion sequence.</li> <li>0 Single conversion sequence</li> <li>1 Continuous conversion sequences (scan mode)</li> </ul> |

#### Serial Communication Interface (S12SCIV5)

new byte can be written to the SCIDRH/L for transmission.Clear TDRE by reading SCI status register 1 with TDRE set and then writing to SCI data register low (SCIDRL).

### 20.5.3.1.2 TC Description

The TC interrupt is set by the SCI when a transmission has been completed. Transmission is completed when all bits including the stop bit (if transmitted) have been shifted out and no data is queued to be transmitted. No stop bit is transmitted when sending a break character and the TC flag is set (providing there is no more data queued for transmission) when the break character has been shifted out. A TC interrupt indicates that there is no transmission in progress. TC is set high when the TDRE flag is set and no data, preamble, or break character is being transmitted. When TC is set, the TXD pin becomes idle (logic 1). Clear TC by reading SCI status register 1 (SCISR1) with TC set and then writing to SCI data register low (SCIDRL).TC is cleared automatically when data, preamble, or break is queued and ready to be sent.

### 20.5.3.1.3 RDRF Description

The RDRF interrupt is set when the data in the receive shift register transfers to the SCI data register. A RDRF interrupt indicates that the received data has been transferred to the SCI data register and that the byte can now be read by the MCU. The RDRF interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

### 20.5.3.1.4 OR Description

The OR interrupt is set when software fails to read the SCI data register before the receive shift register receives the next frame. The newly acquired data in the shift register will be lost in this case, but the data already in the SCI data registers is not affected. The OR interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

### 20.5.3.1.5 IDLE Description

The IDLE interrupt is set when 10 consecutive logic 1s (if M = 0) or 11 consecutive logic 1s (if M = 1) appear on the receiver input. Once the IDLE is cleared, a valid frame must again set the RDRF flag before an idle condition can set the IDLE flag. Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then reading SCI data register low (SCIDRL).

### 20.5.3.1.6 RXEDGIF Description

The RXEDGIF interrupt is set when an active edge (falling if RXPOL = 0, rising if RXPOL = 1) on the RXD pin is detected. Clear RXEDGIF by writing a "1" to the SCIASR1 SCI alternative status register 1.

### 20.5.3.1.7 BERRIF Description

The BERRIF interrupt is set when a mismatch between the transmitted and the received data in a single wire application like LIN was detected. Clear BERRIF by writing a "1" to the SCIASR1 SCI alternative status register 1. This flag is also cleared if the bit error detect feature is disabled.

Table 24-34. Erase Verify P-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |  |

|-------------|----------------------------------------------------------|----------------------------------------------|--|

| 000         | 0x03                                                     | Global address [17:16] of<br>a P-Flash block |  |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |  |

| 010         | Number of phrases to be verified                         |                                              |  |

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 24-35. Erase Verify P-Flash Section Command Error Handling

| Register | Error Bit | Error Condition                                                                                                |

|----------|-----------|----------------------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                                                                    |

|          |           | Set if command not available in current mode (see Table 24-25)                                                 |

|          |           | Set if an invalid global address [17:0] is supplied see Table 24-3) <sup>1</sup>                               |

|          |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                                   |

| FSTAT    |           | Set if the requested section crosses a the P-Flash address boundary                                            |

|          | FPVIOL    | None                                                                                                           |

|          | MGSTAT1   | Set if any errors have been encountered during the read <sup>2</sup> or if blank check failed.                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read <sup>2</sup> or if blank check failed. |

<sup>1</sup> As defined by the memory map for FTMRG32K1.

$^2$  As found in the memory map for FTMRG32K1.

## 24.4.6.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once command described in Section 24.4.6.6. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| Table 24-3 | 5. Read Once Command FCCOB Requirements |

|------------|-----------------------------------------|

|            |                                         |

| CCOBIX[2:0] | FCCOB Parameters       |                       |

|-------------|------------------------|-----------------------|

| 000         | 0x04                   | Not Required          |

| 001         | Read Once phrase inc   | dex (0x0000 - 0x0007) |

| 010         | Read Once word 0 value |                       |

| 011         | Read Once word 1 value |                       |

| 100         | Read Once word 2 value |                       |

- Fast sector erase and phrase program operation

- Ability to read the P-Flash memory while programming a word in the EEPROM memory

- Flexible protection scheme to prevent accidental program or erase of P-Flash memory

### 25.1.2.2 EEPROM Features

- 1 Kbyte of EEPROM memory composed of one 1 Kbyte Flash block divided into 256 sectors of 4 bytes

- Single bit fault correction and double bit fault detection within a word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and word program operation

- Protection scheme to prevent accidental program or erase of EEPROM memory

- Ability to program up to four words in a burst sequence

### 25.1.2.3 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

# 25.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 25-1.

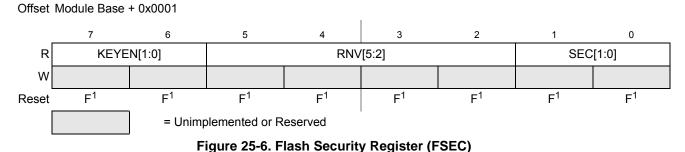

# 25.3.2.2 Flash Security Register (FSEC)

The FSEC register holds all bits associated with the security of the MCU and Flash module.

<sup>1</sup> Loaded from IFR Flash configuration field, during reset sequence.

All bits in the FSEC register are readable but not writable.

During the reset sequence, the FSEC register is loaded with the contents of the Flash security byte in the Flash configuration field at global address 0x3\_FF0F located in P-Flash memory (see Table 25-4) as indicated by reset condition F in Figure 25-6. If a double bit fault is detected while reading the P-Flash phrase containing the Flash security byte during the reset sequence, all bits in the FSEC register will be set to leave the Flash module in a secured state with backdoor key access disabled.

| Field             | Description                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6<br>KEYEN[1:0] | <b>Backdoor Key Security Enable Bits</b> — The KEYEN[1:0] bits define the enabling of backdoor key access to the Flash module as shown in Table 25-10.                                                  |

| 5–2<br>RNV[5:2]   | <b>Reserved Nonvolatile Bits</b> — The RNV bits should remain in the erased state for future enhancements.                                                                                              |

| 1–0<br>SEC[1:0]   | <b>Flash Security Bits</b> — The SEC[1:0] bits define the security state of the MCU as shown in Table 25-11. If the Flash module is unsecured using backdoor key access, the SEC bits are forced to 10. |

| Table 25-10 | . Flash KE | YEN States |

|-------------|------------|------------|

|-------------|------------|------------|

| KEYEN[1:0] | Status of Backdoor Key Access |

|------------|-------------------------------|

| 00         | DISABLED                      |

| 01         | DISABLED <sup>1</sup>         |

| 10         | ENABLED                       |

| 11         | DISABLED                      |

<sup>1</sup> Preferred KEYEN state to disable backdoor key access.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 25-27)                      |

|          |           | Set if an invalid global address [17:0] is supplied see Table 25-3)                 |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the global address [17:0] points to a protected area                         |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 25-41. Program P-Flash Command Error Handling

### 25.4.6.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash. The Program Once reserved field can be read using the Read Once command as described in Section 25.4.6.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |              |  |

|-------------|---------------------------------------------|--------------|--|

| 000         | 0x07                                        | Not Required |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |              |  |

| 010         | Program Once word 0 value                   |              |  |

| 011         | Program Once word 1 value                   |              |  |

| 100         | Program Once word 2 value                   |              |  |

| 101         | Program Once word 3 value                   |              |  |

Table 25-42. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash will return invalid data.

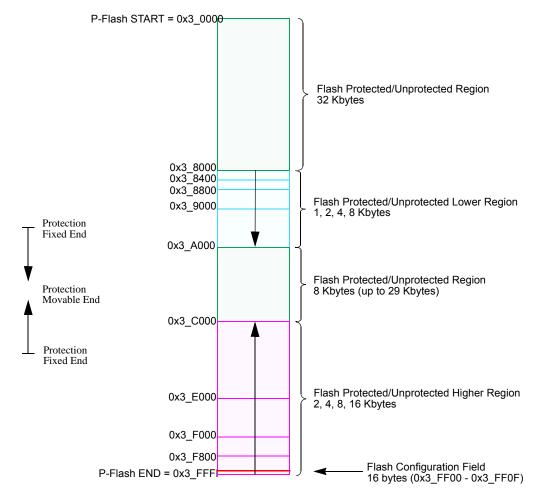

Figure 27-2. P-Flash Memory Map

| Table 27-5. Program IFR | Fields |

|-------------------------|--------|

|-------------------------|--------|

| Global Address      | Size<br>(Bytes) | Field Description                                                       |

|---------------------|-----------------|-------------------------------------------------------------------------|

| 0x0_4000 - 0x0_4007 | 8               | Reserved                                                                |

| 0x0_4008 - 0x0_40B5 | 174             | Reserved                                                                |

| 0x0_40B6 - 0x0_40B7 | 2               | Version ID <sup>1</sup>                                                 |

| 0x0_40B8 - 0x0_40BF | 8               | Reserved                                                                |

| 0x0_40C0 - 0x0_40FF | 64              | Program Once Field<br>Refer to Section 27.4.6.6, "Program Once Command" |

<sup>1</sup> Used to track firmware patch versions, see Section 27.4.2

#### 64 KByte Flash Module (S12FTMRG64K1V1)

During the reset sequence, fields DPOPEN and DPS of the EEPROT register are loaded with the contents of the EEPROM protection byte in the Flash configuration field at global address 0x3\_FF0D located in P-Flash memory (see Table 27-4) as indicated by reset condition F in Table 27-23. To change the EEPROM protection that will be loaded during the reset sequence, the P-Flash sector containing the EEPROM protection byte must be unprotected, then the EEPROM protection byte must be programmed. If a double bit fault is detected while reading the P-Flash phrase containing the EEPROM protection byte must be to leave the EEPROM protection byte must be programmed. If a double bit fault is detected while reading the P-Flash phrase containing the EEPROM protection byte must be memory fully protected.

Trying to alter data in any protected area in the EEPROM memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. Block erase of the EEPROM memory is not possible if any of the EEPROM sectors are protected.

| Field           | Description                                                                                                                                                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DPOPEN     | <ul> <li>EEPROM Protection Control</li> <li>Enables EEPROM memory protection from program and erase with protected address range defined by DPS bits</li> <li>Disables EEPROM memory protection from program and erase</li> </ul> |

| 5–0<br>DPS[5:0] | <b>EEPROM Protection Size</b> — The DPS[5:0] bits determine the size of the protected area in the EEPROM memory as shown in Table 27-23.                                                                                          |

| DPS[5:0]                                                                                         | Global Address Range            | Protected Size |  |

|--------------------------------------------------------------------------------------------------|---------------------------------|----------------|--|

| 000000                                                                                           | 0x0_0400 – 0x0_041F             | 32 bytes       |  |

| 000001                                                                                           | 0x0_0400 – 0x0_043F             | 64 bytes       |  |

| 000010                                                                                           | 0x0_0400 – 0x0_045F             | 96 bytes       |  |

| 000011                                                                                           | 0x0_0400 – 0x0_047F             | 128 bytes      |  |

| 000100                                                                                           | 0x0_0400 – 0x0_049F             | 160 bytes      |  |

| 000101                                                                                           | 0x0_0400 – 0x0_04BF             | 192 bytes      |  |

| The Protection Size goes on enlarging in step of 32 bytes, for each DPS value increasing of one. |                                 |                |  |

| 111111                                                                                           | 0x0_0400 – 0x0_0BFF 2,048 bytes |                |  |

#### Table 27-23. EEPROM Protection Address Range

#### 96 KByte Flash Module (S12FTMRG96K1V1)

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|------|-------------------------------------------|

| 010         | HI   | Data 0 [15:8]                             |

|             | LO   | Data 0 [7:0]                              |

| 011         | HI   | Data 1 [15:8]                             |

|             | LO   | Data 1 [7:0]                              |

| 100         | HI   | Data 2 [15:8]                             |

|             | LO   | Data 2 [7:0]                              |

| 101         | HI   | Data 3 [15:8]                             |

|             | LO   | Data 3 [7:0]                              |

Table 28-24. FCCOB - NVM Command Mode (Typical Usage)

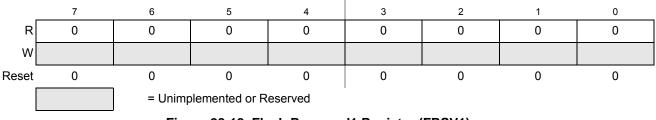

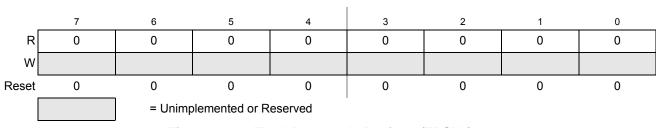

### 28.3.2.12 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000C

Offset Module Base + 0x000D

Figure 28-18. Flash Reserved1 Register (FRSV1)

All bits in the FRSV1 register read 0 and are not writable.

## 28.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

Figure 28-19. Flash Reserved2 Register (FRSV2)

All bits in the FRSV2 register read 0 and are not writable.

### 28.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

#### 96 KByte Flash Module (S12FTMRG96K1V1)

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 28.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 28.4.6.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0x3\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x3\_FF00-0x3\_FF07 are unaffected by the Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired. In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses 0x3\_FF00-0x3\_FF07 in the Flash configuration field.

# 28.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

A secured MCU can be unsecured in special single chip mode by using the following method to erase the P-Flash and EEPROM memory:

- 1. Reset the MCU into special single chip mode

- 2. Delay while the BDM executes the Erase Verify All Blocks command write sequence to check if the P-Flash and EEPROM memories are erased

- 3. Send BDM commands to disable protection in the P-Flash and EEPROM memory

- 4. Execute the Erase All Blocks command write sequence to erase the P-Flash and EEPROM memory. Alternatively the Unsecure Flash command can be executed, if so the steps 5 and 6 below are skeeped.

- 5. After the CCIF flag sets to indicate that the Erase All Blocks operation has completed, reset the MCU into special single chip mode

- 6. Delay while the BDM executes the Erase Verify All Blocks command write sequence to verify that the P-Flash and EEPROM memory are erased

If the P-Flash and EEPROM memory are verified as erased, the MCU will be unsecured. All BDM commands will now be enabled and the Flash security byte may be programmed to the unsecure state by continuing with the following steps:

7. Send BDM commands to execute the Program P-Flash command write sequence to program the Flash security byte to the unsecured state

# 29.3 Memory Map and Registers

This section describes the memory map and registers for the Flash module. Read data from unimplemented memory space in the Flash module is undefined. Write access to unimplemented or reserved memory space in the Flash module will be ignored by the Flash module.

### CAUTION

Writing to the Flash registers while a Flash command is executing (that is indicated when the value of flag CCIF reads as '0') is not allowed. If such action is attempted the write operation will not change the register value.

Writing to the Flash registers is allowed when the Flash is not busy executing commands (CCIF = 1) and during initialization right after reset, despite the value of flag CCIF in that case (refer to Section 29.6 for a complete description of the reset sequence).

| Global Address (in Bytes) | Size<br>(Bytes) | Description                                                  |  |

|---------------------------|-----------------|--------------------------------------------------------------|--|

| 0x0_0000 - 0x0_03FF       | 1,024           | Register Space                                               |  |

| 0x0_0400 – 0x0_13FF       | 4,096           | EEPROM Memory                                                |  |

| 0x0_4000 - 0x0_7FFF       | 16,284          | NVMRES <sup>1</sup> =1 : NVM Resource area (see Figure 29-3) |  |

| 0x2_0000 – 0x3_FFFF       | 131,072         | P-Flash Memory                                               |  |

#### Table 29-2. FTMRG Memory Map

<sup>1</sup> See NVMRES description in Section 29.4.3

## 29.3.1 Module Memory Map

The S12 architecture places the P-Flash memory between global addresses 0x2\_0000 and 0x3\_FFFF as shown in Table 29-3. The P-Flash memory map is shown in Figure 29-2.

| Global Address      | Size<br>(Bytes) | Description                                                             |

|---------------------|-----------------|-------------------------------------------------------------------------|

| 0x2_0000 – 0x3_FFFF | 128 K           | P-Flash Block<br>Contains Flash Configuration Field<br>(see Table 29-4) |

#### Table 29-3. P-Flash Memory Addressing

#### 128 KByte Flash Module (S12FTMRG128K1V1)

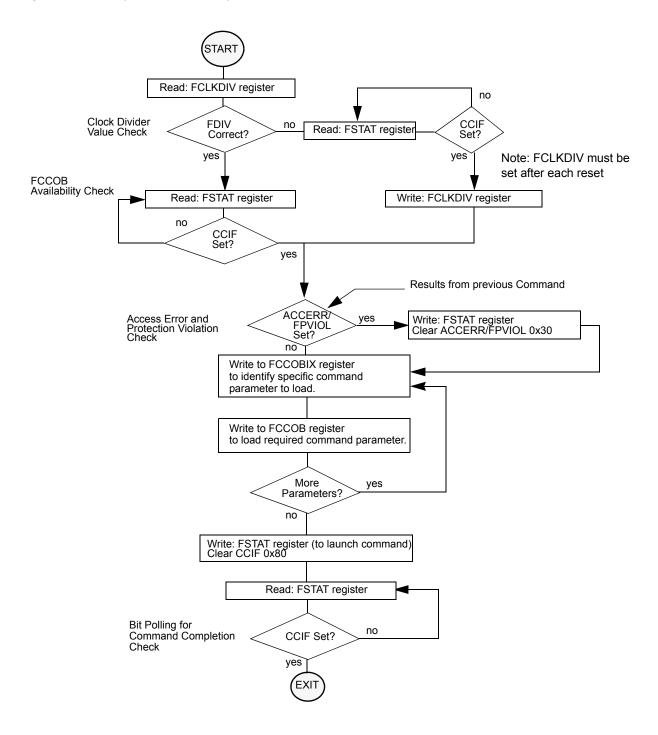

Figure 29-26. Generic Flash Command Write Sequence Flowchart

**Electrical Characteristics**

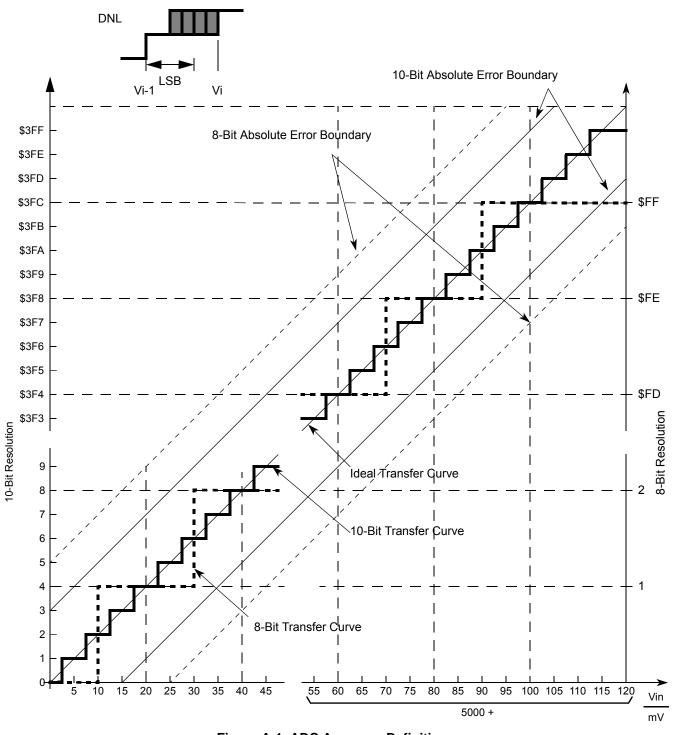

Figure A-1. ADC Accuracy Definitions

### NOTE

Figure A-1 shows only definitions, for specification values refer to Table A-21 and Table A-26.

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

/4 dimensions to be determined at seating plane c.

5. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 mm AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm.

A THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

$/\overline{2}$  exact shape of each corner is optional.

A. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 mm AND 0.25 mm FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.               |  | LOUTLINE     | E PRINT VERSION NOT TO SCALE |             |

|--------------------------------------------------------------------|--|--------------|------------------------------|-------------|

| TITLE: 64LD LQFP,<br>10 X 10 X 1.4 PKG,<br>0.5 PITCH, CASE OUTLINE |  | DOCUMENT NO  | : 98ASS23234W                | REV: E      |

|                                                                    |  | CASE NUMBER  | : 840F-02                    | 11 AUG 2006 |

|                                                                    |  | STANDARD: JE | DEC MS-026 BCD               |             |