Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 26                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1.5K x 8                                                               |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g48f1clcr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

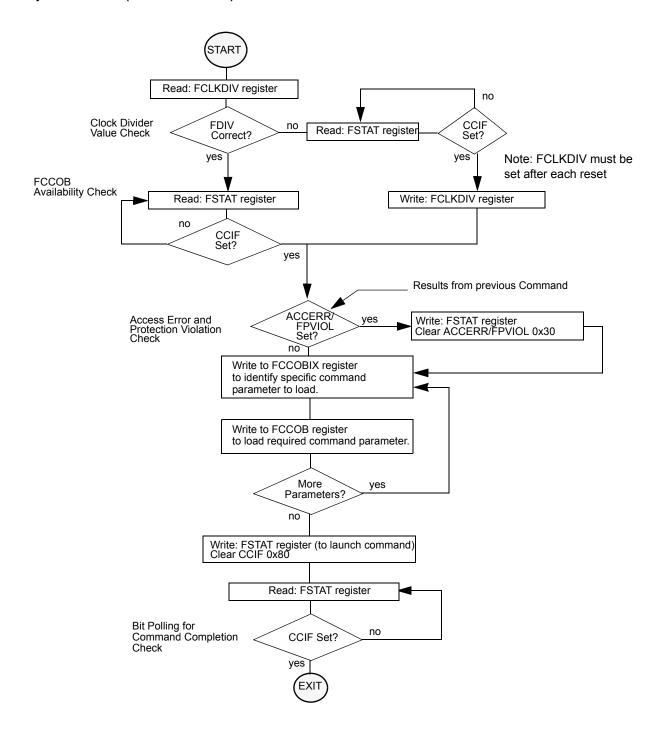

|             | 30.4.4 Flash Command Operations                                 | 1100 |

|-------------|-----------------------------------------------------------------|------|

|             | 30.4.5 Allowed Simultaneous P-Flash and EEPROM Operations       | 1105 |

|             | 30.4.6 Flash Command Description                                | 1106 |

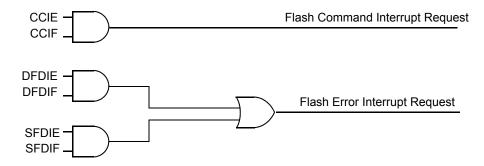

|             | 30.4.7 Interrupts                                               |      |

|             | 30.4.8 Wait Mode                                                |      |

|             | 30.4.9 Stop Mode                                                |      |

| 30.5        | Security                                                        |      |

|             | 30.5.1 Unsecuring the MCU using Backdoor Key Access             |      |

|             | 30.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM |      |

|             | 30.5.3 Mode and Security Effects on Flash Command Availability  |      |

| 30.6        | Initialization                                                  |      |

| 2010        |                                                                 |      |

|             | Chapter 31                                                      |      |

|             | 240 KByte Flash Module (S12FTMRG240K2V1)                        |      |

| 31.1        | Introduction                                                    | 1125 |

|             | 31.1.1 Glossary                                                 |      |

|             | 31.1.2 Features                                                 |      |

|             | 31.1.3 Block Diagram                                            |      |

| 31.2        | External Signal Description                                     |      |

| 31.3        |                                                                 |      |

| 51.5        | 31.3.1 Module Memory Map                                        |      |

|             | 31.3.2 Register Descriptions                                    |      |

| 31 4        | Functional Description                                          |      |

| 31.1        | 31.4.1 Modes of Operation                                       |      |

|             | 31.4.2 IFR Version ID Word                                      |      |

|             | 31.4.3 Internal NVM resource (NVMRES)                           |      |

|             | 31.4.4 Flash Command Operations                                 |      |

|             | 31.4.5 Allowed Simultaneous P-Flash and EEPROM Operations       |      |

|             | 31.4.6 Flash Command Description                                |      |

|             | 31.4.7 Interrupts                                               |      |

|             | 31.4.8 Wait Mode                                                |      |

|             | 31.4.9 Stop Mode                                                |      |

| 31.5        | Security                                                        |      |

| 51.0        | 31.5.1 Unsecuring the MCU using Backdoor Key Access             |      |

|             | 31.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM |      |

|             | 31.5.3 Mode and Security Effects on Flash Command Availability  |      |

| 31.6        | Initialization                                                  |      |

| 31.0        |                                                                 |      |

|             | Appendix A                                                      |      |

|             | Electrical Characteristics                                      |      |

| <b>A.</b> 1 | General                                                         | 1178 |

|             | A.1.1 Parameter Classification                                  |      |

|             | A.1.2 Power Supply                                              |      |

|             | A.1.3 Pins                                                      |      |

|             |                                                                 |      |

MC9S12G Family Reference Manual Rev.1.27

### 1.3.8 System Integrity Support

- Power-on reset (POR)

- System reset generation

- Illegal address detection with reset

- Low-voltage detection with interrupt or reset

- Real time interrupt (RTI)

- Computer operating properly (COP) watchdog

- Configurable as window COP for enhanced failure detection

- Initialized out of reset using option bits located in flash memory

- Clock monitor supervising the correct function of the oscillator

### 1.3.9 Timer (TIM)

- Up to eight x 16-bit channels for input capture or output compare

- 16-bit free-running counter with 7-bit precision prescaler

- In case of eight channel timer Version an additional 16-bit pulse accumulator is available

### 1.3.10 Pulse Width Modulation Module (PWM)

- Up to eight channel x 8-bit or up to four channel x 16-bit pulse width modulator

- Programmable period and duty cycle per channel

- Center-aligned or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

# 1.3.11 Controller Area Network Module (MSCAN)

- 1 Mbit per second, CAN 2.0 A, B software compatible

- Standard and extended data frames

- 0–8 bytes data length

- Programmable bit rate up to 1 Mbps

- Five receive buffers with FIFO storage scheme

- Three transmit buffers with internal prioritization

- Flexible identifier acceptance filter programmable as:

- 2 x 32-bit

- 4 x 16-bit

- 8 x 8-bit

- Wakeup with integrated low pass filter option

- Loop back for self test

- Listen-only mode to monitor CAN bus

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 35

Table 1-27. 64-Pin LQFP Pinout for S12G192 and S12G240

|             |       | <lowest< th=""><th>Function<br/>-PRIORITY-</th><th>highest</th><th>&gt;</th><th>Power</th><th colspan="4"></th></lowest<> | Function<br>-PRIORITY- | highest     | >           | Power            |               |                |  |  |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|-------------|------------------|---------------|----------------|--|--|

| Package Pin | Pin   | 2nd<br>Func.                                                                                                              | 3rd<br>Func.           | 4th<br>Func | 5th<br>Func | Supply           | CTRL          | Reset<br>State |  |  |

| 28          | PT4   | IOC4                                                                                                                      | _                      | _           | _           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |  |  |

| 29          | PT3   | IOC3                                                                                                                      | _                      | _           | _           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |  |  |

| 30          | PT2   | IOC2                                                                                                                      | _                      | _           | _           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |  |  |

| 31          | PT1   | IOC1                                                                                                                      | ĪRQ                    | _           | _           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |  |  |

| 32          | PT0   | IOC0                                                                                                                      | XIRQ                   | _           | _           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |  |  |

| 33          | PAD0  | KWAD0                                                                                                                     | AN0                    | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |  |  |

| 34          | PAD8  | KWAD8                                                                                                                     | AN8                    | _           | _           | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |  |  |

| 35          | PAD1  | KWAD1                                                                                                                     | AN1                    | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |  |  |

| 36          | PAD9  | KWAD9                                                                                                                     | AN9                    | _           | _           | $V_{DDA}$        | PER0ADPPS0AD  | Disabled       |  |  |

| 37          | PAD2  | KWAD2                                                                                                                     | AN2                    | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |  |  |

| 38          | PAD10 | KWAD10                                                                                                                    | AN10                   | _           | _           | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |  |  |

| 39          | PAD3  | KWAD3                                                                                                                     | AN3                    | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |  |  |

| 40          | PAD11 | KWAD11                                                                                                                    | AN11                   | _           | _           | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |  |  |

| 41          | PAD4  | KWAD4                                                                                                                     | AN4                    | _           | _           | $V_{DDA}$        | PER1AD/PPS1AD | Disabled       |  |  |

| 42          | PAD12 | KWAD12                                                                                                                    | AN12                   | _           | _           | $V_{DDA}$        | PER0AD/PPS0AD | Disabled       |  |  |

| 43          | PAD5  | KWAD5                                                                                                                     | AN5                    |             | _           | $V_{DDA}$        | PER1AD/PPS1AD | Disabled       |  |  |

| 44          | PAD13 | KWAD13                                                                                                                    | AN13                   |             | _           | $V_{DDA}$        | PER0AD/PPS0AD | Disabled       |  |  |

| 45          | PAD6  | KWAD6                                                                                                                     | AN6                    | _           | _           | $V_{DDA}$        | PER1AD/PPS1AD | Disabled       |  |  |

| 46          | PAD14 | KWAD14                                                                                                                    | AN14                   | _           | _           | $V_{DDA}$        | PER0AD/PPS0AD | Disabled       |  |  |

| 47          | PAD7  | KWAD7                                                                                                                     | AN7                    |             | _           | $V_{DDA}$        | PER1AD/PPS1AD | Disabled       |  |  |

| 48          | PAD15 | KWAD15                                                                                                                    | AN15                   |             | _           | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |  |  |

| 49          | VRH   | _                                                                                                                         | _                      | _           | _           | _                | _             | _              |  |  |

| 50          | VDDA  | _                                                                                                                         | _                      | _           | _           | _                | _             | _              |  |  |

| 51          | VSSA  | _                                                                                                                         | _                      | _           | _           | _                | _             | _              |  |  |

| 52          | PS0   | RXD0                                                                                                                      | _                      | _           | _           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |  |

| 53          | PS1   | TXD0                                                                                                                      | _                      | _           | _           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |  |

| 54          | PS2   | RXD1                                                                                                                      | _                      | _           | _           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |  |

| 55          | PS3   | TXD1                                                                                                                      | _                      | _           | _           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |  |

| 56          | PS4   | MISO0                                                                                                                     | _                      | _           | _           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |  |

MC9S12G Family Reference Manual Rev.1.27

Table 1-28. 100-Pin LQFP Pinout for S12G192 and S12G240

|             | < 0   | Fund<br>owestPRIO |              | st>          | Power            | Internal Pull<br>Resistor |                |  |  |

|-------------|-------|-------------------|--------------|--------------|------------------|---------------------------|----------------|--|--|

| Package Pin | Pin   | 2nd<br>Func.      | 3rd<br>Func. | 4th<br>Func. | Supply           | CTRL                      | Reset<br>State |  |  |

| 86          | PS4   | MISO0             | _            | _            | $V_{DDX}$        | PERS/PPSS                 | Up             |  |  |

| 87          | PS5   | MOSI0             | _            | _            | $V_{DDX}$        | PERS/PPSS                 | Up             |  |  |

| 88          | PS6   | SCK0              | _            | _            | $V_{DDX}$        | PERS/PPSS                 | Up             |  |  |

| 89          | PS7   | API_EXTC<br>LK    | SS0          | _            | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |  |

| 90          | VSSX2 | _                 | _            | _            | _                | <del>_</del>              | _              |  |  |

| 91          | VDDX2 | _                 | _            | _            | _                | _                         | _              |  |  |

| 92          | PM0   | RXCAN             | _            | _            | $V_{DDX}$        | PERM/PPSM                 | Disabled       |  |  |

| 93          | PM1   | TXCAN             | _            | _            | $V_{DDX}$        | PERM/PPSM                 | Disabled       |  |  |

| 94          | PD4   | _                 | _            | _            | $V_{DDX}$        | PUCR/PUPDE                | Disabled       |  |  |

| 95          | PD5   | _                 | _            | _            | $V_{DDX}$        | PUCR/PUPDE                | Disabled       |  |  |

| 96          | PD6   | _                 | _            | _            | $V_{DDX}$        | PUCR/PUPDE                | Disabled       |  |  |

| 97          | PD7   | _                 | _            | _            | $V_{DDX}$        | PUCR/PUPDE                | Disabled       |  |  |

| 98          | PM2   | RXD2              | _            | _            | $V_{DDX}$        | PERM/PPSM                 | Disabled       |  |  |

| 99          | PM3   | TXD2              | _            | _            | $V_{DDX}$        | PERM/PPSM                 | Disabled       |  |  |

| 100         | PJ7   | KWJ7              | SS2          | _            | $V_{DDX}$        | PERJ/PPSJ                 | Up             |  |  |

<sup>&</sup>lt;sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

#### Port Integration Module (S12GPIMV1)

This section describes the signals available on each pin.

Although trying to enable multiple signals on a shared pin is not a proper use case in most applications, the resulting pin function will be determined by a predefined priority scheme as defined in 2.2.2 and 2.2.3.

Only enabled signals arbitrate for the pin and the highest priority defines its data direction and output value if used as output. Signals with programmable routing options are assumed to select the appropriate target pin to participate in the arbitration.

The priority is represented for each pin with shared signals from highest to lowest in the following format:

```

SignalA > SignalB > GPO

```

Here SignalA has priority over SignalB and general-purpose output function (GPO; represented by related port data register bit). The general-purpose output is always of lowest priority if no other signal is enabled.

Peripheral input signals on shared pins are always connected monitoring the pin level independent of their use.

**Table 3-2. ACMPC Register Field Descriptions (continued)**

| Field                 | Description                                                                                                                                                                                                                                                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>ACICE            | ACMP Input Capture Enable— Establishes internal link to a timer input capture channel. When enabled, the associated timer pin is disconnected from the timer input. Refer to ACE description to account for initialization delay on this path.                                                                         |

|                       | 0 Timer link disabled<br>1 ACMP output connected to input capture channel 5                                                                                                                                                                                                                                            |

| 4<br>ACDIEN           | ACMP Digital Input Buffer Enable— Enables the input buffers on ACMPP and ACMPM for the pins to be used with digital functions.                                                                                                                                                                                         |

|                       | <b>Note:</b> If this bit is set while simultaneously using the pin as an analog port, there is potentially increased power consumption because the digital input buffer may be in the linear region.                                                                                                                   |

|                       | 0 Input buffers disabled on ACMPP and ACMPM 1 Input buffers enabled on ACMPP and ACMPM                                                                                                                                                                                                                                 |

| 3-2<br>ACMOD<br>[1:0] | ACMP Mode— Selects the type of compare event setting ACIF.                                                                                                                                                                                                                                                             |

|                       | 00 Flag setting disabled 01 Comparator output rising edge 10 Comparator output falling edge 11 Comparator output rising or falling edge                                                                                                                                                                                |

| 0<br>ACE              | ACMP Enable— This bit enables the ACMP module and takes it into normal mode (see Section 3.5, "Modes of Operation"). This bit also connects the related input pins with the module's low pass input filters. When the module is not enabled, it remains in low power shutdown mode.                                    |

|                       | Note: After setting ACE=1 an initialization delay of 63 bus clock cycles must be accounted for. During this time the comparator output path to all subsequent logic (ACO, ACIF, timer link, excl. ACMPO) is held at its current state. When resetting ACE to 0 the current state of the comparator will be maintained. |

|                       | 0 ACMP disabled<br>1 ACMP enabled                                                                                                                                                                                                                                                                                      |

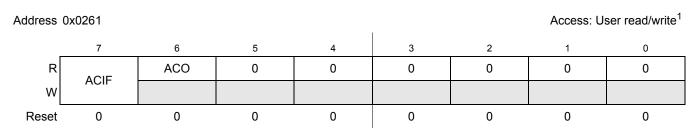

# 3.6.2.2 ACMP Status Register (ACMPS)

Figure 3-4. ACMP Status Register (ACMPS)

ACIF: Anytime, write 1 to clear

ACO: Never

Read: Anytime Write:

Analog-to-Digital Converter (ADC10B12CV2)

### 13.3.2 Register Descriptions

This section describes in address order all the ADC10B12C registers and their individual bits.

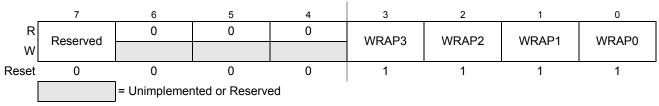

### 13.3.2.1 ATD Control Register 0 (ATDCTL0)

Writes to this register will abort current conversion sequence.

Module Base + 0x0000

Figure 13-3. ATD Control Register 0 (ATDCTL0)

Read: Anytime

Write: Anytime, in special modes always write 0 to Reserved Bit 7.

Table 13-1. ATDCTL0 Field Descriptions

| Field | Description                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                         |

|       | <b>Wrap Around Channel Select Bits</b> — These bits determine the channel for wrap around when doing multi-channel conversions. The coding is summarized in Table 13-2. |

Table 13-2. Multi-Channel Wrap Around Coding

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1) Wraparound to AN0 after Converting |

|-------|-------|-------|-------|----------------------------------------------------------------------------|

| 0     | 0     | 0     | 0     | Reserved <sup>1</sup>                                                      |

| 0     | 0     | 0     | 1     | AN1                                                                        |

| 0     | 0     | 1     | 0     | AN2                                                                        |

| 0     | 0     | 1     | 1     | AN3                                                                        |

| 0     | 1     | 0     | 0     | AN4                                                                        |

| 0     | 1     | 0     | 1     | AN5                                                                        |

| 0     | 1     | 1     | 0     | AN6                                                                        |

| 0     | 1     | 1     | 1     | AN7                                                                        |

| 1     | 0     | 0     | 0     | AN8                                                                        |

| 1     | 0     | 0     | 1     | AN9                                                                        |

| 1     | 0     | 1     | 0     | AN10                                                                       |

| 1     | 0     | 1     | 1     | AN11                                                                       |

| 1     | 1     | 0     | 0     | AN11                                                                       |

| 1     | 1     | 0     | 1     | AN11                                                                       |

| 1     | 1     | 1     | 0     | AN11                                                                       |

| 1     | 1     | 1     | 1     | AN11                                                                       |

MC9S12G Family Reference Manual Rev.1.27

| Address | Name               | _      | Bit 7                                                                                                                                                                                         | 6                                                                                                                             | 5            | 4             | 3               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1       | Bit 0 |

|---------|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|

| 0x0003  | ATDCTL3            | R<br>W | DJM                                                                                                                                                                                           | S8C                                                                                                                           | S4C          | S2C           | S1C             | FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FRZ1    | FRZ0  |

| 0x0004  | ATDCTL4            | R<br>W | SMP2                                                                                                                                                                                          | SMP1                                                                                                                          | SMP0         | PRS[4:0]      |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |

| 0x0005  | ATDCTL5            | R<br>W | 0                                                                                                                                                                                             | SC                                                                                                                            | SCAN         | MULT          | CD              | CC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | СВ      | CA    |

| 0x0006  | ATDSTAT0           | R<br>W | SCF                                                                                                                                                                                           | 0                                                                                                                             | ETORF        | FIFOR         | CC3             | CC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CC1     | CC0   |

| 0x0007  | Unimple-<br>mented | R<br>W | 0                                                                                                                                                                                             | 0                                                                                                                             | 0            | 0             | 0               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0       | 0     |

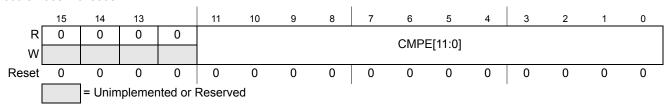

| 0x0008  | ATDCMPEH           | R<br>W | 0                                                                                                                                                                                             | 0                                                                                                                             | 0            | 0             |                 | CMPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [11:8]  |       |

| 0x0009  | ATDCMPEL           | R<br>W |                                                                                                                                                                                               |                                                                                                                               |              | CM            | PE[7:0]         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |

| 0x000A  | ATDSTAT2H          | R<br>W | 0                                                                                                                                                                                             | 0                                                                                                                             | 0            | 0             |                 | CCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | [11:8]  |       |

| 0x000B  | ATDSTAT2L          | R<br>W |                                                                                                                                                                                               |                                                                                                                               |              | CC            | F[7:0]          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |

| 0x000C  | ATDDIENH           | R<br>W | 1                                                                                                                                                                                             | 1                                                                                                                             | 1            | 1             |                 | IEN[                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11:8]   |       |

| 0x000D  | ATDDIENL           | R<br>W |                                                                                                                                                                                               |                                                                                                                               |              | IE            | l<br>N[7:0]     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |

| 0x000E  | ATDCMPHTH          | R<br>W | 0                                                                                                                                                                                             | 0                                                                                                                             | 0            | 0             |                 | СМРН                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T[11:8] |       |

| 0x000F  | ATDCMPHTL          | R<br>W |                                                                                                                                                                                               |                                                                                                                               |              | L<br>CMF      | <br>PHT[7:0]    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |

| 0x0010  | ATDDR0             | R<br>W |                                                                                                                                                                                               |                                                                                                                               |              |               |                 | esult Data (Data ( |         |       |

| 0x0012  | ATDDR1             | R<br>W |                                                                                                                                                                                               | See S                                                                                                                         | Section 14.3 | .2.12.1, "Let | ft Justified Re | esult Data (Data ( | JM=0)"  |       |

| 0x0014  | ATDDR2             | R<br>W |                                                                                                                                                                                               | See S                                                                                                                         | Section 14.3 | .2.12.1, "Let | ft Justified Re | esult Data (Data ( | JM=0)"  |       |

| 0x0016  | ATDDR3             | R<br>W |                                                                                                                                                                                               | See S                                                                                                                         | Section 14.3 | .2.12.1, "Let | ft Justified Re | esult Data (Data ( | JM=0)"  |       |

| 0x0018  | ATDDR4             | R<br>W |                                                                                                                                                                                               | See S                                                                                                                         | Section 14.3 | .2.12.1, "Let | ft Justified Re | esult Data (D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | JM=0)"  |       |

| 0x001A  | ATDDR5             | R<br>W |                                                                                                                                                                                               | and Section 14.3.2.12.2, "Right Justified Result Data (DJM=1)"  See Section 14.3.2.12.1, "Left Justified Result Data (DJM=0)" |              |               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |

| 0x001C  | ATDDR6             | R<br>W | and Section 14.3.2.12.2, "Right Justified Result Data (DJM=1)"  See Section 14.3.2.12.1, "Left Justified Result Data (DJM=0)"  and Section 14.3.2.12.3, "Right Justified Result Data (DJM=1)" |                                                                                                                               |              |               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |

| 0x001E  | ATDDR7             | R<br>W | and Section 14.3.2.12.2, "Right Justified Result Data (DJM=1)"  See Section 14.3.2.12.1, "Left Justified Result Data (DJM=0)"  and Section 14.3.2.12.2, "Pight Justified Result Data (DJM=1)" |                                                                                                                               |              |               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |