Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 12V1                                                        |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 25MHz                                                       |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                              |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 26                                                          |

| Program Memory Size        | 48KB (48K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 1.5K × 8                                                    |

| RAM Size                   | 4K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                |

| Data Converters            | A/D 12x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s12g48f1mlcr |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

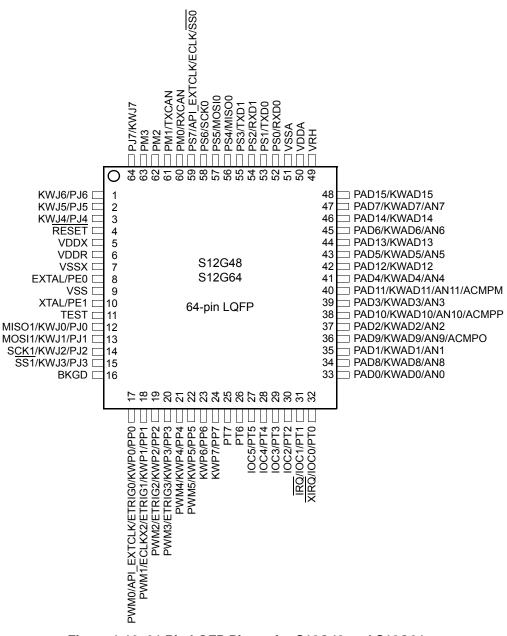

## 1.8.4.3 Pinout 64-Pin LQFP

Figure 1-12. 64-Pin LQFP Pinout for S12G48 and S12G64

|             |                  | <lowest< th=""><th>Function<br/>PRIORITY</th><th>highest&gt;</th><th>&gt;</th><th colspan="4">Internal Pull<br/>Resistor</th></lowest<> | Function<br>PRIORITY | highest>       | >           | Internal Pull<br>Resistor |               |                |  |

|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-------------|---------------------------|---------------|----------------|--|

| Package Pin | Pin              | 2nd<br>Func.                                                                                                                            | 3rd<br>Func.         | 4th<br>Func    | 5th<br>Func | Supply                    | CTRL          | Reset<br>State |  |

| 2           | VDDXR            | _                                                                                                                                       | —                    | _              | _           | —                         | _             | —              |  |

| 3           | VSSX             |                                                                                                                                         | —                    | _              | _           | _                         | —             | _              |  |

| 4           | PE0 <sup>1</sup> | EXTAL                                                                                                                                   | —                    | _              |             | V <sub>DDX</sub>          | PUCR/PDPEE    | Down           |  |

| 5           | VSS              | _                                                                                                                                       | —                    | _              |             | _                         | —             | _              |  |

| 6           | PE1 <sup>1</sup> | XTAL                                                                                                                                    | —                    | _              |             | V <sub>DDX</sub>          | PUCR/PDPEE    | Down           |  |

| 7           | TEST             | _                                                                                                                                       | —                    | —              |             | N.A.                      | RESET pin     | Down           |  |

| 8           | PJ0              | KWJ0                                                                                                                                    | PWM6                 | MISO1          | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |  |

| 9           | PJ1              | KWJ1                                                                                                                                    | IOC6                 | MOSI1          |             | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |  |

| 10          | PJ2              | KWJ2                                                                                                                                    | IOC7                 | SCK1           |             | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |  |

| 11          | PJ3              | KWJ3                                                                                                                                    | PWM7                 | SS1            | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |  |

| 12          | BKGD             | MODC                                                                                                                                    | —                    | —              |             | V <sub>DDX</sub>          | PUCR/BKPUE    | Up             |  |

| 13          | PP0              | KWP0                                                                                                                                    | ETRIG0               | API_EXTC<br>LK | PWM0        | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |  |

| 14          | PP1              | KWP1                                                                                                                                    | ETRIG1               | ECLKX2         | PWM1        | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |  |

| 15          | PP2              | KWP2                                                                                                                                    | ETRIG2               | PWM2           |             | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |  |

| 16          | PP3              | KWP3                                                                                                                                    | ETRIG3               | PWM3           | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |  |

| 17          | PP4              | KWP4                                                                                                                                    | PWM4                 | _              |             | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |  |

| 18          | PP5              | KWP5                                                                                                                                    | PWM5                 | _              |             | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |  |

| 19          | PT5              | IOC5                                                                                                                                    | —                    | _              |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |  |

| 20          | PT4              | IOC4                                                                                                                                    | —                    | _              |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |  |

| 21          | PT3              | IOC3                                                                                                                                    | —                    | _              |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |  |

| 22          | PT2              | IOC2                                                                                                                                    | —                    | _              |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |  |

| 23          | PT1              | IOC1                                                                                                                                    | IRQ                  | —              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |  |

| 24          | PT0              | IOC0                                                                                                                                    | XIRQ                 | _              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |  |

| 25          | PAD0             | KWAD0                                                                                                                                   | AN0                  | —              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |  |

| 26          | PAD8             | KWAD8                                                                                                                                   | AN8                  | _              | _           | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |  |

| 27          | PAD1             | KWAD1                                                                                                                                   | AN1                  | _              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |  |

| 28          | PAD9             | KWAD9                                                                                                                                   | AN9                  |                | _           | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |  |

| 29          | PAD2             | KWAD2                                                                                                                                   | AN2                  | _              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |  |

Table 1-20. 48-Pin LQFP Pinout for S12G96 and S12G128

MC9S12G Family Reference Manual Rev.1.27

|             |                  | <lowest< th=""><th>Function<br/>-PRIORITY-</th><th>highest&gt;</th><th>&gt;</th><th>Power</th><th colspan="3">Internal Pull<br/>Resistor</th></lowest<> | Function<br>-PRIORITY- | highest>       | >           | Power            | Internal Pull<br>Resistor |                |  |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|-------------|------------------|---------------------------|----------------|--|

| Package Pin | Pin              | 2nd<br>Func.                                                                                                                                            | 3rd<br>Func.           | 4th<br>Func    | 5th<br>Func | Supply           | CTRL                      | Reset<br>State |  |

| 1           | PJ6              | KWJ6                                                                                                                                                    | SCK2                   | _              | —           | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 2           | PJ5              | KWJ5                                                                                                                                                    | MOSI2                  | _              | _           | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 3           | PJ4              | KWJ4                                                                                                                                                    | MISO2                  | _              | _           | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 4           | RESET            |                                                                                                                                                         | _                      | _              | _           | V <sub>DDX</sub> | PULLU                     |                |  |

| 5           | VDDX             | _                                                                                                                                                       | —                      | _              | _           |                  | _                         | _              |  |

| 6           | VDDR             | _                                                                                                                                                       | —                      | _              | _           |                  | _                         | _              |  |

| 7           | VSSX             | _                                                                                                                                                       | —                      | _              |             |                  | _                         | _              |  |

| 8           | PE0 <sup>1</sup> | EXTAL                                                                                                                                                   | —                      | _              |             | V <sub>DDX</sub> | PUCR/PDPEE                | Down           |  |

| 9           | VSS              | _                                                                                                                                                       | —                      | _              |             |                  | _                         | _              |  |

| 10          | PE1 <sup>1</sup> | XTAL                                                                                                                                                    | —                      | _              |             | V <sub>DDX</sub> | PUCR/PDPEE                | Down           |  |

| 11          | TEST             | _                                                                                                                                                       | —                      | _              |             | N.A.             | RESET pin                 | Down           |  |

| 12          | PJ0              | KWJ0                                                                                                                                                    | MISO1                  | _              |             | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 13          | PJ1              | KWJ1                                                                                                                                                    | MOSI1                  | _              |             | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 14          | PJ2              | KWJ2                                                                                                                                                    | SCK1                   | _              |             | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 15          | PJ3              | KWJ3                                                                                                                                                    | SS1                    | _              | _           | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 16          | BKGD             | MODC                                                                                                                                                    | —                      | _              |             | V <sub>DDX</sub> | PUCR/BKPUE                | Up             |  |

| 17          | PP0              | KWP0                                                                                                                                                    | ETRIG0                 | API_EXTC<br>LK | PWM0        | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 18          | PP1              | KWP1                                                                                                                                                    | ETRIG1                 | ECLKX2         | PWM1        | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 19          | PP2              | KWP2                                                                                                                                                    | ETRIG2                 | PWM2           |             | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 20          | PP3              | KWP3                                                                                                                                                    | ETRIG3                 | PWM3           |             | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 21          | PP4              | KWP4                                                                                                                                                    | PWM4                   | _              | —           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 22          | PP5              | KWP5                                                                                                                                                    | PWM5                   | _              | _           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 23          | PP6              | KWP6                                                                                                                                                    | PWM6                   | _              | _           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 24          | PP7              | KWP7                                                                                                                                                    | PWM7                   | _              | _           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 25          | PT7              | IOC7                                                                                                                                                    | —                      |                | _           | V <sub>DDX</sub> | PERT/PPST                 | Disabled       |  |

| 26          | PT6              | IOC6                                                                                                                                                    | —                      | _              |             | V <sub>DDX</sub> | PERT/PPST                 | Disabled       |  |

| 27          | PT5              | IOC5                                                                                                                                                    |                        |                | _           | V <sub>DDX</sub> | PERT/PPST                 | Disabled       |  |

MC9S12G Family Reference Manual Rev.1.27

|             | < (   | FunctowestPRIO |              | st>          | Power            | Internal Pull<br>Resistor |                |  |

|-------------|-------|----------------|--------------|--------------|------------------|---------------------------|----------------|--|

| Package Pin | Pin   | 2nd<br>Func.   | 3rd<br>Func. | 4th<br>Func. | Supply           | CTRL                      | Reset<br>State |  |

| 57          | PAD1  | KWAD1          | AN1          | _            | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 58          | PAD9  | KWAD9          | AN9          | _            | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 59          | PAD2  | KWAD2          | AN2          |              | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 60          | PAD10 | KWAD10         | AN10         |              | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 61          | PAD3  | KWAD3          | AN3          |              | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 62          | PAD11 | KWAD11         | AN11         |              | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 63          | PAD4  | KWAD4          | AN4          |              | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 64          | PAD12 | KWAD12         | AN12         | _            | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 65          | PAD5  | KWAD5          | AN5          | _            | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 66          | PAD13 | KWAD13         | AN13         | _            | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 67          | PAD6  | KWAD6          | AN6          |              | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 68          | PAD14 | KWAD14         | AN14         |              | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 69          | PAD7  | KWAD7          | AN7          |              | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |  |

| 70          | PAD15 | KWAD15         | AN15         |              | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |  |

| 71          | PC4   | _              |              |              | V <sub>DDA</sub> | PUCR/PUPCE                | Disabled       |  |

| 72          | PC5   | _              |              |              | V <sub>DDA</sub> | PUCR/PUPCE                | Disabled       |  |

| 73          | PC6   | _              |              |              | V <sub>DDA</sub> | PUCR/PUPCE                | Disabled       |  |

| 74          | PC7   | _              |              |              | V <sub>DDA</sub> | PUCR/PUPCE                | Disabled       |  |

| 75          | VRH   | _              | _            | _            | _                | _                         | _              |  |

| 76          | VDDA  | _              | _            |              | —                | _                         |                |  |

| 77          | VSSA  | _              | _            |              | —                | _                         |                |  |

| 78          | PD0   | _              | _            | _            | V <sub>DDX</sub> | PUCR/PUPDE                | Disabled       |  |

| 79          | PD1   | —              |              | —            | V <sub>DDX</sub> | PUCR/PUPDE                | Disabled       |  |

| 80          | PD2   | _              | _            | _            | V <sub>DDX</sub> | PUCR/PUPDE                | Disabled       |  |

| 81          | PD3   | _              | _            | _            | V <sub>DDX</sub> | PUCR/PUPDE                | Disabled       |  |

| 82          | PS0   | RXD0           | _            | _            | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 83          | PS1   | TXD0           |              | _            | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 84          | PS2   | RXD1           |              |              | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

| 85          | PS3   | TXD1           |              |              | V <sub>DDX</sub> | PERS/PPSS                 | Up             |  |

Table 1-28. 100-Pin LQFP Pinout for S12G192 and S12G240

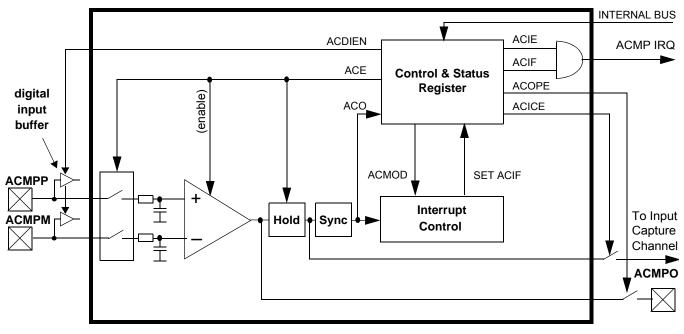

Figure 3-1. ACMP Block Diagram

Figure 3-2.

# 3.4 External Signals

The ACMP has two analog input signals, ACMPP and ACMPM, and one digital output, ACMPO. The associated pins are defined by the package option.

The ACMPP signal is connected to the non-inverting input of the comparator. The ACMPM signal is connected to the inverting input of the comparator. Each of these signals can accept an input voltage that varies across the full 5V operating voltage range. The module monitors the voltage on these inputs independent of any other functions in use (GPIO, ADC).

The raw comparator output signal can optionally be driven on an external pin.

# 3.5 Modes of Operation

1. Normal Mode

The ACMP is operating when enabled and not in STOP mode.

2. Shutdown Mode

The ACMP is held in shutdown mode either when disabled or during STOP mode. In this case the supply of the analog block is disconnected for power saving. ACMPO drives zero in shutdown mode.

# 15.1.2 Modes of Operation

#### 15.1.2.1 Conversion Modes

There is software programmable selection between performing **single** or **continuous conversion** on a **single channel** or **multiple channels**.

## 15.1.2.2 MCU Operating Modes

#### • Stop Mode

Entering Stop Mode aborts any conversion sequence in progress and if a sequence was aborted restarts it after exiting stop mode. This has the same effect/consequences as starting a conversion sequence with write to ATDCTL5. So after exiting from stop mode with a previously aborted sequence all flags are cleared etc.

#### • Wait Mode

ADC10B16C behaves same in Run and Wait Mode. For reduced power consumption continuous conversions should be aborted before entering Wait mode.

#### • Freeze Mode

In Freeze Mode the ADC10B16C will either continue or finish or stop converting according to the FRZ1 and FRZ0 bits. This is useful for debugging and emulation.

#### Analog-to-Digital Converter (ADC12B16CV2)

<sup>1</sup>If only AN0 should be converted use MULT=0.

# 16.3.2.2 ATD Control Register 1 (ATDCTL1)

Writes to this register will abort current conversion sequence.

Module Base + 0x0001

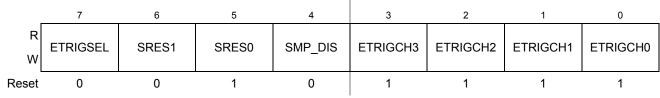

Figure 16-4. ATD Control Register 1 (ATDCTL1)

Read: Anytime

Write: Anytime

| Table 16-3. | ATDCTL1 | Field  | Descriptions |

|-------------|---------|--------|--------------|

|             |         | 1 1010 | Dooonpliono  |

| Field               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ETRIGSEL       | <b>External Trigger Source Select</b> — This bit selects the external trigger source to be either one of the AD channels or one of the ETRIG3-0 inputs. See device specification for availability and connectivity of ETRIG3-0 inputs. If a particular ETRIG3-0 input option is not available, writing a 1 to ETRISEL only sets the bit but has no effect, this means that one of the AD channels (selected by ETRIGCH3-0) is configured as the source for external trigger. The coding is summarized in Table 16-5. |

| 6–5<br>SRES[1:0]    | <b>A/D Resolution Select</b> — These bits select the resolution of A/D conversion results. See Table 16-4 for coding.                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>SMP_DIS        | <ul> <li>Discharge Before Sampling Bit</li> <li>No discharge before sampling.</li> <li>The internal sample capacitor is discharged before sampling the channel. This adds 2 ATD clock cycles to the sampling time. This can help to detect an open circuit instead of measuring the previous sampled channel.</li> </ul>                                                                                                                                                                                             |

| 3–0<br>ETRIGCH[3:0] | <b>External Trigger Channel Select</b> — These bits select one of the AD channels or one of the ETRIG3-0 inputs as source for the external trigger. The coding is summarized in Table 16-5.                                                                                                                                                                                                                                                                                                                          |

| Table | 16-4. | A/D | Resolution | Coding |

|-------|-------|-----|------------|--------|

|-------|-------|-----|------------|--------|

| SRES1 | SRES0 | A/D Resolution |

|-------|-------|----------------|

| 0     | 0     | 8-bit data     |

| 0     | 1     | 10-bit data    |

| 1     | 0     | 12-bit data    |

| 1     | 1     | Reserved       |

| BRP5 | BRP4 | BRP3 | BRP2 | BRP1 | BRP0 | Prescaler value (P) |

|------|------|------|------|------|------|---------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 1                   |

| 0    | 0    | 0    | 0    | 0    | 1    | 2                   |

| 0    | 0    | 0    | 0    | 1    | 0    | 3                   |

| 0    | 0    | 0    | 0    | 1    | 1    | 4                   |

| :    | :    | :    | :    | :    | :    | :                   |

| 1    | 1    | 1    | 1    | 1    | 1    | 64                  |

#### Table 18-7. Baud Rate Prescaler

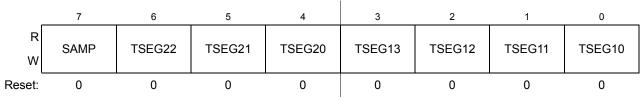

## 18.3.2.4 MSCAN Bus Timing Register 1 (CANBTR1)

The CANBTR1 register configures various CAN bus timing parameters of the MSCAN module.

Module Base + 0x0003

Access: User read/write<sup>1</sup>

Figure 18-7. MSCAN Bus Timing Register 1 (CANBTR1)

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 18-8. CANBTR1 Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SAMP         | <ul> <li>Sampling — This bit determines the number of CAN bus samples taken per bit time.</li> <li>One sample per bit.</li> <li>Three samples per bit<sup>1</sup>.</li> <li>If SAMP = 0, the resulting bit value is equal to the value of the single bit positioned at the sample point. If SAMP = 1, the resulting bit value is determined by using majority rule on the three total samples. For higher bit rates, it is recommended that only one sample is taken per bit time (SAMP = 0).</li> </ul> |

| 6-4<br>TSEG2[2:0] | <b>Time Segment 2</b> — Time segments within the bit time fix the number of clock cycles per bit time and the location of the sample point (see Figure 18-44). Time segment 2 (TSEG2) values are programmable as shown in Table 18-9.                                                                                                                                                                                                                                                                    |

| 3-0<br>TSEG1[3:0] | <b>Time Segment 1</b> — Time segments within the bit time fix the number of clock cycles per bit time and the location of the sample point (see Figure 18-44). Time segment 1 (TSEG1) values are programmable as shown in Table 18-10.                                                                                                                                                                                                                                                                   |

<sup>1</sup> In this case, PHASE\_SEG1 must be at least 2 time quanta (Tq).

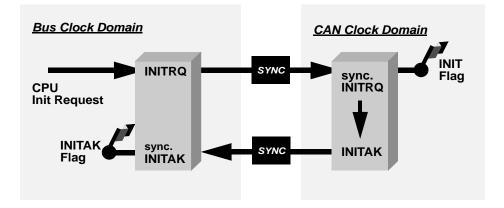

Figure 18-45. Initialization Request/Acknowledge Cycle

Due to independent clock domains within the MSCAN, INITRQ must be synchronized to all domains by using a special handshake mechanism. This handshake causes additional synchronization delay (see Figure 18-45).

If there is no message transfer ongoing on the CAN bus, the minimum delay will be two additional bus clocks and three additional CAN clocks. When all parts of the MSCAN are in initialization mode, the INITAK flag is set. The application software must use INITAK as a handshake indication for the request (INITRQ) to go into initialization mode.

#### NOTE

The CPU cannot clear INITRQ before initialization mode (INITRQ = 1 and INITAK = 1) is active.

## 18.4.5 Low-Power Options

If the MSCAN is disabled (CANE = 0), the MSCAN clocks are stopped for power saving.

If the MSCAN is enabled (CANE = 1), the MSCAN has two additional modes with reduced power consumption, compared to normal mode: sleep and power down mode. In sleep mode, power consumption is reduced by stopping all clocks except those to access the registers from the CPU side. In power down mode, all clocks are stopped and no power is consumed.

Table 18-38 summarizes the combinations of MSCAN and CPU modes. A particular combination of modes is entered by the given settings on the CSWAI and SLPRQ/SLPAK bits.

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>RWU | <ul> <li>Receiver Wakeup Bit — Standby state</li> <li>0 Normal operation.</li> <li>1 RWU enables the wakeup function and inhibits further receiver interrupt requests. Normally, hardware wakes<br/>the receiver by automatically clearing RWU.</li> </ul>                                                                                                                                                                                    |

| 0<br>SBK | <ul> <li>Send Break Bit — Toggling SBK sends one break character (10 or 11 logic 0s, respectively 13 or 14 logics 0s if BRK13 is set). Toggling implies clearing the SBK bit before the break character has finished transmitting. As long as SBK is set, the transmitter continues to send complete break characters (10 or 11 bits, respectively 13 or 14 bits).</li> <li>No break characters</li> <li>Transmit break characters</li> </ul> |

#### Table 20-10. SCICR2 Field Descriptions (continued)

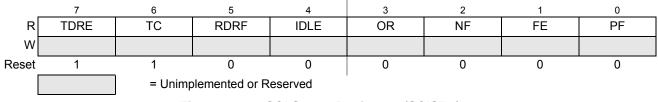

#### 20.3.2.7 SCI Status Register 1 (SCISR1)

The SCISR1 and SCISR2 registers provides inputs to the MCU for generation of SCI interrupts. Also, these registers can be polled by the MCU to check the status of these bits. The flag-clearing procedures require that the status register be read followed by a read or write to the SCI data register. It is permissible to execute other instructions between the two steps as long as it does not compromise the handling of I/O, but the order of operations is important for flag clearing.

Module Base + 0x0004

Figure 20-10. SCI Status Register 1 (SCISR1)

Read: Anytime

Write: Has no meaning or effect

#### Internal Bus $\langle \rangle$ SBR12:SBR0 SCI Data Register Ζ Bus Baud Divider Clock Start Stop 11-Bit Receive Shift Register **RXPOL** Data Н 8 7 6 5 4 3 2 L 1 0 Recovery SCRXD S ₹ Loop Control From TXD Pin MSB RE or Transmitter RAF FE LOOPS Μ RWU NF RSRC WAKE Wakeup ΡE Logic ILT PE R8 Parity Checking PT Idle IRQ IDI F ILIE BRKDFE **RDRF/OR** RDRF IRQ OR RIE Break BRKDIF Detect Logic Break IRQ BRKDIE Active Edge RXEDGIF Detect Logic RX Active Edge IRQ RXEDGIE

# 20.4.6 Receiver

Figure 20-20. SCI Receiver Block Diagram

#### 20.4.6.1 Receiver Character Length

The SCI receiver can accommodate either 8-bit or 9-bit data characters. The state of the M bit in SCI control register 1 (SCICR1) determines the length of data characters. When receiving 9-bit data, bit R8 in SCI data register high (SCIDRH) is the ninth bit (bit 8).

## 20.4.6.2 Character Reception

During an SCI reception, the receive shift register shifts a frame in from the RXD pin. The SCI data register is the read-only buffer between the internal data bus and the receive shift register.

After a complete frame shifts into the receive shift register, the data portion of the frame transfers to the SCI data register. The receive data register full flag, RDRF, in SCI status register 1 (SCISR1) becomes set,

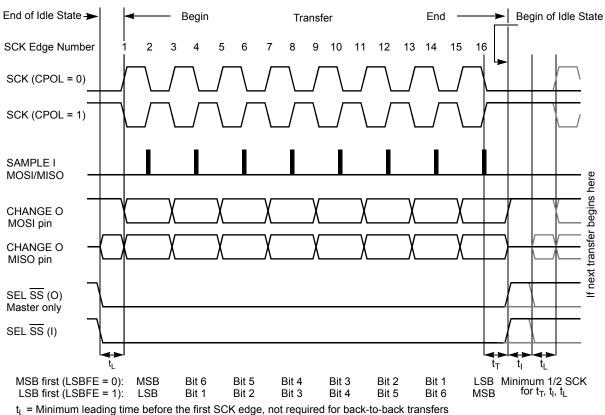

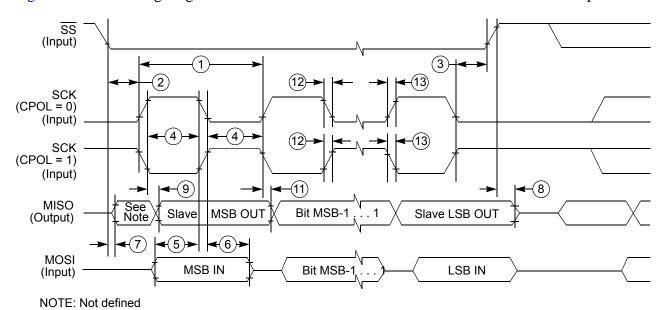

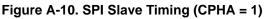

$t_T$  = Minimum trailing time after the last SCK edge

$t_1$  = Minimum idling time between transfers (minimum  $\overline{SS}$  high time), not required for back-to-back transfers

Figure 21-14. SPI Clock Format 1 (CPHA = 1), with 8-Bit Transfer Width selected (XFRW = 0)

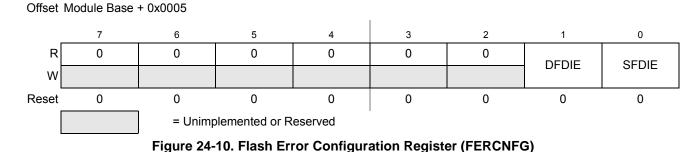

All assigned bits in the FERCNFG register are readable and writable.

#### Table 24-14. FERCNFG Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIE | <ul> <li>Double Bit Fault Detect Interrupt Enable — The DFDIE bit controls interrupt generation when a double bit fault is detected during a Flash block read operation.</li> <li>0 DFDIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the DFDIF flag is set (see Section 24.3.2.8)</li> </ul>                                                       |

| 0<br>SFDIE | <ul> <li>Single Bit Fault Detect Interrupt Enable — The SFDIE bit controls interrupt generation when a single bit fault is detected during a Flash block read operation.</li> <li>0 SFDIF interrupt disabled whenever the SFDIF flag is set (see Section 24.3.2.8)</li> <li>1 An interrupt will be requested whenever the SFDIF flag is set (see Section 24.3.2.8)</li> </ul> |

## 24.3.2.7 Flash Status Register (FSTAT)

The FSTAT register reports the operational status of the Flash module.

Offset Module Base + 0x0006

Figure 24-11. Flash Status Register (FSTAT)

<sup>1</sup> Reset value can deviate from the value shown if a double bit fault is detected during the reset sequence (see Section 24.6).

CCIF, ACCERR, and FPVIOL bits are readable and writable, MGBUSY and MGSTAT bits are readable but not writable, while remaining bits read 0 and are not writable.

| DPS[4:0]                                                                                         | Global Address Range | Protected Size |  |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------------|----------------|--|--|--|--|

| 00000                                                                                            | 0x0_0400 - 0x0_041F  | 32 bytes       |  |  |  |  |

| 00001                                                                                            | 0x0_0400 - 0x0_043F  | 64 bytes       |  |  |  |  |

| 00010                                                                                            | 0x0_0400 – 0x0_045F  | 96 bytes       |  |  |  |  |

| 00011                                                                                            | 0x0_0400 – 0x0_047F  | 128 bytes      |  |  |  |  |

| 00100                                                                                            | 0x0_0400 - 0x0_049F  | 160 bytes      |  |  |  |  |

| 00101                                                                                            | 0x0_0400 – 0x0_04BF  | 192 bytes      |  |  |  |  |

| The Protection Size goes on enlarging in step of 32 bytes, for each DPS value increasing of one. |                      |                |  |  |  |  |

| 01111 - to - 11111                                                                               | 512 bytes            |                |  |  |  |  |

Table 24-21. EEPROM Protection Address Range

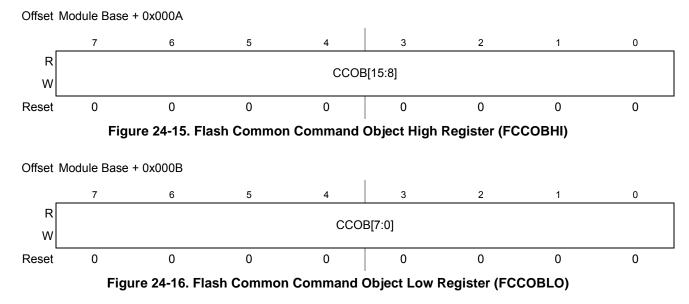

#### 24.3.2.11 Flash Common Command Object Register (FCCOB)

The FCCOB is an array of six words addressed via the CCOBIX index found in the FCCOBIX register. Byte wide reads and writes are allowed to the FCCOB register.

#### 24.3.2.11.1 FCCOB - NVM Command Mode

NVM command mode uses the indexed FCCOB register to provide a command code and its relevant parameters to the Memory Controller. The user first sets up all required FCCOB fields and then initiates

## 26.4.6.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of the P-Flash or EEPROM block.

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the Table 26-57. Set Field Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters      |                                                   |  |  |  |

|-------------|-----------------------|---------------------------------------------------|--|--|--|

| 000         | 0x0E                  | Flash block selection code [1:0]. See Table 26-34 |  |  |  |

| 001         | Margin level setting. |                                                   |  |  |  |

field margin level for the targeted block and then set the CCIF flag.

#### NOTE

When the EEPROM block is targeted, the EEPROM field margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash field margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply field margin levels to the P-Flash block only.

Valid margin level settings for the Set Field Margin Level command are defined in Table 26-58.

| CCOB<br>(CCOBIX=001) | Level Description                 |

|----------------------|-----------------------------------|

| 0x0000               | Return to Normal Level            |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |

Table 26-58. Valid Set Field Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

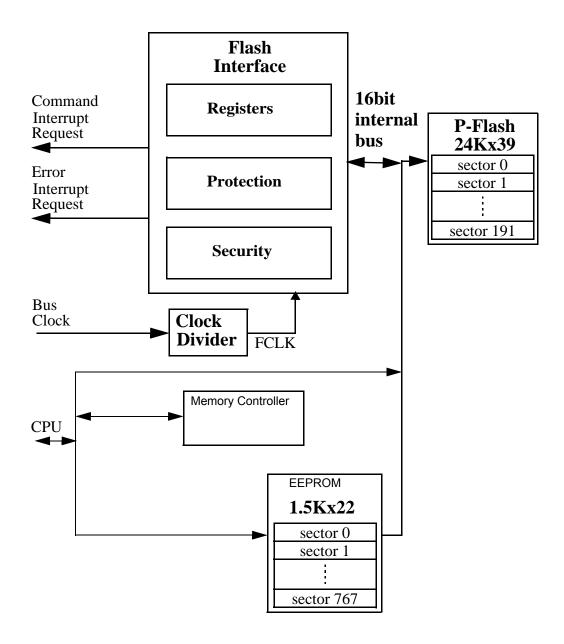

Figure 28-1. FTMRG96K1 Block Diagram

# 28.2 External Signal Description

The Flash module contains no signals that connect off-chip.

8. Reset the MCU

# 29.5.3 Mode and Security Effects on Flash Command Availability

The availability of Flash module commands depends on the MCU operating mode and security state as shown in Table 29-27.

# 29.6 Initialization

On each system reset the flash module executes an initialization sequence which establishes initial values for the Flash Block Configuration Parameters, the FPROT and DFPROT protection registers, and the FOPT and FSEC registers. The initialization routine reverts to built-in default values that leave the module in a fully protected and secured state if errors are encountered during execution of the reset sequence. If a double bit fault is detected during the reset sequence, both MGSTAT bits in the FSTAT register will be set.

CCIF is cleared throughout the initialization sequence. The Flash module holds off all CPU access for a portion of the initialization sequence. Flash reads are allowed once the hold is removed. Completion of the initialization sequence is marked by setting CCIF high which enables user commands.

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

All VDDX pins are internally connected by metal.

All VSSX pins are internally connected by metal.

VDDA, VDDX and VSSA, VSSX are connected by diodes for ESD protection.

#### NOTE

In the following context  $V_{DD35}$  is used for either VDDA, VDDR, and VDDX;  $V_{SS35}$  is used for either VSSA and VSSX unless otherwise noted.

$I_{\text{DD35}}$  denotes the sum of the currents flowing into the VDDA, VDDX and VDDR pins.

## A.1.3 Pins

There are four groups of functional pins.

#### A.1.3.1 I/O Pins

The I/O pins have a level in the range of 3.13V to 5.5V. This class of pins is comprised of all port I/O pins, the analog inputs, BKGD and the RESET pins. Some functionality may be disabled.

#### A.1.3.2 Analog Reference

This group consists of the VRH pin.

#### A.1.3.3 Oscillator

The pins EXTAL, XTAL dedicated to the oscillator have a nominal 1.8V level.

#### A.1.3.4 TEST

This pin is used for production testing only. The TEST pin must be tied to ground in all applications.

## A.1.4 Current Injection

Power supply must maintain regulation within operating  $V_{DD35}$  or  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD35}$ ) is greater than  $I_{DD35}$ , the injection current may flow out of  $V_{DD35}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD35}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power; e.g., if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

## A.1.5 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only. A functional operation under or outside those maxima is not guaranteed. Stress beyond those limits may affect the reliability or cause permanent damage of the device.

In Figure A-10 the timing diagram for slave mode with transmission format CPHA = 1 is depicted.

## 0x00A0-0x0C7 Pulse-Width-Modulator (PWM)

| Address            | Name     |             | Bit 7      | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0      |

|--------------------|----------|-------------|------------|---------|---------|---------|---------|---------|---------|------------|

| 0x00A0             | PWME     | R<br>W      | PWME7      | PWME6   | PWME5   | PWME4   | PWME3   | PWME2   | PWME1   | PWME0      |

| 0x00A1             | PWMPOL   | R<br>W      | PPOL7      | PPOL6   | PPOL5   | PPOL4   | PPOL3   | PPOL2   | PPOL1   | PPOL0      |

| 0x00A2             | PWMCLK   | R<br>W      | PCLK7      | PCLKL6  | PCLK5   | PCLK4   | PCLK3   | PCLK2   | PCLK1   | PCLK0      |

| 0x00A3             | PWMPRCLK | R<br>W      | 0          | PCKB2   | PCKB1   | PCKB0   | 0       | PCKA2   | PCKA1   | PCKA0      |

| 0x00A4             | PWMCAE   | R<br>W      | CAE7       | CAE6    | CAE5    | CAE4    | CAE3    | CAE2    | CAE1    | CAE0       |

| 0x00A5             | PWMCTL   | R<br>W      | CON67      | CON45   | CON23   | CON01   | PSWAI   | PFRZ    | 0       | 0          |

| 0x00A6             | PWMCLKAB | R<br>W      | PCLKAB7    | PCLKAB6 | PCLKAB5 | PCLKAB4 | PCLKAB3 | PCLKAB2 | PCLKAB1 | PCLKAB0    |

| 0x00A7             | Reserved | R<br>W      | 0          | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

| 0x00A8             | PWMSCLA  | R<br>W      | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

| 0x00A9             | PWMSCLB  | R<br>W      | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

| 0x00AA -<br>0x00AB | Reserved | R<br>W      | 0          | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

| 0x00AC             | PWMCNT0  | R<br>W      | Bit 7<br>0 | 6<br>0  | 5<br>0  | 4<br>0  | 3<br>0  | 2<br>0  | 1<br>0  | Bit 0<br>0 |

|                    |          | R           | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

| 0x00AD             | PWMCNT1  | W           | 0          | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

| 0x00AE             | PWMCNT2  | R           | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

| UXUUAL             | PWWCNTZ  | W           | 0          | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

| 0x00AF             | PWMCNT3  | R           | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

| 0/00/1             |          | W           | 0          | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

| 0x0B0              | PWMCNT4  | R           | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

|                    | _        | W           | 0          | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

| 0x00B1             | PWMCNT5  | R           | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

|                    |          | W           |            | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

| 0x00B2             | PWMCNT6  | R           | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

|                    |          | W           | 0          | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

| 0x00B3             | PWMCNT7  | R           | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

| 0x00B4             | PWMPER0  | W<br>R<br>W | 0<br>Bit 7 | 0       | 0<br>5  | 0       | 0<br>3  | 0       | 0       | 0<br>Bit 0 |

| 0x00B5             | PWMPER1  | R<br>W      | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

| 0x00B6             | PWMPER2  | R<br>W      | Bit 7      | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0      |

MC9S12G Family Reference Manual Rev.1.27