Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 12V1                                                                  |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 40                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g64f0clf |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |       | <lowest< th=""><th>Function</th><th>highest</th><th>&gt;</th><th>Power</th><th colspan="3"></th></lowest<> | Function     | highest     | >           | Power            |               |                |  |

|-------------|-------|------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------|------------------|---------------|----------------|--|

| Package Pin | Pin   | 2nd<br>Func.                                                                                               | 3rd<br>Func. | 4th<br>Func | 5th<br>Func | Supply           | CTRL          | Reset<br>State |  |

| 30          | PAD10 | KWAD10                                                                                                     | AN10         | —           | —           | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |  |

| 31          | PAD3  | KWAD3                                                                                                      | AN3          |             | —           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |  |

| 32          | PAD11 | KWAD11                                                                                                     | AN11         | _           | —           | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |  |

| 33          | PAD4  | KWAD4                                                                                                      | AN4          | _           | —           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |  |

| 34          | PAD5  | KWAD5                                                                                                      | AN5          |             | _           | V <sub>DDA</sub> | PER1AD/PPS0AD | Disabled       |  |

| 35          | PAD6  | KWAD6                                                                                                      | AN6          |             | _           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |  |

| 36          | PAD7  | KWAD7                                                                                                      | AN7          | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disable        |  |

| 37          | VDDA  | VRH                                                                                                        | _            | _           | —           | _                | —             | _              |  |

| 38          | VSSA  | _                                                                                                          | _            | _           | _           | _                | —             | _              |  |

| 39          | PS0   | RXD0                                                                                                       | _            | _           | _           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |

| 40          | PS1   | TXD0                                                                                                       | _            | _           | —           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |

| 41          | PS2   | RXD1                                                                                                       | _            | _           | _           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |

| 42          | PS3   | TXD1                                                                                                       | _            | _           | _           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |

| 43          | PS4   | MISO0                                                                                                      | —            | —           | —           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |

| 44          | PS5   | MOSI0                                                                                                      | —            | —           | │ —         | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |

| 45          | PS6   | SCK0                                                                                                       | _            | _           | —           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |

| 46          | PS7   | API_EXTC<br>LK                                                                                             | ECLK         | <u>SS0</u>  | _           | V <sub>DDX</sub> | PERS/PPSS     | Up             |  |

| 47          | PM0   | RXD2                                                                                                       | RXCAN        | —           | │ —         | V <sub>DDX</sub> | PERM/PPSM     | Disabled       |  |

| 48          | PM1   | TXD2                                                                                                       | TXCAN        | _           | _           | V <sub>DDX</sub> | PERM/PPSM     | Disabled       |  |

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

# 1.8.9.4 Known Good Die Option (KGD)

|                      | <                | Func<br>owestPRIO |              | st>          | Power            | Internal Pull<br>Resistor |                |

|----------------------|------------------|-------------------|--------------|--------------|------------------|---------------------------|----------------|

| Wire Bond<br>Die Pad | Pin              | 2nd<br>Func.      | 3rd<br>Func. | 4th<br>Func. | Supply           | CTRL                      | Reset<br>State |

| 1                    | PJ6              | KWJ6              | SCK2         | _            | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

| 2                    | PJ5              | KWJ5              | MOSI2        | —            | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

| 3                    | PJ4              | KWJ4              | MISO2        | —            | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

| 4                    | PA0              | —                 | _            | —            | V <sub>DDX</sub> | PUCR/PUPAE                | Disabled       |

| 5                    | PA1              | _                 |              | _            | V <sub>DDX</sub> | PUCR/PUPAE                | Disabled       |

| 6                    | PA2              | _                 | _            | —            | V <sub>DDX</sub> | PUCR/PUPAE                | Disabled       |

| 7                    | PA3              | _                 |              | _            | V <sub>DDX</sub> | PUCR/PUPAE                | Disabled       |

| 8                    | RESET            | _                 | _            | —            | V <sub>DDX</sub> | PULLU                     | P              |

| 9                    | VDDX1            | _                 | _            | —            | _                | _                         | _              |

| 10                   | VDDR             | _                 |              | _            | _                | _                         | _              |

| 11                   | VSSX1            | _                 | _            | —            | _                | _                         | _              |

| 12                   | PE0 <sup>1</sup> | EXTAL             | _            | —            | V <sub>DDX</sub> | PUCR/PDPEE                | Down           |

| 13                   | VSS              | _                 | _            | —            | _                | _                         | _              |

| 14                   | PE1 <sup>1</sup> | XTAL              | _            | —            | V <sub>DDX</sub> | PUCR/PDPEE                | Down           |

| 15                   | TEST             | _                 |              | _            | N.A.             | RESET pin                 | Down           |

| 16                   | PA4              | _                 |              | _            | V <sub>DDX</sub> | PUCR/PUPAE                | Disabled       |

| 17                   | PA5              | _                 |              | _            | V <sub>DDX</sub> | PUCR/PUPAE                | Disabled       |

| 18                   | PA6              | _                 | _            | —            | V <sub>DDX</sub> | PUCR/PUPAE                | Disabled       |

| 19                   | PA7              | _                 |              | _            | V <sub>DDX</sub> | PUCR/PUPAE                | Disabled       |

| 20                   | PJ0              | KWJ0              | MISO1        | —            | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

| 21                   | PJ1              | KWJ1              | MOSI1        | _            | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

| 22                   | PJ2              | KWJ2              | SCK1         | _            | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

| 23                   | PJ3              | KWJ3              | SS1          | _            | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

| 24                   | BKGD             | MODC              |              | _            | V <sub>DDX</sub> | PUCR/BKPUE                | Up             |

| 25                   | PB0              | ECLK              |              | _            | V <sub>DDX</sub> | PUCR/PUPBE                | Disabled       |

| 26                   | PB1              | API_EXTC<br>LK    |              | —            | V <sub>DDX</sub> | PUCR/PUPBE                | Disabled       |

Table 1-32. KGD Option for S12GA192 and S12GA240

# 1.17 ADC Result Reference

MCUs of the S12G-Family are able to measure the internal reference voltage  $V_{DDF}$  (see Table 1-38).  $V_{DDF}$  is a constant voltage with a narrow distribution over temperature and external voltage supply (see Table A-47).

A 12-bit left justified<sup>1</sup> ADC conversion result of  $V_{DDF}$  is provided at address  $0x0_4022/0x0_4023$  in the NVM's IFR for reference. The measurement conditions of the reference conversion are listed in Section A.16, "ADC Conversion Result Reference". By measuring the voltage  $V_{DDF}$  (see Table 1-38) and comparing the result to the reference value in the IFR, it is possible to determine the ADC's reference voltage  $V_{RH}$  in the application environment:

$V_{RH} = \frac{StoredReference}{ConvertedReference} \bullet 5V$

The exact absolute value of an analog conversion can be determined as follows:

$Result = ConvertedADInput \bullet \frac{StoredReference \bullet 5V}{ConvertedReference \bullet 2^{n}}$

With:

ConvertedADInput:Result of the analog to digital conversion of the desired pinConvertedReference:Result of channel "Internal\_0" conversionStoredReference:Value in IFR locatio 0x0\_4022/0x0\_4023n:ADC resolution (10 bit)

### **CAUTION**

To assure high accuracy of the  $V_{DDF}$  reference conversion, the NVMs must not be programmed, erased, or read while the conversion takes place. This implies that code must be executed from RAM. The "ConvertedReference" value must be the average of eight consecutive conversions.

## CAUTION

The ADC's reference voltage  $V_{RH}$  must remain at a constant level throughout the conversion process.

# 1.18 ADC VRH/VRL Signal Connection

On all S12G devices except for the S12GA192 and the S12GA240 the external VRH signal is directly connected to the ADC's VRH signal input. The ADC's VRL input is connected to VSSA. (see Figure 1-27).

1. The format of the stored  $\mathsf{V}_{\mathsf{DDF}}$  reference value is still subject to change.

PJ1

| Table 2-15. Fort 5 Fills F57-0 (continued)                                                          |

|-----------------------------------------------------------------------------------------------------|

| • Except 20 TSSOP and 32 LQFP: The SPI1 MOSI signal is mapped to this pin when used with the SPI    |

| function. Depending on the configuration of the enabled SPI1 the I/O state is forced to be input or |

|     | <ul> <li>function. Depending on the configuration of the enabled SPI1 the I/O state is forced to be input or output.</li> <li>48 LQFP: The TIM channel 6 signal is mapped to this pin when used with the timer function. The TIM forces the I/O state to be an output for a timer port associated with an enabled output.</li> <li>Except 20 TSSOP and 32 LQFP: Pin interrupts can be generated if enabled in input or output mode.</li> <li>Signal priority: <ul> <li>48 LQFP: MOSI1 &gt; IOC6 &gt; GPO</li> <li>64/100 LQFP: MOSI1 &gt; GPO</li> </ul> </li> </ul>                                     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PJ0 | <ul> <li>Except 20 TSSOP and 32 LQFP: The SPI1 MISO signal is mapped to this pin when used with the SPI function. Depending on the configuration of the enabled SPI1 the I/O state is forced to be input or output.</li> <li>48 LQFP: The PWM channel 6 signal is mapped to this pin when used with the PWM function. The enabled PWM channel forces the I/O state to be an output.</li> <li>Except 20 TSSOP and 32 LQFP: Pin interrupts can be generated if enabled in input or output mode.</li> <li>Signal priority:<br/>48 LQFP: MISO1 &gt; PWM6 &gt; GPO<br/>64/100 LQFP: MISO1 &gt; GPO</li> </ul> |

### Table 2-15. Port J Pins PJ7-0 (continued)

# 2.3.12 Pins AD15-0

### NOTE

The following sources contribute to enable the input buffers on port AD:

- Digital input enable register bits set for each individual pin in ADC

- External trigger function of ADC enabled on ADC channel

- ADC channels routed to port C freeing up pins

- Digital input enable register set bit in and ACMP

Taking the availability of the different sources on each pin into account the following logic equation must be true to activate the digital input buffer for general-purpose input use:

### IBEx = ( (ATDDIENH/L[IENx]=1) OR (ATDCTL1[ETRIGSEL]=0 AND ATDCTL2[ETRIGE]=1) OR (PRR1[PRR1AN]=1) ) AND (ACDIEN=1) Eqn. 2-1

| Field      | Description                                                                                                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>PUPCE | <b>Port C Pullup Enable</b> —Enable pullup devices on all port input pins<br>This bit configures whether a pullup device is activated on all associated port input pins. If a pin is used as output<br>this bit has no effect. |

|            | 1 Pullup devices enabled<br>0 Pullup devices disabled                                                                                                                                                                          |

| 1<br>PUPBE | <b>Port B Pullup Enable</b> —Enable pullup devices on all port input pins<br>This bit configures whether a pullup device is activated on all associated port input pins. If a pin is used as output<br>this bit has no effect. |

|            | 1 Pullup devices enabled<br>0 Pullup devices disabled                                                                                                                                                                          |

| 0<br>PUPAE | <b>Port A Pullup Enable</b> —Enable pullup devices on all port input pins<br>This bit configures whether a pullup device is activated on all associated port input pins. If a pin is used as output<br>this bit has no effect. |

|            | 1 Pullup devices enabled<br>0 Pullup devices disabled                                                                                                                                                                          |

### Table 2-32. PUCR Register Field Descriptions (continued)

#### Interrupt Module (S12SINTV1)

- 2-58 I bit maskable interrupt vector requests (at addresses vector base + 0x0082-0x00F2).

- I bit maskable interrupts can be nested.

- One X bit maskable interrupt vector request (at address vector base + 0x00F4).

- One non-maskable software interrupt request (SWI) or background debug mode vector request (at address vector base + 0x00F6).

- One non-maskable unimplemented op-code trap (TRAP) vector (at address vector base + 0x00F8).

- Three system reset vectors (at addresses 0xFFFA–0xFFFE).

- Determines the highest priority interrupt vector requests, drives the vector to the bus on CPU request

- Wakes up the system from stop or wait mode when an appropriate interrupt request occurs.

## 6.1.3 Modes of Operation

• Run mode

This is the basic mode of operation.

• Wait mode

In wait mode, the clock to the INT module is disabled. The INT module is however capable of waking-up the CPU from wait mode if an interrupt occurs. Please refer to Section 6.5.3, "Wake Up from Stop or Wait Mode" for details.

• Stop Mode

In stop mode, the clock to the INT module is disabled. The INT module is however capable of waking-up the CPU from stop mode if an interrupt occurs. Please refer to Section 6.5.3, "Wake Up from Stop or Wait Mode" for details.

• Freeze mode (BDM active)

In freeze mode (BDM active), the interrupt vector base register is overridden internally. Please refer to Section 6.3.1.1, "Interrupt Vector Base Register (IVBR)" for details.

## 6.1.4 Block Diagram

Figure 6-1 shows a block diagram of the INT module.

<sup>1.</sup> The vector base is a 16-bit address which is accumulated from the contents of the interrupt vector base register (IVBR, used as upper byte) and 0x00 (used as lower byte).

| COMRV | Visible State Control Register |

|-------|--------------------------------|

| 01    | DBGSCR2                        |

| 10    | DBGSCR3                        |

| 11    | DBGMFR                         |

Table 8-14. State Control Register Access Encoding

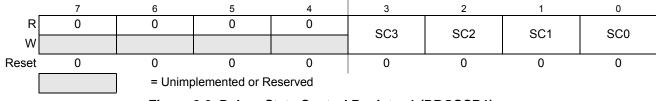

## 8.3.2.7.1 Debug State Control Register 1 (DBGSCR1)

Address: 0x0027

### Figure 8-9. Debug State Control Register 1 (DBGSCR1)

Read: If COMRV[1:0] = 00

Write: If COMRV[1:0] = 00 and DBG is not armed.

This register is visible at 0x0027 only with COMRV[1:0] = 00. The state control register 1 selects the targeted next state whilst in State1. The matches refer to the match channels of the comparator match control logic as depicted in Figure 8-1 and described in Section 8.3.2.8.1, "Debug Comparator Control Register (DBGXCTL). Comparators must be enabled by setting the comparator enable bit in the associated DBGXCTL control register.

| Field          | Description                                                                             |

|----------------|-----------------------------------------------------------------------------------------|

| 3–0<br>SC[3:0] | These bits select the targeted next state whilst in State1, based upon the match event. |

### Table 8-16. State1 Sequencer Next State Selection

| SC[3:0] | Description (Unspecified matches have no effect) |  |

|---------|--------------------------------------------------|--|

| 0000    | Any match to Final State                         |  |

| 0001    | Match1 to State3                                 |  |

| 0010    | Match2 to State2                                 |  |

| 0011    | Match1 to State2                                 |  |

| 0100    | Match0 to State2 Match1 to State3                |  |

| 0101    | Match1 to State3Match0 to Final State            |  |

| 0110    | Match0 to State2 Match2 to State3                |  |

| 0111    | Either Match0 or Match1 to State2                |  |

| 1000    | Reserved                                         |  |

| 1001    | Match0 to State3                                 |  |

### Table 10-3. CPMUFLG Field Descriptions (continued)

| Field      | Description                                                                                                                                                                                                                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>OSCIF | <ul> <li>Oscillator Interrupt Flag — OSCIF is set to 1 when UPOSC status bit changes. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (OSCIE=1), OSCIF causes an interrupt request.</li> <li>0 No change in UPOSC bit.</li> <li>1 UPOSC bit has changed.</li> </ul>                                              |

| 0<br>UPOSC | <ul> <li>Oscillator Status Bit — UPOSC reflects the status of the oscillator. Writes have no effect. While UPOSC=0 the OSCCLK going to the MSCAN module is off. Entering Full Stop Mode UPOSC is cleared.</li> <li>0 The oscillator is off or oscillation is not qualified by the PLL.</li> <li>1 The oscillator is qualified by the PLL.</li> </ul> |

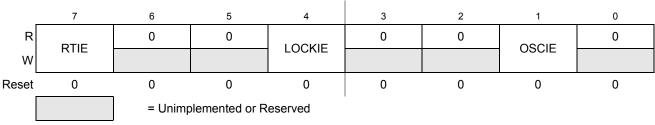

## 10.3.2.5 S12CPMU Interrupt Enable Register (CPMUINT)

This register enables S12CPMU interrupt requests.

0x0038

Read: Anytime

Write: Anytime

| Field       | Description                                                                                                                                                       |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7<br>RTIE   | Real Time Interrupt Enable Bit         0 Interrupt requests from RTI are disabled.         1 Interrupt will be requested whenever RTIF is set.                    |  |  |  |

| 4<br>LOCKIE | <ul><li>PLL Lock Interrupt Enable Bit</li><li>0 PLL LOCK interrupt requests are disabled.</li><li>1 Interrupt will be requested whenever LOCKIF is set.</li></ul> |  |  |  |

| 1<br>OSCIE  | Oscillator Corrupt Interrupt Enable Bit<br>0 Oscillator Corrupt interrupt requests are disabled.<br>1 Interrupt will be requested whenever OSCIF is set.          |  |  |  |

## 10.3.2.6 S12CPMU Clock Select Register (CPMUCLKS)

This register controls S12CPMU clock selection.

## 11.3.2 Register Descriptions

This section describes in address order all the ADC10B8C registers and their individual bits.

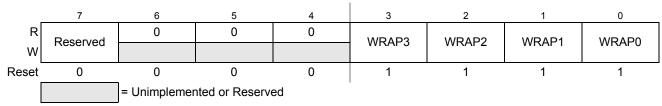

## 11.3.2.1 ATD Control Register 0 (ATDCTL0)

Writes to this register will abort current conversion sequence.

Module Base + 0x0000

### Figure 11-3. ATD Control Register 0 (ATDCTL0)

### Read: Anytime

Write: Anytime, in special modes always write 0 to Reserved Bit 7.

| Field            | Description                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                                                                         |

| 3-0<br>WRAP[3-0] | <b>Wrap Around Channel Select Bits</b> — These bits determine the channel for wrap around when doing multi-channel conversions. The coding is summarized in Table 11-2. |

### Table 11-2. Multi-Channel Wrap Around Coding

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1)<br>Wraparound to AN0 after Converting |

|-------|-------|-------|-------|-------------------------------------------------------------------------------|

| 0     | 0     | 0     | 0     | Reserved <sup>1</sup>                                                         |

| 0     | 0     | 0     | 1     | AN1                                                                           |

| 0     | 0     | 1     | 0     | AN2                                                                           |

| 0     | 0     | 1     | 1     | AN3                                                                           |

| 0     | 1     | 0     | 0     | AN4                                                                           |

| 0     | 1     | 0     | 1     | AN5                                                                           |

| 0     | 1     | 1     | 0     | AN6                                                                           |

| 0     | 1     | 1     | 1     | AN7                                                                           |

| 1     | 0     | 0     | 0     | AN7                                                                           |

| 1     | 0     | 0     | 1     | AN7                                                                           |

| 1     | 0     | 1     | 0     | AN7                                                                           |

| 1     | 0     | 1     | 1     | AN7                                                                           |

| 1     | 1     | 0     | 0     | AN7                                                                           |

| 1     | 1     | 0     | 1     | AN7                                                                           |

| 1     | 1     | 1     | 0     | AN7                                                                           |

| 1     | 1     | 1     | 1     | AN7                                                                           |

MC9S12G Family Reference Manual Rev.1.27

# 18.5 Initialization/Application Information

# 18.5.1 MSCAN initialization

The procedure to initially start up the MSCAN module out of reset is as follows:

- 1. Assert CANE

- 2. Write to the configuration registers in initialization mode

- 3. Clear INITRQ to leave initialization mode

If the configuration of registers which are only writable in initialization mode shall be changed:

- 1. Bring the module into sleep mode by setting SLPRQ and awaiting SLPAK to assert after the CAN bus becomes idle.

- 2. Enter initialization mode: assert INITRQ and await INITAK

- 3. Write to the configuration registers in initialization mode

- 4. Clear INITRQ to leave initialization mode and continue

# 18.5.2 Bus-Off Recovery

The bus-off recovery is user configurable. The bus-off state can either be left automatically or on user request.

For reasons of backwards compatibility, the MSCAN defaults to automatic recovery after reset. In this case, the MSCAN will become error active again after counting 128 occurrences of 11 consecutive recessive bits on the CAN bus (see the Bosch CAN 2.0 A/B specification for details).

If the MSCAN is configured for user request (BORM set in MSCAN Control Register 1 (CANCTL1)), the recovery from bus-off starts after both independent events have become true:

- 128 occurrences of 11 consecutive recessive bits on the CAN bus have been monitored

- BOHOLD in MSCAN Miscellaneous Register (CANMISC) has been cleared by the user

These two events may occur in any order.

### Table 19-10. PWMCTL Field Descriptions

Note: Bits related to available channels have functional significance. Writing to unavailable bits has no effect. Read from unavailable bits return a zero

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CON67 | <ul> <li>Concatenate Channels 6 and 7</li> <li>Channels 6 and 7 are separate 8-bit PWMs.</li> <li>Channels 6 and 7 are concatenated to create one 16-bit PWM channel. Channel 6 becomes the high order byte and channel 7 becomes the low order byte. Channel 7 output pin is used as the output for this 16-bit PWM (bit 7 of port PWMP). Channel 7 clock select control-bit determines the clock source, channel 7 polarity bit determines the polarity, channel 7 enable bit enables the output and channel 7 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| 6<br>CON45 | <ul> <li>Concatenate Channels 4 and 5</li> <li>Channels 4 and 5 are separate 8-bit PWMs.</li> <li>Channels 4 and 5 are concatenated to create one 16-bit PWM channel. Channel 4 becomes the high order byte and channel 5 becomes the low order byte. Channel 5 output pin is used as the output for this 16-bit PWM (bit 5 of port PWMP). Channel 5 clock select control-bit determines the clock source, channel 5 polarity bit determines the polarity, channel 5 enable bit enables the output and channel 5 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| 5<br>CON23 | <ul> <li>Concatenate Channels 2 and 3</li> <li>Channels 2 and 3 are separate 8-bit PWMs.</li> <li>Channels 2 and 3 are concatenated to create one 16-bit PWM channel. Channel 2 becomes the high order byte and channel 3 becomes the low order byte. Channel 3 output pin is used as the output for this 16-bit PWM (bit 3 of port PWMP). Channel 3 clock select control-bit determines the clock source, channel 3 polarity bit determines the polarity, channel 3 enable bit enables the output and channel 3 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| 4<br>CON01 | <ul> <li>Concatenate Channels 0 and 1</li> <li>Channels 0 and 1 are separate 8-bit PWMs.</li> <li>Channels 0 and 1 are concatenated to create one 16-bit PWM channel. Channel 0 becomes the high order byte and channel 1 becomes the low order byte. Channel 1 output pin is used as the output for this 16-bit PWM (bit 1 of port PWMP). Channel 1 clock select control-bit determines the clock source, channel 1 polarity bit determines the polarity, channel 1 enable bit enables the output and channel 1 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| 3<br>PSWAI | <ul> <li>PWM Stops in Wait Mode — Enabling this bit allows for lower power consumption in wait mode by disabling the input clock to the prescaler.</li> <li>0 Allow the clock to the prescaler to continue while in wait mode.</li> <li>1 Stop the input clock to the prescaler whenever the MCU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2<br>PFRZ  | <ul> <li>PWM Counters Stop in Freeze Mode — In freeze mode, there is an option to disable the input clock to the prescaler by setting the PFRZ bit in the PWMCTL register. If this bit is set, whenever the MCU is in freeze mode, the input clock to the prescaler is disabled. This feature is useful during emulation as it allows the PWM function to be suspended. In this way, the counters of the PWM can be stopped while in freeze mode so that once normal program flow is continued, the counters are re-enabled to simulate real-time operations. Since the registers can still be accessed in this mode, to re-enable the prescaler clock, either disable the PFRZ bit or exit freeze mode.</li> <li>O Allow PWM to continue while in freeze mode.</li> <li>1 Disable PWM input clock to the prescaler whenever the part is in freeze mode. This is useful for emulation.</li> </ul> |

# 19.3.2.7 PWM Clock A/B Select Register (PWMCLKAB)

Each PWM channel has a choice of four clocks to use as the clock source for that channel as described below.

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 24.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 24.4.6.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0x3\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x3\_FF00-0x3\_FF07 are unaffected by the Verify Backdoor Access Key command sequence. The Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired. In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses 0x3\_FF00-0x3\_FF07 in the Flash configuration field.

# 24.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

A secured MCU can be unsecured in special single chip mode by using the following method to erase the P-Flash and EEPROM memory:

- 1. Reset the MCU into special single chip mode

- 2. Delay while the BDM executes the Erase Verify All Blocks command write sequence to check if the P-Flash and EEPROM memories are erased

- 3. Send BDM commands to disable protection in the P-Flash and EEPROM memory

- 4. Execute the Erase All Blocks command write sequence to erase the P-Flash and EEPROM memory. Alternatively the Unsecure Flash command can be executed, if so the steps 5 and 6 below are skeeped.

- 5. After the CCIF flag sets to indicate that the Erase All Blocks operation has completed, reset the MCU into special single chip mode

- 6. Delay while the BDM executes the Erase Verify All Blocks command write sequence to verify that the P-Flash and EEPROM memory are erased

If the P-Flash and EEPROM memory are verified as erased, the MCU will be unsecured. All BDM commands will now be enabled and the Flash security byte may be programmed to the unsecure state by continuing with the following steps:

7. Send BDM commands to execute the Program P-Flash command write sequence to program the Flash security byte to the unsecured state

MC9S12G Family Reference Manual Rev.1.27

### 32 KByte Flash Module (S12FTMRG32K1V1)

Upon clearing CCIF to launch the Read Once command, a Read Once phrase is fetched and stored in the FCCOB indexed register. The CCIF flag will set after the Read Once operation has completed. Valid phrase index values for the Read Once command range from 0x0000 to 0x0007. During execution of the Read Once command, any attempt to read addresses within P-Flash block will return invalid data.

| Register | Error Bit | Error Condition                                                         |  |

|----------|-----------|-------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                             |  |

|          |           | Set if command not available in current mode (see Table 25-27)          |  |

| FSTAT    |           | Set if an invalid phrase index is supplied                              |  |

| FSTAL    | FPVIOL    | None                                                                    |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |  |

| Table 25-39. Read Once Command Error Handling |

|-----------------------------------------------|

|-----------------------------------------------|

## 25.4.6.5 Program P-Flash Command

The Program P-Flash operation will program a previously erased phrase in the P-Flash memory using an embedded algorithm.

## CAUTION

A P-Flash phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash phrase is not allowed.

Table 25-40. Program P-Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                       |                                                     |  |

|-------------|------------------------------------------------------------------------|-----------------------------------------------------|--|

| 000         | 0x06                                                                   | Global address [17:16] to<br>identify P-Flash block |  |

| 001         | Global address [15:0] of phrase location to be programmed <sup>1</sup> |                                                     |  |

| 010         | Word 0 program value                                                   |                                                     |  |

| 011         | Word 1 program value                                                   |                                                     |  |

| 100         | Word 2 program value                                                   |                                                     |  |

| 101         | Word 3 program value                                                   |                                                     |  |

<sup>1</sup> Global address [2:0] must be 000

Upon clearing CCIF to launch the Program P-Flash command, the Memory Controller will program the data words to the supplied global address and will then proceed to verify the data words read back as expected. The CCIF flag will set after the Program P-Flash operation has completed.

#### 32 KByte Flash Module (S12FTMRG32K1V1)

user-supplied keys match those stored in the Flash security bytes of the Flash configuration field (see Table 25-4). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x0C             | Not required |

| 001         | Ke               | y 0          |

| 010         | Key 1            |              |

| 011         | Key 2            |              |

| 100         | Key 3            |              |

Table 25-52. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

Table 25-53. Verify Backdoor Access Key Command Error Handling

| Register | Error Bit | Error Condition                                                                          |  |

|----------|-----------|------------------------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 100 at command launch                                              |  |

|          |           | Set if an incorrect backdoor key is supplied                                             |  |

|          |           | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 25.3.2.2) |  |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                              |  |

|          | FPVIOL    | None                                                                                     |  |

|          | MGSTAT1   | None                                                                                     |  |

|          | MGSTAT0   | None                                                                                     |  |

## 25.4.6.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

| CCOBIX[2:0] | FCCOB Parameters |                                                   |  |

|-------------|------------------|---------------------------------------------------|--|

| 000         | 0x0D             | Flash block selection code [1:0]. See Table 25-34 |  |

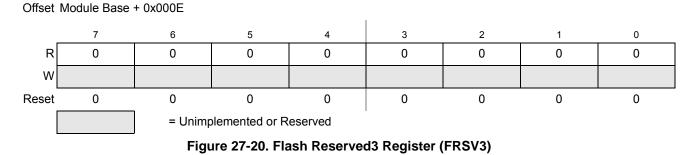

All bits in the FRSV3 register read 0 and are not writable.

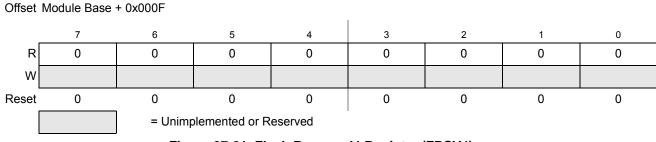

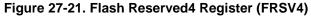

## 27.3.2.15 Flash Reserved4 Register (FRSV4)

This Flash register is reserved for factory testing.

All bits in the FRSV4 register read 0 and are not writable.

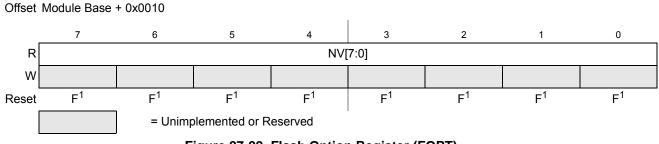

# 27.3.2.16 Flash Option Register (FOPT)

The FOPT register is the Flash option register.

<sup>1</sup> Loaded from IFR Flash configuration field, during reset sequence.

All bits in the FOPT register are readable but are not writable.

During the reset sequence, the FOPT register is loaded from the Flash nonvolatile byte in the Flash configuration field at global address  $0x_3$ \_FF0E located in P-Flash memory (see Table 27-4) as indicated by reset condition F in Figure 27-22. If a double bit fault is detected while reading the P-Flash phrase containing the Flash nonvolatile byte during the reset sequence, all bits in the FOPT register will be set.

#### 64 KByte Flash Module (S12FTMRG64K1V1)

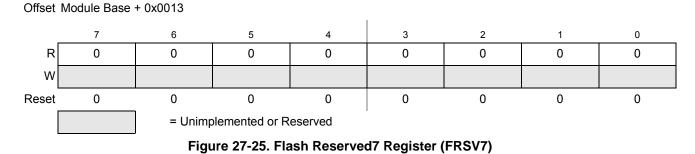

All bits in the FRSV7 register read 0 and are not writable.

# 27.4 Functional Description

## 27.4.1 Modes of Operation

The FTMRG64K1 module provides the modes of operation normal and special . The operating mode is determined by module-level inputs and affects the FCLKDIV, FCNFG, and EEPROT registers (see Table 27-27).

## 27.4.2 IFR Version ID Word

The version ID word is stored in the IFR at address  $0x0_40B6$ . The contents of the word are defined in Table 27-26.

| [15:4]   | [3:0]  |  |  |

|----------|--------|--|--|

| Reserved | VERNUM |  |  |

| Table 27-26 | . IFR \ | Version | ID | Fields |

|-------------|---------|---------|----|--------|

|-------------|---------|---------|----|--------|

| CCOBIX[2:0] | FCCOB Parameters      |                                                        |  |

|-------------|-----------------------|--------------------------------------------------------|--|

| 000         | 0x0D                  | 0x0D Flash block selection code [1:0]. See Table 28-34 |  |

| 001         | Margin level setting. |                                                        |  |

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 28-55.

| Table 28-55. | Valid Set User Margin Level Settings |

|--------------|--------------------------------------|

|              |                                      |

| CCOB<br>(CCOBIX=001) | Level Description                |

|----------------------|----------------------------------|

| 0x0000               | Return to Normal Level           |

| 0x0001               | User Margin-1 Level <sup>1</sup> |

| 0x0002               | User Margin-0 Level <sup>2</sup> |

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

| Register | Error Bit | Error Condition                                                              |  |  |

|----------|-----------|------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                  |  |  |

|          |           | Set if command not available in current mode (see Table 28-27)               |  |  |

|          | ACCERR    | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 28-34) |  |  |

| FSTAT    |           | Set if an invalid margin level setting is supplied                           |  |  |

|          | FPVIOL    | None                                                                         |  |  |

|          | MGSTAT1   | None                                                                         |  |  |

|          | MGSTAT0   | None                                                                         |  |  |

#### 96 KByte Flash Module (S12FTMRG96K1V1)

## 30.4.4.3 Valid Flash Module Commands

Table 30-27 present the valid Flash commands, as enabled by the combination of the functional MCU mode (Normal SingleChip NS, Special Singlechip SS) with the MCU security state (Unsecured, Secured).

Special Singlechip mode is selected by input mmc\_ss\_mode\_ts2 asserted. MCU Secured state is selected by input mmc\_secure input asserted.

| FOMD | Command                      | Unse | Unsecured       |                 | Secured         |  |

|------|------------------------------|------|-----------------|-----------------|-----------------|--|

| FCMD | Command                      |      | SS <sup>2</sup> | NS <sup>3</sup> | SS <sup>4</sup> |  |

| 0x01 | Erase Verify All Blocks      | *    | *               | *               | *               |  |

| 0x02 | Erase Verify Block           | *    | *               | *               | *               |  |

| 0x03 | Erase Verify P-Flash Section | *    | *               | *               |                 |  |

| 0x04 | Read Once                    | * *  |                 | *               |                 |  |

| 0x06 | Program P-Flash              | *    | *               | *               |                 |  |

| 0x07 | Program Once                 | *    | *               | *               |                 |  |

| 0x08 | Erase All Blocks             |      | *               |                 | *               |  |

| 0x09 | Erase Flash Block            | *    | *               | *               |                 |  |

| 0x0A | Erase P-Flash Sector         | *    | *               | *               |                 |  |

| 0x0B | Unsecure Flash               |      | *               |                 | *               |  |

| 0x0C | Verify Backdoor Access Key   | *    |                 | *               |                 |  |

| 0x0D | Set User Margin Level        | *    | *               | *               |                 |  |

| 0x0E | Set Field Margin Level       |      | *               |                 |                 |  |

| 0x10 | Erase Verify EEPROM Section  | *    | *               | *               |                 |  |

| 0x11 | Program EEPROM               | *    | *               | *               |                 |  |

| 0x12 | Erase EEPROM Sector          | *    | *               | *               |                 |  |

Table 30-27. Flash Commands by Mode and Security State

<sup>1</sup> Unsecured Normal Single Chip mode

<sup>2</sup> Unsecured Special Single Chip mode.

<sup>3</sup> Secured Normal Single Chip mode.

<sup>4</sup> Secured Special Single Chip mode.

## 30.4.4.4 P-Flash Commands

Table 30-28 summarizes the valid P-Flash commands along with the effects of the commands on the P-Flash block and other resources within the Flash module.

| FCMD | Command                    | Function on P-Flash Memory                              |

|------|----------------------------|---------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks | Verify that all P-Flash (and EEPROM) blocks are erased. |

### Table 30-28. P-Flash Commands

### 240 KByte Flash Module (S12FTMRG240K2V1)

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.