Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 40                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g64f0vlfr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 28.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM | 1018 |

|------|-----------------------------------------------------------------|------|

|      | 28.5.3 Mode and Security Effects on Flash Command Availability  | 1019 |

| 28.6 | nitialization                                                   | 1019 |

# Chapter 29

# 128 KByte Flash Module (S12FTMRG128K1V1)

| Introduction                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29.1.1 Glossary                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.1.2 Features                                                 | 1023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 29.1.3 Block Diagram                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| External Signal Description                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Memory Map and Registers                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.3.1 Module Memory Map                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.3.2 Register Descriptions                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Functional Description                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.4.1 Modes of Operation                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.4.2 IFR Version ID Word                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.4.3 Internal NVM resource (NVMRES)                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.4.4 Flash Command Operations                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.4.5 Allowed Simultaneous P-Flash and EEPROM Operations       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.4.6 Flash Command Description                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.4.7 Interrupts                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.4.8 Wait Mode                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.4.9 Stop Mode                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Security                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.5.1 Unsecuring the MCU using Backdoor Key Access             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29.5.3 Mode and Security Effects on Flash Command Availability  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Initialization                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                 | 29.1.1 Glossary29.1.2 Features29.1.3 Block DiagramExternal Signal DescriptionMemory Map and Registers29.3.1 Module Memory Map29.3.2 Register DescriptionsFunctional Description29.4.1 Modes of Operation29.4.2 IFR Version ID Word29.4.3 Internal NVM resource (NVMRES)29.4.4 Flash Command Operations29.4.5 Allowed Simultaneous P-Flash and EEPROM Operations29.4.6 Flash Command Description29.4.7 Interrupts29.4.8 Wait Mode29.4.9 Stop ModeSecurity29.5.1 Unsecuring the MCU using Backdoor Key Access29.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM29.5.3 Mode and Security Effects on Flash Command Availability |

# Chapter 30

# 192 KByte Flash Module (S12FTMRG192K2V1)

| 30.1 | Introduction                          | 1073 |

|------|---------------------------------------|------|

|      | 30.1.1 Glossary                       | 1074 |

|      | 30.1.2 Features                       | 1074 |

|      | 30.1.3 Block Diagram                  | 1075 |

|      | External Signal Description           |      |

| 30.3 | Memory Map and Registers              | 1077 |

|      | 30.3.1 Module Memory Map              | 1077 |

|      | 30.3.2 Register Descriptions          | 1081 |

| 30.4 | Functional Description                | 1099 |

|      | 30.4.1 Modes of Operation             |      |

|      | 30.4.2 IFR Version ID Word            |      |

|      | 30.4.3 Internal NVM resource (NVMRES) | 1100 |

Device Overview MC9S12G-Family

|             |       | <lowest< th=""><th>Function<br/>PRIORITY</th><th>highest</th><th>&gt;</th><th>Power</th><th colspan="2">Internal Pull<br/>Resistor</th></lowest<> | Function<br>PRIORITY | highest     | >           | Power            | Internal Pull<br>Resistor |                |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|-------------|------------------|---------------------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.                                                                                                                                      | 3rd<br>Func.         | 4th<br>Func | 5th<br>Func | Supply           | CTRL                      | Reset<br>State |

| 28          | PAD9  | KWAD9                                                                                                                                             | AN9                  | ACMPO       |             | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |

| 29          | PAD2  | KWAD2                                                                                                                                             | AN2                  | _           | _           | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |

| 30          | PAD10 | KWAD10                                                                                                                                            | AN10                 | ACMPP       |             | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |

| 31          | PAD3  | KWAD3                                                                                                                                             | AN3                  | _           |             | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |

| 32          | PAD11 | KWAD11                                                                                                                                            | AN11                 | ACMPM       |             | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |

| 33          | PAD4  | KWAD4                                                                                                                                             | AN4                  | _           |             | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |

| 34          | PAD5  | KWAD5                                                                                                                                             | AN5                  | _           |             | V <sub>DDA</sub> | PER1AD/PPS0AD             | Disabled       |

| 35          | PAD6  | KWAD6                                                                                                                                             | AN6                  | _           |             | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |

| 36          | PAD7  | KWAD7                                                                                                                                             | AN7                  | _           |             | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |

| 37          | VDDA  | VRH                                                                                                                                               | _                    | _           | _           | _                | _                         |                |

| 38          | VSSA  | _                                                                                                                                                 |                      | _           |             |                  |                           |                |

| 39          | PS0   | RXD0                                                                                                                                              |                      | _           |             | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 40          | PS1   | TXD0                                                                                                                                              |                      | _           |             | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 41          | PS2   | RXD1                                                                                                                                              | _                    | _           |             | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 42          | PS3   | TXD1                                                                                                                                              | _                    | _           |             | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 43          | PS4   | MISO0                                                                                                                                             | _                    | —           | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 44          | PS5   | MOSI0                                                                                                                                             | _                    | _           |             | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 45          | PS6   | SCK0                                                                                                                                              | _                    | _           | —           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 46          | PS7   | API_EXTC<br>LK                                                                                                                                    | ECLK                 | SS0         | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 47          | PM0   | —                                                                                                                                                 | _                    | —           | —           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 48          | PM1   | —                                                                                                                                                 |                      | _           | _           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| Table 1-13. 48-Pin LQFP Pinout for | S12GN48 |

|------------------------------------|---------|

|------------------------------------|---------|

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

# 1.17 ADC Result Reference

MCUs of the S12G-Family are able to measure the internal reference voltage  $V_{DDF}$  (see Table 1-38).  $V_{DDF}$  is a constant voltage with a narrow distribution over temperature and external voltage supply (see Table A-47).

A 12-bit left justified<sup>1</sup> ADC conversion result of  $V_{DDF}$  is provided at address  $0x0_4022/0x0_4023$  in the NVM's IFR for reference. The measurement conditions of the reference conversion are listed in Section A.16, "ADC Conversion Result Reference". By measuring the voltage  $V_{DDF}$  (see Table 1-38) and comparing the result to the reference value in the IFR, it is possible to determine the ADC's reference voltage  $V_{RH}$  in the application environment:

$V_{RH} = \frac{StoredReference}{ConvertedReference} \bullet 5V$

The exact absolute value of an analog conversion can be determined as follows:

$Result = ConvertedADInput \bullet \frac{StoredReference \bullet 5V}{ConvertedReference \bullet 2^{n}}$

With:

ConvertedADInput:Result of the analog to digital conversion of the desired pinConvertedReference:Result of channel "Internal\_0" conversionStoredReference:Value in IFR locatio 0x0\_4022/0x0\_4023n:ADC resolution (10 bit)

### **CAUTION**

To assure high accuracy of the  $V_{DDF}$  reference conversion, the NVMs must not be programmed, erased, or read while the conversion takes place. This implies that code must be executed from RAM. The "ConvertedReference" value must be the average of eight consecutive conversions.

### CAUTION

The ADC's reference voltage  $V_{RH}$  must remain at a constant level throughout the conversion process.

# 1.18 ADC VRH/VRL Signal Connection

On all S12G devices except for the S12GA192 and the S12GA240 the external VRH signal is directly connected to the ADC's VRH signal input. The ADC's VRL input is connected to VSSA. (see Figure 1-27).

1. The format of the stored  $\mathsf{V}_{\mathsf{DDF}}$  reference value is still subject to change.

| Port | Global<br>Address | Register                                 | Access | Reset Value | Section/Page   |

|------|-------------------|------------------------------------------|--------|-------------|----------------|

| Т    | 0x0240            | PTT—Port T Data Register                 | R/W    | 0x00        | 2.4.3.15/2-207 |

|      | 0x0241            | PTIT—Port T Input Register               | R      | 3           | 2.4.3.16/2-207 |

|      | 0x0242            | DDRT—Port T Data Direction Register      | R/W    | 0x00        | 2.4.3.17/2-208 |

|      | 0x0243            | Reserved                                 | R      | 0x00        |                |

|      | 0x0244            | PERT—Port T Pull Device Enable Register  | R/W    | 0x00        | 2.4.3.18/2-209 |

|      | 0x0245            | PPST—Port T Polarity Select Register     | R/W    | 0x00        | 2.4.3.19/2-210 |

|      | 0x0246            | Reserved                                 | R      | 0x00        |                |

|      | 0x0247            | Reserved                                 | R      | 0x00        |                |

| S    | 0x0248            | PTS—Port S Data Register                 | R/W    | 0x00        | 2.4.3.20/2-210 |

|      | 0x0249            | PTIS—Port S Input Register               | R      | 3           | 2.4.3.21/2-211 |

|      | 0x024A            | DDRS—Port S Data Direction Register      | R/W    | 0x00        | 2.4.3.22/2-211 |

|      | 0x024B            | Reserved                                 | R      | 0x00        |                |

|      | 0x024C            | PERS—Port S Pull Device Enable Register  | R/W    | 0xFF        | 2.4.3.23/2-212 |

|      | 0x024D            | PPSS—Port S Polarity Select Register     | R/W    | 0x00        | 2.4.3.24/2-212 |

|      | 0x024E            | WOMS—Port S Wired-Or Mode Register       | R/W    | 0x00        | 2.4.3.25/2-213 |

|      | 0x024F            | PRR0—Pin Routing Register 0 <sup>4</sup> | R/W    | 0x00        | 2.4.3.26/2-213 |

| М    | 0x0250            | PTM—Port M Data Register                 | R/W    | 0x00        | 2.4.3.27/2-215 |

|      | 0x0251            | PTIM—Port M Input Register               | R      | 3           | 2.4.3.29/2-216 |

|      | 0x0252            | DDRM—Port M Data Direction Register      | R/W    | 0x00        | 2.4.3.29/2-216 |

|      | 0x0253            | Reserved                                 | R      | 0x00        |                |

|      | 0x0254            | PERM—Port M Pull Device Enable Register  | R/W    | 0x00        | 2.4.3.30/2-217 |

|      | 0x0255            | PPSM—Port M Polarity Select Register     | R/W    | 0x00        | 2.4.3.31/2-218 |

|      | 0x0256            | WOMM—Port M Wired-Or Mode Register       | R/W    | 0x00        | 2.4.3.32/2-218 |

|      | 0x0257            | PKGCR—Package Code Register              | R/W    | 5           | 2.4.3.33/2-219 |

| Р    | 0x0258            | PTP—Port P Data Register                 | R/W    | 0x00        | 2.4.3.34/2-220 |

|      | 0x0259            | PTIP—Port P Input Register               | R      | 3           | 2.4.3.35/2-221 |

|      | 0x025A            | DDRP—Port P Data Direction Register      | R/W    | 0x00        | 2.4.3.36/2-222 |

|      | 0x025B            | Reserved                                 | R      | 0x00        |                |

|      | 0x025C            | PERP—Port P Pull Device Enable Register  | R/W    | 0x00        | 2.4.3.37/2-222 |

|      | 0x025D            | PPSP—Port P Polarity Select Register     | R/W    | 0x00        | 2.4.3.38/2-223 |

|      | 0x025E            | PIEP—Port P Interrupt Enable Register    | R/W    | 0x00        | 2.4.3.39/2-224 |

|      | 0x025F            | PIFP—Port P Interrupt Flag Register      | R/W    | 0x00        | 2.4.3.40/2-224 |

Table 2-18. Block Memory Map (0x0000-0x027F) (continued)

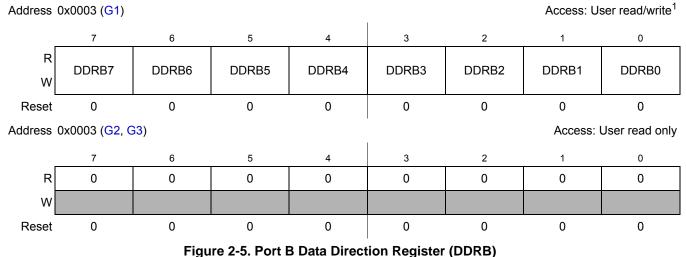

## 2.4.3.4 Port B Data Direction Register (DDRB)

<sup>1</sup> Read: Anytime

Write: Anytime

#### Table 2-25. DDRB Register Field Descriptions

| Field       | Description                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------|

| 7-0<br>DDRB | Port B Data Direction—<br>This bit determines whether the associated pin is an input or output. |

|             | 1 Associated pin configured as output<br>0 Associated pin configured as input                   |

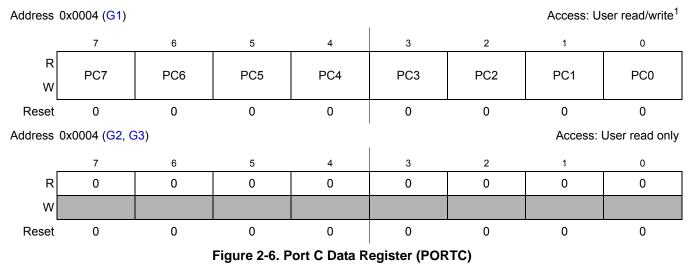

# 2.4.3.5 Port C Data Register (PORTC)

<sup>1</sup> Read: Anytime. The data source is depending on the data direction value. Write: Anytime

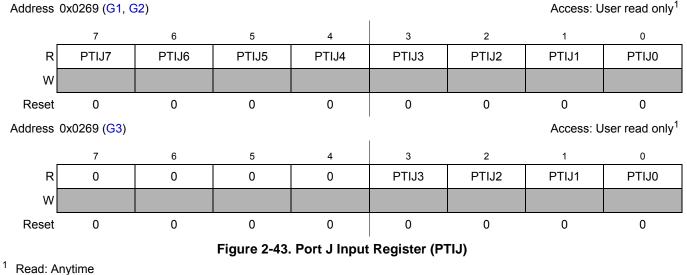

## 2.4.3.43 Port J Input Register (PTIJ)

Write:Never

#### Table 2-69. PTIJ Register Field Descriptions

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTIJ  | <b>Port J input data</b> —<br>A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

## 2.4.3.44 Port J Data Direction Register (DDRJ)

| Address                                 | 0x026A ( <mark>G1</mark> , C | G2)   |               |              |              | Access: U | ser read/write <sup>1</sup> |                             |  |  |  |

|-----------------------------------------|------------------------------|-------|---------------|--------------|--------------|-----------|-----------------------------|-----------------------------|--|--|--|

|                                         | 7                            | 6     | 5             | 4            | 3            | 2         | 1                           | 0                           |  |  |  |

| R                                       |                              |       |               |              | 2100         | מו ססס    |                             |                             |  |  |  |

| W                                       | DDRJ7                        | DDRJ6 | DDRJ5         | DDRJ4        | DDRJ3        | DDRJ2     | DDRJ1                       | DDRJ0                       |  |  |  |

| Reset                                   | 0                            | 0     | 0             | 0            | 0            | 0         | 0                           | 0                           |  |  |  |

| Address 0x026A (G3) Access: User read/w |                              |       |               |              |              |           |                             | ser read/write <sup>1</sup> |  |  |  |

|                                         | 7                            | 6     | 5             | 4            | 3            | 2         | 1                           | 0                           |  |  |  |

| R                                       | 0                            | 0     | 0             | 0            | מו ססס       | מו ססס    |                             |                             |  |  |  |

| W                                       | W DDRJ3 DDRJ2 DDRJ1 DDRJ0    |       |               |              |              |           |                             |                             |  |  |  |

| Reset                                   | 0                            | 0     | 0             | 0            | 0            | 0         | 0                           | 0                           |  |  |  |

|                                         |                              | Figu  | re 2-44. Port | J Data Direc | tion Registe | r (DDRJ)  |                             |                             |  |  |  |

| 1                                       |                              |       |               |              |              |           |                             |                             |  |  |  |

<sup>1</sup> Read: Anytime Write: Anytime

# 2.5 PIM Ports - Functional Description

## 2.5.1 General

Each pin except BKGD can act as general-purpose I/O. In addition most pins can act as an output or input of a peripheral module.

# 2.5.2 Registers

A set of configuration registers is common to all ports with exception of the ADC port (Table 2-91). All registers can be written at any time, however a specific configuration might not become active.

Example: Selecting a pullup device. This device does not become active while the port is used as a push-pull output.

| Port | Data<br>(Portx,<br>PTx) | Input<br>(PTIx) | Data<br>Direction<br>(DDRx) | Pull<br>Enable<br>(PERx) | Polarity<br>Select<br>(PPSx) | Wired-<br>Or Mode<br>(WOMx) | Interrupt<br>Enable<br>(PIEx) | Interrupt<br>Flag<br>(PIFx) |

|------|-------------------------|-----------------|-----------------------------|--------------------------|------------------------------|-----------------------------|-------------------------------|-----------------------------|

| А    | yes                     | -               | yes                         |                          | -                            | -                           | -                             | -                           |

| В    | yes                     | -               | yes                         |                          | -                            | -                           | -                             | -                           |

| С    | yes                     | -               | yes                         | yes                      | -                            | -                           | -                             | -                           |

| D    | yes                     | -               | yes                         |                          | -                            | -                           | -                             | -                           |

| E    | yes                     | -               | yes                         |                          | -                            | -                           | -                             | -                           |

| Т    | yes                     | yes             | yes                         | yes                      | yes                          | -                           | -                             | -                           |

| S    | yes                     | yes             | yes                         | yes                      | yes                          | yes                         | -                             | -                           |

| М    | yes                     | yes             | yes                         | yes                      | yes                          | yes                         | -                             | -                           |

| Р    | yes                     | yes             | yes                         | yes                      | yes                          | -                           | yes                           | yes                         |

| J    | yes                     | yes             | yes                         | yes                      | yes                          | -                           | yes                           | yes                         |

| AD   | yes                     | yes             | yes                         | yes                      | yes                          | -                           | yes                           | yes                         |

### Table 2-91. Register availability per port<sup>1</sup>

<sup>1</sup> Each cell represents one register with individual configuration bits

# 2.5.2.1 Data Register (PORTx, PTx)

This register holds the value driven out to the pin if the pin is used as a general-purpose I/O.

Writing to this register has only an effect on the pin if the pin is used as general-purpose output. When reading this address, the buffered state of the pin is returned if the associated data direction register bit is set to 0.

If the data direction register bits are set to 1, the contents of the data register is returned. This is independent of any other configuration (Figure 2-64).

# 2.5.2.2 Input Register (PTIx)

This register is read-only and always returns the buffered state of the pin (Figure 2-64).

Write: All modes through BDM operation when not secured

### NOTE

When BDM is made active, the CPU stores the content of its CCR register in the BDMCCR register. However, out of special single-chip reset, the BDMCCR is set to 0xD8 and not 0xD0 which is the reset value of the CCR register in this CPU mode. Out of reset in all other modes the BDMCCR register is read zero.

When entering background debug mode, the BDM CCR holding register is used to save the condition code register of the user's program. It is also used for temporary storage in the standard BDM firmware mode. The BDM CCR holding register can be written to modify the CCR value.

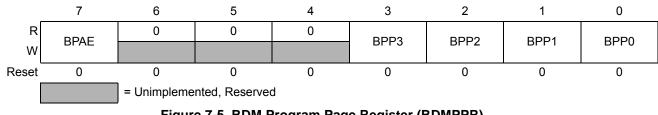

## 7.3.2.2 BDM Program Page Index Register (BDMPPR)

Register Global Address 0x3\_FF08

Figure 7-5. BDM Program Page Register (BDMPPR)

Read: All modes through BDM operation when not secured

Write: All modes through BDM operation when not secured

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>BPAE       | <ul> <li>BDM Program Page Access Enable Bit — BPAE enables program page access for BDM hardware and firmware read/write instructions The BDM hardware commands used to access the BDM registers (READ_BD and WRITE_BD) can not be used for program page accesses even if the BPAE bit is set.</li> <li>0 BDM Program Paging disabled</li> <li>1 BDM Program Paging enabled</li> </ul> |

| 3–0<br>BPP[3:0] | <b>BDM Program Page Index Bits 3–0</b> — These bits define the selected program page. For more detailed information regarding the program page window scheme, please refer to the S12S_MMC Block Guide.                                                                                                                                                                               |

# 7.3.3 Family ID Assignment

The family ID is an 8-bit value located in the BDM ROM in active BDM (at global address: 0x3\_FF0F). The read-only value is a unique family ID which is 0xC2 for devices with an HCS12S core.

# 7.4 Functional Description

The BDM receives and executes commands from a host via a single wire serial interface. There are two types of BDM commands: hardware and firmware commands.

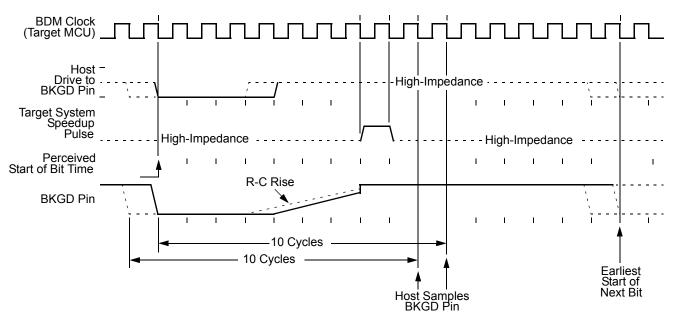

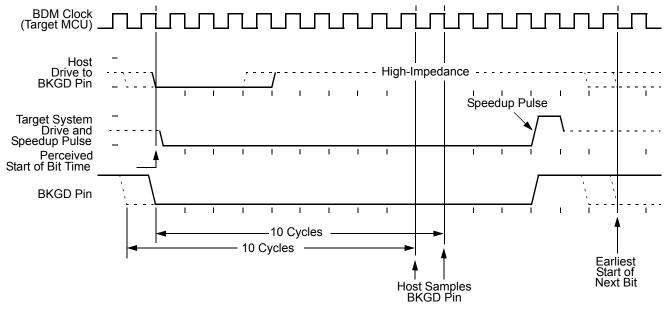

Figure 7-8. BDM Target-to-Host Serial Bit Timing (Logic 1)

Figure 7-9 shows the host receiving a logic 0 from the target. Since the host is asynchronous to the target, there is up to a one clock-cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target. The host initiates the bit time but the target finishes it. Since the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 target clock cycles then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 target clock cycles after starting the bit time.

Figure 7-9. BDM Target-to-Host Serial Bit Timing (Logic 0)

#### Analog-to-Digital Converter (ADC10B16CV2)

edge or level sensitive with polarity control. Table 15-23 gives a brief description of the different combinations of control bits and their effect on the external trigger function.

In order to avoid maybe false trigger events please enable the external digital input via ATDDIEN register first and in the following enable the external trigger mode by bit ETRIGE.

| ETRIGLE | ETRIGP | ETRIGE | SCAN | Description                                                                                       |

|---------|--------|--------|------|---------------------------------------------------------------------------------------------------|

| X       | х      | 0      | 0    | Ignores external trigger. Performs one conversion sequence and stops.                             |

| X       | х      | 0      | 1    | Ignores external trigger. Performs continuous conversion sequences.                               |

| 0       | 0      | 1      | х    | Trigger falling edge sensitive. Performs one conversion sequence per trigger.                     |

| 0       | 1      | 1      | х    | Trigger rising edge sensitive. Performs one conversion sequence per trigger.                      |

| 1       | 0      | 1      | Х    | Trigger low level sensitive. Performs<br>continuous conversions while trigger level<br>is active. |

| 1       | 1      | 1      | х    | Trigger high level sensitive. Performs continuous conversions while trigger level is active.      |

Table 15-23. External Trigger Control Bits

In either level or edge sensitive mode, the first conversion begins when the trigger is received.

Once ETRIGE is enabled a conversion must be triggered externally after writing to ATDCTL5 register.

During a conversion in edge sensitive mode, if additional trigger events are detected the overrun error flag ETORF is set.

If level sensitive mode is active and the external trigger de-asserts and later asserts again during a conversion sequence, this does not constitute an overrun. Therefore, the flag is not set. If the trigger is left active in level sensitive mode when a sequence is about to complete, another sequence will be triggered immediately.

## 15.4.2.2 General-Purpose Digital Port Operation

Each ATD input pin can be switched between analog or digital input functionality. An analog multiplexer makes each ATD input pin selected as analog input available to the A/D converter.

The pad of the ATD input pin is always connected to the analog input channel of the analog mulitplexer.

Each pad input signal is buffered to the digital port register.

This buffer can be turned on or off with the ATDDIEN register for each ATD input pin. This is important so that the buffer does not draw excess current when an ATD input pin is selected as analog input to the ADC10B16C.

#### Pulse-Width Modulator (S12PWM8B8CV2)

Clock A is used as an input to an 8-bit down counter. This down counter loads a user programmable scale value from the scale register (PWMSCLA). When the down counter reaches one, a pulse is output and the 8-bit counter is re-loaded. The output signal from this circuit is further divided by two. This gives a greater range with only a slight reduction in granularity. Clock SA equals clock A divided by two times the value in the PWMSCLA register.

### NOTE

Clock SA = Clock A / (2 \* PWMSCLA)

When PWMSCLA = 00, PWMSCLA value is considered a full scale value of 256. Clock A is thus divided by 512.

Similarly, clock B is used as an input to an 8-bit down counter followed by a divide by two producing clock SB. Thus, clock SB equals clock B divided by two times the value in the PWMSCLB register.

### NOTE

Clock SB = Clock B / (2 \* PWMSCLB)

When PWMSCLB = 00, PWMSCLB value is considered a full scale value of 256. Clock B is thus divided by 512.

As an example, consider the case in which the user writes \$FF into the PWMSCLA register. Clock A for this case will be E (bus clock) divided by 4. A pulse will occur at a rate of once every 255x4 E cycles. Passing this through the divide by two circuit produces a clock signal at an E divided by 2040 rate. Similarly, a value of \$01 in the PWMSCLA register when clock A is E divided by 4 will produce a clock at an E divided by 8 rate.

Writing to PWMSCLA or PWMSCLB causes the associated 8-bit down counter to be re-loaded. Otherwise, when changing rates the counter would have to count down to \$01 before counting at the proper rate. Forcing the associated counter to re-load the scale register value every time PWMSCLA or PWMSCLB is written prevents this.

### NOTE

Writing to the scale registers while channels are operating can cause irregularities in the PWM outputs.

### 19.4.1.3 Clock Select

Each PWM channel has the capability of selecting one of four clocks, clock A, clock SA, clock B or clock SB. The clock selection is done with the PCLKx control bits in the PWMCLK register and PCLKABx control bits in PWMCLKAB register. For backward compatibility consideration, the reset value of PWMCLK and PWMCLKAB configures following default clock selection.

For channels 0, 1, 4, and 5 the clock choices are clock A.

For channels 2, 3, 6, and 7 the clock choices are clock B.

### NOTE

Changing clock control bits while channels are operating can cause irregularities in the PWM outputs.

#### Serial Communication Interface (S12SCIV5)

indicating that the received byte can be read. If the receive interrupt enable bit, RIE, in SCI control register 2 (SCICR2) is also set, the RDRF flag generates an RDRF interrupt request.

### 20.4.6.3 Data Sampling

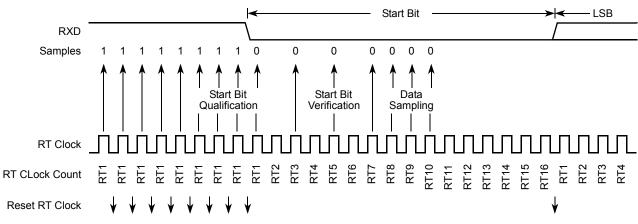

The RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock (see Figure 20-21) is re-synchronized:

- After every start bit

- After the receiver detects a data bit change from logic 1 to logic 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid logic 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid logic 0)

To locate the start bit, data recovery logic does an asynchronous search for a logic 0 preceded by three logic 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 20-21. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Figure 20-17 summarizes the results of the start bit verification samples.

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |

|---------------------------|------------------------|------------|

| 000                       | Yes                    | 0          |

| 001                       | Yes                    | 1          |

| 010                       | Yes                    | 1          |

| 011                       | No                     | 0          |

| 100                       | Yes                    | 1          |

| 101                       | No                     | 0          |

| 110                       | No                     | 0          |

| 111                       | No                     | 0          |

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

| Register<br>Name   |                             | Bit 7 | 6  | 5  | 4  | 3  | 2  | 1  | Bit 0 |

|--------------------|-----------------------------|-------|----|----|----|----|----|----|-------|

| 0x0005             | R                           | R7    | R6 | R5 | R4 | R3 | R2 | R1 | R0    |

| SPIDRL             | W                           | T7    | T6 | T5 | T4 | Т3 | T2 | T1 | TO    |

| 0x0006<br>Reserved | R<br>W                      |       |    |    |    |    |    |    |       |

| 0x0007<br>Reserved | R<br>W                      |       |    |    |    |    |    |    |       |

|                    | = Unimplemented or Reserved |       |    |    |    |    |    |    |       |

Figure 21-2. SPI Register Summary

## 21.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.

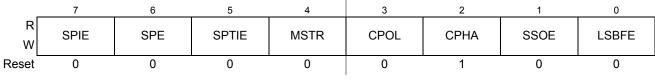

## 21.3.2.1 SPI Control Register 1 (SPICR1)

Module Base +0x0000

Figure 21-3. SPI Control Register 1 (SPICR1)

Read: Anytime

Write: Anytime

#### Table 21-1. SPICR1 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable Bit — This bit enables SPI interrupt requests, if SPIF or MODF status flag is set.</li> <li>SPI interrupts disabled.</li> <li>SPI interrupts enabled.</li> </ul>                                                                                                                                                                |

| 6<br>SPE   | <ul> <li>SPI System Enable Bit — This bit enables the SPI system and dedicates the SPI port pins to SPI system functions. If SPE is cleared, SPI is disabled and forced into idle state, status bits in SPISR register are reset.</li> <li>SPI disabled (lower power consumption).</li> <li>SPI enabled, port pins are dedicated to SPI functions.</li> </ul> |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This bit enables SPI interrupt requests, if SPTEF flag is set.</li> <li>O SPTEF interrupt disabled.</li> <li>1 SPTEF interrupt enabled.</li> </ul>                                                                                                                                                                   |

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] < 010 at command launch                                          |  |  |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |  |  |

|          |           | Set if command not available in current mode (see Table 25-27)                      |  |  |

|          |           | Set if an invalid global address [17:0] is supplied                                 |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |

|          |           | Set if the requested group of words breaches the end of the EEPROM block            |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

Table 25-63. Program EEPROM Command Error Handling

### 25.4.6.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

| CCOBIX[2:0] | FCCOB Parameters                                                                                               |                                                    |  |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| 000         | 0x12                                                                                                           | Global address [17:16] to identify<br>EEPROM block |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 25.1.2.2 for EEPROM sector size. |                                                    |  |

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |

|          |           | Set if command not available in current mode (see Table 25-27)                      |  |  |

|          | ACCERK    | Set if an invalid global address [17:0] is suppliedsee Table 25-3)                  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

Table 25-65. Erase EEPROM Sector Command Error Handling

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_F800-0x3_FFFF    | 2 Kbytes       |

| 01        | 0x3_F000-0x3_FFFF    | 4 Kbytes       |

| 10        | 0x3_E000-0x3_FFFF    | 8 Kbytes       |

| 11        | 0x3_C000-0x3_FFFF    | 16 Kbytes      |

Table 26-19. P-Flash Protection Higher Address Range

#### Table 26-20. P-Flash Protection Lower Address Range

| FPLS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_8000-0x3_83FF    | 1 Kbyte        |

| 01        | 0x3_8000-0x3_87FF    | 2 Kbytes       |

| 10        | 0x3_8000-0x3_8FFF    | 4 Kbytes       |

| 11        | 0x3_8000-0x3_9FFF    | 8 Kbytes       |

All possible P-Flash protection scenarios are shown in Figure 26-14. Although the protection scheme is loaded from the Flash memory at global address 0x3\_FFOC during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 26.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 26.4.6.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0x3\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x3\_FF00-0x3\_FF07 are unaffected by the Verify Backdoor Access Key command sequence. The Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired. In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses 0x3\_FF00-0x3\_FF07 in the Flash configuration field.

# 26.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

A secured MCU can be unsecured in special single chip mode by using the following method to erase the P-Flash and EEPROM memory:

- 1. Reset the MCU into special single chip mode

- 2. Delay while the BDM executes the Erase Verify All Blocks command write sequence to check if the P-Flash and EEPROM memories are erased

- 3. Send BDM commands to disable protection in the P-Flash and EEPROM memory

- 4. Execute the Erase All Blocks command write sequence to erase the P-Flash and EEPROM memory. Alternatively the Unsecure Flash command can be executed, if so the steps 5 and 6 below are skeeped.

- 5. After the CCIF flag sets to indicate that the Erase All Blocks operation has completed, reset the MCU into special single chip mode

- 6. Delay while the BDM executes the Erase Verify All Blocks command write sequence to verify that the P-Flash and EEPROM memory are erased

If the P-Flash and EEPROM memory are verified as erased, the MCU will be unsecured. All BDM commands will now be enabled and the Flash security byte may be programmed to the unsecure state by continuing with the following steps:

7. Send BDM commands to execute the Program P-Flash command write sequence to program the Flash security byte to the unsecured state

| SEC[1:0] | Status of Security   |

|----------|----------------------|

| 00       | SECURED              |

| 01       | SECURED <sup>1</sup> |

| 10       | UNSECURED            |

| 11       | SECURED              |

| Table 28-11. | Flash | Security | States |

|--------------|-------|----------|--------|

|--------------|-------|----------|--------|

<sup>1</sup> Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 28.5.

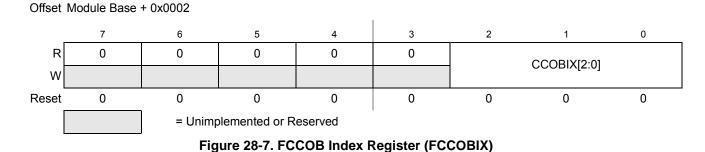

### 28.3.2.3 Flash CCOB Index Register (FCCOBIX)

The FCCOBIX register is used to index the FCCOB register for Flash memory operations.

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

Table 28-12. FCCOBIX Field Descriptions

| Fiel          | d      | Description                                                                                                                                                                                                                  |

|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2–0<br>CCOBIX | X[1:0] | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See 28.3.2.11 Flash Common Command Object Register (FCCOB)," for more details. |

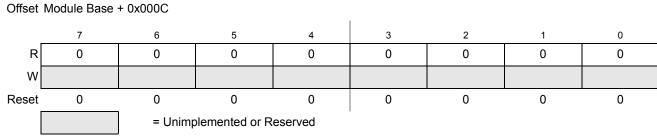

## 28.3.2.4 Flash Reserved0 Register (FRSV0)

This Flash register is reserved for factory testing.

Figure 28-8. Flash Reserved0 Register (FRSV0)

All bits in the FRSV0 register read 0 and are not writable.

| Table 30-17 | . FPROT Field | I Descriptions | (continued) |

|-------------|---------------|----------------|-------------|

|-------------|---------------|----------------|-------------|

| Field            | Description                                                                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>FPLDIS      | Flash Protection Lower Address Range Disable — The FPLDIS bit determines whether there is a<br>protected/unprotected area in a specific region of the P-Flash memory beginning with global address 0x3_8000.0Protection/Unprotection enabled1Protection/Unprotection disabled |

| 1–0<br>FPLS[1:0] | Flash Protection Lower Address Size — The FPLS bits determine the size of the protected/unprotected area in P-Flash memory as shown in Table 30-20. The FPLS bits can only be written to while the FPLDIS bit is set.                                                         |

| FPOPEN | FPHDIS | FPLDIS                          | Function <sup>1</sup>           |  |  |  |

|--------|--------|---------------------------------|---------------------------------|--|--|--|

| 1      | 1      | 1                               | No P-Flash Protection           |  |  |  |

| 1      | 1      | 0                               | Protected Low Range             |  |  |  |

| 1      | 0      | 1                               | Protected High Range            |  |  |  |

| 1      | 0      | 0 Protected High and Low Ranges |                                 |  |  |  |

| 0      | 1      | 1 Full P-Flash Memory Protected |                                 |  |  |  |

| 0      | 1      | 0                               | Unprotected Low Range           |  |  |  |

| 0      | 0      | 1                               | Unprotected High Range          |  |  |  |

| 0      | 0      | 0                               | Unprotected High and Low Ranges |  |  |  |

#### Table 30-18. P-Flash Protection Function

<sup>1</sup> For range sizes, refer to Table 30-19 and Table 30-20.

#### Table 30-19. P-Flash Protection Higher Address Range

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_F800-0x3_FFFF    | 2 Kbytes       |

| 01        | 0x3_F000-0x3_FFFF    | 4 Kbytes       |

| 10        | 0x3_E000-0x3_FFFF    | 8 Kbytes       |

| 11        | 0x3_C000-0x3_FFFF    | 16 Kbytes      |

#### Table 30-20. P-Flash Protection Lower Address Range

| FPLS[1:0] | Global Address Range | Protected Size |  |  |

|-----------|----------------------|----------------|--|--|

| 00        | 0x3_8000-0x3_83FF    | 1 Kbyte        |  |  |

| 01        | 0x3_8000-0x3_87FF    | 2 Kbytes       |  |  |

| 10        | 0x3_8000-0x3_8FFF    | 4 Kbytes       |  |  |

| 11        | 0x3_8000-0x3_9FFF    | 8 Kbytes       |  |  |

All possible P-Flash protection scenarios are shown in Figure 30-14. Although the protection scheme is loaded from the Flash memory at global address 0x3\_FFOC during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 31-55.

| CCOB<br>(CCOBIX=001) | Level Description                |  |  |  |  |

|----------------------|----------------------------------|--|--|--|--|

| 0x0000               | Return to Normal Level           |  |  |  |  |

| 0x0001               | User Margin-1 Level <sup>1</sup> |  |  |  |  |

| 0x0002               | User Margin-0 Level <sup>2</sup> |  |  |  |  |

### Table 31-55. Valid Set User Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### Table 31-56. Set User Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                 |

|----------|-----------|-----------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 001 at command launch.                    |

|          | ACCERR    | Set if command not available in current mode (see Table 31-27). |

| FSTAT    |           | Set if an invalid margin level setting is supplied.             |

| FSTAT    | FPVIOL    | None                                                            |

|          | MGSTAT1   | None                                                            |

|          | MGSTAT0   | None                                                            |

### NOTE

User margin levels can be used to check that Flash memory contents have adequate margin for normal level read operations. If unexpected results are encountered when checking Flash memory contents at user margin levels, a potential loss of information has been detected.

## 31.4.6.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of the P-Flash or EEPROM block.

# Appendix B Detailed Register Address Map

# **Revision History**

| Version<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                         |

|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 0.05          | 30-Aug-2010      | <ul> <li>Updated ADCCTL2 register in Appendix B, "Detailed Register Address Map".</li> <li>Updated CPMUOSC register in Appendix B, "Detailed Register Address Map".</li> </ul> |

| Rev 0.06          | 18-Oct-2010      | Updated ADC registers in Appendix B, "Detailed Register Address Map".                                                                                                          |

| Rev 0.07          | 9-Nov-2010       | Updated CPMU registers in Appendix B, "Detailed Register Address Map".                                                                                                         |

| Rev 0.08          | 4-Dec-2010       | Updated PIM registers in Appendix B, "Detailed Register Address Map".                                                                                                          |

| Rev 0.09          | 24-Apr-2012      | Typos and formatting                                                                                                                                                           |

# B.1 Detailed Register Map

The following tables show the detailed register map of the MC9S12G-Family.

#### NOTE

This is a summary of all register bits implemented on MC9S12G devices. Each member of the MC9S12G-Family implements the subset of registers, which is associated with its feature set (see Table 1-1).

### 0x0000–0x0009 Port Integration Module (PIM) Map 1 of 6

| Address | Name  |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0000  | PORTA | R<br>W | PA7   | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA 0  |

| 0x0001  | PORTB | R<br>W | PB7   | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   |

| 0x0002  | DDRA  | R<br>W | DDRA7 | DDRA6 | DDRA5 | DDRA4 | DDRA3 | DDRA2 | DDRA1 | DDRA0 |

| 0x0003  | DDRB  | R<br>W | DDRB7 | DDRB6 | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 |

| 0x0004  | PORTC | R<br>W | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| 0x0005  | PORTD | R<br>W | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| 0x0006  | DDRC  | R<br>W | DDRC7 | DDRC6 | DDRC5 | DDRC4 | DDRC3 | DDRC2 | DDRC1 | DDRC0 |

| 0x0007  | DDRD  | R<br>W | DDRD7 | DDRD6 | DDRD5 | DDRD4 | DDRD3 | DDRD2 | DDRD1 | DDRD0 |

| 0x0008  | PORTE | R<br>W | 0     | 0     | 0     | 0     | 0     | 0     | PE1   | PE0   |

| 0x0009  | DDRE  | R<br>W | 0     | 0     | 0     | 0     | 0     | 0     | DDRE1 | DDRE0 |