Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 40                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g64f0wlfr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | <     | Func<br>owestPRIO |              | Power        | Internal Pull<br>Resistor |                    |                |

|-------------|-------|-------------------|--------------|--------------|---------------------------|--------------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.      | 3rd<br>Func. | 4th<br>Func. | Supply                    | CTRL               | Reset<br>State |

| 86          | PS4   | MISO0             | _            |              | V <sub>DDX</sub>          | PERS/PPSS          | Up             |

| 87          | PS5   | MOSI0             | _            | _            | V <sub>DDX</sub>          | PERS/PPSS          | Up             |

| 88          | PS6   | SCK0              | _            | _            | V <sub>DDX</sub>          | PERS/PPSS          | Up             |

| 89          | PS7   | API_EXTC<br>LK    | SS0          | —            | V <sub>DDX</sub>          | PERS/PPSS          | Up             |

| 90          | VSSX2 | _                 | _            | _            | —                         |                    |                |

| 91          | VDDX2 | —                 | _            | —            | —                         | _                  | —              |

| 92          | PM0   | RXCAN             | _            | —            | V <sub>DDX</sub>          | PERM/PPSM          | Disabled       |

| 93          | PM1   | TXCAN             | _            | —            | V <sub>DDX</sub>          | PERM/PPSM          | Disabled       |

| 94          | PD4   | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE         | Disabled       |

| 95          | PD5   | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE         | Disabled       |

| 96          | PD6   | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE         | Disabled       |

| 97          | PD7   | —                 | —            | —            | V <sub>DDX</sub>          | PUCR/PUPDE Disable |                |

| 98          | PM2   | RXD2              | —            | _            | V <sub>DDX</sub>          | PERM/PPSM          | Disabled       |

| 99          | PM3   | TXD2              | _            | —            | V <sub>DDX</sub>          | PERM/PPSM          | Disabled       |

| 100         | PJ7   | KWJ7              | SS2          |              | V <sub>DDX</sub>          | PERJ/PPSJ          | Up             |

Table 1-25.

100-Pin LQFP Pinout for S12GA96 and S12GA128

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

|             |       | Function<br><lowestpriorityhighest></lowestpriorityhighest> |              | Power       | Internal P<br>Resisto |                  |               |                |

|-------------|-------|-------------------------------------------------------------|--------------|-------------|-----------------------|------------------|---------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.                                                | 3rd<br>Func. | 4th<br>Func | 5th<br>Func           | Supply           | CTRL          | Reset<br>State |

| 28          | PT4   | IOC4                                                        | —            |             | _                     | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 29          | PT3   | IOC3                                                        | —            | _           | _                     | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 30          | PT2   | IOC2                                                        | —            |             | _                     | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 31          | PT1   | IOC1                                                        | IRQ          |             | _                     | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 32          | PT0   | IOC0                                                        | XIRQ         |             | _                     | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 33          | PAD0  | KWAD0                                                       | AN0          |             | _                     | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 34          | PAD8  | KWAD8                                                       | AN8          | _           | _                     | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 35          | PAD1  | KWAD1                                                       | AN1          |             | _                     | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 36          | PAD9  | KWAD9                                                       | AN9          |             | _                     | V <sub>DDA</sub> | PER0ADPPS0AD  | Disabled       |

| 37          | PAD2  | KWAD2                                                       | AN2          | _           | _                     | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 38          | PAD10 | KWAD10                                                      | AN10         | DACU1       | AMP1                  | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 39          | PAD3  | KWAD3                                                       | AN3          |             | _                     | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 40          | PAD11 | KWAD11                                                      | AN11         | AMP0        | _                     | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 41          | PAD4  | KWAD4                                                       | AN4          |             | _                     | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 42          | PAD12 | KWAD12                                                      | AN12         | _           | _                     | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 43          | PAD5  | KWAD5                                                       | AN5          |             | _                     | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 44          | PAD13 | KWAD13                                                      | AN13         | AMPM0       | _                     | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 45          | PAD6  | KWAD6                                                       | AN6          |             | _                     | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 46          | PAD14 | KWAD14                                                      | AN14         | AMPP0       | _                     | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 47          | PAD7  | KWAD7                                                       | AN7          |             | _                     | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 48          | PAD15 | KWAD15                                                      | AN15         | DACU0       | _                     | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 49          | VRH   |                                                             | —            |             | _                     |                  | _             | _              |

| 50          | VDDA  | —                                                           | —            | —           | _                     | _                | —             | —              |

| 51          | VSSA  | _                                                           | _            | _           | _                     | _                | —             | _              |

| 52          | PS0   | RXD0                                                        | _            | _           | _                     | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 53          | PS1   | TXD0                                                        | —            | _           | _                     | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 54          | PS2   | RXD1                                                        | _            | —           | _                     | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 55          | PS3   | TXD1                                                        | _            | _           | _                     | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 56          | PS4   | MISO0                                                       | —            | —           | —                     | V <sub>DDX</sub> | PERS/PPSS     | Up             |

Table 1-30. 64-Pin LQFP Pinout for S12GA192 and S12GA240

# Chapter 2 Port Integration Module (S12GPIMV1)

## **Revision History**

| Rev. No.<br>(Item No.) | Date<br>(Submitted By) | Sections<br>Affected                                                 | Substantial Change(s)                                                                                                                                                                                                                               |

|------------------------|------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V01.01                 | 01 Dec 2010            | Table 2-4<br>Table 2-5<br>Table 2-8<br>Table 2-16<br>Table 2-17      | <ul> <li>Removed TXD2 and RXD2 from PM1 and PM0 for G64</li> <li>Simplified input buffer control description on port C and AD</li> <li>Corrected DAC signal priorities on pins PAD10 and PAD11 with shared AMP and DACU output functions</li> </ul> |

| V01.02                 | 30 Aug 2011            | 2.4.3.40/2-224<br>2.4.3.48/2-230<br>2.4.3.63/2-239<br>2.4.3.64/2-240 | Corrected PIFx descriptions                                                                                                                                                                                                                         |

| V01.03                 | 15 Mar 2012            | Table 2-2./2-150<br>Table 2-4./2-154                                 | Added GA and GNA derivatives                                                                                                                                                                                                                        |

## 2.1 Introduction

This section describes the S12G-family port integration module (PIM) in its configurations depending on the family devices in their available package options.

It is split up into two parts, firstly determining the routing of the various signals to the available package pins ("PIM Routing") and secondly describing the general-purpose port related logic ("PIM Ports").

## 2.1.1 Glossary

### Table 2-1. Glossary Of Terms

| Term | Definition                                                                                                  |

|------|-------------------------------------------------------------------------------------------------------------|

| Pin  | Package terminal with a unique number defined in the device pinout section                                  |

| •    | Input or output line of a peripheral module or general-purpose I/O function arbitrating for a dedicated pin |

| Port | Group of general-purpose I/O pins sharing peripheral signals                                                |

Port Integration Module (S12GPIMV1)

| Global Address<br>Register Name |        | Bit 7    | 6          | 5            | 4       | 3       | 2        | 1      | Bit 0  |

|---------------------------------|--------|----------|------------|--------------|---------|---------|----------|--------|--------|

| 0x0249                          | R      | PTIS7    | PTIS6      | PTIS5        | PTIS4   | PTIS3   | PTIS2    | PTIS1  | PTIS0  |

| PTIS                            | W      |          |            |              |         |         |          |        |        |

| 0x024A<br>DDRS                  | R<br>W | DDRS7    | DDRS6      | DDRS5        | DDRS4   | DDRS3   | DDRS2    | DDRS1  | DDRS0  |

| 0x024B                          | R      | 0        | 0          | 0            | 0       | 0       | 0        | 0      | 0      |

| Reserved                        | W      |          |            |              |         |         |          |        |        |

| 0x024C<br>PERS                  | R<br>W | PERS7    | PERS6      | PERS5        | PERS4   | PERS3   | PERS2    | PERS1  | PERS0  |

| 0x024D<br>PPSS                  | R<br>W | PPSS7    | PPSS6      | PPSS5        | PPSS4   | PPSS3   | PPSS2    | PPSS1  | PPSS0  |

| 0x024E<br>WOMS                  | R<br>W | WOMS7    | WOMS6      | WOMS5        | WOMS4   | WOMS3   | WOMS2    | WOMS1  | WOMS0  |

| 0x024F<br>PRR0                  | R<br>W | PRR0P3   | PRR0P2     | PRR0T31      | PRR0T30 | PRR0T21 | PRR0T20  | PRR0S1 | PRR0S0 |

| 0x0250                          | R      | 0        | 0          | 0            | 0       | 0       | 0        | PTM1   | PTM0   |

| PTM                             | W      |          |            |              |         |         |          | FIIVII | FTIVIO |

| 0x0251                          | R      | 0        | 0          | 0            | 0       | 0       | 0        | PTIM1  | PTIM0  |

| PTIM                            | W      |          |            |              |         |         |          |        |        |

| 0x0252                          | R      | 0        | 0          | 0            | 0       | 0       | 0        |        |        |

| DDRM                            | W      |          |            |              |         |         |          | DDRM1  | DDRM0  |

| 0x0253                          | R      | 0        | 0          | 0            | 0       | 0       | 0        | 0      | 0      |

| Reserved                        | w      |          |            |              |         |         |          |        |        |

| 0x0254                          | R      | 0        | 0          | 0            | 0       | 0       | 0        |        |        |

| PERM                            | W      | Ŭ        |            |              |         |         | <b>.</b> | PERM1  | PERM0  |

| 0x0255                          | R      | 0        | 0          | 0            | 0       | 0       | 0        |        |        |

| PPSM                            | W      | 0        | 0          | 0            | 0       | 0       | 0        | PPSM1  | PPSM0  |

| 0.0050                          | L      | 0        |            | 0            | 0       | 0       | 0        |        |        |

| 0x0256<br>WOMM                  | R<br>W | 0        | 0          | 0            | 0       | 0       | 0        | WOMM1  | WOMM0  |

|                                 | L      |          |            |              |         |         |          |        |        |

| 0x0257<br>PKGCR                 | R<br>W | APICLKS7 | 0          | 0            | 0       | 0       | PKGCR2   | PKGCR1 | PKGCR0 |

|                                 | [      |          | = Unimplem | nented or Re | served  |         |          |        |        |

#### Table 2-21. Block Register Map (G3) (continued)

- The Bus Clock is based on the Oscillator Clock (OSCCLK).

- The PLLCLK is always on to qualify the external oscillator clock. Therefore it is necessary to make sure a valid PLL configuration is used for the selected oscillator frequency.

- This mode can be entered from default mode PEI by performing the following steps:

- Make sure the PLL configuration is valid for the selected oscillator frequency.

- Enable the external oscillator (OSCE bit)

- Wait for oscillator to start up (UPOSC=1)

- Select the Oscillator Clock (OSCCLK) as Bus Clock (PLLSEL=0).

- The PLLCLK is on and used to qualify the external oscillator clock.

### 10.1.2.2 Wait Mode

For S12CPMU Wait Mode is the same as Run Mode.

### 10.1.2.3 Stop Mode

This mode is entered by executing the CPU STOP instruction.

The voltage regulator is in Reduced Power Mode (RPM).

The API is available.

The Phase Locked Loop (PLL) is off.

The Internal Reference Clock (IRC1M) is off.

Core Clock, Bus Clock and BDM Clock are stopped.

Depending on the setting of the PSTP and the OSCE bit, Stop Mode can be differentiated between Full Stop Mode (PSTP = 0 or OSCE=0) and Pseudo Stop Mode (PSTP = 1 and OSCE=1). In addition, the behavior of the COP in each mode will change based on the clocking method selected by COPOSCSEL[1:0].

• Full Stop Mode (PSTP = 0 or OSCE=0)

External oscillator (XOSCLCP) is disabled.

— If COPOSCSEL1=0:

The COP and RTI counters halt during Full Stop Mode.

After wake-up from Full Stop Mode the Core Clock and Bus Clock are running on PLLCLK (PLLSEL=1). COP and RTI are running on IRCCLK (COPOSCSEL0=0, RTIOSCSEL=0).

— If COPOSCSEL1=1:

During Full Stop Mode the COP is running on ACLK (trimmable internal RC-Oscillator clock) and the RTI counter halts.

After wake-up from Full Stop Mode the Core Clock and Bus Clock are running on PLLCLK (PLLSEL=1). The COP runs on ACLK and RTI is running on IRCCLK (COPOSCSEL0=0, RTIOSCSEL=0).

# 12.4 Functional Description

The ADC12B8C consists of an analog sub-block and a digital sub-block.

## 12.4.1 Analog Sub-Block

The analog sub-block contains all analog electronics required to perform a single conversion. Separate power supplies VDDA and VSSA allow to isolate noise of other MCU circuitry from the analog sub-block.

### 12.4.1.1 Sample and Hold Machine

The Sample and Hold Machine controls the storage and charge of the sample capacitor to the voltage level of the analog signal at the selected ADC input channel.

During the sample process the analog input connects directly to the storage node.

The input analog signals are unipolar and must be within the potential range of VSSA to VDDA.

During the hold process the analog input is disconnected from the storage node.

## 12.4.1.2 Analog Input Multiplexer

The analog input multiplexer connects one of the 8 external analog input channels to the sample and hold machine.

## 12.4.1.3 Analog-to-Digital (A/D) Machine

The A/D Machine performs analog to digital conversions. The resolution is program selectable to be either 8 or 10 or 12 bits. The A/D machine uses a successive approximation architecture. It functions by comparing the sampled and stored analog voltage with a series of binary coded discrete voltages.

By following a binary search algorithm, the A/D machine identifies the discrete voltage that is nearest to the sampled and stored voltage.

When not converting the A/D machine is automatically powered down.

Only analog input signals within the potential range of VRL to VRH (A/D reference potentials) will result in a non-railed digital output code.

## 12.4.2 Digital Sub-Block

This subsection describes some of the digital features in more detail. See Section 12.3.2, "Register Descriptions" for all details.

## 12.4.2.1 External Trigger Input

The external trigger feature allows the user to synchronize ATD conversions to an external event rather than relying only on software to trigger the ATD module when a conversion is about to take place. The external trigger signal (out of reset ATD channel 7, configurable in ATDCTL1) is programmable to be edge

Analog-to-Digital Converter (ADC12B12CV2)

## 14.3.2 Register Descriptions

This section describes in address order all the ADC12B12C registers and their individual bits.

## 14.3.2.1 ATD Control Register 0 (ATDCTL0)

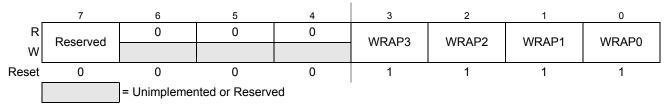

Writes to this register will abort current conversion sequence.

Module Base + 0x0000

#### Figure 14-3. ATD Control Register 0 (ATDCTL0)

#### Read: Anytime

Write: Anytime, in special modes always write 0 to Reserved Bit 7.

| Field            | Description                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                                                                         |

| 3-0<br>WRAP[3-0] | <b>Wrap Around Channel Select Bits</b> — These bits determine the channel for wrap around when doing multi-channel conversions. The coding is summarized in Table 14-2. |

#### Table 14-2. Multi-Channel Wrap Around Coding

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1)<br>Wraparound to AN0 after Converting |

|-------|-------|-------|-------|-------------------------------------------------------------------------------|

| 0     | 0     | 0     | 0     | Reserved <sup>1</sup>                                                         |

| 0     | 0     | 0     | 1     | AN1                                                                           |

| 0     | 0     | 1     | 0     | AN2                                                                           |

| 0     | 0     | 1     | 1     | AN3                                                                           |

| 0     | 1     | 0     | 0     | AN4                                                                           |

| 0     | 1     | 0     | 1     | AN5                                                                           |

| 0     | 1     | 1     | 0     | AN6                                                                           |

| 0     | 1     | 1     | 1     | AN7                                                                           |

| 1     | 0     | 0     | 0     | AN8                                                                           |

| 1     | 0     | 0     | 1     | AN9                                                                           |

| 1     | 0     | 1     | 0     | AN10                                                                          |

| 1     | 0     | 1     | 1     | AN11                                                                          |

| 1     | 1     | 0     | 0     | AN11                                                                          |

| 1     | 1     | 0     | 1     | AN11                                                                          |

| 1     | 1     | 1     | 0     | AN11                                                                          |

| 1     | 1     | 1     | 1     | AN11                                                                          |

# Chapter 15 Analog-to-Digital Converter (ADC10B16CV2)

# **Revision History**

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-------------------|------------------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V02.00            | 18 June 2009     | 18 June 2009      |        | Initial version copied 12 channel block guide                                                                                                                                                                                                                                                                                                                      |  |  |  |

| V02.01            | 09 Feb 2010      | 09 Feb 2010       |        | Updated Table 15-15 Analog Input Channel Select Coding -<br>description of internal channels.<br>Updated register ATDDR (left/right justified result) description<br>in section 15.3.2.12.1/15-527 and 15.3.2.12.2/15-528 and<br>added Table 15-21 to improve feature description.<br>Fixed typo in Table 15-9 - conversion result for 3mV and 10bit<br>resolution |  |  |  |

| V02.03            | 26 Feb 2010      | 26 Feb 2010       |        | Corrected Table 15-15 Analog Input Channel Select Coding - description of internal channels.                                                                                                                                                                                                                                                                       |  |  |  |

| V02.04            | 26 Mar 2010      | 16 Mar 2010       |        | Corrected typo: Reset value of ATDDIEN register                                                                                                                                                                                                                                                                                                                    |  |  |  |

| V02.05            | 14 Apr 2010      | 14 Apr 2010       |        | Corrected typos to be in-line with SoC level pin naming conventions for VDDA, VSSA, VRL and VRH.                                                                                                                                                                                                                                                                   |  |  |  |

| V02.06            | 25 Aug 2010      | 25 Aug 2010       |        | Removed feature of conversion during STOP and general wording clean up done in Section 15.4, "Functional Description                                                                                                                                                                                                                                               |  |  |  |

| v02.07            | 09 Sep 2010      | 09 Sep 2010       |        | Update of internal only information.                                                                                                                                                                                                                                                                                                                               |  |  |  |

| V02.08            | 11 Feb 2011      | 11 Feb 2011       |        | Connectivity Information regarding internal channel_6 added to Table 15-15.                                                                                                                                                                                                                                                                                        |  |  |  |

| V02.09            | 29 Mar 2011      | 29 Mar 2011       |        | Fixed typo in bit description field Table 15-14 for bits CD, CC, CB, CA. Last sentence contained a wrong highest channel number (it is not AN7 to AN0 instead it is AN15 to AN0).                                                                                                                                                                                  |  |  |  |

| V02.10            | 22. Jun 2012     | 22. Jun 2012      |        | Updated register wirte access information in section 15.3.2.9/15-525                                                                                                                                                                                                                                                                                               |  |  |  |

| V02.11            | 29. Jun 2012     | 29. Jun 2012      |        | Removed IP name in block diagram Figure 15-1                                                                                                                                                                                                                                                                                                                       |  |  |  |

| V02.12            | 02 Oct 2012      | 02 Oct 2012       |        | Added user information to avoid maybe false external trigger<br>events when enabling the external trigger mode<br>(Section 15.4.2.1, "External Trigger Input).                                                                                                                                                                                                     |  |  |  |

## 16.1 Introduction

The ADC12B16C is a 16-channel, 12-bit, multiplexed input successive approximation analog-to-digital converter. Refer to device electrical specifications for ATD accuracy.

## 16.1.1 Features

- 8-, 10-, or 12-bit resolution.

- Automatic return to low power after conversion sequence

- Automatic compare with interrupt for higher than or less/equal than programmable value

- Programmable sample time.

- Left/right justified result data.

- External trigger control.

- Sequence complete interrupt.

- Analog input multiplexer for 8 analog input channels.

- Special conversions for VRH, VRL, (VRL+VRH)/2.

- 1-to-16 conversion sequence lengths.

- Continuous conversion mode.

- Multiple channel scans.

- Configurable external trigger functionality on any AD channel or any of four additional trigger inputs. The four additional trigger inputs can be chip external or internal. Refer to device specification for availability and connectivity.

- Configurable location for channel wrap around (when converting multiple channels in a sequence).

## 16.3.2.10 ATD Input Enable Register (ATDDIEN)

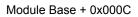

Figure 16-12. ATD Input Enable Register (ATDDIEN)

#### Read: Anytime

Write: Anytime

#### Table 16-19. ATDDIEN Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>IEN[15:0] | <ul> <li>ATD Digital Input Enable on channel x (x= 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) — This bit controls the digital input buffer from the analog input pin (ANx) to the digital data register.</li> <li>0 Disable digital input buffer to ANx pin</li> <li>1 Enable digital input buffer on ANx pin.</li> <li>Note: Setting this bit will enable the corresponding digital input buffer continuously. If this bit is set while simultaneously using it as an analog port, there is potentially increased power consumption because the digital input buffer maybe in the linear region.</li> </ul> |

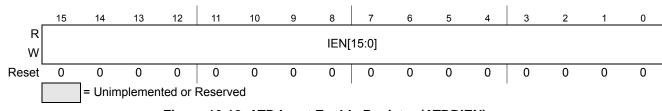

## 16.3.2.11 ATD Compare Higher Than Register (ATDCMPHT)

Writes to this register will abort current conversion sequence.

#### Read: Anytime

Write: Anytime

Module Base + 0x000E

#### Figure 16-13. ATD Compare Higher Than Register (ATDCMPHT)

#### Table 16-20. ATDCMPHT Field Descriptions

| Field       | Description                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

| 15–0        | Compare Operation Higher Than Enable for conversion number <i>n</i> ( <i>n</i> = 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5,       |

| CMPHT[15:0] | 4, 3, 2, 1, 0) of a Sequence ( <i>n conversion number, NOT channel number!</i> ) — This bit selects the operator              |

|             | for comparison of conversion results.                                                                                         |

|             | 0 If result of conversion <i>n</i> is <b>lower or same than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2 |

|             | 1 If result of conversion <i>n</i> is <b>higher than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2        |

#### Table 19-4. PWMCLK Field Descriptions

**Note:** Bits related to available channels have functional significance. Writing to unavailable bits has no effect. Read from unavailable bits return a zero

| ĺ | Field     | Description                                                                                                                                                                                                                                                                |

|---|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | PCLK[7:0] | <ul> <li>Pulse Width Channel 7-0 Clock Select</li> <li>0 Clock A or B is the clock source for PWM channel 7-0, as shown in Table 19-5 and Table 19-6.</li> <li>1 Clock SA or SB is the clock source for PWM channel 7-0, as shown in Table 19-5 and Table 19-6.</li> </ul> |

The clock source of each PWM channel is determined by PCLKx bits in PWMCLK and PCLKABx bits in PWMCLKAB (see Section 19.3.2.7, "PWM Clock A/B Select Register (PWMCLKAB)). For Channel 0, 1, 4, 5, the selection is shown in Table 19-5; For Channel 2, 3, 6, 7, the selection is shown in Table 19-6.

PCLKAB[0,1,4,5]

PCLK[0,1,4,5]

Clock Source Selection

0

0

Clock A

0

1

Clock SA

1

0

Clock B

Table 19-5. PWM Channel 0, 1, 4, 5 Clock Source Selection

1

Clock SB

| PCLKAB[2,3,6,7] | PCLK[2,3,6,7] | Clock Source Selection |  |  |  |

|-----------------|---------------|------------------------|--|--|--|

| 0               | 0             | Clock B                |  |  |  |

| 0               | 1             | Clock SB               |  |  |  |

| 1               | 0             | Clock A                |  |  |  |

| 1               | 1             | Clock SA               |  |  |  |

### 19.3.2.4 PWM Prescale Clock Select Register (PWMPRCLK)

1

This register selects the prescale clock source for clocks A and B independently.

Module Base + 0x0003

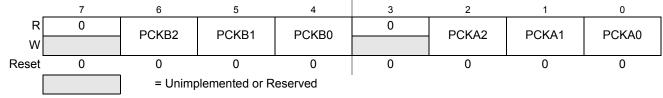

Figure 19-6. PWM Prescale Clock Select Register (PWMPRCLK)

Read: Anytime

Write: Anytime

### NOTE

PCKB2–0 and PCKA2–0 register bits can be written anytime. If the clock pre-scale is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during the transition.

## 20.1.4 Block Diagram

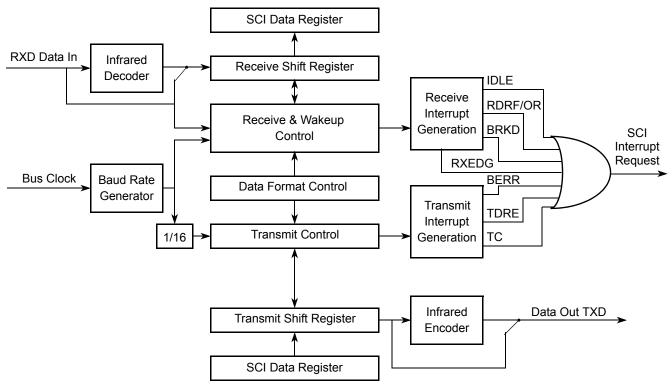

Figure 20-1 is a high level block diagram of the SCI module, showing the interaction of various function blocks.

Figure 20-1. SCI Block Diagram

## 20.2 External Signal Description

The SCI module has a total of two external pins.

## 20.2.1 TXD — Transmit Pin

The TXD pin transmits SCI (standard or infrared) data. It will idle high in either mode and is high impedance anytime the transmitter is disabled.

## 20.2.2 RXD — Receive Pin

The RXD pin receives SCI (standard or infrared) data. An idle line is detected as a line high. This input is ignored when the receiver is disabled and should be terminated to a known voltage.

## 20.3 Memory Map and Register Definition

This section provides a detailed description of all the SCI registers.

### BaudRateDivisor = (SPPR + 1) • 2<sup>(SPR + 1)</sup>

When all bits are clear (the default condition), the SPI module clock is divided by 2. When the selection bits (SPR2–SPR0) are 001 and the preselection bits (SPPR2–SPPR0) are 000, the module clock divisor becomes 4. When the selection bits are 010, the module clock divisor becomes 8, etc.

When the preselection bits are 001, the divisor determined by the selection bits is multiplied by 2. When the preselection bits are 010, the divisor is multiplied by 3, etc. See Table 21-6 for baud rate calculations for all bit conditions, based on a 25 MHz bus clock. The two sets of selects allows the clock to be divided by a non-power of two to achieve other baud rates such as divide by 6, divide by 10, etc.

The baud rate generator is activated only when the SPI is in master mode and a serial transfer is taking place. In the other cases, the divider is disabled to decrease  $I_{DD}$  current.

### NOTE

For maximum allowed baud rates, please refer to the SPI Electrical Specification in the Electricals chapter of this data sheet.

## 21.4.5 Special Features

## 21.4.5.1 SS Output

The  $\overline{SS}$  output feature automatically drives the  $\overline{SS}$  pin low during transmission to select external devices and drives it high during idle to deselect external devices. When  $\overline{SS}$  output is selected, the  $\overline{SS}$  output pin is connected to the  $\overline{SS}$  input pin of the external device.

The  $\overline{SS}$  output is available only in master mode during normal SPI operation by asserting SSOE and MODFEN bit as shown in Table 21-2.

The mode fault feature is disabled while  $\overline{SS}$  output is enabled.

### NOTE

Care must be taken when using the  $\overline{SS}$  output feature in a multimaster system because the mode fault feature is not available for detecting system errors between masters.

## 21.4.5.2 Bidirectional Mode (MOMI or SISO)

The bidirectional mode is selected when the SPC0 bit is set in SPI control register 2 (see Table 21-10). In this mode, the SPI uses only one serial data pin for the interface with external device(s). The MSTR bit decides which pin to use. The MOSI pin becomes the serial data I/O (MOMI) pin for the master mode, and the MISO pin becomes serial data I/O (SISO) pin for the slave mode. The MISO pin in master mode and MOSI pin in slave mode are not used by the SPI.

#### 64 KByte Flash Module (S12FTMRG64K1V1)

• VERNUM: Version number. The first version is number 0b\_0001 with both 0b\_0000 and 0b\_1111 meaning 'none'.

### 27.4.3 Internal NVM resource (NVMRES)

IFR is an internal NVM resource readable by CPU, when NVMRES is active. The IFR fields are shown in Table 27-5.

The NVMRES global address map is shown in Table 27-6.

## 27.4.4 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

- How to write the FCLKDIV register that is used to generate a time base (FCLK) derived from BUSCLK for Flash program and erase command operations

- The command write sequence used to set Flash command parameters and launch execution

- Valid Flash commands available for execution, according to MCU functional mode and MCU security state.

### 27.4.4.1 Writing the FCLKDIV Register

Prior to issuing any Flash program or erase command after a reset, the user is required to write the FCLKDIV register to divide BUSCLK down to a target FCLK of 1 MHz. Table 27-8 shows recommended values for the FDIV field based on BUSCLK frequency.

### NOTE

Programming or erasing the Flash memory cannot be performed if the bus clock runs at less than 0.8 MHz. Setting FDIV too high can destroy the Flash memory due to overstress. Setting FDIV too low can result in incomplete programming or erasure of the Flash memory cells.

When the FCLKDIV register is written, the FDIVLD bit is set automatically. If the FDIVLD bit is 0, the FCLKDIV register has not been written since the last reset. If the FCLKDIV register has not been written, any Flash program or erase command loaded during a command write sequence will not execute and the ACCERR bit in the FSTAT register will set.

### 27.4.4.2 Command Write Sequence

The Memory Controller will launch all valid Flash commands entered using a command write sequence.

Before launching a command, the ACCERR and FPVIOL bits in the FSTAT register must be clear (see Section 27.3.2.7) and the CCIF flag should be tested to determine the status of the current command write sequence. If CCIF is 0, the previous command write sequence is still active, a new command write sequence cannot be started, and all writes to the FCCOB register are ignored.

8. Reset the MCU

## 27.5.3 Mode and Security Effects on Flash Command Availability

The availability of Flash module commands depends on the MCU operating mode and security state as shown in Table 27-27.

## 27.6 Initialization

On each system reset the flash module executes an initialization sequence which establishes initial values for the Flash Block Configuration Parameters, the FPROT and EEPROT protection registers, and the FOPT and FSEC registers. The initialization routine reverts to built-in default values that leave the module in a fully protected and secured state if errors are encountered during execution of the reset sequence. If a double bit fault is detected during the reset sequence, both MGSTAT bits in the FSTAT register will be set.

CCIF is cleared throughout the initialization sequence. The Flash module holds off all CPU access for a portion of the initialization sequence. Flash reads are allowed once the hold is removed. Completion of the initialization sequence is marked by setting CCIF high which enables user commands.

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

#### 96 KByte Flash Module (S12FTMRG96K1V1)

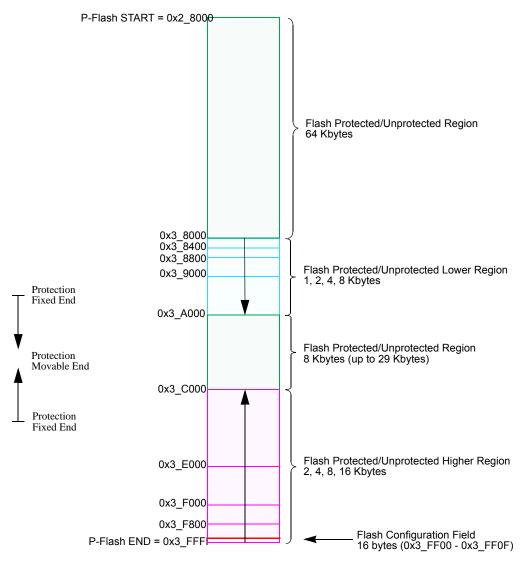

| Global Address      | Size<br>(Bytes) | Description                                                             |

|---------------------|-----------------|-------------------------------------------------------------------------|

| 0x2_8000 – 0x3_FFFF | 96 K            | P-Flash Block<br>Contains Flash Configuration Field<br>(see Table 28-4) |

| Table 28-3. P-Flash M | lemory Addressing |

|-----------------------|-------------------|

|-----------------------|-------------------|

The FPROT register, described in Section 28.3.2.9, can be set to protect regions in the Flash memory from accidental program or erase. Three separate memory regions, one growing upward from global address 0x3\_8000 in the Flash memory (called the lower region), one growing downward from global address 0x3\_FFFF in the Flash memory (called the higher region), and the remaining addresses in the Flash memory, can be activated for protection. The Flash memory addresses covered by these protectable regions are shown in the P-Flash memory map. The higher address region is mainly targeted to hold the boot loader code since it covers the vector space. Default protection settings as well as security information that allows the MCU to restrict access to the Flash module are stored in the Flash configuration field as described in Table 28-4.

Table 28-4. Flash Configuration Field

| Global Address Size (Bytes)    |   | Description                                                                                                                                                        |  |  |  |  |

|--------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0x3_FF00-0x3_FF07              | 8 | Backdoor Comparison Key<br>Refer to Section 28.4.6.11, "Verify Backdoor Access Key Command," and<br>Section 28.5.1, "Unsecuring the MCU using Backdoor Key Access" |  |  |  |  |

| 0x3_FF08-0x3_FF0B <sup>1</sup> | 4 | Reserved                                                                                                                                                           |  |  |  |  |

| 0x3_FF0C <sup>1</sup>          | 1 | P-Flash Protection byte.<br>Refer to Section 28.3.2.9, "P-Flash Protection Register (FPROT)"                                                                       |  |  |  |  |

| 0x3_FF0D <sup>1</sup> 1        |   | EEPROM Protection byte.<br>Refer to Section 28.3.2.10, "EEPROM Protection Register (EEPROT)"                                                                       |  |  |  |  |

| 0x3_FF0E <sup>1</sup> 1        |   | Flash Nonvolatile byte<br>Refer to Section 28.3.2.16, "Flash Option Register (FOPT)"                                                                               |  |  |  |  |

| 0x3_FF0F <sup>1</sup>          | 1 | Flash Security byte<br>Refer to Section 28.3.2.2, "Flash Security Register (FSEC)"                                                                                 |  |  |  |  |

<sup>1</sup> 0x3FF08-0x3\_FF0F form a Flash phrase and must be programmed in a single command write sequence. Each byte in the 0x3\_FF08 - 0x3\_FF0B reserved field should be programmed to 0xFF.

| Global Address      | Size<br>(Bytes) | Field Description                                                       |

|---------------------|-----------------|-------------------------------------------------------------------------|

| 0x0_4000 - 0x0_4007 | 8               | Reserved                                                                |

| 0x0_4008 - 0x0_40B5 | 174             | Reserved                                                                |

| 0x0_40B6 - 0x0_40B7 | 2               | Version ID <sup>1</sup>                                                 |

| 0x0_40B8 - 0x0_40BF | 8               | Reserved                                                                |

|                     |                 | Program Once Field<br>Refer to Section 28.4.6.6, "Program Once Command" |

<sup>1</sup> Used to track firmware patch versions, see Section 28.4.2

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>CCIE  | Command Complete Interrupt Enable — The CCIE bit controls interrupt generation when a Flash command has completed.           0         Command complete interrupt disabled           1         An interrupt will be requested whenever the CCIF flag in the FSTAT register is set (see Section 30.3.2.7)                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 4<br>IGNSF | Ignore Single Bit Fault — The IGNSF controls single bit fault reporting in the FERSTAT register (see Section 30.3.2.8).         0 All single bit faults detected during array reads are reported         1 Single bit faults detected during array reads are not reported and the single bit fault interrupt will not be generated                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 1<br>FDFD  | <ul> <li>Force Double Bit Fault Detect — The FDFD bit allows the user to simulate a double bit fault during Flash array read operations and check the associated interrupt routine. The FDFD bit is cleared by writing a 0 to FDFD.</li> <li>0 Flash array read operations will set the DFDIF flag in the FERSTAT register only if a double bit fault is detected</li> <li>1 Any Flash array read operation will force the DFDIF flag in the FERSTAT register to be set (see Section 30.3.2.7) and an interrupt will be generated as long as the DFDIE interrupt enable in the FERCNFG register is set (see Section 30.3.2.6)</li> </ul> |  |  |  |  |  |  |

| 0<br>FSFD  | <ul> <li>Force Single Bit Fault Detect — The FSFD bit allows the user to simulate a single bit fault during Flash array read operations and check the associated interrupt routine. The FSFD bit is cleared by writing a 0 to FSFD.</li> <li>0 Flash array read operations will set the SFDIF flag in the FERSTAT register only if a single bit fault is detected</li> <li>1 Flash array read operation will force the SFDIF flag in the FERSTAT register to be set (see Section 30.3.2.7) and an interrupt will be generated as long as the SFDIE interrupt enable in the FERCNFG register is set (see Section 30.3.2.6)</li> </ul>     |  |  |  |  |  |  |

#### Table 30-13. FCNFG Field Descriptions

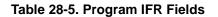

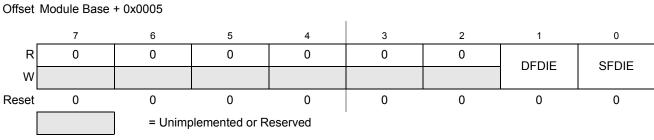

### 30.3.2.6 Flash Error Configuration Register (FERCNFG)

The FERCNFG register enables the Flash error interrupts for the FERSTAT flags.

#### Figure 30-10. Flash Error Configuration Register (FERCNFG)

All assigned bits in the FERCNFG register are readable and writable.

• VERNUM: Version number. The first version is number 0b\_0001 with both 0b\_0000 and 0b\_1111 meaning 'none'.

## 30.4.3 Internal NVM resource (NVMRES)

IFR is an internal NVM resource readable by CPU, when NVMRES is active. The IFR fields are shown in Table 30-5.

The NVMRES global address map is shown in Table 30-6.

## 30.4.4 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

- How to write the FCLKDIV register that is used to generate a time base (FCLK) derived from BUSCLK for Flash program and erase command operations

- The command write sequence used to set Flash command parameters and launch execution

- Valid Flash commands available for execution, according to MCU functional mode and MCU security state.

### 30.4.4.1 Writing the FCLKDIV Register

Prior to issuing any Flash program or erase command after a reset, the user is required to write the FCLKDIV register to divide BUSCLK down to a target FCLK of 1 MHz. Table 30-8 shows recommended values for the FDIV field based on BUSCLK frequency.

### NOTE

Programming or erasing the Flash memory cannot be performed if the bus clock runs at less than 0.8 MHz. Setting FDIV too high can destroy the Flash memory due to overstress. Setting FDIV too low can result in incomplete programming or erasure of the Flash memory cells.

When the FCLKDIV register is written, the FDIVLD bit is set automatically. If the FDIVLD bit is 0, the FCLKDIV register has not been written since the last reset. If the FCLKDIV register has not been written, any Flash program or erase command loaded during a command write sequence will not execute and the ACCERR bit in the FSTAT register will set.

### 30.4.4.2 Command Write Sequence

The Memory Controller will launch all valid Flash commands entered using a command write sequence.

Before launching a command, the ACCERR and FPVIOL bits in the FSTAT register must be clear (see Section 30.3.2.7) and the CCIF flag should be tested to determine the status of the current command write sequence. If CCIF is 0, the previous command write sequence is still active, a new command write sequence cannot be started, and all writes to the FCCOB register are ignored.

| S12G96, S12GA96, S12G128, S12GA128 |                                          |                             |                              |                        |                  |                  |                  |                    |      |

|------------------------------------|------------------------------------------|-----------------------------|------------------------------|------------------------|------------------|------------------|------------------|--------------------|------|

| Num                                | Command                                  | f <sub>NVMOP</sub><br>cycle | f <sub>NVMBUS</sub><br>cycle | Symbol                 | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>3</sup> | Lfmax <sup>4</sup> | Unit |

| 1                                  | Erase Verify All Blocks <sup>5,6</sup>   | 0                           | 35345                        | t <sub>RD1ALL</sub>    | 1.41             | 1.41             | 2.83             | 70.69              | ms   |

| 2                                  | Erase Verify Block (Pflash) <sup>5</sup> | 0                           | 33308                        | t <sub>RD1BLK_P</sub>  | 1.33             | 1.33             | 2.66             | 66.62              | ms   |

| 3                                  | Erase Verify Block (EEPROM) <sup>6</sup> | 0                           | 2536                         | t <sub>RD1BLK_</sub> D | 0.1              | 0.1              | 0.2              | 5.07               | ms   |

| 4                                  | Erase Verify P-Flash Section             | 0                           | 476                          | t <sub>RD1SEC</sub>    | 19.04            | 19.04            | 38.08            | 952                | ms   |

| 5                                  | Read Once                                | 0                           | 445                          | t <sub>RDONCE</sub>    | 17.8             | 17.8             | 17.8             | 445                | μS   |

| 6                                  | Program P-Flash (4 Word)                 | 164                         | 2925                         | t <sub>PGM_4</sub>     | 0.27             | 0.28             | 0.63             | 11.91              | ms   |

| 7                                  | Program Once                             | 164                         | 2888                         | t <sub>PGMONCE</sub>   | 0.27             | 0.28             | 0.28             | 3.09               | ms   |

| 8                                  | Erase All Blocks <sup>5,6</sup>          | 100066                      | 35681                        | t <sub>ERSALL</sub>    | 96.73            | 101.49           | 102.92           | 196.44             | ms   |

| 9                                  | Erase Flash Block (Pflash) <sup>5</sup>  | 100060                      | 33541                        | t <sub>ERSBLK_P</sub>  | 96.64            | 101.4            | 102.74           | 192.16             | ms   |

| 10                                 | Erase Flash Block (EEPROM) <sup>6</sup>  | 100060                      | 2832                         | t <sub>ERSBLK_D</sub>  | 95.41            | 100.17           | 100.29           | 130.74             | ms   |

| 11                                 | Erase P-Flash Sector                     | 20015                       | 865                          | t <sub>ERSPG</sub>     | 19.1             | 20.05            | 20.08            | 26.75              | ms   |

| 12                                 | Unsecure Flash                           | 100066                      | 35759                        | t <sub>UNSECU</sub>    | 96.73            | 101.5            | 102.93           | 196.6              | ms   |

| 13                                 | Verify Backdoor Access Key               | 0                           | 481                          | t <sub>VFYKEY</sub>    | 19.24            | 19.24            | 19.24            | 481                | μS   |

| 14                                 | Set User Margin Level                    | 0                           | 399                          | t <sub>MLOADU</sub>    | 15.96            | 15.96            | 15.96            | 399                | μS   |

| 15                                 | Set Factory Margin Level                 | 0                           | 408                          | t <sub>MLOADF</sub>    | 16.32            | 16.32            | 16.32            | 408                | μS   |

| 16                                 | Erase Verify EEPROM Section              | 0                           | 546                          | t <sub>DRD1SEC</sub>   | 0.02             | 0.02             | 0.04             | 1.09               | ms   |

| 17                                 | Program EEPROM (1 Word)                  | 68                          | 1565                         | t <sub>DPGM_1</sub>    | 0.13             | 0.13             | 0.32             | 6.35               | ms   |

| 18                                 | Program EEPROM (2 Word)                  | 136                         | 2512                         | t <sub>DPGM_2</sub>    | 0.23             | 0.24             | 0.54             | 10.22              | ms   |

| 19                                 | Program EEPROM (3 Word)                  | 204                         | 3459                         | t <sub>DPGM_3</sub>    | 0.33             | 0.34             | 0.76             | 14.09              | ms   |

| 20                                 | Program EEPROM (4 Word)                  | 272                         | 4406                         | t <sub>DPGM_4</sub>    | 0.44             | 0.45             | 0.98             | 17.96              | ms   |

| 21                                 | Erase EEPROM Sector                      | 5015                        | 753                          | t <sub>DERSPG</sub>    | 4.81             | 5.05             | 20.57            | 37.88              | ms   |

#### Table A-37. NVM Timing Characteristics)

$^1\,$  Minimum times are based on maximum  $f_{NVMOP}$  and maximum  $f_{NVMBUS}$

$^2\,$  Typical times are based on typical  $f_{NVMOP}$  and typical  $f_{NVMBUS}$

$^3\,$  Maximum times are based on typical  $f_{\rm NVMOP}$  and typical  $f_{\rm NVMBUS}$  plus aging

$^4$  Lowest-frequency max times are based on minimum  $f_{\rm NVMOP}$  and minimum  $f_{\rm NVMBUS}$  plus aging

<sup>5</sup> Affected by Pflash size

<sup>6</sup> Affected by EEPROM size