### NXP USA Inc. - S9S12G96F0MLHR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 54                                                                     |

| Program Memory Size        | 96КВ (96К х 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 3K x 8                                                                 |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g96f0mlhr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

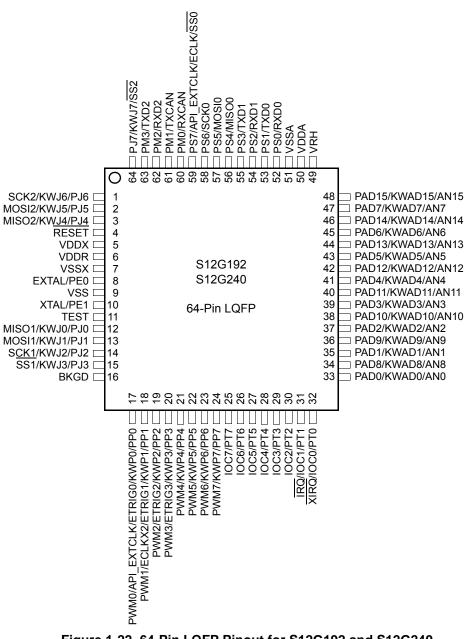

## 1.8.8.2 Pinout 64-Pin LQFP

Figure 1-22. 64-Pin LQFP Pinout for S12G192 and S12G240

|             | <                | Func<br>owestPRIO |              | Power        | Internal Pull<br>Resistor |                     |                |  |

|-------------|------------------|-------------------|--------------|--------------|---------------------------|---------------------|----------------|--|

| Package Pin | Pin              | 2nd<br>Func.      | 3rd<br>Func. | 4th<br>Func. | Supply                    | CTRL                | Reset<br>State |  |

| 1           | PJ6              | KWJ6              | SCK2         | _            | V <sub>DDX</sub>          | PERJ/PPSJ           | Up             |  |

| 2           | PJ5              | KWJ5              | MOSI2        | _            | V <sub>DDX</sub>          | PERJ/PPSJ           | Up             |  |

| 3           | PJ4              | KWJ4              | MISO2        | —            | V <sub>DDX</sub>          | PERJ/PPSJ           | Up             |  |

| 4           | PA0              | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPAE          | Disabled       |  |

| 5           | PA1              | _                 | _            | _            | V <sub>DDX</sub>          | PUCR/PUPAE          | Disabled       |  |

| 6           | PA2              | _                 | _            | _            | V <sub>DDX</sub>          | PUCR/PUPAE          | Disabled       |  |

| 7           | PA3              | _                 | _            | _            | V <sub>DDX</sub>          | PUCR/PUPAE          | Disabled       |  |

| 8           | RESET            | _                 | _            |              | V <sub>DDX</sub>          | PULLUP              |                |  |

| 9           | VDDX1            | _                 | _            | _            | —                         |                     |                |  |

| 10          | VDDR             | _                 | _            | _            | —                         |                     |                |  |

| 11          | VSSX1            | _                 | _            |              | _                         | _                   | _              |  |

| 12          | PE0 <sup>1</sup> | EXTAL             | _            | _            | V <sub>DDX</sub>          | PUCR/PDPEE          | Down           |  |

| 13          | VSS              | _                 | _            |              | _                         | _                   | _              |  |

| 14          | PE1 <sup>1</sup> | XTAL              | _            |              | V <sub>DDX</sub>          | PUCR/PDPEE          | Down           |  |

| 15          | TEST             | _                 | _            |              | N.A.                      | RESET pin           | Down           |  |

| 16          | PA4              | _                 | _            | _            | V <sub>DDX</sub>          | PUCR/PUPAE Disabled |                |  |

| 17          | PA5              | _                 | _            | _            | V <sub>DDX</sub>          | PUCR/PUPAE Disabled |                |  |

| 18          | PA6              | _                 | _            | _            | V <sub>DDX</sub>          | PUCR/PUPAE          | Disabled       |  |

| 19          | PA7              | _                 | _            | _            | V <sub>DDX</sub>          | PUCR/PUPAE          | Disabled       |  |

| 20          | PJ0              | KWJ0              | MISO1        |              | V <sub>DDX</sub>          | PERJ/PPSJ           | Up             |  |

| 21          | PJ1              | KWJ1              | MOSI1        | _            | V <sub>DDX</sub>          | PERJ/PPSJ Up        |                |  |

| 22          | PJ2              | KWJ2              | SCK1         | —            | V <sub>DDX</sub>          | PERJ/PPSJ           | Up             |  |

| 23          | PJ3              | KWJ3              | SS1          | _            | V <sub>DDX</sub>          | PERJ/PPSJ           | Up             |  |

| 24          | BKGD             | MODC              |              | _            | V <sub>DDX</sub>          | PUCR/BKPUE Up       |                |  |

| 25          | PB0              | ECLK              |              | _            | V <sub>DDX</sub>          | PUCR/PUPBE          | Disabled       |  |

| 26          | PB1              | API_EXTC<br>LK    |              | _            | V <sub>DDX</sub>          | PUCR/PUPBE Disabled |                |  |

| 27          | PB2              | ECLKX2            |              | _            | V <sub>DDX</sub>          | PUCR/PUPBE          | Disabled       |  |

Table 1-31. 100-Pin LQFP Pinout for S12GA192 and S12GA240

MC9S12G Family Reference Manual Rev.1.27

<sup>1</sup> Read: Anytime. The data source is depending on the data direction value. Write: Anytime

#### Table 2-23. PORTB Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PB | <b>Port B general-purpose input/output data</b> —Data Register<br>The associated pin can be used as general-purpose I/O. In general-purpose output mode the port data register bit<br>value is driven to the pin.<br>If the associated data direction bit is set to 1, a read returns the value of the port data register bit, otherwise the<br>buffered pin input state is read. |

## 2.4.3.3 Port A Data Direction Register (DDRA)

| Address (                               | Address 0x0002 (G1) Access: User read/write <sup>1</sup> |       |             |               |              |                |       |       |

|-----------------------------------------|----------------------------------------------------------|-------|-------------|---------------|--------------|----------------|-------|-------|

|                                         | 7                                                        | 6     | 5           | 4             | 3            | 2              | 1     | 0     |

| R<br>W                                  | DDRA7                                                    | DDRA6 | DDRA5       | DDRA4         | DDRA3        | DDRA2          | DDRA1 | DDRA0 |

| Reset                                   | 0                                                        | 0     | 0           | 0             | 0            | 0              | 0     | 0     |

| Address 0x0002 (G2, G3) Access: User re |                                                          |       |             |               |              | User read only |       |       |

| _                                       | 7                                                        | 6     | 5           | 4             | 3            | 2              | 1     | 0     |

| R                                       | 0                                                        | 0     | 0           | 0             | 0            | 0              | 0     | 0     |

| w                                       |                                                          |       |             |               |              |                |       |       |

| Reset                                   | 0                                                        | 0     | 0           | 0             | 0            | 0              | 0     | 0     |

|                                         |                                                          | Figu  | ro 2-1 Port | A Data Direct | ion Register |                |       |       |

#### Figure 2-4. Port A Data Direction Register (DDRA)

<sup>1</sup> Read: Anytime Write: Anytime

### Table 2-24. DDRA Register Field Descriptions

| Field       | Description                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------|

| 7-0<br>DDRA | Port A Data Direction—<br>This bit determines whether the associated pin is an input or output. |

|             | 1 Associated pin configured as output<br>0 Associated pin configured as input                   |

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>WCOP      | <ul> <li>Window COP Mode Bit — When set, a write to the CPMUARMCOP register must occur in the last 25% of the selected period. A write during the first 75% of the selected period generates a COP reset. As long as all writes occur during this window, \$55 can be written as often as desired. Once \$AA is written after the \$55, the time-out logic restarts and the user must wait until the next window before writing to CPMUARMCOP. Table 10-13 shows the duration of this window for the seven available COP rates.</li> <li>0 Normal COP operation</li> <li>1 Window COP operation</li> </ul>                                                                                             |

| 6<br>RSBCK     | <ul><li>COP and RTI Stop in Active BDM Mode Bit</li><li>0 Allows the COP and RTI to keep running in Active BDM mode.</li><li>1 Stops the COP and RTI counters whenever the part is in Active BDM mode.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5<br>WRTMASK   | <ul> <li>Write Mask for WCOP and CR[2:0] Bit — This write-only bit serves as a mask for the WCOP and CR[2:0] bits while writing the CPMUCOP register. It is intended for BDM writing the RSBCK without changing the content of WCOP and CR[2:0].</li> <li>0 Write of WCOP and CR[2:0] has an effect with this write of CPMUCOP</li> <li>1 Write of WCOP and CR[2:0] has no effect with this write of CPMUCOP. (Does not count for "write once".)</li> </ul>                                                                                                                                                                                                                                            |

| 2–0<br>CR[2:0] | COP Watchdog Timer Rate Select — These bits select the COP time-out rate (see Table 10-13 and Table 10-14). Writing a nonzero value to CR[2:0] enables the COP counter and starts the time-out period. A COP counter time-out causes a System Reset. This can be avoided by periodically (before time-out) initializing the COP counter via the CPMUARMCOP register.<br>While all of the following four conditions are true the CR[2:0], WCOP bits are ignored and the COP operates at highest time-out period (2 <sup>24</sup> cycles) in normal COP mode (Window COP mode disabled):<br>1) COP is enabled (CR[2:0] is not 000)<br>2) BDM mode active<br>3) RSBCK = 0<br>4) Operation in Special Mode |

#### Table 10-13. COP Watchdog Rates if COPOSCSEL1=0 (default out of reset)

| CR2 | CR1 | CR0 | COPCLK<br>Cycles to Time-out<br>(COPCLK is either IRCCLK or<br>OSCCLK depending on the<br>COPOSCSEL0 bit) |

|-----|-----|-----|-----------------------------------------------------------------------------------------------------------|

| 0   | 0   | 0   | COP disabled                                                                                              |

| 0   | 0   | 1   | 2 <sup>14</sup>                                                                                           |

| 0   | 1   | 0   | 2 <sup>16</sup>                                                                                           |

| 0   | 1   | 1   | 2 <sup>18</sup>                                                                                           |

| 1   | 0   | 0   | 2 <sup>20</sup>                                                                                           |

| 1   | 0   | 1   | 2 <sup>22</sup>                                                                                           |

| 1   | 1   | 0   | 2 <sup>23</sup>                                                                                           |

| 1   | 1   | 1   | 2 <sup>24</sup>                                                                                           |

## 11.1.1 Features

- 8-, 10-bit resolution.

- Automatic return to low power after conversion sequence

- Automatic compare with interrupt for higher than or less/equal than programmable value

- Programmable sample time.

- Left/right justified result data.

- External trigger control.

- Sequence complete interrupt.

- Analog input multiplexer for 8 analog input channels.

- Special conversions for VRH, VRL, (VRL+VRH)/2.

- 1-to-8 conversion sequence lengths.

- Continuous conversion mode.

- Multiple channel scans.

- Configurable external trigger functionality on any AD channel or any of four additional trigger inputs. The four additional trigger inputs can be chip external or internal. Refer to device specification for availability and connectivity.

- Configurable location for channel wrap around (when converting multiple channels in a sequence).

Analog-to-Digital Converter (ADC10B12CV2)

| Address            | Name               |        | Bit 7 | 6           | 5           | 4        | 3                                 | 2   | 1 | Bit 0 |

|--------------------|--------------------|--------|-------|-------------|-------------|----------|-----------------------------------|-----|---|-------|

| 0x0024             | ATDDR10            | R<br>W |       |             |             |          | ft Justified Re<br>ht Justified R |     |   |       |

| 0x0026             | ATDDR11            | R<br>W |       |             |             |          | ft Justified Re<br>ht Justified R | × × |   |       |

| 0x0028 -<br>0x002F | Unimple-<br>mented | R<br>W | 0     | 0           | 0           | 0        | 0                                 | 0   | 0 | 0     |

|                    |                    | Г      |       | ]– Unimpler | mented or P | Posorvod |                                   |     |   |       |

= Unimplemented or Reserved

Figure 13-2. ADC10B12C Register Summary (Sheet 3 of 3)

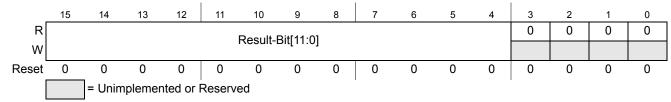

# 15.3.2.12 ATD Conversion Result Registers (ATDDR*n*)

The A/D conversion results are stored in 16 result registers. Results are always in unsigned data representation. Left and right justification is selected using the DJM control bit in ATDCTL3.

If automatic compare of conversions results is enabled (CMPE[n]=1 in ATDCMPE), these registers must be written with the compare values in left or right justified format depending on the actual value of the DJM bit. In this case, as the ATDDRn register is used to hold the compare value, the result will not be stored there at the end of the conversion but is lost.

### Attention, n is the conversion number, NOT the channel number!

Read: Anytime

Write: Anytime

### NOTE

For conversions not using automatic compare, results are stored in the result registers after each conversion. In this case avoid writing to ATDDRn except for initial values, because an A/D result might be overwritten.

### 15.3.2.12.1 Left Justified Result Data (DJM=0)

```

Module Base +

```

```

0x0010 = ATDDR0, 0x0012 = ATDDR1, 0x0014 = ATDDR2, 0x0016 = ATDDR3

0x0018 = ATDDR4, 0x001A = ATDDR5, 0x001C = ATDDR6, 0x001E = ATDDR7

0x0020 = ATDDR8, 0x0022 = ATDDR9, 0x0024 = ATDDR10, 0x0026 = ATDDR11

0x0028 = ATDDR12, 0x002A = ATDDR13, 0x002C = ATDDR14, 0x002E = ATDDR15

```

### Figure 15-14. Left justified ATD conversion result register (ATDDRn)

Table 15-21 shows how depending on the A/D resolution the conversion result is transferred to the ATD result registers for left justified data. Compare is always done using all 12 bits of both the conversion result and the compare value in ATDDRn.

| A/D<br>resolution | DJM | conversion result mapping to ATDDR <i>n</i>                   |

|-------------------|-----|---------------------------------------------------------------|

| 8-bit data        | 0   | Result-Bit[11:4] = conversion result,<br>Result-Bit[3:0]=0000 |

| 10-bit data       | 0   | Result-Bit[11:2] = conversion result,<br>Result-Bit[1:0]=00   |

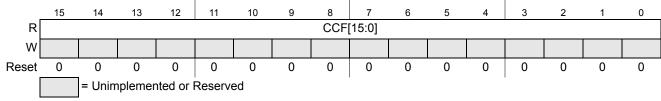

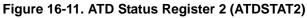

# 16.3.2.9 ATD Status Register 2 (ATDSTAT2)

This read-only register contains the Conversion Complete Flags CCF[15:0].

Module Base + 0x000A

### Read: Anytime

Write: Anytime (for details see Table 16-18 below)

### Table 16-18. ATDSTAT2 Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>CCF[15:0] | <b>Conversion Complete Flag n (n= 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) (n conversion number, NOT channel number!)</b> — A conversion complete flag is set at the end of each conversion in a sequence. The flags are associated with the conversion position in a sequence (and also the result register number). Therefore in non-fifo mode, CCF[4] is set when the fifth conversion in a sequence is complete and the result is available in result register ATDDR4; CCF[5] is set when the sixth conversion in a sequence is complete and the result is available in ATDDR5, and so forth.                                                                                                                                                |

|                   | If automatic compare of conversion results is enabled (CMPE[ <i>n</i> ]=1 in ATDCMPE), the conversion complete flag<br>is only set if comparison with ATDDR <i>n</i> is true. If ACMPIE=1 a compare interrupt will be requested. In this case,<br>as the ATDDR <i>n</i> result register is used to hold the compare value, the result will not be stored there at the end of<br>the conversion but is lost.<br>A flag CCF[ <i>n</i> ] is cleared when one of the following occurs:<br>A) Write to ATDCTL5 (a new conversion sequence is started)<br>B) If AFFC=0, write "1" to CCF[ <i>n</i> ]<br>C) If AFFC=1 and CMPE[ <i>n</i> ]=0, read of result register ATDDR <i>n</i><br>D) If AFFC=1 and CMPE[ <i>n</i> ]=1, write to result register ATDDR <i>n</i> |

|                   | <ul> <li>In case of a concurrent set and clear on CCF[<i>n</i>]: The clearing by method A) will overwrite the set. The clearing by methods B) or C) or D) will be overwritten by the set.</li> <li>Conversion number <i>n</i> not completed or successfully compared</li> <li>If (CMPE[<i>n</i>]=0): Conversion number <i>n</i> has completed. Result is ready in ATDDR<i>n</i>. If (CMPE[<i>n</i>]=1): Compare for conversion result number <i>n</i> with compare value in ATDDR<i>n</i>, using compare operator CMPGT[<i>n</i>] is true. (No result available in ATDDR<i>n</i>)</li> </ul>                                                                                                                                                                  |

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>RXPOL | <ul> <li>Receive Polarity — This bit control the polarity of the received data. In NRZ format, a one is represented by a mark and a zero is represented by a space for normal polarity, and the opposite for inverted polarity. In IrDA format, a zero is represented by short high pulse in the middle of a bit time remaining idle low for a one for normal polarity, and a zero is represented by short low pulse in the middle of a bit time remaining idle high for a one for inverted polarity.</li> <li>0 Normal polarity</li> <li>1 Inverted polarity</li> </ul> |

| 2<br>BRK13 | <ul> <li>Break Transmit Character Length — This bit determines whether the transmit break character is 10 or 11 bit respectively 13 or 14 bits long. The detection of a framing error is not affected by this bit.</li> <li>0 Break character is 10 or 11 bit long</li> <li>1 Break character is 13 or 14 bit long</li> </ul>                                                                                                                                                                                                                                            |

| 1<br>TXDIR | <ul> <li>Transmitter Pin Data Direction in Single-Wire Mode — This bit determines whether the TXD pin is going to be used as an input or output, in the single-wire mode of operation. This bit is only relevant in the single-wire mode of operation.</li> <li>TXD pin to be used as an input in single-wire mode</li> <li>TXD pin to be used as an output in single-wire mode</li> </ul>                                                                                                                                                                               |

| 0<br>RAF   | <ul> <li>Receiver Active Flag — RAF is set when the receiver detects a logic 0 during the RT1 time period of the start bit search. RAF is cleared when the receiver detects an idle character.</li> <li>0 No reception in progress</li> <li>1 Reception in progress</li> </ul>                                                                                                                                                                                                                                                                                           |

## 20.3.2.9 SCI Data Registers (SCIDRH, SCIDRL)

Module Base + 0x0006

### Figure 20-12. SCI Data Registers (SCIDRH)

Module Base + 0x0007

|       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|----|----|

| R     | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| W     | T7 | T6 | T5 | T4 | Т3 | T2 | T1 | Т0 |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

### Figure 20-13. SCI Data Registers (SCIDRL)

Read: Anytime; reading accesses SCI receive data register

Write: Anytime; writing accesses SCI transmit data register; writing to R8 has no effect

#### Serial Communication Interface (S12SCIV5)

indicating that the received byte can be read. If the receive interrupt enable bit, RIE, in SCI control register 2 (SCICR2) is also set, the RDRF flag generates an RDRF interrupt request.

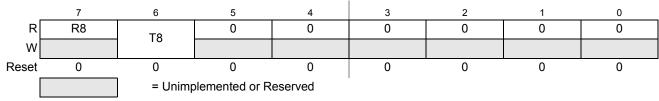

## 20.4.6.3 Data Sampling

The RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock (see Figure 20-21) is re-synchronized:

- After every start bit

- After the receiver detects a data bit change from logic 1 to logic 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid logic 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid logic 0)

To locate the start bit, data recovery logic does an asynchronous search for a logic 0 preceded by three logic 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 20-21. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Figure 20-17 summarizes the results of the start bit verification samples.

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |

|---------------------------|------------------------|------------|

| 000                       | Yes                    | 0          |

| 001                       | Yes                    | 1          |

| 010                       | Yes                    | 1          |

| 011                       | No                     | 0          |

| 100                       | Yes                    | 1          |

| 101                       | No                     | 0          |

| 110                       | No                     | 0          |

| 111                       | No                     | 0          |

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

MC9S12G Family Reference Manual Rev.1.27

#### Table 22-5. TTOV Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Fiel         | ld | Description                                                                                                                                                                                                                                                                                                                                          |

|--------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0<br>TOV[5 |    | <ul> <li>Toggle On Overflow Bits — TOVx toggles output compare pin on overflow. This feature only takes effect when in output compare mode. When set, it takes precedence over forced output compare</li> <li>0 Toggle output compare pin on overflow feature disabled.</li> <li>1 Toggle output compare pin on overflow feature enabled.</li> </ul> |

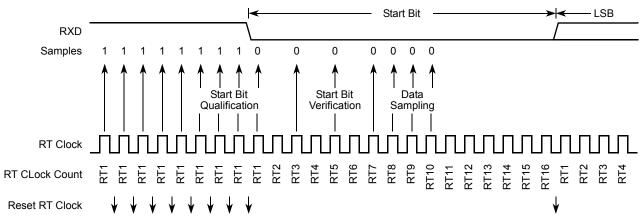

## 22.3.2.6 Timer Control Register 1/Timer Control Register 2 (TCTL1/TCTL2)

Module Base + 0x0008

Figure 22-10. Timer Control Register 1 (TCTL1)

Module Base + 0x0009

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | OM3 | OL3 | OM2 | OL2 | OM1 | OL1 | OM0 | OL0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Figure 22-11. Timer Control Register 2 (TCTL2)

Read: Anytime

Write: Anytime

#### Table 22-6. TCTL1/TCTL2 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero

| Field | Description                                                                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0   | Output Mode — These six pairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx. |

| OMx   | Note: For an output line to be driven by an OCx the OCPDx must be cleared.                                                                                                                                                          |

| 5:0   | Output Level — These sixpairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx. |

| OLx   | Note: For an output line to be driven by an OCx the OCPDx must be cleared.                                                                                                                                                          |

# Chapter 27 64 KByte Flash Module (S12FTMRG64K1V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected                                                          | Description of Changes                                                                            |

|--------------------|------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| V01.04             | 17 Jun 2010      | 27.4.6.1/27-950<br>27.4.6.2/27-951<br>27.4.6.3/27-951<br>27.4.6.14/27-96<br>1 | Clarify Erase Verify Commands Descriptions related to the bits MGSTAT[1:0] of the register FSTAT. |

| V01.05             | 20 aug 2010      | 27.4.6.2/27-951<br>27.4.6.12/27-95<br>8<br>27.4.6.13/27-96<br>0               | Updated description of the commands RD1BLK, MLOADU and MLOADF                                     |

| Rev.1.27           | 31 Jan 2011      | 27.3.2.9/27-933                                                               | Updated description of protection on Section 27.3.2.9                                             |

#### Table 27-1. Revision History

# 27.1 Introduction

The FTMRG64K1 module implements the following:

- 64Kbytes of P-Flash (Program Flash) memory

- 2 Kbytes of EEPROM memory

The Flash memory is ideal for single-supply applications allowing for field reprogramming without requiring external high voltage sources for program or erase operations. The Flash module includes a memory controller that executes commands to modify Flash memory contents. The user interface to the memory controller consists of the indexed Flash Common Command Object (FCCOB) register which is written to with the command, global address, data, and any required command parameters. The memory controller must complete the execution of a command before the FCCOB register can be written to with a new command.

### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

The Flash memory may be read as bytes and aligned words. Read access time is one bus cycle for bytes and aligned words. For misaligned words access, the CPU has to perform twice the byte read access command. For Flash memory, an erased bit reads 1 and a programmed bit reads 0.

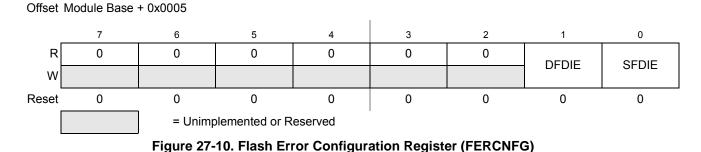

All assigned bits in the FERCNFG register are readable and writable.

#### Table 27-14. FERCNFG Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIE | <ul> <li>Double Bit Fault Detect Interrupt Enable — The DFDIE bit controls interrupt generation when a double bit fault is detected during a Flash block read operation.</li> <li>0 DFDIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the DFDIF flag is set (see Section 27.3.2.8)</li> </ul>                                                       |

| 0<br>SFDIE | <ul> <li>Single Bit Fault Detect Interrupt Enable — The SFDIE bit controls interrupt generation when a single bit fault is detected during a Flash block read operation.</li> <li>0 SFDIF interrupt disabled whenever the SFDIF flag is set (see Section 27.3.2.8)</li> <li>1 An interrupt will be requested whenever the SFDIF flag is set (see Section 27.3.2.8)</li> </ul> |

## 27.3.2.7 Flash Status Register (FSTAT)

The FSTAT register reports the operational status of the Flash module.

Offset Module Base + 0x0006

Figure 27-11. Flash Status Register (FSTAT)

<sup>1</sup> Reset value can deviate from the value shown if a double bit fault is detected during the reset sequence (see Section 27.6).

CCIF, ACCERR, and FPVIOL bits are readable and writable, MGBUSY and MGSTAT bits are readable but not writable, while remaining bits read 0 and are not writable.

# 28.3 Memory Map and Registers

This section describes the memory map and registers for the Flash module. Read data from unimplemented memory space in the Flash module is undefined. Write access to unimplemented or reserved memory space in the Flash module will be ignored by the Flash module.

### CAUTION

Writing to the Flash registers while a Flash command is executing (that is indicated when the value of flag CCIF reads as '0') is not allowed. If such action is attempted the write operation will not change the register value.

Writing to the Flash registers is allowed when the Flash is not busy executing commands (CCIF = 1) and during initialization right after reset, despite the value of flag CCIF in that case (refer to Section 28.6 for a complete description of the reset sequence).

| Global Address (in Bytes) | Size<br>(Bytes) | Description                                                  |

|---------------------------|-----------------|--------------------------------------------------------------|

| 0x0_0000 - 0x0_03FF       | 1,024           | Register Space                                               |

| 0x0_0400 - 0x0_0FFF       | 3,072           | EEPROM Memory                                                |

| 0x0_1000 – 0x0_13FF       | 1,024           | FTMRG reserved area                                          |

| 0x0_4000 – 0x0_7FFF       | 16,284          | NVMRES <sup>1</sup> =1 : NVM Resource area (see Figure 28-3) |

| 0x2_0000 – 0x2_7FFF       | 32,767          | FTMRG reserved area                                          |

| 0x2_8000 – 0x3_FFFF       | 98,304          | P-Flash Memory                                               |

### Table 28-2. FTMRG Memory Map

<sup>1</sup> See NVMRES description in Section 28.4.3

# 28.3.1 Module Memory Map

The S12 architecture places the P-Flash memory between global addresses 0x2\_8000 and 0x3\_FFFF as shown in Table 28-3. The P-Flash memory map is shown in Figure 28-2.

#### 128 KByte Flash Module (S12FTMRG128K1V1)

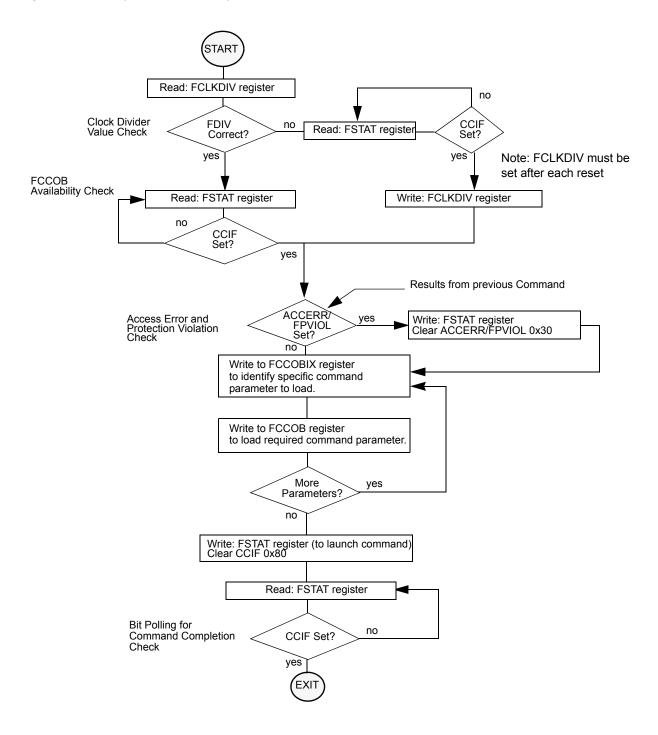

Figure 29-26. Generic Flash Command Write Sequence Flowchart

MC9S12G Family Reference Manual Rev.1.27

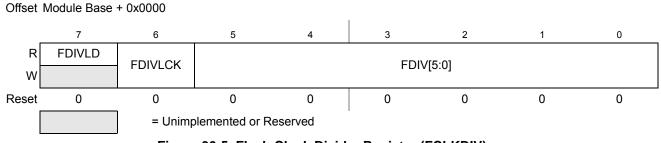

All bits in the FCLKDIV register are readable, bit 7 is not writable, bit 6 is write-once-hi and controls the writability of the FDIV field in normal mode. In special mode, bits 6-0 are writable any number of times but bit 7 remains unwritable.

### CAUTION

The FCLKDIV register should never be written while a Flash command is executing (CCIF=0).

| Table 30-7 | . FCLKDIV | Field | Descriptions |

|------------|-----------|-------|--------------|

|------------|-----------|-------|--------------|

| Field            | Description                                                                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written since the last reset<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                   |

| 6<br>FDIVLCK     | <ul> <li>Clock Divider Locked</li> <li>FDIV field is open for writing</li> <li>FDIV value is locked and cannot be changed. Once the lock bit is set high, only reset can clear this bit and restore writability to the FDIV field in normal mode.</li> </ul>                                                                       |

| 5–0<br>FDIV[5:0] | <b>Clock Divider Bits</b> — FDIV[5:0] must be set to effectively divide BUSCLK down to 1 MHz to control timed events during Flash program and erase algorithms. Table 30-8 shows recommended values for FDIV[5:0] based on the BUSCLK frequency. Please refer to Section 30.4.4, "Flash Command Operations," for more information. |

#### 192 KByte Flash Module (S12FTMRG192K2V1)

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

# 31.3 Memory Map and Registers

This section describes the memory map and registers for the Flash module. Read data from unimplemented memory space in the Flash module is undefined. Write access to unimplemented or reserved memory space in the Flash module will be ignored by the Flash module.

### CAUTION

Writing to the Flash registers while a Flash command is executing (that is indicated when the value of flag CCIF reads as '0') is not allowed. If such action is attempted the write operation will not change the register value.

Writing to the Flash registers is allowed when the Flash is not busy executing commands (CCIF = 1) and during initialization right after reset, despite the value of flag CCIF in that case (refer to Section 31.6 for a complete description of the reset sequence).

| Global Address (in Bytes) | Size<br>(Bytes) | Description                                                  |

|---------------------------|-----------------|--------------------------------------------------------------|

| 0x0_0000 - 0x0_03FF       | 1,024           | Register Space                                               |

| 0x0_0400 – 0x0_13FF       | 4,096           | EEPROM Memory                                                |

| 0x0_4000 – 0x0_7FFF       | 16,284          | NVMRES=0 : P-Flash Memory area active                        |

| 0x0_4000 – 0x0_7FFF       | 16,284          | NVMRES <sup>1</sup> =1 : NVM Resource area (see Figure 31-3) |

| 0x0_8000 – 0x3_FFFF       | 229,376         | P-Flash Memory                                               |

#### Table 31-2. FTMRG Memory Map

<sup>1</sup> See NVMRES description in Section 31.4.3

## 31.3.1 Module Memory Map

The S12 architecture places the P-Flash memory between global addresses  $0x0_4000$  and  $0x3_FFFF$  as shown in Table 31-3. The P-Flash memory map is shown in Figure 31-2.

| Conditions are $3.13V < V_{DD35} < 5.5 V$ unless otherwise noted. |   |                                                                                                                               |                     |     |     |     |      |

|-------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| Nu<br>m                                                           | с | Rating                                                                                                                        | Symbol              | Min | Тур | Max | Unit |

| 1                                                                 | М | Port J, P, AD interrupt input pulse filtered (STOP) <sup>1</sup>                                                              | t <sub>P_MASK</sub> | _   | _   | 3   | μS   |

| 2                                                                 | М | Port J, P, AD interrupt input pulse passed (STOP) <sup>1</sup>                                                                | t <sub>P_PASS</sub> | 10  | _   | —   | μS   |

| 3                                                                 | D | Port J, P, AD interrupt input pulse filtered ( $\overline{\text{STOP}}$ ) in number of bus clock cycles of period $1/f_{bus}$ | n <sub>P_MASK</sub> | —   | —   | 3   |      |

| 4                                                                 | D | Port J, P, AD interrupt input pulse passed ( $\overline{\text{STOP}}$ ) in number of bus clock cycles of period $1/f_{bus}$   | n <sub>P_PASS</sub> | 4   | _   |     |      |

| 5                                                                 | D | $\overline{IRQ}$ pulse width, edge-sensitive mode ( $\overline{STOP}$ ) in number of bus clock cycles of period $1/f_{bus}$   | n <sub>IRQ</sub>    | 1   | _   | —   |      |

Table A-11. Pin Interrupt Characteristics (Junction Temperature From +150°C To +160°C)

<sup>1</sup> Parameter only applies in stop or pseudo stop mode.

# A.3 Supply Currents

This section describes the current consumption characteristics of the device as well as the conditions for the measurements.

### A.3.1 Measurement Conditions

Run current is measured on the VDDX, VDDR<sup>1</sup>, and VDDA<sup>2</sup> pins. It does not include the current to drive external loads. Unless otherwise noted the currents are measured in special single chip mode and the CPU code is executed from RAM. For Run and Wait current measurements PLL is on and the reference clock is the IRC1M trimmed to 1MHz. The bus frequency is 25MHz and the CPU frequency is 50MHz. Table A-12., Table A-13. and Table A-14. show the configuration of the CPMU module and the peripherals for Run, Wait and Stop current measurement.

| Table A-12. CPMU Configuration for Pseu | udo Stop Current Measurement |

|-----------------------------------------|------------------------------|

|-----------------------------------------|------------------------------|

| CPMU REGISTER | Bit settings/Conditions                            |

|---------------|----------------------------------------------------|

| CPMUCLKS      | PLLSEL=0, PSTP=1,<br>PRE=PCE=RTIOSCSEL=COPOSCSEL=1 |

1. On some packages VDDR is bonded to VDDX and the pin is named

VDDXR. Refer to Section 1.8, "Device Pinouts" for further details.

<sup>2.</sup> On some packages VDDA is connected with VDDXR and the common pin

is named VDDXRA.On some packages VSSA is connected to VSSX and the common pin is named

VSSXA. See section Section 1.8, "Device Pinouts" for further details.

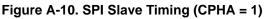

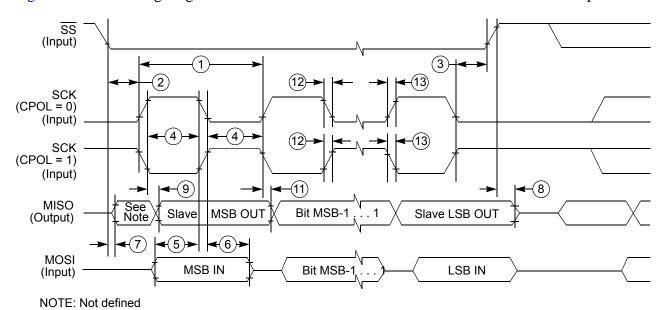

In Figure A-10 the timing diagram for slave mode with transmission format CPHA = 1 is depicted.