# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 12V1                                                                  |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 86                                                                    |

| Program Memory Size        | 96КВ (96К х 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 3K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g96f0mll |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |                  | <lowest< th=""><th>Function<br/>-PRIORITY-</th><th>highest&gt;</th><th>&gt;</th><th>Power</th><th colspan="3">Internal Pull<br/>Resistor</th></lowest<> | Function<br>-PRIORITY- | highest>       | >           | Power            | Internal Pull<br>Resistor |                |  |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|-------------|------------------|---------------------------|----------------|--|

| Package Pin | Pin              | 2nd<br>Func.                                                                                                                                            | 3rd<br>Func.           | 4th<br>Func    | 5th<br>Func | Supply           | CTRL                      | Reset<br>State |  |

| 1           | PJ6              | KWJ6                                                                                                                                                    | —                      | _              | _           | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 2           | PJ5              | KWJ5                                                                                                                                                    | —                      | _              | —           | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 3           | PJ4              | KWJ4                                                                                                                                                    | —                      | _              | —           | V <sub>DDX</sub> | PERJ/PPSJ Up              |                |  |

| 4           | RESET            | _                                                                                                                                                       | —                      | _              | —           | V <sub>DDX</sub> | PULLU                     | P              |  |

| 5           | VDDX             |                                                                                                                                                         | _                      | _              | _           |                  |                           | _              |  |

| 6           | VDDR             |                                                                                                                                                         | _                      | _              | _           |                  |                           | —              |  |

| 7           | VSSX             | _                                                                                                                                                       | —                      | _              | _           |                  | _                         | _              |  |

| 8           | PE0 <sup>1</sup> | EXTAL                                                                                                                                                   | —                      | _              |             | V <sub>DDX</sub> | PUCR/PDPEE                | Down           |  |

| 9           | VSS              |                                                                                                                                                         | _                      | _              |             |                  | _                         | —              |  |

| 10          | PE1 <sup>1</sup> | XTAL                                                                                                                                                    | —                      | _              | _           | V <sub>DDX</sub> | PUCR/PDPEE Dow            |                |  |

| 11          | TEST             | _                                                                                                                                                       | —                      | _              | _           | N.A.             | RESET pin Dowr            |                |  |

| 12          | PJ0              | KWJ0                                                                                                                                                    | MISO1                  | _              | _           | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 13          | PJ1              | KWJ1                                                                                                                                                    | MOSI1                  | _              |             | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 14          | PJ2              | KWJ2                                                                                                                                                    | SCK1                   | _              |             | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |  |

| 15          | PJ3              | KWJ3                                                                                                                                                    | SS1                    | _              |             | V <sub>DDX</sub> | PERJ/PPSJ Up              |                |  |

| 16          | BKGD             | MODC                                                                                                                                                    | —                      | _              |             | V <sub>DDX</sub> | PUCR/BKPUE Up             |                |  |

| 17          | PP0              | KWP0                                                                                                                                                    | ETRIG0                 | API_EXTC<br>LK | PWM0        | V <sub>DDX</sub> | PERP/PPSP Disabled        |                |  |

| 18          | PP1              | KWP1                                                                                                                                                    | ETRIG1                 | ECLKX2         | PWM1        | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 19          | PP2              | KWP2                                                                                                                                                    | ETRIG2                 | PWM2           | —           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 20          | PP3              | KWP3                                                                                                                                                    | ETRIG3                 | PWM3           | —           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 21          | PP4              | KWP4                                                                                                                                                    | PWM4                   | _              | _           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 22          | PP5              | KWP5                                                                                                                                                    | PWM5                   | _              | _           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 23          | PP6              | KWP6                                                                                                                                                    | _                      | _              | _           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 24          | PP7              | KWP7                                                                                                                                                    | _                      | _              | _           | V <sub>DDX</sub> | PERP/PPSP                 | Disabled       |  |

| 25          | PT7              | _                                                                                                                                                       | _                      | _              | _           | V <sub>DDX</sub> | PERT/PPST                 | Disabled       |  |

| 26          | PT6              | _                                                                                                                                                       | _                      | _              | _           | V <sub>DDX</sub> | PERT/PPST                 | Disabled       |  |

| 27          | PT5              | IOC5                                                                                                                                                    | _                      | _              |             | V <sub>DDX</sub> | PERT/PPST                 | Disabled       |  |

Table 1-17. 64-Pin LQFP Pinout for S12G48 and S12G64

| PAD3      | <ul> <li>20 TSSOP: The ACMPO signal of the analog comparator is mapped to this pin when used with the ACMP function. If the ACMP output is enabled (ACMPC[ACOPE]=1) the I/O state will be forced to output.</li> <li>The ADC analog input channel signal AN3 and the related digital trigger input are mapped to this pin. The ADC function has no effect on the output state. Refer to NOTE/2-172 for input buffer control.</li> <li>Pin interrupts can be generated if enabled in digital input or output mode.</li> <li>Signal priority:</li> <li>20 TSSOP: ACMPO &gt; GPO Others: GPO</li> </ul> |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAD2-PAD0 | <ul> <li>The ADC analog input channel signals AN2-0 and their related digital trigger inputs are mapped to this pin. The ADC function has no effect on the output state. Refer to NOTE/2-172 for input buffer control.</li> <li>Pin interrupts can be generated if enabled in digital input or output mode.</li> <li>Signal priority:<br/>GPO</li> </ul>                                                                                                                                                                                                                                             |

## Table 2-17. Port AD Pins AD7-0 (continued)

- Autonomous periodical interrupt (API)

- Bus Clock Generator

- Clock switch to select either PLLCLK or external crystal/resonator based Bus Clock

- PLLCLK divider to adjust system speed

- System Reset generation from the following possible sources:

- Power-on reset (POR)

- Low-voltage reset (LVR)

- Illegal address access

- COP time out

- Loss of oscillation (clock monitor fail)

- External pin RESET

# 10.1.2 Modes of Operation

This subsection lists and briefly describes all operating modes supported by the S12CPMU.

# 10.1.2.1 Run Mode

The voltage regulator is in Full Performance Mode (FPM).

```

The Phase Locked Loop (PLL) is on.

```

The Internal Reference Clock (IRC1M) is on.

The API is available.

- PLL Engaged Internal (PEI)

- This is the default mode after System Reset and Power-On Reset.

- The Bus Clock is based on the PLLCLK.

- After reset the PLL is configured for 50 MHz VCOCLK operation Post divider is 0x03, so PLLCLK is VCOCLK divided by 4, that is 12.5MHz and Bus Clock is 6.25MHz.

- The PLL can be re-configured for other bus frequencies.

- The reference clock for the PLL (REFCLK) is based on internal reference clock IRC1M

- PLL Engaged External (PEE)

- The Bus Clock is based n the PLLCLK.

- This mode can be entered from default mode PEI by performing the following steps:

- Configure the PLL for desired bus frequency.

- Program the reference divider (REFDIV[3:0] bits) to divide down oscillator frequency if necessary.

- Enable the external oscillator (OSCE bit)

- Wait for oscillator to start up (UPOSC=1) and PLL to lock (LOCK=1).

- PLL Bypassed External (PBE)

- The Bus Clock is based on the Oscillator Clock (OSCCLK).

- The PLLCLK is always on to qualify the external oscillator clock. Therefore it is necessary to make sure a valid PLL configuration is used for the selected oscillator frequency.

- This mode can be entered from default mode PEI by performing the following steps:

- Make sure the PLL configuration is valid for the selected oscillator frequency.

- Enable the external oscillator (OSCE bit)

- Wait for oscillator to start up (UPOSC=1)

- Select the Oscillator Clock (OSCCLK) as Bus Clock (PLLSEL=0).

- The PLLCLK is on and used to qualify the external oscillator clock.

# 10.1.2.2 Wait Mode

For S12CPMU Wait Mode is the same as Run Mode.

# 10.1.2.3 Stop Mode

This mode is entered by executing the CPU STOP instruction.

The voltage regulator is in Reduced Power Mode (RPM).

The API is available.

The Phase Locked Loop (PLL) is off.

The Internal Reference Clock (IRC1M) is off.

Core Clock, Bus Clock and BDM Clock are stopped.

Depending on the setting of the PSTP and the OSCE bit, Stop Mode can be differentiated between Full Stop Mode (PSTP = 0 or OSCE=0) and Pseudo Stop Mode (PSTP = 1 and OSCE=1). In addition, the behavior of the COP in each mode will change based on the clocking method selected by COPOSCSEL[1:0].

• Full Stop Mode (PSTP = 0 or OSCE=0)

External oscillator (XOSCLCP) is disabled.

— If COPOSCSEL1=0:

The COP and RTI counters halt during Full Stop Mode.

After wake-up from Full Stop Mode the Core Clock and Bus Clock are running on PLLCLK (PLLSEL=1). COP and RTI are running on IRCCLK (COPOSCSEL0=0, RTIOSCSEL=0).

— If COPOSCSEL1=1:

During Full Stop Mode the COP is running on ACLK (trimmable internal RC-Oscillator clock) and the RTI counter halts.

After wake-up from Full Stop Mode the Core Clock and Bus Clock are running on PLLCLK (PLLSEL=1). The COP runs on ACLK and RTI is running on IRCCLK (COPOSCSEL0=0, RTIOSCSEL=0).

S12 Clock, Reset and Power Management Unit (S12CPMU)

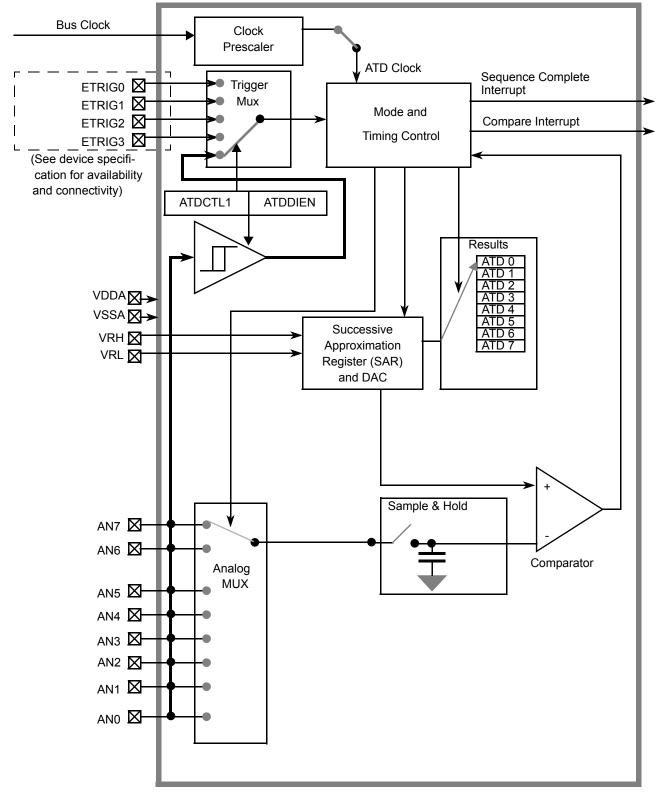

# 11.1.3 Block Diagram

# Chapter 13 Analog-to-Digital Converter (ADC10B12CV2)

# **Revision History**

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author                                                                                                                                                                                                                                                                                  | Description of Changes                                                                                                                                                            |

|-------------------|------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V02.00            | 13 May 2009      | 13 May 2009       |                                                                                                                                                                                                                                                                                         | Initial version copied from V01.06,<br>changed unused Bits in ATDDIEN to read logic 1                                                                                             |

| V02.01            | 30.Nov 2009      | 30.Nov 2009       | Updated Table 13-15 Analog Input Channel Select Coding -<br>description of internal channels.<br>Updated register ATDDR (left/right justified result) descriptio<br>in section 13.3.2.12.1/13-475 and 13.3.2.12.2/13-476 and<br>added table Table 13-21 to improve feature description. |                                                                                                                                                                                   |

| V02.02            | 09 Feb 2010      | 09 Feb 2010       |                                                                                                                                                                                                                                                                                         | Fixed typo in Table 13-9- conversion result for 3mV and 10bit resolution                                                                                                          |

| V02.03            | 26 Feb 2010      | 26 Feb 2010       |                                                                                                                                                                                                                                                                                         | Corrected Table 13-15 Analog Input Channel Select Coding - description of internal channels.                                                                                      |

| V02.04            | 14 Apr 2010      | 14 Apr 2010       |                                                                                                                                                                                                                                                                                         | Corrected typos to be in-line with SoC level pin naming conventions for VDDA, VSSA, VRL and VRH.                                                                                  |

| V02.05            | 25 Aug 2010      | 25 Aug 2010       | Removed feature of conversion during STOP and general<br>wording clean up done in Section 13.4, "Functional<br>Description                                                                                                                                                              |                                                                                                                                                                                   |

| V02.06            | 09 Sep 2010      | 09 Sep 2010       |                                                                                                                                                                                                                                                                                         | Update of internal only information.                                                                                                                                              |

| V02.07            | 11 Feb 2011      | 11 Feb 2011       |                                                                                                                                                                                                                                                                                         | Connectivity Information regarding internal channel_6 added to Table 13-15.                                                                                                       |

| V02.08            | 29 Mar 2011      | 29 Mar 2011       |                                                                                                                                                                                                                                                                                         | Fixed typo in bit description field Table 13-14 for bits CD, CC, CB, CA. Last sentence contained a wrong highest channel number (it is not AN7 to AN0 instead it is AN11 to AN0). |

| V02.09            | 22. Jun 2012     | 22. Jun 2012      |                                                                                                                                                                                                                                                                                         | Update of register write access information in section 13.3.2.9/13-473.                                                                                                           |

| V02.10            | 29 Jun 2012      | 29. Jun 2012      |                                                                                                                                                                                                                                                                                         | Removed IP name in block diagram Figure 13-1                                                                                                                                      |

| V02.11            | 02 Oct 2012      | 02 Oct 2012       |                                                                                                                                                                                                                                                                                         | Added user information to avoid maybe false external trigger<br>events when enabling the external trigger mode<br>(Section 13.4.2.1, "External Trigger Input).                    |

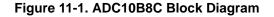

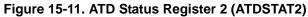

# 15.3.2.9 ATD Status Register 2 (ATDSTAT2)

This read-only register contains the Conversion Complete Flags CCF[15:0].

## Read: Anytime

Write: Anytime (for details see Table 15-18 below)

## Table 15-18. ATDSTAT2 Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>CCF[15:0] | <b>Conversion Complete Flag n (n= 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) (n conversion number, NOT channel number!)</b> — A conversion complete flag is set at the end of each conversion in a sequence. The flags are associated with the conversion position in a sequence (and also the result register number). Therefore in non-fifo mode, CCF[4] is set when the fifth conversion in a sequence is complete and the result is available in result register ATDDR4; CCF[5] is set when the sixth conversion in a sequence is complete and the result is available in ATDDR5, and so forth.                                                                                                                                                |

|                   | If automatic compare of conversion results is enabled (CMPE[ <i>n</i> ]=1 in ATDCMPE), the conversion complete flag<br>is only set if comparison with ATDDR <i>n</i> is true. If ACMPIE=1 a compare interrupt will be requested. In this case,<br>as the ATDDR <i>n</i> result register is used to hold the compare value, the result will not be stored there at the end of<br>the conversion but is lost.<br>A flag CCF[ <i>n</i> ] is cleared when one of the following occurs:<br>A) Write to ATDCTL5 (a new conversion sequence is started)<br>B) If AFFC=0, write "1" to CCF[ <i>n</i> ]<br>C) If AFFC=1 and CMPE[ <i>n</i> ]=0, read of result register ATDDR <i>n</i><br>D) If AFFC=1 and CMPE[ <i>n</i> ]=1, write to result register ATDDR <i>n</i> |

|                   | <ul> <li>In case of a concurrent set and clear on CCF[<i>n</i>]: The clearing by method A) will overwrite the set. The clearing by methods B) or C) or D) will be overwritten by the set.</li> <li>Conversion number <i>n</i> not completed or successfully compared</li> <li>If (CMPE[<i>n</i>]=0): Conversion number <i>n</i> has completed. Result is ready in ATDDR<i>n</i>. If (CMPE[<i>n</i>]=1): Compare for conversion result number <i>n</i> with compare value in ATDDR<i>n</i>, using compare operator CMPGT[<i>n</i>] is true. (No result available in ATDDR<i>n</i>)</li> </ul>                                                                                                                                                                  |

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>WUPIE <sup>1</sup> | Wake-Up Interrupt Enable0 No interrupt request is generated from this event.1 A wake-up event causes a Wake-Up interrupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6<br>CSCIE              | <ul> <li>CAN Status Change Interrupt Enable</li> <li>0 No interrupt request is generated from this event.</li> <li>1 A CAN Status Change event causes an error interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5-4<br>RSTATE[1:0<br>]  | <ul> <li>Receiver Status Change Enable — These RSTAT enable bits control the sensitivity level in which receiver state changes are causing CSCIF interrupts. Independent of the chosen sensitivity level the RSTAT flags continue to indicate the actual receiver state and are only updated if no CSCIF interrupt is pending.</li> <li>00 Do not generate any CSCIF interrupt caused by receiver state changes.</li> <li>01 Generate CSCIF interrupt only if the receiver enters or leaves "bus-off" state. Discard other receiver state changes for generating CSCIF interrupt.</li> <li>10 Generate CSCIF interrupt only if the receiver enters or leaves "RxErr" or "bus-off"<sup>2</sup> state. Discard other receiver state changes for generating CSCIF interrupt.</li> <li>11 Generate CSCIF interrupt on all state changes.</li> </ul>              |

| 3-2<br>TSTATE[1:0]      | <ul> <li>Transmitter Status Change Enable — These TSTAT enable bits control the sensitivity level in which transmitter state changes are causing CSCIF interrupts. Independent of the chosen sensitivity level, the TSTAT flags continue to indicate the actual transmitter state and are only updated if no CSCIF interrupt is pending.</li> <li>00 Do not generate any CSCIF interrupt caused by transmitter state changes.</li> <li>01 Generate CSCIF interrupt only if the transmitter enters or leaves "bus-off" state. Discard other transmitter state changes for generating CSCIF interrupt.</li> <li>10 Generate CSCIF interrupt only if the transmitter enters or leaves "TxErr" or "bus-off" state. Discard other transmitter state changes for generating CSCIF interrupt.</li> <li>11 Generate CSCIF interrupt on all state changes.</li> </ul> |

| 1<br>OVRIE              | Overrun Interrupt Enable0 No interrupt request is generated from this event.1 An overrun event causes an error interrupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0<br>RXFIE              | <ul> <li>Receiver Full Interrupt Enable</li> <li>0 No interrupt request is generated from this event.</li> <li>1 A receive buffer full (successful message reception) event causes a receiver interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### Table 18-12. CANRIER Register Field Descriptions

<sup>1</sup> WUPIE and WUPE (see Section 18.3.2.1, "MSCAN Control Register 0 (CANCTL0)") must both be enabled if the recovery mechanism from stop or wait is required.

<sup>2</sup> Bus-off state is only defined for transmitters by the CAN standard (see Bosch CAN 2.0A/B protocol specification). Because the only possible state change for the transmitter from bus-off to TxOK also forces the receiver to skip its current state to RxOK, the coding of the RXSTAT[1:0] flags define an additional bus-off state for the receiver (see Section 18.3.2.5, "MSCAN Receiver Flag Register (CANRFLG)").

# 18.3.2.7 MSCAN Transmitter Flag Register (CANTFLG)

The transmit buffer empty flags each have an associated interrupt enable bit in the CANTIER register.

# 18.3.2.17 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 18.3.3.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 18.4.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

Module Base + 0x0010 to Module Base + 0x0013

Access: User read/write<sup>1</sup>

Access: User read/write<sup>1</sup>

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

### Figure 18-20. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0–CANIDAR3

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 18-22. CANIDAR0–CANIDAR3 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AC[7:0] | Acceptance Code Bits — AC[7:0] comprise a user-defined sequence of bits with which the corresponding bits of the related identifier register (IDRn) of the receive message buffer are compared. The result of this comparison is then masked with the corresponding identifier mask register. |

Module Base + 0x0018 to Module Base + 0x001B

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 18-21. MSCAN Identifier Acceptance Registers (Second Bank) — CANIDAR4–CANIDAR7

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

### Table 19-9. PWMCAE Field Descriptions

Note: Bits related to available channels have functional significance. Writing to unavailable bits has no effect. Read from unavailable bits return a zero

| Field           | Description                                                                                                                                                 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>CAE[7:0] | Center Aligned Output Modes on Channels 7–0<br>0 Channels 7–0 operate in left aligned output mode.<br>1 Channels 7–0 operate in center aligned output mode. |

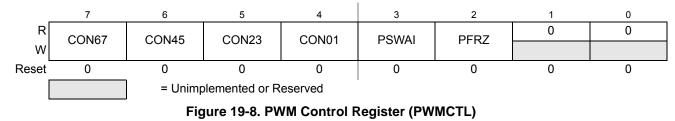

# 19.3.2.6 PWM Control Register (PWMCTL)

The PWMCTL register provides for various control of the PWM module.

Module Base + 0x0005

## Read: Anytime

Write: Anytime

There are up to four control bits for concatenation, each of which is used to concatenate a pair of PWM channels into one 16-bit channel. If the corresponding channels do not exist on a particular derivative, then writes to these bits have no effect and reads will return zeroes. When channels 6 and 7 are concatenated, channel 6 registers become the high order bytes of the double byte channel. When channels 4 and 5 are concatenated, channel 4 registers become the high order bytes of the double byte channel. When channels 2 and 3 are concatenated, channel 2 registers become the high order bytes of the double byte of the double byte channel. When channels 0 and 1 are concatenated, channel 0 registers become the high order bytes of the double byte of the double byte channel.

See Section 19.4.2.7, "PWM 16-Bit Functions" for a more detailed description of the concatenation PWM Function.

## NOTE

Change these bits only when both corresponding channels are disabled.

# NOTE

In single-wire operation data from the TXD pin is inverted if RXPOL is set.

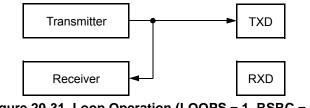

# 20.4.8 Loop Operation

In loop operation the transmitter output goes to the receiver input. The RXD pin is disconnected from the SCI.

Figure 20-31. Loop Operation (LOOPS = 1, RSRC = 0)

Enable loop operation by setting the LOOPS bit and clearing the RSRC bit in SCI control register 1 (SCICR1). Setting the LOOPS bit disables the path from the RXD pin to the receiver. Clearing the RSRC bit connects the transmitter output to the receiver input. Both the transmitter and receiver must be enabled (TE = 1 and RE = 1).

## NOTE

In loop operation data from the transmitter is not recognized by the receiver if RXPOL and TXPOL are not the same.

# 20.5 Initialization/Application Information

# 20.5.1 Reset Initialization

See Section 20.3.2, "Register Descriptions".

# 20.5.2 Modes of Operation

# 20.5.2.1 Run Mode

Normal mode of operation.

To initialize a SCI transmission, see Section 20.4.5.2, "Character Transmission".

# 20.5.2.2 Wait Mode

SCI operation in wait mode depends on the state of the SCISWAI bit in the SCI control register 1 (SCICR1).

- If SCISWAI is clear, the SCI operates normally when the CPU is in wait mode.

- If SCISWAI is set, SCI clock generation ceases and the SCI module enters a power-conservation state when the CPU is in wait mode. Setting SCISWAI does not affect the state of the receiver enable bit, RE, or the transmitter enable bit, TE.

- Fast sector erase and phrase program operation

- Ability to read the P-Flash memory while programming a word in the EEPROM memory

- Flexible protection scheme to prevent accidental program or erase of P-Flash memory

# 24.1.2.2 EEPROM Features

- 512 bytes of EEPROM memory composed of one 512 byte Flash block divided into 128 sectors of 4 bytes

- Single bit fault correction and double bit fault detection within a word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and word program operation

- Protection scheme to prevent accidental program or erase of EEPROM memory

- Ability to program up to four words in a burst sequence

# 24.1.2.3 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

# 24.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 24-1.

#### 16 KByte Flash Module (S12FTMRG16K1V1)

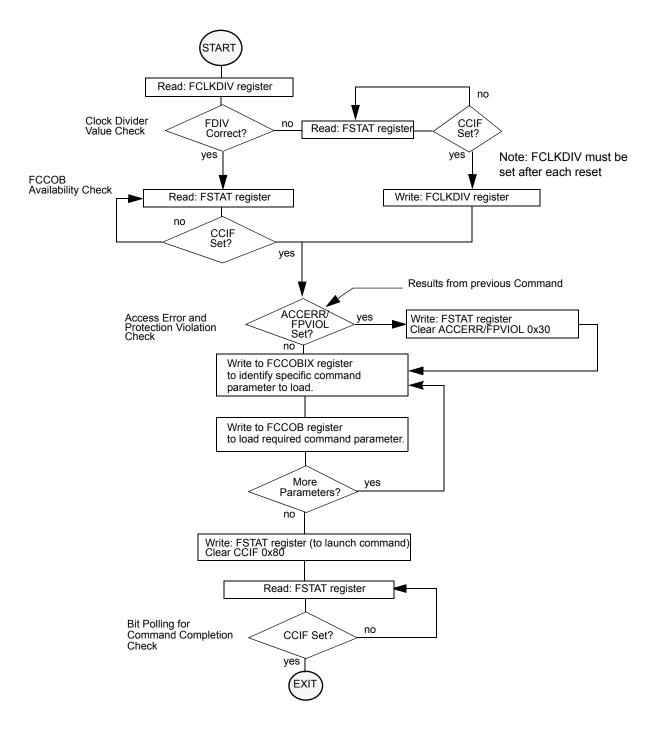

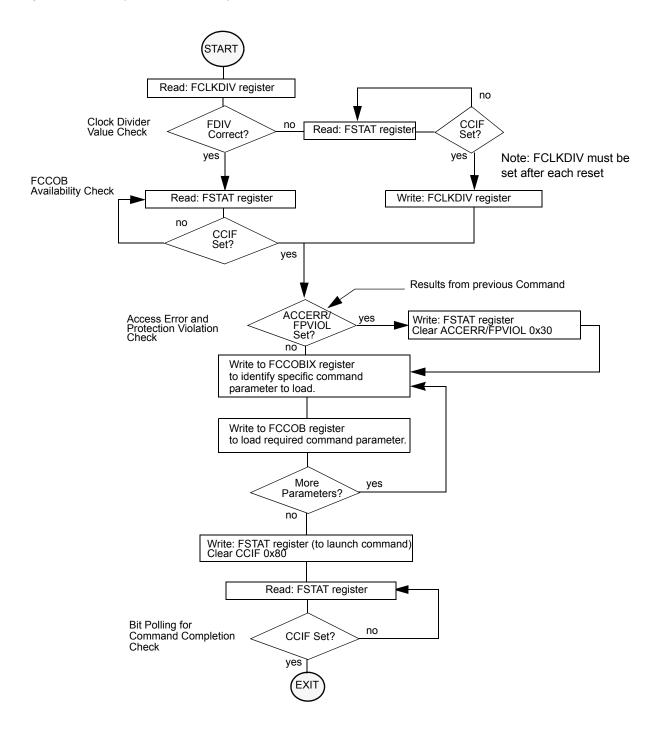

Figure 24-25. Generic Flash Command Write Sequence Flowchart

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIF          | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command completion or command violation.</li> <li>O Flash command in progress</li> <li>1 Flash command has completed</li> </ul>                                                                                                                                          |

| 5<br>ACCERR        | Flash Access Error Flag — The ACCERR bit indicates an illegal access has occurred to the Flash memory caused by either a violation of the command write sequence (see Section 25.4.4.2) or issuing an illegal Flash command. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR.<br>0 No access error detected<br>1 Access error detected       |

| 4<br>FPVIOL        | Flash Protection Violation Flag —The FPVIOL bit indicates an attempt was made to program or erase an address in a protected area of P-Flash or EEPROM memory during a command write sequence. The FPVIOL bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL is set, it is not possible to launch a command or start a command write sequence.<br>0 No protection violation detected<br>1 Protection violation detected |

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                                                                                                                                                                                                             |

| 2<br>RSVD          | <b>Reserved Bit</b> — This bit is reserved and always reads 0.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 25.4.6, "Flash Command Description," and Section 25.6, "Initialization" for details.                                                                                                                                                                                  |

### Table 25-15. FSTAT Field Descriptions

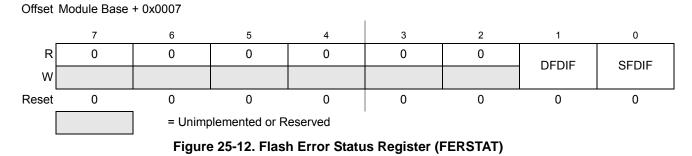

# 25.3.2.8 Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

All flags in the FERSTAT register are readable and only writable to clear the flag.

#### 32 KByte Flash Module (S12FTMRG32K1V1)

## CAUTION

The FCLKDIV register should never be written while a Flash command is executing (CCIF=0).

### Table 26-7. FCLKDIV Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written since the last reset<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                   |

| 6<br>FDIVLCK     | <ul> <li>Clock Divider Locked</li> <li>FDIV field is open for writing</li> <li>FDIV value is locked and cannot be changed. Once the lock bit is set high, only reset can clear this bit and restore writability to the FDIV field in normal mode.</li> </ul>                                                                       |

| 5–0<br>FDIV[5:0] | <b>Clock Divider Bits</b> — FDIV[5:0] must be set to effectively divide BUSCLK down to 1 MHz to control timed events during Flash program and erase algorithms. Table 26-8 shows recommended values for FDIV[5:0] based on the BUSCLK frequency. Please refer to Section 26.4.4, "Flash Command Operations," for more information. |

| BUSCLK Frequency<br>(MHz) |                  | FDIV[5:0] | BUSCLK Frequency<br>(MHz) |                  | FDIV[5:0] |

|---------------------------|------------------|-----------|---------------------------|------------------|-----------|

| MIN <sup>1</sup>          | MAX <sup>2</sup> |           | MIN <sup>1</sup>          | MAX <sup>2</sup> |           |

| 1.0                       | 1.6              | 0x00      | 16.6                      | 17.6             | 0x10      |

| 1.6                       | 2.6              | 0x01      | 17.6                      | 18.6             | 0x11      |

| 2.6                       | 3.6              | 0x02      | 18.6                      | 19.6             | 0x12      |

| 3.6                       | 4.6              | 0x03      | 19.6                      | 20.6             | 0x13      |

| 4.6                       | 5.6              | 0x04      | 20.6                      | 21.6             | 0x14      |

| 5.6                       | 6.6              | 0x05      | 21.6                      | 22.6             | 0x15      |

| 6.6                       | 7.6              | 0x06      | 22.6                      | 23.6             | 0x16      |

| 7.6                       | 8.6              | 0x07      | 23.6                      | 24.6             | 0x17      |

| 8.6                       | 9.6              | 0x08      | 24.6                      | 25.6             | 0x18      |

| 9.6                       | 10.6             | 0x09      |                           |                  |           |

| 10.6                      | 11.6             | 0x0A      |                           |                  |           |

| 11.6                      | 12.6             | 0x0B      |                           |                  |           |

| 12.6                      | 13.6             | 0x0C      |                           |                  |           |

| 13.6                      | 14.6             | 0x0D      |                           |                  |           |

| 14.6                      | 15.6             | 0x0E      |                           |                  |           |

| 15.6                      | 16.6             | 0x0F      |                           |                  |           |

#### Table 26-8. FDIV values for various BUSCLK Frequencies

<sup>1</sup> BUSCLK is Greater Than this value.

<sup>2</sup> BUSCLK is Less Than or Equal to this value.

#### 48 KByte Flash Module (S12FTMRG48K1V1)

Trying to alter data in any protected area in the P-Flash memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. The block erase of a P-Flash block is not possible if any of the P-Flash sectors contained in the same P-Flash block are protected.

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FPOPEN      | <ul> <li>Flash Protection Operation Enable — The FPOPEN bit determines the protection function for program or erase operations as shown in Table 26-18 for the P-Flash block.</li> <li>When FPOPEN is clear, the FPHDIS and FPLDIS bits define unprotected address ranges as specified by the corresponding FPHS and FPLS bits</li> <li>When FPOPEN is set, the FPHDIS and FPLDIS bits enable protection for the address range specified by the corresponding FPHS and FPLS bits</li> </ul> |

| 6<br>RNV[6]      | <b>Reserved Nonvolatile Bit</b> — The RNV bit should remain in the erased state for future enhancements.                                                                                                                                                                                                                                                                                                                                                                                    |

| 5<br>FPHDIS      | Flash Protection Higher Address Range Disable — The FPHDIS bit determines whether there is a protected/unprotected area in a specific region of the P-Flash memory ending with global address 0x3_FFFF. 0 Protection/Unprotection enabled 1 Protection/Unprotection disabled                                                                                                                                                                                                                |

| 4–3<br>FPHS[1:0] | <b>Flash Protection Higher Address Size</b> — The FPHS bits determine the size of the protected/unprotected area in P-Flash memory as shown inTable 26-19. The FPHS bits can only be written to while the FPHDIS bit is set.                                                                                                                                                                                                                                                                |

| 2<br>FPLDIS      | Flash Protection Lower Address Range Disable — The FPLDIS bit determines whether there is a protected/unprotected area in a specific region of the P-Flash memory beginning with global address 0x3_8000.<br>0 Protection/Unprotection enabled<br>1 Protection/Unprotection disabled                                                                                                                                                                                                        |

| 1–0<br>FPLS[1:0] | <b>Flash Protection Lower Address Size</b> — The FPLS bits determine the size of the protected/unprotected area in P-Flash memory as shown in Table 26-20. The FPLS bits can only be written to while the FPLDIS bit is set.                                                                                                                                                                                                                                                                |

#### Table 26-17. FPROT Field Descriptions

| Table 26-18. P-Flash Protection Function |

|------------------------------------------|

|                                          |

| FPOPEN | FPHDIS | FPLDIS | Function <sup>1</sup>           |  |

|--------|--------|--------|---------------------------------|--|

| 1      | 1      | 1      | No P-Flash Protection           |  |

| 1      | 1      | 0      | Protected Low Range             |  |

| 1      | 0      | 1      | Protected High Range            |  |

| 1      | 0      | 0      | Protected High and Low Ranges   |  |

| 0      | 1      | 1      | Full P-Flash Memory Protected   |  |

| 0      | 1      | 0      | Unprotected Low Range           |  |

| 0      | 0      | 1      | Unprotected High Range          |  |

| 0      | 0      | 0      | Unprotected High and Low Ranges |  |

<sup>1</sup> For range sizes, refer to Table 26-19 and Table 26-20.

| Field | Description                                                                                                                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Nonvolatile Bits</b> — The NV[7:0] bits are available as nonvolatile bits. Refer to the device user guide for proper use of the NV bits. |

#### Table 28-25. FOPT Field Descriptions

# 28.3.2.17 Flash Reserved5 Register (FRSV5)

This Flash register is reserved for factory testing.

All bits in the FRSV5 register read 0 and are not writable.

# 28.3.2.18 Flash Reserved6 Register (FRSV6)

This Flash register is reserved for factory testing.

Figure 28-24. Flash Reserved6 Register (FRSV6)

All bits in the FRSV6 register read 0 and are not writable.

# 28.3.2.19 Flash Reserved7 Register (FRSV7)

This Flash register is reserved for factory testing.

#### 240 KByte Flash Module (S12FTMRG240K2V1)

Figure 31-26. Generic Flash Command Write Sequence Flowchart