Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | 12V1                                                                  |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 40                                                                    |

| Program Memory Size        | 96KB (96K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 3K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g96f0vlf |

| 5.2 | External Signal Description                     | 261 |

|-----|-------------------------------------------------|-----|

| 5.3 | Memory Map and Registers                        |     |

|     | 5.3.1 Module Memory Map                         | 261 |

|     | 5.3.2 Register Descriptions                     | 262 |

| 5.4 | Functional Description                          |     |

|     | 5.4.1 MCU Operating Modes                       | 266 |

|     | 5.4.2 Memory Map Scheme                         |     |

|     | 5.4.3 Unimplemented and Reserved Address Ranges |     |

|     | 5.4.4 Prioritization of Memory Accesses         |     |

|     | 5.4.5 Interrupts                                |     |

|     | Chapter 6                                       |     |

|     | Interrupt Module (S12SINTV1)                    |     |

| 6.1 | Introduction                                    | 273 |

|     | 6.1.1 Glossary                                  | 273 |

|     | 6.1.2 Features                                  | 273 |

|     | 6.1.3 Modes of Operation                        | 274 |

|     | 6.1.4 Block Diagram                             | 274 |

| 6.2 | External Signal Description                     |     |

| 6.3 | Memory Map and Register Definition              |     |

|     | 6.3.1 Register Descriptions                     |     |

| 6.4 | Functional Description                          |     |

|     | 6.4.1 S12S Exception Requests                   | 276 |

|     | 6.4.2 Interrupt Prioritization                  | 276 |

|     | 6.4.3 Reset Exception Requests                  | 277 |

|     | 6.4.4 Exception Priority                        | 277 |

| 6.5 | Initialization/Application Information          | 278 |

|     | 6.5.1 Initialization                            | 278 |

|     | 6.5.2 Interrupt Nesting                         | 278 |

|     | 6.5.3 Wake Up from Stop or Wait Mode            | 278 |

|     | Chapter 7                                       |     |

|     | Background Debug Module (S12SBDMV1)             |     |

| 7.1 | Introduction                                    |     |

|     | 7.1.1 Features                                  |     |

|     | 7.1.2 Modes of Operation                        |     |

|     | 7.1.3 Block Diagram                             |     |

| 7.2 | External Signal Description                     |     |

| 7.3 | Memory Map and Register Definition              |     |

|     | 7.3.1 Module Memory Map                         |     |

|     | 7.3.2 Register Descriptions                     |     |

|     | 7.3.3 Family ID Assignment                      |     |

| 7.4 | Functional Description                          |     |

|     | 7.4.1 Security                                  | 288 |

|     |                                                 |     |

Table 1-21. 64-Pin LQFP Pinout for S12G96 and S12G128

|             |                  | <lowest< th=""><th>Function<br/>-PRIORITY-</th><th>highest&gt;</th><th>&gt;</th><th>Power</th><th>Internal F<br/>Resisto</th><th></th></lowest<> | Function<br>-PRIORITY- | highest>       | >           | Power            | Internal F<br>Resisto |                |

|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|-------------|------------------|-----------------------|----------------|

| Package Pin | Pin              | 2nd<br>Func.                                                                                                                                     | 3rd<br>Func.           | 4th<br>Func    | 5th<br>Func | Supply           | CTRL                  | Reset<br>State |

| 1           | PJ6              | KWJ6                                                                                                                                             | SCK2                   | _              | _           | $V_{DDX}$        | PERJ/PPSJ             | Up             |

| 2           | PJ5              | KWJ5                                                                                                                                             | MOSI2                  | _              | _           | $V_{DDX}$        | PERJ/PPSJ             | Up             |

| 3           | PJ4              | KWJ4                                                                                                                                             | MISO2                  | _              | _           | $V_{DDX}$        | PERJ/PPSJ             | Up             |

| 4           | RESET            | _                                                                                                                                                | _                      | _              | _           | $V_{DDX}$        | PULLUI                | P              |

| 5           | VDDX             |                                                                                                                                                  | _                      | _              | _           | _                | _                     | _              |

| 6           | VDDR             |                                                                                                                                                  | _                      | _              | _           | _                | _                     | _              |

| 7           | VSSX             |                                                                                                                                                  | _                      | _              | _           | _                | _                     | _              |

| 8           | PE0 <sup>1</sup> | EXTAL                                                                                                                                            | _                      | _              | _           | $V_{DDX}$        | PUCR/PDPEE            | Down           |

| 9           | VSS              | _                                                                                                                                                | _                      | _              | _           | _                | _                     | _              |

| 10          | PE1 <sup>1</sup> | XTAL                                                                                                                                             | _                      | _              | _           | $V_{DDX}$        | PUCR/PDPEE            | Down           |

| 11          | TEST             | _                                                                                                                                                | _                      | _              | _           | N.A.             | RESET pin Down        |                |

| 12          | PJ0              | KWJ0                                                                                                                                             | MISO1                  | _              | _           | $V_{DDX}$        | PERJ/PPSJ             | Up             |

| 13          | PJ1              | KWJ1                                                                                                                                             | MOSI1                  | _              | _           | $V_{DDX}$        | PERJ/PPSJ             | Up             |

| 14          | PJ2              | KWJ2                                                                                                                                             | SCK1                   | _              | _           | $V_{DDX}$        | PERJ/PPSJ             | Up             |

| 15          | PJ3              | KWJ3                                                                                                                                             | SS1                    | _              | _           | $V_{DDX}$        | PERJ/PPSJ Up          |                |

| 16          | BKGD             | MODC                                                                                                                                             | _                      | _              | _           | $V_{DDX}$        | PUCR/BKPUE Up         |                |

| 17          | PP0              | KWP0                                                                                                                                             | ETRIG0                 | API_EXTC<br>LK | PWM0        | V <sub>DDX</sub> | PERP/PPSP Disabled    |                |

| 18          | PP1              | KWP1                                                                                                                                             | ETRIG1                 | ECLKX2         | PWM1        | $V_{DDX}$        | PERP/PPSP             | Disabled       |

| 19          | PP2              | KWP2                                                                                                                                             | ETRIG2                 | PWM2           | _           | $V_{DDX}$        | PERP/PPSP             | Disabled       |

| 20          | PP3              | KWP3                                                                                                                                             | ETRIG3                 | PWM3           | _           | $V_{DDX}$        | PERP/PPSP             | Disabled       |

| 21          | PP4              | KWP4                                                                                                                                             | PWM4                   | _              | _           | $V_{DDX}$        | PERP/PPSP             | Disabled       |

| 22          | PP5              | KWP5                                                                                                                                             | PWM5                   | _              | _           | $V_{DDX}$        | PERP/PPSP             | Disabled       |

| 23          | PP6              | KWP6                                                                                                                                             | PWM6                   | _              | _           | $V_{DDX}$        | PERP/PPSP             | Disabled       |

| 24          | PP7              | KWP7                                                                                                                                             | PWM7                   | _              | _           | $V_{DDX}$        | PERP/PPSP             | Disabled       |

| 25          | PT7              | IOC7                                                                                                                                             | _                      | _              | _           | $V_{DDX}$        | PERT/PPST Disabled    |                |

| 26          | PT6              | IOC6                                                                                                                                             | _                      | _              | _           | $V_{DDX}$        | PERT/PPST             | Disabled       |

| 27          | PT5              | IOC5                                                                                                                                             | _                      | _              | _           | $V_{DDX}$        | PERT/PPST             | Disabled       |

Table 1-31. 100-Pin LQFP Pinout for S12GA192 and S12GA240

|             | < ı   | Fund<br>owestPRIO | Power        | Internal F<br>Resisto |                  |            |                |

|-------------|-------|-------------------|--------------|-----------------------|------------------|------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.      | 3rd<br>Func. | 4th<br>Func.          | Supply           | CTRL       | Reset<br>State |

| 86          | PS4   | MISO0             | _            | _                     | V <sub>DDX</sub> | PERS/PPSS  | Up             |

| 87          | PS5   | MOSI0             | _            | _                     | V <sub>DDX</sub> | PERS/PPSS  | Up             |

| 88          | PS6   | SCK0              | _            |                       | V <sub>DDX</sub> | PERS/PPSS  | Up             |

| 89          | PS7   | API_EXTC<br>LK    | SS0          | _                     | V <sub>DDX</sub> | PERS/PPSS  | Up             |

| 90          | VSSX2 | _                 | _            | _                     | _                | _          | _              |

| 91          | VDDX2 | _                 | _            | _                     | _                | _          | _              |

| 92          | PM0   | RXCAN             | _            | _                     | V <sub>DDX</sub> | PERM/PPSM  | Disabled       |

| 93          | PM1   | TXCAN             | _            | _                     | V <sub>DDX</sub> | PERM/PPSM  | Disabled       |

| 94          | PD4   | _                 | _            | _                     | V <sub>DDX</sub> | PUCR/PUPDE | Disabled       |

| 95          | PD5   | _                 | _            | _                     | V <sub>DDX</sub> | PUCR/PUPDE | Disabled       |

| 96          | PD6   | _                 | _            | _                     | V <sub>DDX</sub> | PUCR/PUPDE | Disabled       |

| 97          | PD7   | _                 | _            | _                     | V <sub>DDX</sub> | PUCR/PUPDE | Disabled       |

| 98          | PM2   | RXD2              | _            | _                     | V <sub>DDX</sub> | PERM/PPSM  | Disabled       |

| 99          | PM3   | TXD2              | _            | _                     | V <sub>DDX</sub> | PERM/PPSM  | Disabled       |

| 100         | PJ7   | KWJ7              | SS2          | _                     | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

<sup>&</sup>lt;sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

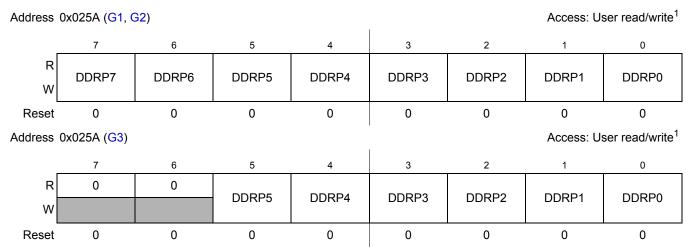

## 2.4.3.36 Port P Data Direction Register (DDRP)

Figure 2-37. Port P Data Direction Register (DDRP)

Table 2-63. DDRP Register Field Descriptions

| Field       | Description                                                                                  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------|--|--|--|

| 7-0<br>DDRP | Port P data direction— This bit determines whether the associated pin is an input or output. |  |  |  |

|             | Associated pin configured as output     Associated pin configured as input                   |  |  |  |

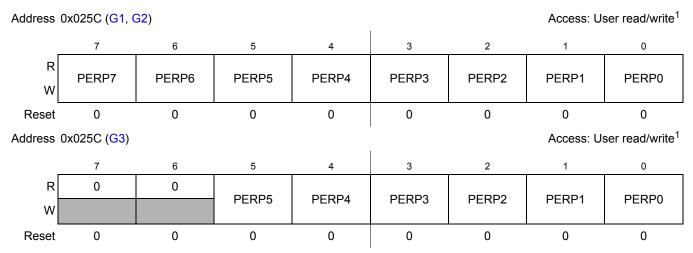

# 2.4.3.37 Port P Pull Device Enable Register (PERP)

Figure 2-38. Port P Pull Device Enable Register (PERP)

MC9S12G Family Reference Manual Rev.1.27

Read: Anytime Write: Anytime

Read: Anytime Write: Anytime

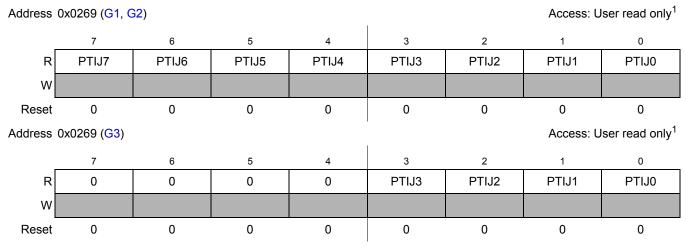

# 2.4.3.43 Port J Input Register (PTIJ)

Figure 2-43. Port J Input Register (PTIJ)

Table 2-69. PTIJ Register Field Descriptions

| Field       | Description                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PTIJ | Port J input data— A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

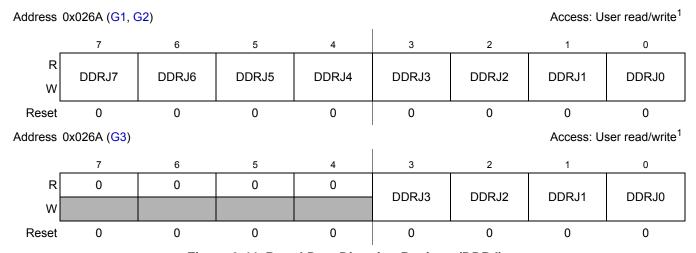

# 2.4.3.44 Port J Data Direction Register (DDRJ)

Figure 2-44. Port J Data Direction Register (DDRJ)

MC9S12G Family Reference Manual Rev.1.27

Read: Anytime Write: Never

Read: Anytime Write: Anytime

# 2.5 PIM Ports - Functional Description

#### 2.5.1 General

Each pin except BKGD can act as general-purpose I/O. In addition most pins can act as an output or input of a peripheral module.

# 2.5.2 Registers

A set of configuration registers is common to all ports with exception of the ADC port (Table 2-91). All registers can be written at any time, however a specific configuration might not become active.

Example: Selecting a pullup device. This device does not become active while the port is used as a push-pull output.

| Port | Data<br>(Portx,<br>PTx) | Input<br>(PTIx) | Data<br>Direction<br>(DDRx) | Pull<br>Enable<br>(PERx) | Polarity<br>Select<br>(PPSx) | Wired-<br>Or Mode<br>(WOMx) | Interrupt<br>Enable<br>(PIEx) | Interrupt<br>Flag<br>(PIFx) |

|------|-------------------------|-----------------|-----------------------------|--------------------------|------------------------------|-----------------------------|-------------------------------|-----------------------------|

| Α    | yes                     | -               | yes                         |                          | -                            | -                           | -                             | -                           |

| В    | yes                     | -               | yes                         |                          | -                            | -                           | -                             | -                           |

| С    | yes                     | -               | yes                         | yes                      | -                            | -                           | -                             | -                           |

| D    | yes                     | -               | yes                         |                          | -                            | -                           | -                             | -                           |

| Е    | yes                     | -               | yes                         |                          | -                            | -                           | -                             | -                           |

| Т    | yes                     | yes             | yes                         | yes                      | yes                          | -                           | -                             | -                           |

| S    | yes                     | yes             | yes                         | yes                      | yes                          | yes                         | -                             | -                           |

| М    | yes                     | yes             | yes                         | yes                      | yes                          | yes                         | -                             | -                           |

| Р    | yes                     | yes             | yes                         | yes                      | yes                          | -                           | yes                           | yes                         |

| J    | yes                     | yes             | yes                         | yes                      | yes                          | -                           | yes                           | yes                         |

| AD   | yes                     | yes             | yes                         | yes                      | yes                          | -                           | yes                           | yes                         |

Table 2-91. Register availability per port<sup>1</sup>

# 2.5.2.1 Data Register (PORTx, PTx)

This register holds the value driven out to the pin if the pin is used as a general-purpose I/O.

Writing to this register has only an effect on the pin if the pin is used as general-purpose output. When reading this address, the buffered state of the pin is returned if the associated data direction register bit is set to 0.

If the data direction register bits are set to 1, the contents of the data register is returned. This is independent of any other configuration (Figure 2-64).

# 2.5.2.2 Input Register (PTIx)

This register is read-only and always returns the buffered state of the pin (Figure 2-64).

NXP Semiconductors 241

#### MC9S12G Family Reference Manual Rev.1.27

<sup>&</sup>lt;sup>1</sup> Each cell represents one register with individual configuration bits

## 8.4.6 Tagging

A tag follows program information as it advances through the instruction queue. When a tagged instruction reaches the head of the queue a tag hit occurs and can initiate a state sequencer transition.

Each comparator control register features a TAG bit, which controls whether the comparator match causes a state sequencer transition immediately or tags the opcode at the matched address. If a comparator is enabled for tagged comparisons, the address stored in the comparator match address registers must be an opcode address.

Using Begin trigger together with tagging, if the tagged instruction is about to be executed then the transition to the next state sequencer state occurs. If the transition is to the Final State, tracing is started. Only upon completion of the tracing session can a breakpoint be generated. Using End alignment, when the tagged instruction is about to be executed and the next transition is to Final State then a breakpoint is generated immediately, before the tagged instruction is carried out.

R/W monitoring, access size (SZ) monitoring and data bus monitoring are not useful if tagging is selected, since the tag is attached to the opcode at the matched address and is not dependent on the data bus nor on the type of access. Thus these bits are ignored if tagging is selected.

When configured for range comparisons and tagging, the ranges are accurate only to word boundaries.

Tagging is disabled when the BDM becomes active.

# 8.4.7 Breakpoints

It is possible to generate breakpoints from channel transitions to final state or using software to write to the TRIG bit in the DBGC1 register.

# 8.4.7.1 Breakpoints From Comparator Channels

Breakpoints can be generated when the state sequencer transitions to the Final State. If configured for tagging, then the breakpoint is generated when the tagged opcode reaches the execution stage of the instruction queue.

If a tracing session is selected by the TSOURCE bit, breakpoints are requested when the tracing session has completed, thus if Begin aligned triggering is selected, the breakpoint is requested only on completion of the subsequent trace (see Table 8-42). If no tracing session is selected, breakpoints are requested immediately.

If the BRK bit is set, then the associated breakpoint is generated immediately independent of tracing trigger alignment.

BRKTALIGNDBGBRKBreakpoint Alignment00Fill Trace Buffer until trigger then disarm (no breakpoints)001Fill Trace Buffer until trigger, then breakpoint request occurs010Start Trace Buffer at trigger (no breakpoints)

Table 8-42. Breakpoint Setup For CPU Breakpoints

MC9S12G Family Reference Manual Rev.1.27

Table 12-13. Sample Time Select

| S | SMP2 | SMP1 | SMP0 | Sample Time<br>in Number of<br>ATD Clock Cycles |

|---|------|------|------|-------------------------------------------------|

|   | 1    | 1    | 1    | 24                                              |

# 12.3.2.6 ATD Control Register 5 (ATDCTL5)

Writes to this register will abort current conversion sequence and start a new conversion sequence. If the external trigger function is enabled (ETRIGE=1) an initial write to ATDCTL5 is required to allow starting of a conversion sequence which will then occur on each trigger event. Start of conversion means the beginning of the sampling phase.

Module Base + 0x0005

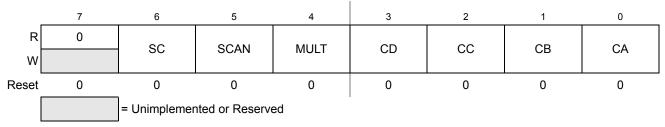

Figure 12-8. ATD Control Register 5 (ATDCTL5)

Read: Anytime Write: Anytime

Table 12-14. ATDCTL5 Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>SC   | Special Channel Conversion Bit — If this bit is set, then special channel conversion can be selected using CD, CC, CB and CA of ATDCTL5. Table 12-15 lists the coding.  O Special channel conversions disabled  Special channel conversions enabled                                                                                                                   |

| 5<br>SCAN | Continuous Conversion Sequence Mode — This bit selects whether conversion sequences are performed continuously or only once. If the external trigger function is enabled (ETRIGE=1) setting this bit has no effect, thus the external trigger always starts a single conversion sequence.  0 Single conversion sequence 1 Continuous conversion sequences (scan mode) |

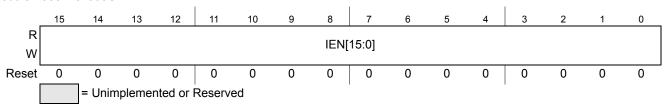

## 16.3.2.10 ATD Input Enable Register (ATDDIEN)

Module Base + 0x000C

Figure 16-12. ATD Input Enable Register (ATDDIEN)

Read: Anytime Write: Anytime

**Table 16-19. ATDDIEN Field Descriptions**

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>IEN[15:0] | <ul> <li>ATD Digital Input Enable on channel x (x= 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) — This bit controls the digital input buffer from the analog input pin (ANx) to the digital data register.</li> <li>Disable digital input buffer to ANx pin</li> <li>Enable digital input buffer on ANx pin.</li> <li>Note: Setting this bit will enable the corresponding digital input buffer continuously. If this bit is set while simultaneously using it as an analog port, there is potentially increased power consumption because the digital input buffer maybe in the linear region.</li> </ul> |

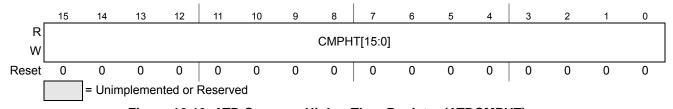

# 16.3.2.11 ATD Compare Higher Than Register (ATDCMPHT)

Writes to this register will abort current conversion sequence.

Read: Anytime

Write: Anytime

Module Base + 0x000E

Figure 16-13. ATD Compare Higher Than Register (ATDCMPHT)

**Table 16-20. ATDCMPHT Field Descriptions**

| Field       | Description                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

| 15–0        | Compare Operation Higher Than Enable for conversion number n (n= 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5,                       |

| CMPHT[15:0] | 4, 3, 2, 1, 0) of a Sequence ( <i>n conversion number, NOT channel number!</i> ) — This bit selects the operator              |

|             | for comparison of conversion results.                                                                                         |

|             | 0 If result of conversion <i>n</i> is <b>lower or same than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2 |

|             | 1 If result of conversion <i>n</i> is <b>higher than</b> compare value in ATDDR <i>n</i> , this is flagged in ATDSTAT2        |

MC9S12G Family Reference Manual Rev.1.27

Scalable Controller Area Network (S12MSCANV3)

MC9S12G Family Reference Manual Rev.1.27

622

NXP Semiconductors

Table 20-11. SCISR1 Field Descriptions (continued)

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>FE | Framing Error Flag — FE is set when a logic 0 is accepted as the stop bit. FE bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. FE inhibits further data reception until it is cleared. Clear FE by reading SCI status register 1 (SCISR1) with FE set and then reading the SCI data register low (SCIDRL).  0 No framing error  1 Framing error |

| 0<br>PF | Parity Error Flag — PF is set when the parity enable bit (PE) is set and the parity of the received data does not match the parity type bit (PT). PF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear PF by reading SCI status register 1 (SCISR1), and then reading SCI data register low (SCIDRL).  0 No parity error  1 Parity error   |

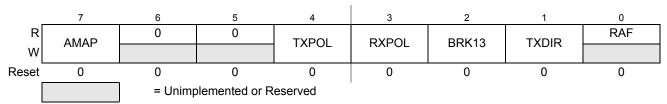

# 20.3.2.8 SCI Status Register 2 (SCISR2)

Module Base + 0x0005

Figure 20-11. SCI Status Register 2 (SCISR2)

Read: Anytime Write: Anytime

Table 20-12. SCISR2 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>AMAP  | Alternative Map — This bit controls which registers sharing the same address space are accessible. In the reset condition the SCI behaves as previous versions. Setting AMAP=1 allows the access to another set of control and status registers and hides the baud rate and SCI control Register 1.  0 The registers labelled SCIBDH (0x0000),SCIBDL (0x0001), SCICR1 (0x0002) are accessible 1 The registers labelled SCIASR1 (0x0000),SCIACR1 (0x0001), SCIACR2 (0x00002) are accessible                                             |

| 4<br>TXPOL | Transmit Polarity — This bit control the polarity of the transmitted data. In NRZ format, a one is represented by a mark and a zero is represented by a space for normal polarity, and the opposite for inverted polarity. In IrDA format, a zero is represented by short high pulse in the middle of a bit time remaining idle low for a one for normal polarity, and a zero is represented by short low pulse in the middle of a bit time remaining idle high for a one for inverted polarity.  O Normal polarity  Inverted polarity |

#### Serial Peripheral Interface (S12SPIV5)

The main element of the SPI system is the SPI data register. The n-bit<sup>1</sup> data register in the master and the n-bit<sup>1</sup> data register in the slave are linked by the MOSI and MISO pins to form a distributed 2n-bit<sup>1</sup> register. When a data transfer operation is performed, this 2n-bit<sup>1</sup> register is serially shifted n<sup>1</sup> bit positions by the S-clock from the master, so data is exchanged between the master and the slave. Data written to the master SPI data register becomes the output data for the slave, and data read from the master SPI data register a transfer operation is the input data from the slave.

A read of SPISR with SPTEF = 1 followed by a write to SPIDR puts data into the transmit data register. When a transfer is complete and SPIF is cleared, received data is moved into the receive data register. This data register acts as the SPI receive data register for reads and as the SPI transmit data register for writes. A common SPI data register address is shared for reading data from the read data buffer and for writing data to the transmit data register.

The clock phase control bit (CPHA) and a clock polarity control bit (CPOL) in the SPI control register 1 (SPICR1) select one of four possible clock formats to be used by the SPI system. The CPOL bit simply selects a non-inverted or inverted clock. The CPHA bit is used to accommodate two fundamentally different protocols by sampling data on odd numbered SCK edges or on even numbered SCK edges (see Section 21.4.3, "Transmission Formats").

The SPI can be configured to operate as a master or as a slave. When the MSTR bit in SPI control register1 is set, master mode is selected, when the MSTR bit is clear, slave mode is selected.

#### NOTE

A change of CPOL or MSTR bit while there is a received byte pending in the receive shift register will destroy the received byte and must be avoided.

## 21.4.1 Master Mode

The SPI operates in master mode when the MSTR bit is set. Only a master SPI module can initiate transmissions. A transmission begins by writing to the master SPI data register. If the shift register is empty, data immediately transfers to the shift register. Data begins shifting out on the MOSI pin under the control of the serial clock.

- Serial clock

- The SPR2, SPR1, and SPR0 baud rate selection bits, in conjunction with the SPPR2, SPPR1, and SPPR0 baud rate preselection bits in the SPI baud rate register, control the baud rate generator and determine the speed of the transmission. The SCK pin is the SPI clock output. Through the SCK pin, the baud rate generator of the master controls the shift register of the slave peripheral.

- MOSI, MISO pin

In master mode, the function of the serial data output pin (MOSI) and the serial data input pin (MISO) is determined by the SPC0 and BIDIROE control bits.

- $\overline{SS}$  pin

If MODFEN and SSOE are set, the  $\overline{SS}$  pin is configured as slave select output. The  $\overline{SS}$  output becomes low during each transmission and is high when the SPI is in idle state.

MC9S12G Family Reference Manual Rev.1.27

<sup>1.</sup> n depends on the selected transfer width, please refer to Section 21.3.2.2, "SPI Control Register 2 (SPICR2)

# Chapter 22 Timer Module (TIM16B6CV3)

**Table 22-1. Revision History**

| V03.00 | Jan. 28, 2009 |                                                     | Initial version                                                                                                                                                                                                                   |

|--------|---------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V03.01 | Aug. 26, 2009 | 22.1.2/22-720<br>22.3.2.2/22-723,<br>22.4.3/22-735  | - Correct typo: TSCR ->TSCR1; - Correct typo: ECTxxx->TIMxxx - Add description, "a counter overflow when TTOV[7] is set", to be the condition of channel 7 override event Phrase the description of OC7M to make it more explicit |

| V03.02 | Apri,12,2010  | 22.3.2.6/22-726<br>22.3.2.9/22-728<br>22.4.3/22-735 | -update TCRE bit description                                                                                                                                                                                                      |

| V03.03 | Jan,14,2013   |                                                     | -single source generate different channel guide                                                                                                                                                                                   |

### 22.1 Introduction

The basic scalable timer consists of a 16-bit, software-programmable counter driven by a flexible programmable prescaler.

This timer can be used for many purposes, including input waveform measurements while simultaneously generating an output waveform.

This timer could contain up to 6 input capture/output compare channels. The input capture function is used to detect a selected transition edge and record the time. The output compare function is used for generating output signals or for timer software delays.

A full access for the counter registers or the input capture/output compare registers should take place in one clock cycle. Accessing high byte and low byte separately for all of these registers may not yield the same result as accessing them in one word.

### 22.1.1 Features

The TIM16B6CV3 includes these distinctive features:

- Up to 6 channels available. (refer to device specification for exact number)

- All channels have same input capture/output compare functionality.

- Clock prescaling.

- 16-bit counter.

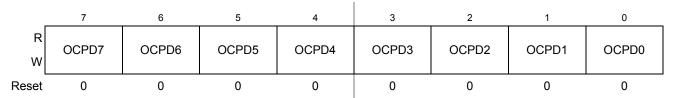

# 23.3.2.18 Output Compare Pin Disconnect Register(OCPD)

Module Base + 0x002C

Figure 23-28. Output Compare Pin Disconnect Register (OCPD)

Read: Anytime

Write: Anytime

All bits reset to zero.

#### Table 23-22. OCPD Field Description

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field            | Description                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OCPD[7:0] | Output Compare Pin Disconnect Bits  0 Enables the timer channel port. Output Compare action will occur on the channel pin. These bits do not affect the input capture or pulse accumulator functions.  1 Disables the timer channel port. Output Compare action will not occur on the channel pin, but the output compare flag still become set. |

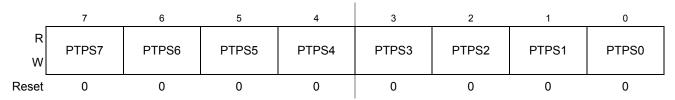

# 23.3.2.19 Precision Timer Prescaler Select Register (PTPSR)

Module Base + 0x002E

Figure 23-29. Precision Timer Prescaler Select Register (PTPSR)

Read: Anytime Write: Anytime

All bits reset to zero.

**Table 24-15. FSTAT Field Descriptions**

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIF          | Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command completion or command violation.  0 Flash command in progress 1 Flash command has completed                                                                                                                                                                           |

| 5<br>ACCERR        | Flash Access Error Flag — The ACCERR bit indicates an illegal access has occurred to the Flash memory caused by either a violation of the command write sequence (see Section 24.4.4.2) or issuing an illegal Flash command. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR.  0 No access error detected  1 Access error detected       |

| 4<br>FPVIOL        | Flash Protection Violation Flag —The FPVIOL bit indicates an attempt was made to program or erase an address in a protected area of P-Flash or EEPROM memory during a command write sequence. The FPVIOL bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL is set, it is not possible to launch a command or start a command write sequence.  0 No protection violation detected  1 Protection violation detected |

| 3<br>MGBUSY        | Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.  0 Memory Controller is idle 1 Memory Controller is busy executing a Flash command (CCIF = 0)                                                                                                                                                                                                                                                                              |

| 2<br>RSVD          | Reserved Bit — This bit is reserved and always reads 0.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 24.4.6, "Flash Command Description," and Section 24.6, "Initialization" for details.                                                                                                                                                                              |

# 24.3.2.8 Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

Offset Module Base + 0x0007

Figure 24-12. Flash Error Status Register (FERSTAT)

All flags in the FERSTAT register are readable and only writable to clear the flag.

Table 26-4. Flash Configuration Field

| Global Address                 | Size<br>(Bytes) | Description                                                                                                                                                  |

|--------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x3_FF00-0x3_FF07              | 8               | Backdoor Comparison Key Refer to Section 26.4.6.11, "Verify Backdoor Access Key Command," and Section 26.5.1, "Unsecuring the MCU using Backdoor Key Access" |

| 0x3_FF08-0x3_FF0B <sup>1</sup> | 4               | Reserved                                                                                                                                                     |

| 0x3_FF0C <sup>1</sup>          | 1               | P-Flash Protection byte.<br>Refer to Section 26.3.2.9, "P-Flash Protection Register (FPROT)"                                                                 |

| 0x3_FF0D <sup>1</sup>          | 1               | EEPROM Protection byte. Refer to Section 26.3.2.10, "EEPROM Protection Register (EEPROT)"                                                                    |

| 0x3_FF0E <sup>1</sup>          | 1               | Flash Nonvolatile byte<br>Refer to Section 26.3.2.16, "Flash Option Register (FOPT)"                                                                         |

| 0x3_FF0F <sup>1</sup>          | 1               | Flash Security byte<br>Refer to Section 26.3.2.2, "Flash Security Register (FSEC)"                                                                           |

<sup>1 0</sup>x3FF08-0x3\_FF0F form a Flash phrase and must be programmed in a single command write sequence. Each byte in the 0x3\_FF08 - 0x3\_FF0B reserved field should be programmed to 0xFF.

Table 26-63. Program EEPROM Command Error Handling

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] < 010 at command launch                                          |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |

|          |           | Set if command not available in current mode (see Table 26-27)                      |

|          |           | Set if an invalid global address [17:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

| . •      |           | Set if the requested group of words breaches the end of the EEPROM block            |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

### 26.4.6.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

Table 26-64. Erase EEPROM Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                             |                                                 |

|-------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 000         | 0x12                                                                                                         | Global address [17:16] to identify EEPROM block |

| 001         | Global address [15:0] anywhere within the sector to be erased.  See Section 26.1.2.2 for EEPROM sector size. |                                                 |

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

Table 26-65. Erase EEPROM Sector Command Error Handling

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 26-27)                      |

|          |           | Set if an invalid global address [17:0] is suppliedsee Table 26-3)                  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Upon clearing CCIF to launch the Read Once command, a Read Once phrase is fetched and stored in the FCCOB indexed register. The CCIF flag will set after the Read Once operation has completed. Valid phrase index values for the Read Once command range from 0x0000 to 0x0007. During execution of the Read Once command, any attempt to read addresses within P-Flash block will return invalid data.

|  | Table | 31-39. Read Once Command Error Handling |

|--|-------|-----------------------------------------|

|  |       |                                         |

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                             |

|          |           | Set if command not available in current mode (see Table 31-27)          |

| FSTAT    |           | Set if an invalid phrase index is supplied                              |

| FSIAI    | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

## 31.4.6.5 Program P-Flash Command

The Program P-Flash operation will program a previously erased phrase in the P-Flash memory using an embedded algorithm.

#### CAUTION

A P-Flash phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash phrase is not allowed.

Table 31-40. Program P-Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                       |                                                  |  |

|-------------|------------------------------------------------------------------------|--------------------------------------------------|--|

| 000         | 0x06                                                                   | Global address [17:16] to identify P-Flash block |  |

| 001         | Global address [15:0] of phrase location to be programmed <sup>1</sup> |                                                  |  |

| 010         | Word 0 program value                                                   |                                                  |  |

| 011         | Word 1 pro                                                             | gram value                                       |  |

| 100         | Word 2 program value                                                   |                                                  |  |

| 101         | Word 3 program value                                                   |                                                  |  |

<sup>1</sup> Global address [2:0] must be 000

Upon clearing CCIF to launch the Program P-Flash command, the Memory Controller will program the data words to the supplied global address and will then proceed to verify the data words read back as expected. The CCIF flag will set after the Program P-Flash operation has completed.

#### **CAUTION**

Field margin levels must only be used during verify of the initial factory programming.

#### **NOTE**

Field margin levels can be used to check that Flash memory contents have adequate margin for data retention at the normal level setting. If unexpected results are encountered when checking Flash memory contents at field margin levels, the Flash memory contents should be erased and reprogrammed.

## 31.4.6.14 Erase Verify EEPROM Section Command

The Erase Verify EEPROM Section command will verify that a section of code in the EEPROM is erased. The Erase Verify EEPROM Section command defines the starting point of the data to be verified and the number of words.

CCOBIX[2:0]

FCCOB Parameters

000

0x10

Global address [17:16] to identify the EEPROM block

001

Global address [15:0] of the first word to be verified

010

Number of words to be verified

Table 31-60. Erase Verify EEPROM Section Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Verify EEPROM Section command, the Memory Controller will verify the selected section of EEPROM memory is erased. The CCIF flag will set after the Erase Verify EEPROM Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 31-61. Erase Verify EEPROM Section Command Error Handling

| Register | Error Bit | Error Condition                                                                                   |

|----------|-----------|---------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                                                       |

|          |           | Set if command not available in current mode (see Table 31-27)                                    |

|          |           | Set if an invalid global address [17:0] is supplied                                               |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)                            |

| FSTAT    |           | Set if the requested section breaches the end of the EEPROM block                                 |

|          | FPVIOL    | None                                                                                              |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |

**Table A-18. Pseudo Stop Current Characteristics**

| Conditions are: V <sub>DDX</sub> =5V, V <sub>DDR</sub> =5V, V <sub>DDA</sub> =5V, RTI and COP and API enabled, see Table A-12. |   |        |                   |     |     |     |      |

|--------------------------------------------------------------------------------------------------------------------------------|---|--------|-------------------|-----|-----|-----|------|

| Num                                                                                                                            | С | Rating | Symbol            | Min | Тур | Max | Unit |

| S12GN16, S12GN32                                                                                                               |   |        |                   |     |     |     |      |

| 1                                                                                                                              | С | -40°C  | I <sub>DDPS</sub> |     | 155 |     | μΑ   |

| 2                                                                                                                              | C | 25°C   | I <sub>DDPS</sub> |     | 165 |     | μΑ   |

| 3                                                                                                                              | O | 150°C  | I <sub>DDPS</sub> |     | 265 |     | μΑ   |

| 4                                                                                                                              | O | 160°C  | I <sub>DDPS</sub> |     | 295 |     | μΑ   |

| S12GN48, S12G48, S12G64                                                                                                        |   |        |                   |     |     |     |      |

| 5                                                                                                                              | O | -40°C  | I <sub>DDPS</sub> |     | 160 |     | μΑ   |

| 6                                                                                                                              | С | 25°C   | I <sub>DDPS</sub> |     | 170 |     | μΑ   |

| 7                                                                                                                              | С | 150°C  | I <sub>DDPS</sub> |     | 285 |     | μΑ   |

| S12G96, S12G128                                                                                                                |   |        |                   |     |     |     |      |

| 8                                                                                                                              | С | -40°C  | I <sub>DDPS</sub> |     | 165 |     | μΑ   |

| 9                                                                                                                              | С | 25°C   | I <sub>DDPS</sub> |     | 175 |     | μΑ   |

| 10                                                                                                                             | С | 150°C  | I <sub>DDPS</sub> |     | 320 |     | μΑ   |

| S12G192, S12GA192, S12G240, S12GA240                                                                                           |   |        |                   |     |     |     |      |

| 11                                                                                                                             | O | -40°C  | I <sub>DDPS</sub> |     | 175 |     | μΑ   |

| 12                                                                                                                             | O | 25°C   | I <sub>DDPS</sub> |     | 185 |     | μΑ   |

| 13                                                                                                                             | O | 150°C  | I <sub>DDPS</sub> |     | 430 |     | μΑ   |

## A.4 ADC Characteristics

This section describes the characteristics of the analog-to-digital converter.

# A.4.1 ADC Operating Characteristics

The Table A-19 and Table A-20 show conditions under which the ADC operates.

The following constraints exist to obtain full-scale, full range results:

$$V_{SSA} \leq V_{RL} \leq V_{IN} \leq V_{RH} \leq V_{DDA}.$$