Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 25MHz                                                                    |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 40                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                             |

| Data Converters            | A/D 12x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12ga128f0mlfr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |                  | <lowest< th=""><th>Function<br/>-PRIORITY</th><th>Power</th><th colspan="3">Internal Pull<br/>Resistor</th></lowest<> | Function<br>-PRIORITY | Power          | Internal Pull<br>Resistor |                  |            |                |

|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|---------------------------|------------------|------------|----------------|

| Package Pin | Pin              | 2nd<br>Func.                                                                                                          | 3rd<br>Func.          | 4th<br>Func    | 5th<br>Func               | Supply           | CTRL       | Reset<br>State |

| 1           | PJ6              | KWJ6                                                                                                                  | —                     |                |                           | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 2           | PJ5              | KWJ5                                                                                                                  | —                     | _              | _                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 3           | PJ4              | KWJ4                                                                                                                  | —                     | _              | _                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 4           | RESET            | _                                                                                                                     | —                     | _              | _                         | V <sub>DDX</sub> | PULLU      | P              |

| 5           | VDDX             | _                                                                                                                     | _                     |                |                           | _                | _          | _              |

| 6           | VDDR             | _                                                                                                                     | —                     | _              | _                         | _                | _          | _              |

| 7           | VSSX             | _                                                                                                                     | —                     | _              |                           | —                | _          | —              |

| 8           | PE0 <sup>1</sup> | EXTAL                                                                                                                 | _                     |                |                           | V <sub>DDX</sub> | PUCR/PDPEE | Down           |

| 9           | VSS              | _                                                                                                                     | _                     |                |                           | _                | _          | _              |

| 10          | PE1 <sup>1</sup> | XTAL                                                                                                                  | _                     | _              | _                         | V <sub>DDX</sub> | PUCR/PDPEE | Down           |

| 11          | TEST             | _                                                                                                                     | _                     | _              | _                         | N.A.             | RESET pin  | Down           |

| 12          | PJ0              | KWJ0                                                                                                                  | MISO1                 | _              | _                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 13          | PJ1              | KWJ1                                                                                                                  | MOSI1                 | _              | _                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 14          | PJ2              | KWJ2                                                                                                                  | SCK1                  | —              | —                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 15          | PJ3              | KWJ3                                                                                                                  | SS1                   | _              |                           | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 16          | BKGD             | MODC                                                                                                                  | _                     | _              | _                         | V <sub>DDX</sub> | PUCR/BKPUE | Up             |

| 17          | PP0              | KWP0                                                                                                                  | ETRIG0                | API_EXTC<br>LK | PWM0                      | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 18          | PP1              | KWP1                                                                                                                  | ETRIG1                | ECLKX2         | PWM1                      | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 19          | PP2              | KWP2                                                                                                                  | ETRIG2                | PWM2           | _                         | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 20          | PP3              | KWP3                                                                                                                  | ETRIG3                | PWM3           | —                         | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 21          | PP4              | KWP4                                                                                                                  | PWM4                  | _              | _                         | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 22          | PP5              | KWP5                                                                                                                  | PWM5                  | _              | _                         | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 23          | PP6              | KWP6                                                                                                                  |                       | —              |                           | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 24          | PP7              | KWP7                                                                                                                  |                       | —              | _                         | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 25          | PT7              |                                                                                                                       |                       | _              |                           | V <sub>DDX</sub> | PERT/PPST  | Disabled       |

| 26          | PT6              |                                                                                                                       | _                     | —              |                           | V <sub>DDX</sub> | PERT/PPST  | Disabled       |

| 27          | PT5              | IOC5                                                                                                                  | _                     | —              | _                         | V <sub>DDX</sub> | PERT/PPST  | Disabled       |

| Table 1-14. 6 | 64-Pin LQFP | <b>Pinout for</b> | S12GN48 |

|---------------|-------------|-------------------|---------|

|---------------|-------------|-------------------|---------|

### NOTE

If an attempt is made to activate BDM before being enabled, the CPU resumes normal instruction execution after a brief delay. If BDM is not enabled, any hardware BACKGROUND commands issued are ignored by the BDM and the CPU is not delayed.

In active BDM, the BDM registers and standard BDM firmware lookup table are mapped to addresses 0x3\_FF00 to 0x3\_FFFF. BDM registers are mapped to addresses 0x3\_FF00 to 0x3\_FF0B. The BDM uses these registers which are readable anytime by the BDM. However, these registers are not readable by user programs.

When BDM is activated while CPU executes code overlapping with BDM firmware space the saved program counter (PC) will be auto incremented by one from the BDM firmware, no matter what caused the entry into BDM active mode (BGND instruction, BACKGROUND command or breakpoints). In such a case the PC must be set to the next valid address via a WRITE\_PC command before executing the GO command.

# 7.4.3 BDM Hardware Commands

Hardware commands are used to read and write target system memory locations and to enter active background debug mode. Target system memory includes all memory that is accessible by the CPU such as on-chip RAM, Flash, I/O and control registers.

Hardware commands are executed with minimal or no CPU intervention and do not require the system to be in active BDM for execution, although, they can still be executed in this mode. When executing a hardware command, the BDM sub-block waits for a free bus cycle so that the background access does not disturb the running application program. If a free cycle is not found within 128 clock cycles, the CPU is momentarily frozen so that the BDM can steal a cycle. When the BDM finds a free cycle, the operation does not intrude on normal CPU operation provided that it can be completed in a single cycle. However, if an operation requires multiple cycles the CPU is frozen until the operation is complete, even though the BDM found a free cycle.

The BDM hardware commands are listed in Table 7-5.

The READ\_BD and WRITE\_BD commands allow access to the BDM register locations. These locations are not normally in the system memory map but share addresses with the application in memory. To distinguish between physical memory locations that share the same address, BDM memory resources are enabled just for the READ\_BD and WRITE\_BD access cycle. This allows the BDM to access BDM locations unobtrusively, even if the addresses conflict with the application memory map.

| Command     | Opcode<br>(hex) | Data | Description                                                                                                             |

|-------------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------|

| BACKGROUND  | 90              | None | Enter background mode if BDM is enabled. If enabled, an ACK will be issued when the part enters active background mode. |

| ACK_ENABLE  | D5              | None | Enable Handshake. Issues an ACK pulse after the command is executed.                                                    |

| ACK_DISABLE | D6              | None | Disable Handshake. This command does not issue an ACK pulse.                                                            |

### Table 7-5. Hardware Commands

0x02FA

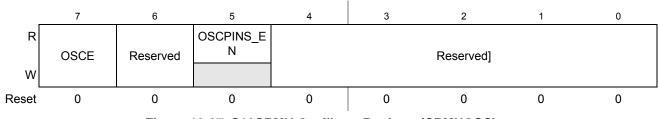

Figure 10-27. S12CPMU Oscillator Register (CPMUOSC)

Read: Anytime

Write: Anytime if PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register). Else write has no effect.

NOTE.

Write to this register clears the LOCK and UPOSC status bits.

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>OSCE       | <ul> <li>Oscillator Enable Bit — This bit enables the external oscillator (XOSCLCP). The UPOSC status bit in the CPMUFLG register indicates when the oscillation is stable and OSCCLK can be selected as Bus Clock or source of the COP or RTI. A loss of oscillation will lead to a clock monitor reset.</li> <li>0 External oscillator is disabled. REFCLK for PLL is IRCCLK.</li> <li>1 External oscillator is enabled.Clock monitor is enabled.External oscillator is qualified by PLLCLK REFCLK for PLL is the external oscillator clock divided by REFDIV.</li> <li>Note: When starting up the external oscillator (either by programming OSCE bit to 1 or on exit from Full Stop Mode with OSCE bit already 1) the software must wait for a minimum time equivalent to the startup-time of the external oscillator t<sub>UPOSC</sub> before entering Pseudo Stop Mode.</li> </ul> |

| 6<br>Reserved   | Do not alter this bit from its reset value. It is for Manufacturer use only and can change the PLL behavior.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5<br>OSCPINS_EN | Oscillator Pins EXTAL and XTAL Enable Bit<br>If OSCE=1 this read-only bit is set. It can only be cleared with the next reset.<br>Enabling the external oscillator reserves the EXTAL and XTAL pins exclusively for oscillator application.<br>0 EXTAL and XTAL pins are not reserved for oscillator.<br>1 EXTAL and XTAL pins exclusively reserved for oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4-0<br>Reserved | Do not alter these bits from their reset value. It is for Manufacturer use only and can change the PLL behavior.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### Table 10-24. CPMUOSC Field Descriptions

## 10.3.2.20 S12CPMU Protection Register (CPMUPROT)

This register protects the following clock configuration registers from accidental overwrite:

#### Analog-to-Digital Converter (ADC12B8CV2)

| SC | CD | сс | СВ | СА | Analog Input<br>Channel |

|----|----|----|----|----|-------------------------|

| 1  | 0  | 0  | 0  | 0  | Internal_6,             |

|    | 0  | 0  | 0  | 1  | Internal_7              |

|    | 0  | 0  | 1  | 0  | Internal_0              |

|    | 0  | 0  | 1  | 1  | Internal_1              |

|    | 0  | 1  | 0  | 0  | VRH                     |

|    | 0  | 1  | 0  | 1  | VRL                     |

|    | 0  | 1  | 1  | 0  | (VRH+VRL) / 2           |

|    | 0  | 1  | 1  | 1  | Reserved                |

|    | 1  | 0  | 0  | 0  | Internal_2              |

|    | 1  | 0  | 0  | 1  | Internal_3              |

|    | 1  | 0  | 1  | 0  | Internal_4              |

|    | 1  | 0  | 1  | 1  | Internal_5              |

|    | 1  | 1  | Х  | Х  | Reserved                |

### Table 12-15. Analog Input Channel Select Coding

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MULT      | Multi-Channel Sample Mode — When MULT is 0, the ATD sequence controller samples only from the specified analog input channel for an entire conversion sequence. The analog channel is selected by channel selection code (control bits CD/CC/CB/CA located in ATDCTL5). When MULT is 1, the ATD sequence controller samples across channels. The number of channels sampled is determined by the sequence length value (S8C, S4C, S2C, S1C). The first analog channel examined is determined by channel selection code (CD, CC, CB, CA control bits); subsequent channels sampled in the sequence are determined by incrementing the channel selection code or wrapping around to AN0 (channel 0). |

| 3–0<br>CD, CC, | Analog Input Channel Select Code — These bits select the analog input channel(s). Table 16-15 lists the coding used to select the various analog input channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CB, CA         | In the case of single channel conversions (MULT=0), this selection code specifies the channel to be examined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | In the case of multiple channel conversions (MULT=1), this selection code specifies the first channel to be examined in the conversion sequence. Subsequent channels are determined by incrementing the channel selection code or wrapping around to AN0 (after converting the channel defined by the Wrap Around Channel Select Bits WRAP3-0 in ATDCTL0). When starting with a channel number higher than the one defined by WRAP3-0 the first wrap around will be AN16 to AN0.                                                                                                                                                                                                                   |

| SC | CD | сс | СВ | СА | Analog Input<br>Channel |

|----|----|----|----|----|-------------------------|

| 0  | 0  | 0  | 0  | 0  | AN0                     |

|    | 0  | 0  | 0  | 1  | AN1                     |

|    | 0  | 0  | 1  | 0  | AN2                     |

|    | 0  | 0  | 1  | 1  | AN3                     |

|    | 0  | 1  | 0  | 0  | AN4                     |

|    | 0  | 1  | 0  | 1  | AN5                     |

|    | 0  | 1  | 1  | 0  | AN6                     |

|    | 0  | 1  | 1  | 1  | AN7                     |

|    | 1  | 0  | 0  | 0  | AN8                     |

|    | 1  | 0  | 0  | 1  | AN9                     |

|    | 1  | 0  | 1  | 0  | AN10                    |

|    | 1  | 0  | 1  | 1  | AN11                    |

|    | 1  | 1  | 0  | 0  | AN12                    |

|    | 1  | 1  | 0  | 1  | AN13                    |

|    | 1  | 1  | 1  | 0  | AN14                    |

|    | 1  | 1  | 1  | 1  | AN15                    |

Table 16-15. Analog Input Channel Select Coding

## 17.3.4 AMPM Input Pin

This analog pin is used as input for the operational amplifier negative input pin, if the according mode is selected, see register bit DACM[2:0].

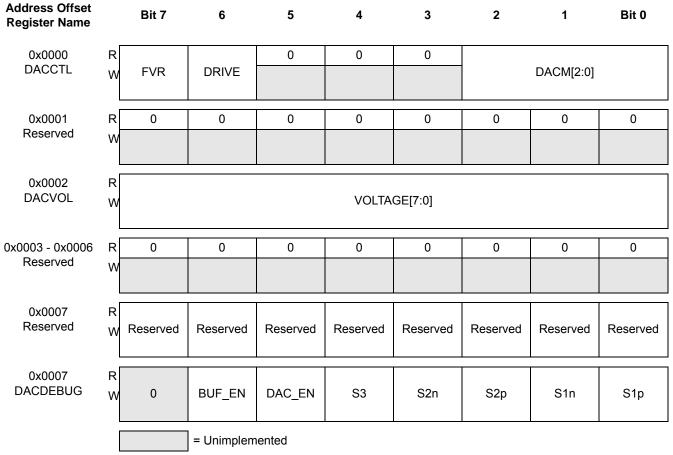

# 17.4 Memory Map and Register Definition

This sections provides the detailed information of all registers for the DAC\_8B5V module.

## 17.4.1 Register Summary

Figure 17-2 shows the summary of all implemented registers inside the DAC\_8B5V module.

### NOTE

Register Address = Module Base Address + Address Offset, where the Module Base Address is defined at the MCU level and the Address Offset is defined at the module level.

## 18.3.2.17 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 18.3.3.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 18.4.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

Module Base + 0x0010 to Module Base + 0x0013

Access: User read/write<sup>1</sup>

Access: User read/write<sup>1</sup>

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

### Figure 18-20. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0–CANIDAR3

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 18-22. CANIDAR0–CANIDAR3 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AC[7:0] | Acceptance Code Bits — AC[7:0] comprise a user-defined sequence of bits with which the corresponding bits of the related identifier register (IDRn) of the receive message buffer are compared. The result of this comparison is then masked with the corresponding identifier mask register. |

Module Base + 0x0018 to Module Base + 0x001B

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 18-21. MSCAN Identifier Acceptance Registers (Second Bank) — CANIDAR4–CANIDAR7

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### 16 KByte Flash Module (S12FTMRG16K1V1)

Trying to alter data in any protected area in the P-Flash memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. The block erase of a P-Flash block is not possible if any of the P-Flash sectors contained in the same P-Flash block are protected.

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>FPOPEN      | <ul> <li>Flash Protection Operation Enable — The FPOPEN bit determines the protection function for program or erase operations as shown in Table 24-18 for the P-Flash block.</li> <li>When FPOPEN is clear, the FPHDIS bit defines an unprotected address range as specified by the FPHS bits</li> <li>When FPOPEN is set, the FPHDIS bit enables protection for the address range specified by the FPHS bits</li> </ul> |  |  |

| 6<br>RNV[6]      | <b>Reserved Nonvolatile Bit</b> — The RNV bit should remain in the erased state for future enhancements.                                                                                                                                                                                                                                                                                                                  |  |  |

| 5<br>FPHDIS      | Flash Protection Higher Address Range Disable — The FPHDIS bit determines whether there is a<br>protected/unprotected area in a specific region of the P-Flash memory ending with global address 0x3_FFFF<br>0 Protection/Unprotection enabled<br>1 Protection/Unprotection disabled                                                                                                                                      |  |  |

| 4–3<br>FPHS[1:0] | Flash Protection Higher Address Size — The FPHS bits determine the size of the protected/unprotected area in P-Flash memory as shown in Table 24-19. The FPHS bits can only be written to while the FPHDIS bit is set.                                                                                                                                                                                                    |  |  |

| 2–0<br>RNV[2:0]  | Reserved Nonvolatile Bits — These RNV bits should remain in the erased state.                                                                                                                                                                                                                                                                                                                                             |  |  |

#### Table 24-17. FPROT Field Descriptions

#### Table 24-18. P-Flash Protection Function

| FPOPEN | FPHDIS | Function <sup>1</sup>         |  |

|--------|--------|-------------------------------|--|

| 1      | 1      | No P-Flash Protection         |  |

| 1      | 0      | Protected High Range          |  |

| 0      | 1      | Full P-Flash Memory Protected |  |

| 0      | 0      | Unprotected High Range        |  |

<sup>1</sup> For range sizes, refer to Table 24-19.

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_F800-0x3_FFFF    | 2 Kbytes       |

| 01        | 0x3_F000-0x3_FFFF    | 4 Kbytes       |

| 10        | 0x3_E000-0x3_FFFF    | 8 Kbytes       |

| 11        | 0x3_C000-0x3_FFFF    | 16 Kbytes      |

Although the protection scheme is loaded from the Flash memory at global address 0x3\_FF0C during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

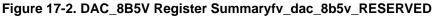

### 24.3.2.16 Flash Option Register (FOPT)

The FOPT register is the Flash option register.

<sup>1</sup> Loaded from IFR Flash configuration field, during reset sequence.

All bits in the FOPT register are readable but are not writable.

During the reset sequence, the FOPT register is loaded from the Flash nonvolatile byte in the Flash configuration field at global address  $0x_3$ \_FF0E located in P-Flash memory (see Table 24-4) as indicated by reset condition F in Figure 24-21. If a double bit fault is detected while reading the P-Flash phrase containing the Flash nonvolatile byte during the reset sequence, all bits in the FOPT register will be set.

| Field | Description                                                                                                                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Nonvolatile Bits</b> — The NV[7:0] bits are available as nonvolatile bits. Refer to the device user guide for proper use of the NV bits. |

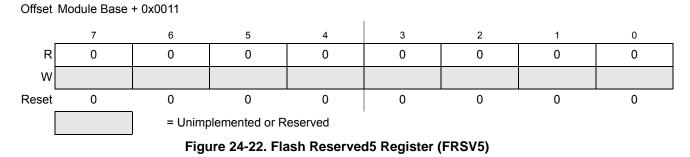

### 24.3.2.17 Flash Reserved5 Register (FRSV5)

This Flash register is reserved for factory testing.

All bits in the FRSV5 register read 0 and are not writable.

### 24.3.2.18 Flash Reserved6 Register (FRSV6)

This Flash register is reserved for factory testing.

32 KByte Flash Module (S12FTMRG32K1V1)

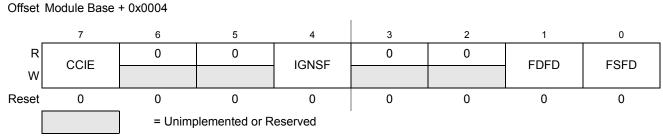

## 25.3.2.5 Flash Configuration Register (FCNFG)

The FCNFG register enables the Flash command complete interrupt and forces ECC faults on Flash array read access from the CPU.

### Figure 25-9. Flash Configuration Register (FCNFG)

CCIE, IGNSF, FDFD, and FSFD bits are readable and writable while remaining bits read 0 and are not writable.

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIE  | <ul> <li>Command Complete Interrupt Enable — The CCIE bit controls interrupt generation when a Flash command has completed.</li> <li>0 Command complete interrupt disabled</li> <li>1 An interrupt will be requested whenever the CCIF flag in the FSTAT register is set (see Section 25.3.2.7)</li> </ul>                                                                                                                                                                                                                                                                                                                               |

| 4<br>IGNSF | <ul> <li>Ignore Single Bit Fault — The IGNSF controls single bit fault reporting in the FERSTAT register (see Section 25.3.2.8).</li> <li>O All single bit faults detected during array reads are reported</li> <li>1 Single bit faults detected during array reads are not reported and the single bit fault interrupt will not be generated</li> </ul>                                                                                                                                                                                                                                                                                 |

| 1<br>FDFD  | <ul> <li>Force Double Bit Fault Detect — The FDFD bit allows the user to simulate a double bit fault during Flash array read operations and check the associated interrupt routine. The FDFD bit is cleared by writing a 0 to FDFD.</li> <li>O Flash array read operations will set the DFDIF flag in the FERSTAT register only if a double bit fault is detected</li> <li>1 Any Flash array read operation will force the DFDIF flag in the FERSTAT register to be set (see Section 25.3.2.7) and an interrupt will be generated as long as the DFDIE interrupt enable in the FERCNFG register is set (see Section 25.3.2.6)</li> </ul> |

| 0<br>FSFD  | <ul> <li>Force Single Bit Fault Detect — The FSFD bit allows the user to simulate a single bit fault during Flash array read operations and check the associated interrupt routine. The FSFD bit is cleared by writing a 0 to FSFD.</li> <li>0 Flash array read operations will set the SFDIF flag in the FERSTAT register only if a single bit fault is detected</li> <li>1 Flash array read operation will force the SFDIF flag in the FERSTAT register to be set (see Section 25.3.2.7) and an interrupt will be generated as long as the SFDIE interrupt enable in the FERCNFG register is set (see Section 25.3.2.6)</li> </ul>     |

### Table 25-13. FCNFG Field Descriptions

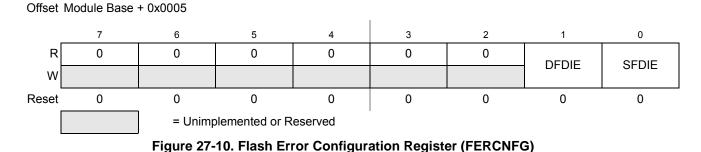

## 25.3.2.6 Flash Error Configuration Register (FERCNFG)

The FERCNFG register enables the Flash error interrupts for the FERSTAT flags.

#### 32 KByte Flash Module (S12FTMRG32K1V1)

All assigned bits in the FERCNFG register are readable and writable.

#### Table 27-14. FERCNFG Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1<br>DFDIE | <ul> <li>Double Bit Fault Detect Interrupt Enable — The DFDIE bit controls interrupt generation when a double bit fault is detected during a Flash block read operation.</li> <li>0 DFDIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the DFDIF flag is set (see Section 27.3.2.8)</li> </ul>                                                       |  |  |

| 0<br>SFDIE | <ul> <li>Single Bit Fault Detect Interrupt Enable — The SFDIE bit controls interrupt generation when a single bit fault is detected during a Flash block read operation.</li> <li>0 SFDIF interrupt disabled whenever the SFDIF flag is set (see Section 27.3.2.8)</li> <li>1 An interrupt will be requested whenever the SFDIF flag is set (see Section 27.3.2.8)</li> </ul> |  |  |

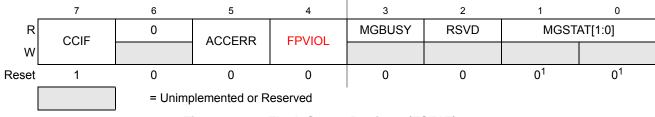

### 27.3.2.7 Flash Status Register (FSTAT)

The FSTAT register reports the operational status of the Flash module.

Offset Module Base + 0x0006

Figure 27-11. Flash Status Register (FSTAT)

<sup>1</sup> Reset value can deviate from the value shown if a double bit fault is detected during the reset sequence (see Section 27.6).

CCIF, ACCERR, and FPVIOL bits are readable and writable, MGBUSY and MGSTAT bits are readable but not writable, while remaining bits read 0 and are not writable.

#### 64 KByte Flash Module (S12FTMRG64K1V1)

Trying to alter data in any protected area in the P-Flash memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. The block erase of a P-Flash block is not possible if any of the P-Flash sectors contained in the same P-Flash block are protected.

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>FPOPEN      | <ul> <li>Flash Protection Operation Enable — The FPOPEN bit determines the protection function for program or erase operations as shown in Table 27-18 for the P-Flash block.</li> <li>When FPOPEN is clear, the FPHDIS and FPLDIS bits define unprotected address ranges as specified by the corresponding FPHS and FPLS bits</li> <li>When FPOPEN is set, the FPHDIS and FPLDIS bits enable protection for the address range specified by the corresponding FPHS and FPLDIS bits</li> </ul> |  |  |

| 6<br>RNV[6]      | Reserved Nonvolatile Bit — The RNV bit should remain in the erased state for future enhancements.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 5<br>FPHDIS      | Flash Protection Higher Address Range Disable — The FPHDIS bit determines whether there is a<br>protected/unprotected area in a specific region of the P-Flash memory ending with global address 0x3_FFFF.0 Protection/Unprotection enabled<br>1 Protection/Unprotection disabled                                                                                                                                                                                                             |  |  |

| 4–3<br>FPHS[1:0] | Flash Protection Higher Address Size — The FPHS bits determine the size of the protected/unprotected area in P-Flash memory as shown inTable 27-19. The FPHS bits can only be written to while the FPHDIS bit is set.                                                                                                                                                                                                                                                                         |  |  |

| 2<br>FPLDIS      | <ul> <li>Flash Protection Lower Address Range Disable — The FPLDIS bit determines whether there is a protected/unprotected area in a specific region of the P-Flash memory beginning with global address 0x3_8000.</li> <li>0 Protection/Unprotection enabled</li> <li>1 Protection/Unprotection disabled</li> </ul>                                                                                                                                                                          |  |  |

| 1–0<br>FPLS[1:0] | Flash Protection Lower Address Size — The FPLS bits determine the size of the protected/unprotected area in P-Flash memory as shown in Table 27-20. The FPLS bits can only be written to while the FPLDIS bit is set.                                                                                                                                                                                                                                                                         |  |  |

### Table 27-17. FPROT Field Descriptions

| FPOPEN | FPHDIS | FPLDIS | Function <sup>1</sup>         |

|--------|--------|--------|-------------------------------|

| 1      | 1      | 1      | No P-Flash Protection         |

| 1      | 1      | 0      | Protected Low Range           |

| 1      | 0      | 1      | Protected High Range          |

| 1      | 0      | 0      | Protected High and Low Ranges |

| 0      | 1      | 1      | Full P-Flash Memory Protected |

| 0      | 1      | 0      | Unprotected Low Range         |

Unprotected High Range

Unprotected High and Low Ranges

### Table 27-18. P-Flash Protection Function

<sup>1</sup> For range sizes, refer to Table 27-19 and Table 27-20.

1

0

0

0

0

0

8. Reset the MCU

# 27.5.3 Mode and Security Effects on Flash Command Availability

The availability of Flash module commands depends on the MCU operating mode and security state as shown in Table 27-27.

# 27.6 Initialization

On each system reset the flash module executes an initialization sequence which establishes initial values for the Flash Block Configuration Parameters, the FPROT and EEPROT protection registers, and the FOPT and FSEC registers. The initialization routine reverts to built-in default values that leave the module in a fully protected and secured state if errors are encountered during execution of the reset sequence. If a double bit fault is detected during the reset sequence, both MGSTAT bits in the FSTAT register will be set.

CCIF is cleared throughout the initialization sequence. The Flash module holds off all CPU access for a portion of the initialization sequence. Flash reads are allowed once the hold is removed. Completion of the initialization sequence is marked by setting CCIF high which enables user commands.

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

| CCOBIX[2:0] | FCCOB Parameters      |                                                   |  |

|-------------|-----------------------|---------------------------------------------------|--|

| 000         | 0x0D                  | Flash block selection code [1:0]. See Table 28-34 |  |

| 001         | Margin level setting. |                                                   |  |

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 28-55.

| Table 28-55. | Valid Set User Margin Level Settings |

|--------------|--------------------------------------|

|              |                                      |

| CCOB<br>(CCOBIX=001) | Level Description                |  |

|----------------------|----------------------------------|--|

| 0x0000               | Return to Normal Level           |  |

| 0x0001               | User Margin-1 Level <sup>1</sup> |  |

| 0x0002               | User Margin-0 Level <sup>2</sup> |  |

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

| Register | Error Bit         | Error Condition                                                              |

|----------|-------------------|------------------------------------------------------------------------------|

|          | 400500            | Set if CCOBIX[2:0] != 001 at command launch                                  |

|          |                   | Set if command not available in current mode (see Table 28-27)               |

|          | ACCERR            | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 28-34) |

| FSTAT    |                   | Set if an invalid margin level setting is supplied                           |

|          | FPVIOL<br>MGSTAT1 | None                                                                         |

|          |                   | None                                                                         |

|          | MGSTAT0           | None                                                                         |

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIE | <ul> <li>Double Bit Fault Detect Interrupt Enable — The DFDIE bit controls interrupt generation when a double bit fault is detected during a Flash block read operation.</li> <li>0 DFDIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the DFDIF flag is set (see Section 29.3.2.8)</li> </ul>                                                       |

| 0<br>SFDIE | <ul> <li>Single Bit Fault Detect Interrupt Enable — The SFDIE bit controls interrupt generation when a single bit fault is detected during a Flash block read operation.</li> <li>0 SFDIF interrupt disabled whenever the SFDIF flag is set (see Section 29.3.2.8)</li> <li>1 An interrupt will be requested whenever the SFDIF flag is set (see Section 29.3.2.8)</li> </ul> |

### Table 29-14. FERCNFG Field Descriptions

### 29.3.2.7 Flash Status Register (FSTAT)

The FSTAT register reports the operational status of the Flash module.

Offset Module Base + 0x0006

#### Figure 29-11. Flash Status Register (FSTAT)

<sup>1</sup> Reset value can deviate from the value shown if a double bit fault is detected during the reset sequence (see Section 29.6).

CCIF, ACCERR, and FPVIOL bits are readable and writable, MGBUSY and MGSTAT bits are readable but not writable, while remaining bits read 0 and are not writable.

#### Table 29-15. FSTAT Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIF   | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command completion or command violation.</li> <li>O Flash command in progress</li> <li>1 Flash command has completed</li> </ul>                                                                                                                                                                           |

| 5<br>ACCERR | <ul> <li>Flash Access Error Flag — The ACCERR bit indicates an illegal access has occurred to the Flash memory caused by either a violation of the command write sequence (see Section 29.4.4.2) or issuing an illegal Flash command. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR.</li> <li>0 No access error detected</li> <li>1 Access error detected</li> </ul>        |

| 4<br>FPVIOL | <ul> <li>Flash Protection Violation Flag — The FPVIOL bit indicates an attempt was made to program or erase an address in a protected area of P-Flash or EEPROM memory during a command write sequence. The FPVIOL bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL is set, it is not possible to launch a command or start a command write sequence.</li> <li>0 No protection violation detected</li> <li>1 Protection violation detected</li> </ul> |

#### 192 KByte Flash Module (S12FTMRG192K2V1)

Table 30-4). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x0C             | Not required |

| 001         | Ke               | у 0          |

| 010         | Ke               | y 1          |

| 011         | Ke               | y 2          |

| 100         | Ke               | у З          |

Table 30-52. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

Table 30-53. Verify Backdoor Access Key Command Error Handling

| Register | Error Bit | Error Condition                                                                          |

|----------|-----------|------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 100 at command launch                                              |

|          |           | Set if an incorrect backdoor key is supplied                                             |

|          |           | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 30.3.2.2) |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                              |

|          |           | None                                                                                     |

|          | MGSTAT1   | None                                                                                     |

|          | MGSTAT0   | None                                                                                     |

### 30.4.6.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

| CCOBIX[2:0] | FCC  | OB Parameters                                     |

|-------------|------|---------------------------------------------------|

| 000         | 0x0D | Flash block selection code [1:0]. See Table 30-34 |

| 001         | Marg | jin level setting.                                |

| CCOBIX[2:0] | FCCOB Parameters                                                                                               |                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 000         | 0x12                                                                                                           | Global address [17:16] to identify<br>EEPROM block |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 30.1.2.2 for EEPROM sector size. |                                                    |

Table 30-64. Erase EEPROM Sector Command FCCOB Requirements

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 30-27)                      |

|          | ACCERK    | Set if an invalid global address [17:0] is suppliedsee Table 30-3)                  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 30-65. Erase EEPROM Sector Command Error Handling

### 30.4.7 Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Table | 30-66. | Flash | Interrupt | Sources |

|-------|--------|-------|-----------|---------|

|-------|--------|-------|-----------|---------|

| Interrupt Source                   | Interrupt Flag              | Local Enable                | Global (CCR)<br>Mask |

|------------------------------------|-----------------------------|-----------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | l Bit                |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register) | DFDIE<br>(FERCNFG register) | l Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | l Bit                |

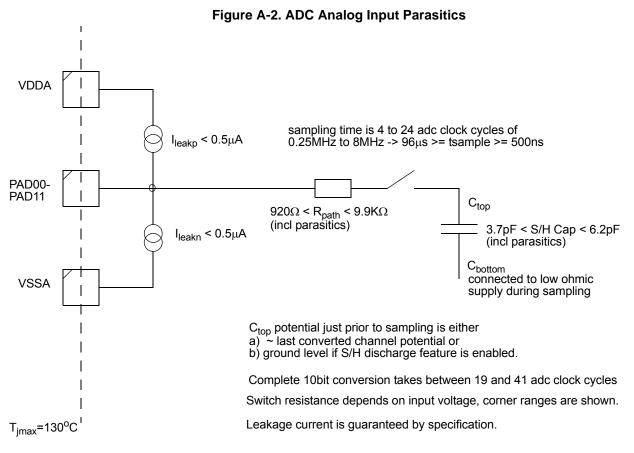

## A.4.3.2 ADC Analog Input Parasitics

## A.4.4 ADC Temperature Sensor

Table A-30. ADC Temperature Sensor

| Num | С | Rating                   | Symbol           | Min  | Тур  | Мах  | Unit  |

|-----|---|--------------------------|------------------|------|------|------|-------|

| 1   | Т | Temperature Sensor Slope | dV <sub>TS</sub> | -4.0 | -3.8 | -3.6 | mV/°C |

# A.5 ACMP Characteristics

This section describes the electrical characteristics of the analog comparator.

MC9S12G Family Reference Manual Rev.1.27

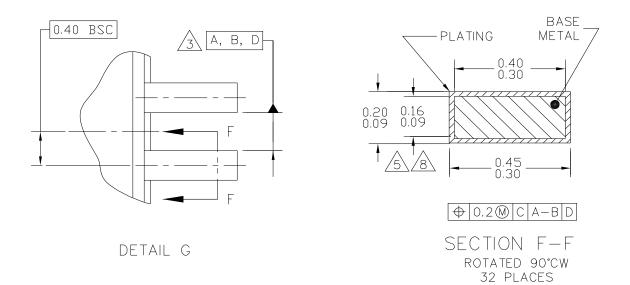

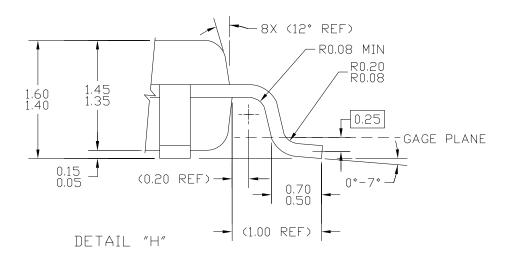

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE   |                            | PRINT VERSION NOT TO SCALE |        |  |

|---------------------------------------------------------|----------------------|----------------------------|----------------------------|--------|--|

| TITLE:                                                  |                      | DOCUMENT NO: 98ASH70029A   |                            | RE∨: D |  |

| LOW PROFILE QUAD FLAT PA                                | CASE NUMBER: 873A-03 |                            | 19 MAY 2005                |        |  |

| 32 LEAD, 0.8 PITCH (7 X 7 X 1.4)                        |                      | STANDARD: JEDEC MS-026 BBA |                            |        |  |