### NXP USA Inc. - S9S12GA192F0MLH Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 54                                                                      |

| Program Memory Size        | 192KB (192K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 11K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12ga192f0mlh |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |                  | <lowest< th=""><th>Function</th><th>Power</th><th></th><th colspan="2">Internal Pull<br/>Resistor</th></lowest<> | Function     | Power          |             | Internal Pull<br>Resistor |               |                |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------|--------------|----------------|-------------|---------------------------|---------------|----------------|

| Package Pin | Pin              | 2nd<br>Func.                                                                                                     | 3rd<br>Func. | 4th<br>Func    | 5th<br>Func | Supply                    | CTRL          | Reset<br>State |

| 3           | VSSX             |                                                                                                                  | —            | _              | _           | _                         | _             | _              |

| 4           | PE0 <sup>1</sup> | EXTAL                                                                                                            | —            | —              | _           | V <sub>DDX</sub>          | PUCR/PDPEE    | Down           |

| 5           | VSS              | —                                                                                                                | —            | —              | _           | —                         | —             | —              |

| 6           | PE1 <sup>1</sup> | XTAL                                                                                                             | —            | _              |             | V <sub>DDX</sub>          | PUCR/PDPEE    | Down           |

| 7           | TEST             | _                                                                                                                | —            | _              | _           | N.A.                      | RESET pin     | Down           |

| 8           | PJ0              | KWJ0                                                                                                             | —            | MISO1          | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 9           | PJ1              | KWJ1                                                                                                             | —            | MOSI1          | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 10          | PJ2              | KWJ2                                                                                                             | —            | SCK1           |             | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 11          | PJ3              | KWJ3                                                                                                             | _            | SS1            | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 12          | BKGD             | MODC                                                                                                             | _            | _              | _           | V <sub>DDX</sub>          | PUCR/BKPUE    | Up             |

| 13          | PP0              | KWP0                                                                                                             | ETRIG0       | API_EXTC<br>LK | PWM0        | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 14          | PP1              | KWP1                                                                                                             | ETRIG1       | ECLKX2         | PWM1        | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 15          | PP2              | KWP2                                                                                                             | ETRIG2       | PWM2           | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 16          | PP3              | KWP3                                                                                                             | ETRIG3       | PWM3           | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 17          | PP4              | KWP4                                                                                                             | PWM4         | _              | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 18          | PP5              | KWP5                                                                                                             | PWM5         | _              | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 19          | PT5              | IOC5                                                                                                             | _            |                |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 20          | PT4              | IOC4                                                                                                             | —            | —              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 21          | PT3              | IOC3                                                                                                             | _            |                |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 22          | PT2              | IOC2                                                                                                             | _            | _              |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 23          | PT1              | IOC1                                                                                                             | IRQ          | _              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 24          | PT0              | IOC0                                                                                                             | XIRQ         | —              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 25          | PAD0             | KWAD0                                                                                                            | AN0          | _              |             | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 26          | PAD8             | KWAD8                                                                                                            | AN8          | —              | _           | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 27          | PAD1             | KWAD1                                                                                                            | AN1          | —              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 28          | PAD9             | KWAD9                                                                                                            | AN9          | ACMPO          |             | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 29          | PAD2             | KWAD2                                                                                                            | AN2          | —              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 30          | PAD10            | KWAD10                                                                                                           | AN10         | ACMPP          |             | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

Table 1-16. 48-Pin LQFP Pinout for S12G48 and S12G64

MC9S12G Family Reference Manual Rev.1.27

|             |                  | <lowest< th=""><th>Function<br/>PRIORITY</th><th>Power</th><th></th><th colspan="2">Internal Pull<br/>Resistor</th></lowest<> | Function<br>PRIORITY | Power          |             | Internal Pull<br>Resistor |               |                |

|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-------------|---------------------------|---------------|----------------|

| Package Pin | Pin              | 2nd<br>Func.                                                                                                                  | 3rd<br>Func.         | 4th<br>Func    | 5th<br>Func | Supply                    | CTRL          | Reset<br>State |

| 2           | VDDXR            | _                                                                                                                             | —                    | _              | _           | —                         | _             | —              |

| 3           | VSSX             |                                                                                                                               | —                    | _              | _           | _                         | —             | _              |

| 4           | PE0 <sup>1</sup> | EXTAL                                                                                                                         | —                    | _              |             | V <sub>DDX</sub>          | PUCR/PDPEE    | Down           |

| 5           | VSS              | _                                                                                                                             | —                    | _              |             | _                         | —             | _              |

| 6           | PE1 <sup>1</sup> | XTAL                                                                                                                          | —                    | _              |             | V <sub>DDX</sub>          | PUCR/PDPEE    | Down           |

| 7           | TEST             | _                                                                                                                             | _                    | —              | _           | N.A.                      | RESET pin     | Down           |

| 8           | PJ0              | KWJ0                                                                                                                          | PWM6                 | MISO1          | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 9           | PJ1              | KWJ1                                                                                                                          | IOC6                 | MOSI1          | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 10          | PJ2              | KWJ2                                                                                                                          | IOC7                 | SCK1           | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 11          | PJ3              | KWJ3                                                                                                                          | PWM7                 | SS1            | _           | V <sub>DDX</sub>          | PERJ/PPSJ     | Up             |

| 12          | BKGD             | MODC                                                                                                                          | _                    | —              | _           | V <sub>DDX</sub>          | PUCR/BKPUE    | Up             |

| 13          | PP0              | KWP0                                                                                                                          | ETRIG0               | API_EXTC<br>LK | PWM0        | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 14          | PP1              | KWP1                                                                                                                          | ETRIG1               | ECLKX2         | PWM1        | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 15          | PP2              | KWP2                                                                                                                          | ETRIG2               | PWM2           |             | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 16          | PP3              | KWP3                                                                                                                          | ETRIG3               | PWM3           | _           | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 17          | PP4              | KWP4                                                                                                                          | PWM4                 | _              |             | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 18          | PP5              | KWP5                                                                                                                          | PWM5                 | _              |             | V <sub>DDX</sub>          | PERP/PPSP     | Disabled       |

| 19          | PT5              | IOC5                                                                                                                          | —                    | _              |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 20          | PT4              | IOC4                                                                                                                          | —                    | _              |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 21          | PT3              | IOC3                                                                                                                          | —                    | _              |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 22          | PT2              | IOC2                                                                                                                          | —                    | _              |             | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 23          | PT1              | IOC1                                                                                                                          | IRQ                  | —              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 24          | PT0              | IOC0                                                                                                                          | XIRQ                 | _              | _           | V <sub>DDX</sub>          | PERT/PPST     | Disabled       |

| 25          | PAD0             | KWAD0                                                                                                                         | AN0                  | —              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 26          | PAD8             | KWAD8                                                                                                                         | AN8                  | _              | _           | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 27          | PAD1             | KWAD1                                                                                                                         | AN1                  | _              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 28          | PAD9             | KWAD9                                                                                                                         | AN9                  |                | _           | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 29          | PAD2             | KWAD2                                                                                                                         | AN2                  | _              | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

Table 1-20. 48-Pin LQFP Pinout for S12G96 and S12G128

MC9S12G Family Reference Manual Rev.1.27

|             |       | <lowest< th=""><th>Function<br/>-PRIORITY-</th><th>Power</th><th colspan="3">Internal Pull<br/>Resistor</th></lowest<> | Function<br>-PRIORITY- | Power       | Internal Pull<br>Resistor |                  |               |                |

|-------------|-------|------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|---------------------------|------------------|---------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.                                                                                                           | 3rd<br>Func.           | 4th<br>Func | 5th<br>Func               | Supply           | CTRL          | Reset<br>State |

| 28          | PT4   | IOC4                                                                                                                   |                        |             | _                         | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 29          | PT3   | IOC3                                                                                                                   |                        | _           | _                         | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 30          | PT2   | IOC2                                                                                                                   |                        |             | _                         | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 31          | PT1   | IOC1                                                                                                                   | IRQ                    |             | _                         | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 32          | PT0   | IOC0                                                                                                                   | XIRQ                   |             | —                         | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 33          | PAD0  | KWAD0                                                                                                                  | AN0                    |             | _                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 34          | PAD8  | KWAD8                                                                                                                  | AN8                    | _           | _                         | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 35          | PAD1  | KWAD1                                                                                                                  | AN1                    | _           | _                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 36          | PAD9  | KWAD9                                                                                                                  | AN9                    | _           | _                         | V <sub>DDA</sub> | PER0ADPPS0AD  | Disabled       |

| 37          | PAD2  | KWAD2                                                                                                                  | AN2                    | _           | _                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 38          | PAD10 | KWAD10                                                                                                                 | AN10                   | _           | _                         | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 39          | PAD3  | KWAD3                                                                                                                  | AN3                    | _           | _                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 40          | PAD11 | KWAD11                                                                                                                 | AN11                   | _           | _                         | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 41          | PAD4  | KWAD4                                                                                                                  | AN4                    | _           | _                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 42          | PAD12 | KWAD12                                                                                                                 |                        | _           | _                         | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 43          | PAD5  | KWAD5                                                                                                                  | AN5                    | _           | _                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 44          | PAD13 | KWAD13                                                                                                                 |                        | _           | _                         | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 45          | PAD6  | KWAD6                                                                                                                  | AN6                    | _           | _                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 46          | PAD14 | KWAD14                                                                                                                 |                        | _           | _                         | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 47          | PAD7  | KWAD7                                                                                                                  | AN7                    | _           | _                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 48          | PAD15 | KWAD15                                                                                                                 |                        |             | —                         | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 49          | VRH   | _                                                                                                                      | _                      | _           | _                         | _                |               | _              |

| 50          | VDDA  | _                                                                                                                      | _                      |             | —                         | —                | _             | _              |

| 51          | VSSA  | _                                                                                                                      | _                      | _           | —                         |                  | _             | _              |

| 52          | PS0   | RXD0                                                                                                                   | _                      | _           | _                         | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 53          | PS1   | TXD0                                                                                                                   | _                      | _           | _                         | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 54          | PS2   | RXD1                                                                                                                   |                        |             | —                         | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 55          | PS3   | TXD1                                                                                                                   |                        |             |                           | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 56          | PS4   | MISO0                                                                                                                  |                        |             |                           | V <sub>DDX</sub> | PERS/PPSS     | Up             |

Table 1-24.

64-Pin LQFP Pinout for S12GA96 and S12GA128

# 6.5 Initialization/Application Information

## 6.5.1 Initialization

After system reset, software should:

- 1. Initialize the interrupt vector base register if the interrupt vector table is not located at the default location (0xFF80–0xFFF9).

- 2. Enable I bit maskable interrupts by clearing the I bit in the CCR.

- 3. Enable the X bit maskable interrupt by clearing the X bit in the CCR.

## 6.5.2 Interrupt Nesting

The interrupt request scheme makes it possible to nest I bit maskable interrupt requests handled by the CPU.

• I bit maskable interrupt requests can be interrupted by an interrupt request with a higher priority.

I bit maskable interrupt requests cannot be interrupted by other I bit maskable interrupt requests per default. In order to make an interrupt service routine (ISR) interruptible, the ISR must explicitly clear the I bit in the CCR (CLI). After clearing the I bit, other I bit maskable interrupt requests can interrupt the current ISR.

An ISR of an interruptible I bit maskable interrupt request could basically look like this:

- 1. Service interrupt, that is clear interrupt flags, copy data, etc.

- 2. Clear I bit in the CCR by executing the instruction CLI (thus allowing other I bit maskable interrupt requests)

- 3. Process data

- 4. Return from interrupt by executing the instruction RTI

## 6.5.3 Wake Up from Stop or Wait Mode

## 6.5.3.1 CPU Wake Up from Stop or Wait Mode

Every I bit maskable interrupt request is capable of waking the MCU from stop or wait mode. To determine whether an I bit maskable interrupts is qualified to wake-up the CPU or not, the same conditions as in normal run mode are applied during stop or wait mode:

• If the I bit in the CCR is set, all I bit maskable interrupts are masked from waking-up the MCU.

Since there are no clocks running in stop mode, only interrupts which can be asserted asynchronously can wake-up the MCU from stop mode.

The X bit maskable interrupt request can wake up the MCU from stop or wait mode at anytime, even if the X bit in CCR is set<sup>1</sup>.

<sup>1.</sup> The capability of the  $\overline{\text{XIRQ}}$  pin to wake-up the MCU with the X bit set may not be available if, for example, the  $\overline{\text{XIRQ}}$  pin is shared with other peripheral modules on the device. Please refer to the Device section of the MCU reference manual for details.

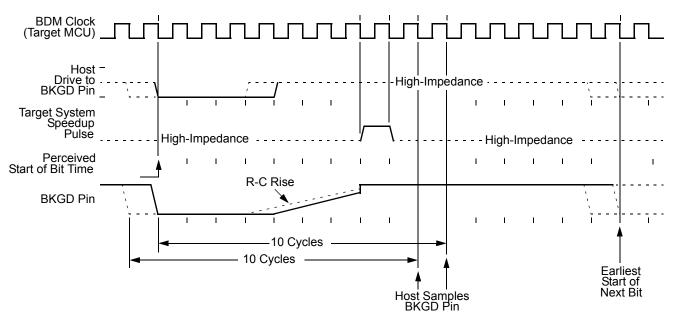

Figure 7-8. BDM Target-to-Host Serial Bit Timing (Logic 1)

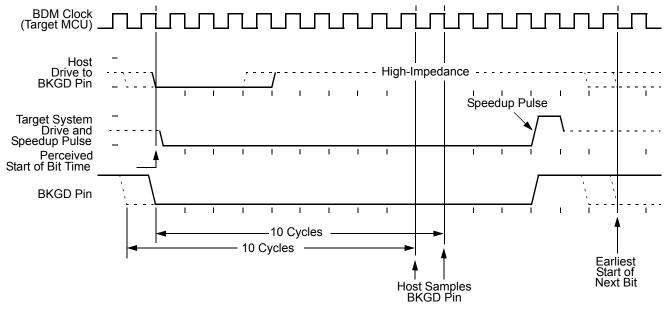

Figure 7-9 shows the host receiving a logic 0 from the target. Since the host is asynchronous to the target, there is up to a one clock-cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target. The host initiates the bit time but the target finishes it. Since the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 target clock cycles then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 target clock cycles after starting the bit time.

Figure 7-9. BDM Target-to-Host Serial Bit Timing (Logic 0)

MC9S12G Family Reference Manual Rev.1.27

| SEC[1:0] | Security State |

|----------|----------------|

| 00       | 1 (secured)    |

| 01       | 1 (secured)    |

| 10       | 0 (unsecured)  |

| 11       | 1 (secured)    |

Table 9-4. Security Bits

### NOTE

Please refer to the Flash block guide for actual security configuration (in section "Flash Module Security").

## 9.1.4 Operation of the Secured Microcontroller

By securing the device, unauthorized access to the EEPROM and Flash memory contents can be prevented. However, it must be understood that the security of the EEPROM and Flash memory contents also depends on the design of the application program. For example, if the application has the capability of downloading code through a serial port and then executing that code (e.g. an application containing bootloader code), then this capability could potentially be used to read the EEPROM and Flash memory contents even when the microcontroller is in the secure state. In this example, the security of the application could be enhanced by requiring a challenge/response authentication before any code can be downloaded.

Secured operation has the following effects on the microcontroller:

## 9.1.4.1 Normal Single Chip Mode (NS)

- Background debug module (BDM) operation is completely disabled.

- Execution of Flash and EEPROM commands is restricted. Please refer to the NVM block guide for details.

- Tracing code execution using the DBG module is disabled.

## 9.1.4.2 Special Single Chip Mode (SS)

- BDM firmware commands are disabled.

- BDM hardware commands are restricted to the register space.

- Execution of Flash and EEPROM commands is restricted. Please refer to the NVM block guide for details.

- Tracing code execution using the DBG module is disabled.

Special single chip mode means BDM is active after reset. The availability of BDM firmware commands depends on the security state of the device. The BDM secure firmware first performs a blank check of both the Flash memory and the EEPROM. If the blank check succeeds, security will be temporarily turned off and the state of the security bits in the appropriate Flash memory location can be changed If the blank check fails, security will remain active, only the BDM hardware commands will be enabled, and the accessible memory space is restricted to the peripheral register area. This will allow the BDM to be used

#### S12 Clock, Reset and Power Management Unit (S12CPMU)

|            | RTR[6:4] =   |                           |                           |                           |                           |                           |                           |                           |

|------------|--------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| RTR[3:0]   | 000<br>(OFF) | 001<br>(2 <sup>10</sup> ) | 010<br>(2 <sup>11</sup> ) | 011<br>(2 <sup>12</sup> ) | 100<br>(2 <sup>13</sup> ) | 101<br>(2 <sup>14</sup> ) | 110<br>(2 <sup>15</sup> ) | 111<br>(2 <sup>16</sup> ) |

| 1110 (÷15) | OFF          | 15x2 <sup>10</sup>        | 15x2 <sup>11</sup>        | 15x2 <sup>12</sup>        | 15x2 <sup>13</sup>        | 15x2 <sup>14</sup>        | 15x2 <sup>15</sup>        | 15x2 <sup>16</sup>        |

| 1111 (÷16) | OFF          | 16x2 <sup>10</sup>        | 16x2 <sup>11</sup>        | 16x2 <sup>12</sup>        | 16x2 <sup>13</sup>        | 16x2 <sup>14</sup>        | 16x2 <sup>15</sup>        | 16x2 <sup>16</sup>        |

#### Table 10-10. RTI Frequency Divide Rates for RTDEC = 0

<sup>1</sup> Denotes the default value out of reset. This value should be used to disable the RTI to ensure future backwards compatibility.

|            |                             | RTR[6:4] =                  |                             |                              |                              |                              |                               |                               |  |  |  |

|------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------------------------------|-------------------------------|-------------------------------|--|--|--|

| RTR[3:0]   | 000<br>(1x10 <sup>3</sup> ) | 001<br>(2x10 <sup>3</sup> ) | 010<br>(5x10 <sup>3</sup> ) | 011<br>(10x10 <sup>3</sup> ) | 100<br>(20x10 <sup>3</sup> ) | 101<br>(50x10 <sup>3</sup> ) | 110<br>(100x10 <sup>3</sup> ) | 111<br>(200x10 <sup>3</sup> ) |  |  |  |

| 0000 (÷1)  | 1x10 <sup>3</sup>           | 2x10 <sup>3</sup>           | 5x10 <sup>3</sup>           | 10x10 <sup>3</sup>           | 20x10 <sup>3</sup>           | 50x10 <sup>3</sup>           | 100x10 <sup>3</sup>           | 200x10 <sup>3</sup>           |  |  |  |

| 0001 (÷2)  | 2x10 <sup>3</sup>           | 4x10 <sup>3</sup>           | 10x10 <sup>3</sup>          | 20x10 <sup>3</sup>           | 40x10 <sup>3</sup>           | 100x10 <sup>3</sup>          | 200x10 <sup>3</sup>           | 400x10 <sup>3</sup>           |  |  |  |

| 0010 (÷3)  | 3x10 <sup>3</sup>           | 6x10 <sup>3</sup>           | 15x10 <sup>3</sup>          | 30x10 <sup>3</sup>           | 60x10 <sup>3</sup>           | 150x10 <sup>3</sup>          | 300x10 <sup>3</sup>           | 600x10 <sup>3</sup>           |  |  |  |

| 0011 (÷4)  | 4x10 <sup>3</sup>           | 8x10 <sup>3</sup>           | 20x10 <sup>3</sup>          | 40x10 <sup>3</sup>           | 80x10 <sup>3</sup>           | 200x10 <sup>3</sup>          | 400x10 <sup>3</sup>           | 800x10 <sup>3</sup>           |  |  |  |

| 0100 (÷5)  | 5x10 <sup>3</sup>           | 10x10 <sup>3</sup>          | 25x10 <sup>3</sup>          | 50x10 <sup>3</sup>           | 100x10 <sup>3</sup>          | 250x10 <sup>3</sup>          | 500x10 <sup>3</sup>           | 1x10 <sup>6</sup>             |  |  |  |

| 0101 (÷6)  | 6x10 <sup>3</sup>           | 12x10 <sup>3</sup>          | 30x10 <sup>3</sup>          | 60x10 <sup>3</sup>           | 120x10 <sup>3</sup>          | 300x10 <sup>3</sup>          | 600x10 <sup>3</sup>           | 1.2x10 <sup>6</sup>           |  |  |  |

| 0110 (÷7)  | 7x10 <sup>3</sup>           | 14x10 <sup>3</sup>          | 35x10 <sup>3</sup>          | 70x10 <sup>3</sup>           | 140x10 <sup>3</sup>          | 350x10 <sup>3</sup>          | 700x10 <sup>3</sup>           | 1.4x10 <sup>6</sup>           |  |  |  |

| 0111 (÷8)  | 8x10 <sup>3</sup>           | 16x10 <sup>3</sup>          | 40x10 <sup>3</sup>          | 80x10 <sup>3</sup>           | 160x10 <sup>3</sup>          | 400x10 <sup>3</sup>          | 800x10 <sup>3</sup>           | 1.6x10 <sup>6</sup>           |  |  |  |

| 1000 (÷9)  | 9x10 <sup>3</sup>           | 18x10 <sup>3</sup>          | 45x10 <sup>3</sup>          | 90x10 <sup>3</sup>           | 180x10 <sup>3</sup>          | 450x10 <sup>3</sup>          | 900x10 <sup>3</sup>           | 1.8x10 <sup>6</sup>           |  |  |  |

| 1001 (÷10) | 10 x10 <sup>3</sup>         | 20x10 <sup>3</sup>          | 50x10 <sup>3</sup>          | 100x10 <sup>3</sup>          | 200x10 <sup>3</sup>          | 500x10 <sup>3</sup>          | 1x10 <sup>6</sup>             | 2x10 <sup>6</sup>             |  |  |  |

| 1010 (÷11) | 11 x10 <sup>3</sup>         | 22x10 <sup>3</sup>          | 55x10 <sup>3</sup>          | 110x10 <sup>3</sup>          | 220x10 <sup>3</sup>          | 550x10 <sup>3</sup>          | 1.1x10 <sup>6</sup>           | 2.2x10 <sup>6</sup>           |  |  |  |

| 1011 (÷12) | 12x10 <sup>3</sup>          | 24x10 <sup>3</sup>          | 60x10 <sup>3</sup>          | 120x10 <sup>3</sup>          | 240x10 <sup>3</sup>          | 600x10 <sup>3</sup>          | 1.2x10 <sup>6</sup>           | 2.4x10 <sup>6</sup>           |  |  |  |

| 1100 (÷13) | 13x10 <sup>3</sup>          | 26x10 <sup>3</sup>          | 65x10 <sup>3</sup>          | 130x10 <sup>3</sup>          | 260x10 <sup>3</sup>          | 650x10 <sup>3</sup>          | 1.3x10 <sup>6</sup>           | 2.6x10 <sup>6</sup>           |  |  |  |

| 1101 (÷14) | 14x10 <sup>3</sup>          | 28x10 <sup>3</sup>          | 70x10 <sup>3</sup>          | 140x10 <sup>3</sup>          | 280x10 <sup>3</sup>          | 700x10 <sup>3</sup>          | 1.4x10 <sup>6</sup>           | 2.8x10 <sup>6</sup>           |  |  |  |

| 1110 (÷15) | 15x10 <sup>3</sup>          | 30x10 <sup>3</sup>          | 75x10 <sup>3</sup>          | 150x10 <sup>3</sup>          | 300x10 <sup>3</sup>          | 750x10 <sup>3</sup>          | 1.5x10 <sup>6</sup>           | 3x10 <sup>6</sup>             |  |  |  |

| 1111 (÷16) | 16x10 <sup>3</sup>          | 32x10 <sup>3</sup>          | 80x10 <sup>3</sup>          | 160x10 <sup>3</sup>          | 320x10 <sup>3</sup>          | 800x10 <sup>3</sup>          | 1.6x10 <sup>6</sup>           | 3.2x10 <sup>6</sup>           |  |  |  |

### Table 10-11. RTI Frequency Divide Rates for RTDEC=1

# 10.3.2.9 S12CPMU COP Control Register (CPMUCOP)

This register controls the COP (Computer Operating Properly) watchdog.

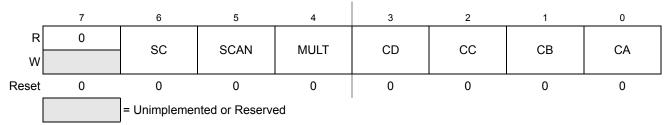

# 11.3.2.6 ATD Control Register 5 (ATDCTL5)

Writes to this register will abort current conversion sequence and start a new conversion sequence. If the external trigger function is enabled (ETRIGE=1) an initial write to ATDCTL5 is required to allow starting of a conversion sequence which will then occur on each trigger event. Start of conversion means the beginning of the sampling phase.

Module Base + 0x0005

Figure 11-8. ATD Control Register 5 (ATDCTL5)

### Read: Anytime

Write: Anytime

### Table 11-14. ATDCTL5 Field Descriptions

| Field                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>SC                  | <ul> <li>Special Channel Conversion Bit — If this bit is set, then special channel conversion can be selected using CD, CC, CB and CA of ATDCTL5. Table 11-15 lists the coding.</li> <li>O Special channel conversions disabled</li> <li>1 Special channel conversions enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5<br>SCAN                | <ul> <li>Continuous Conversion Sequence Mode — This bit selects whether conversion sequences are performed continuously or only once. If the external trigger function is enabled (ETRIGE=1) setting this bit has no effect, thus the external trigger always starts a single conversion sequence.</li> <li>0 Single conversion sequence</li> <li>1 Continuous conversion sequences (scan mode)</li> </ul>                                                                                                                                                                                                                                                                                         |

| 4<br>MULT                | Multi-Channel Sample Mode — When MULT is 0, the ATD sequence controller samples only from the specified analog input channel for an entire conversion sequence. The analog channel is selected by channel selection code (control bits CD/CC/CB/CA located in ATDCTL5). When MULT is 1, the ATD sequence controller samples across channels. The number of channels sampled is determined by the sequence length value (S8C, S4C, S2C, S1C). The first analog channel examined is determined by channel selection code (CD, CC, CB, CA control bits); subsequent channels sampled in the sequence are determined by incrementing the channel selection code or wrapping around to AN0 (channel 0). |

| 3–0<br>CD, CC,<br>CB, CA | Analog Input Channel Select Code — These bits select the analog input channel(s). Table 11-15 lists the coding used to select the various analog input channels.<br>In the case of single channel conversions (MULT=0), this selection code specifies the channel to be examined.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                          | In the case of single channel conversions (MULT=1), this selection code specifies the first channel to be examined in the conversion sequence. Subsequent channels are determined by incrementing the channel selection code or wrapping around to AN0 (after converting the channel defined by the Wrap Around Channel Select Bits WRAP3-0 in ATDCTL0). When starting with a channel number higher than the one defined by WRAP3-0 the first wrap around will be AN7 to AN0.                                                                                                                                                                                                                      |

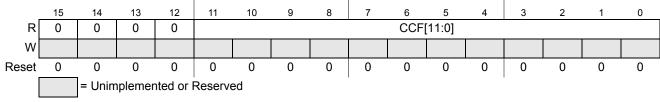

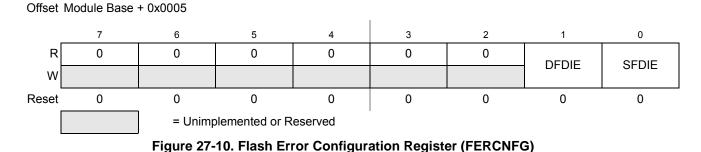

## 14.3.2.9 ATD Status Register 2 (ATDSTAT2)

This read-only register contains the Conversion Complete Flags CCF[11:0].

Module Base + 0x000A

### Read: Anytime

Write: Anytime (for details see Table 14-18 below)

### Table 14-18. ATDSTAT2 Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11–0<br>CCF[11:0] | <b>Conversion Complete Flag</b> <i>n</i> ( <i>n</i> = 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) ( <i>n conversion number, NOT channel number!</i> )— A conversion complete flag is set at the end of each conversion in a sequence. The flags are associated with the conversion position in a sequence (and also the result register number). Therefore in non-fifo mode, CCF[4] is set when the fifth conversion in a sequence is complete and the result is available in result register ATDDR4; CCF[5] is set when the sixth conversion in a sequence is complete and the result is available in ATDDR5, and so forth.                                                                                                                                        |

|                   | If automatic compare of conversion results is enabled (CMPE[ <i>n</i> ]=1 in ATDCMPE), the conversion complete flag<br>is only set if comparison with ATDDR <i>n</i> is true. If ACMPIE=1 a compare interrupt will be requested. In this case,<br>as the ATDDR <i>n</i> result register is used to hold the compare value, the result will not be stored there at the end of<br>the conversion but is lost.<br>A flag CCF[ <i>n</i> ] is cleared when one of the following occurs:<br>A) Write to ATDCTL5 (a new conversion sequence is started)<br>B) If AFFC=0, write "1" to CCF[ <i>n</i> ]<br>C) If AFFC=1 and CMPE[ <i>n</i> ]=0, read of result register ATDDR <i>n</i><br>D) If AFFC=1 and CMPE[ <i>n</i> ]=1, write to result register ATDDR <i>n</i> |

|                   | <ul> <li>In case of a concurrent set and clear on CCF[<i>n</i>]: The clearing by method A) will overwrite the set. The clearing by methods B) or C) or D) will be overwritten by the set.</li> <li>0 Conversion number <i>n</i> not completed or successfully compared</li> <li>1 If (CMPE[<i>n</i>]=0): Conversion number <i>n</i> has completed. Result is ready in ATDDR<i>n</i>.</li> <li>If (CMPE[<i>n</i>]=1): Compare for conversion result number <i>n</i> with compare value in ATDDR<i>n</i>, using compare operator CMPGT[<i>n</i>] is true. (No result available in ATDDR<i>n</i>)</li> </ul>                                                                                                                                                     |

edge or level sensitive with polarity control. Table 14-23 gives a brief description of the different combinations of control bits and their effect on the external trigger function.

In order to avoid maybe false trigger events please enable the external digital input via ATDDIEN register first and in the following enable the external trigger mode by bit ETRIGE.

| ETRIGLE | ETRIGP | ETRIGE | SCAN | Description                                                                                       |

|---------|--------|--------|------|---------------------------------------------------------------------------------------------------|

| X       | х      | 0      | 0    | Ignores external trigger. Performs one conversion sequence and stops.                             |

| X       | х      | 0      | 1    | Ignores external trigger. Performs continuous conversion sequences.                               |

| 0       | 0      | 1      | х    | Trigger falling edge sensitive. Performs one conversion sequence per trigger.                     |

| 0       | 1      | 1      | х    | Trigger rising edge sensitive. Performs one conversion sequence per trigger.                      |

| 1       | 0      | 1      | Х    | Trigger low level sensitive. Performs<br>continuous conversions while trigger level<br>is active. |

| 1       | 1      | 1      | х    | Trigger high level sensitive. Performs continuous conversions while trigger level is active.      |

Table 14-23. External Trigger Control Bits

In either level or edge sensitive modes, the first conversion begins when the trigger is received.

Once ETRIGE is enabled a conversion must be triggered externally after writing to ATDCTL5 register.

During a conversion in edge sensitive mode, if additional trigger events are detected the overrun error flag ETORF is set.

If level sensitive mode is active and the external trigger de-asserts and later asserts again during a conversion sequence, this does not constitute an overrun. Therefore, the flag is not set. If the trigger is left active in level sensitive mode when a sequence is about to complete, another sequence will be triggered immediately.

# 14.4.2.2 General-Purpose Digital Port Operation

Each ATD input pin can be switched between analog or digital input functionality. An analog multiplexer makes each ATD input pin selected as analog input available to the A/D converter.

The pad of the ATD input pin is always connected to the analog input channel of the analog mulitplexer.

Each pad input signal is buffered to the digital port register.

This buffer can be turned on or off with the ATDDIEN register for each ATD input pin. This is important so that the buffer does not draw excess current when an ATD input pin is selected as analog input to the ADC12B12C.

# 20.4.4 Baud Rate Generation

A 13-bit modulus counter in the baud rate generator derives the baud rate for both the receiver and the transmitter. The value from 0 to 8191 written to the SBR12:SBR0 bits determines the bus clock divisor. The SBR bits are in the SCI baud rate registers (SCIBDH and SCIBDL). The baud rate clock is synchronized with the bus clock and drives the receiver. The baud rate clock divided by 16 drives the transmitter. The receiver has an acquisition rate of 16 samples per bit time.

Baud rate generation is subject to one source of error:

• Integer division of the bus clock may not give the exact target frequency.

Table 20-16 lists some examples of achieving target baud rates with a bus clock frequency of 25 MHz.

### When IREN = 0 then,

SCI baud rate = SCI bus clock / (16 \* SCIBR[12:0])

| Bits<br>SBR[12:0] | Receiver<br>Clock (Hz) | Transmitter<br>Clock (Hz) | Target<br>Baud Rate | Error<br>(%) |

|-------------------|------------------------|---------------------------|---------------------|--------------|

| 41                | 609,756.1              | 38,109.8                  | 38,400              | .76          |

| 81                | 308,642.0              | 19,290.1                  | 19,200              | .47          |

| 163               | 153,374.2              | 9585.9                    | 9,600               | .16          |

| 326               | 76,687.1               | 4792.9                    | 4,800               | .15          |

| 651               | 38,402.5               | 2400.2                    | 2,400               | .01          |

| 1302              | 19,201.2               | 1200.1                    | 1,200               | .01          |

| 2604              | 9600.6                 | 600.0                     | 600                 | .00          |

| 5208              | 4800.0                 | 300.0                     | 300                 | .00          |

### Table 20-16. Baud Rates (Example: Bus Clock = 25 MHz)

- Double-buffered data register

- Serial clock with programmable polarity and phase

- Control of SPI operation during wait mode

## 21.1.3 Modes of Operation

The SPI functions in three modes: run, wait, and stop.

• Run mode

This is the basic mode of operation.

• Wait mode

SPI operation in wait mode is a configurable low power mode, controlled by the SPISWAI bit located in the SPICR2 register. In wait mode, if the SPISWAI bit is clear, the SPI operates like in run mode. If the SPISWAI bit is set, the SPI goes into a power conservative state, with the SPI clock generation turned off. If the SPI is configured as a master, any transmission in progress stops, but is resumed after CPU goes into run mode. If the SPI is configured as a slave, reception and transmission of data continues, so that the slave stays synchronized to the master.

• Stop mode

The SPI is inactive in stop mode for reduced power consumption. If the SPI is configured as a master, any transmission in progress stops, but is resumed after CPU goes into run mode. If the SPI is configured as a slave, reception and transmission of data continues, so that the slave stays synchronized to the master.

For a detailed description of operating modes, please refer to Section 21.4.7, "Low Power Mode Options".

## 21.1.4 Block Diagram

Figure 21-1 gives an overview on the SPI architecture. The main parts of the SPI are status, control and data registers, shifter logic, baud rate generator, master/slave control logic, and port control logic.

Figure 25-2. P-Flash Memory Map

Table 25-5. Program IFR Fields

| Global Address      | Size<br>(Bytes) | Field Description                                                       |

|---------------------|-----------------|-------------------------------------------------------------------------|

| 0x0_4000 - 0x0_4007 | 8               | Reserved                                                                |

| 0x0_4008 - 0x0_40B5 | 174             | Reserved                                                                |

| 0x0_40B6 - 0x0_40B7 | 2               | Version ID <sup>1</sup>                                                 |

| 0x0_40B8 - 0x0_40BF | 8               | Reserved                                                                |

| 0x0_40C0 - 0x0_40FF | 64              | Program Once Field<br>Refer to Section 25.4.6.6, "Program Once Command" |

<sup>1</sup> Used to track firmware patch versions, see Section 25.4.2

#### 32 KByte Flash Module (S12FTMRG32K1V1)

| Address<br>& Name |   | 7   | 6       | 5             | 4        | 3   | 2   | 1   | 0   |

|-------------------|---|-----|---------|---------------|----------|-----|-----|-----|-----|

| 0x000D            | R | 0   | 0       | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV2             | W |     |         |               |          |     |     |     |     |

| 0x000E            | R | 0   | 0       | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV3             | W |     |         |               |          |     |     |     |     |

| 0x000F            | R | 0   | 0       | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV4             | w |     |         |               |          |     |     |     |     |

| 0x0010            | R | NV7 | NV6     | NV5           | NV4      | NV3 | NV2 | NV1 | NV0 |

| FOPT              | w |     |         |               |          |     |     |     |     |

| 0x0011            | R | 0   | 0       | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV5             | w |     |         |               |          |     |     |     |     |

| 0x0012            | R | 0   | 0       | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV6             | w |     |         |               |          |     |     |     |     |

| 0x0013            | R | 0   | 0       | 0             | 0        | 0   | 0   | 0   | 0   |

| FRSV7             | w |     |         |               |          |     |     |     |     |

|                   | Γ |     | = Unimp | lemented or F | Reserved |     |     |     |     |

Figure 25-4. FTMRG32K1 Register Summary (continued)

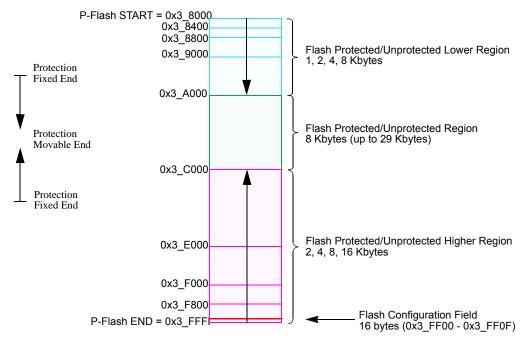

## 25.3.2.1 Flash Clock Divider Register (FCLKDIV)

The FCLKDIV register is used to control timed events in program and erase algorithms.

All bits in the FCLKDIV register are readable, bit 7 is not writable, bit 6 is write-once-hi and controls the writability of the FDIV field in normal mode. In special mode, bits 6-0 are writable any number of times but bit 7 remains unwritable.

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_F800-0x3_FFFF    | 2 Kbytes       |

| 01        | 0x3_F000-0x3_FFFF    | 4 Kbytes       |

| 10        | 0x3_E000-0x3_FFFF    | 8 Kbytes       |

| 11        | 0x3_C000-0x3_FFFF    | 16 Kbytes      |

Table 26-19. P-Flash Protection Higher Address Range

#### Table 26-20. P-Flash Protection Lower Address Range

| FPLS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_8000-0x3_83FF    | 1 Kbyte        |

| 01        | 0x3_8000-0x3_87FF    | 2 Kbytes       |

| 10        | 0x3_8000-0x3_8FFF    | 4 Kbytes       |

| 11        | 0x3_8000-0x3_9FFF    | 8 Kbytes       |

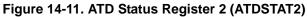

All possible P-Flash protection scenarios are shown in Figure 26-14. Although the protection scheme is loaded from the Flash memory at global address 0x3\_FFOC during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

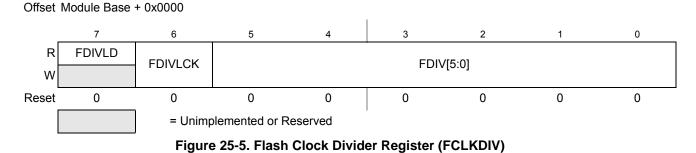

All assigned bits in the FERCNFG register are readable and writable.

#### Table 27-14. FERCNFG Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIE | <ul> <li>Double Bit Fault Detect Interrupt Enable — The DFDIE bit controls interrupt generation when a double bit fault is detected during a Flash block read operation.</li> <li>0 DFDIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the DFDIF flag is set (see Section 27.3.2.8)</li> </ul>                                                       |

| 0<br>SFDIE | <ul> <li>Single Bit Fault Detect Interrupt Enable — The SFDIE bit controls interrupt generation when a single bit fault is detected during a Flash block read operation.</li> <li>0 SFDIF interrupt disabled whenever the SFDIF flag is set (see Section 27.3.2.8)</li> <li>1 An interrupt will be requested whenever the SFDIF flag is set (see Section 27.3.2.8)</li> </ul> |

## 27.3.2.7 Flash Status Register (FSTAT)

The FSTAT register reports the operational status of the Flash module.

Offset Module Base + 0x0006

Figure 27-11. Flash Status Register (FSTAT)

<sup>1</sup> Reset value can deviate from the value shown if a double bit fault is detected during the reset sequence (see Section 27.6).

CCIF, ACCERR, and FPVIOL bits are readable and writable, MGBUSY and MGSTAT bits are readable but not writable, while remaining bits read 0 and are not writable.

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 27-55.

| CCOB<br>(CCOBIX=001) | Level Description                |

|----------------------|----------------------------------|

| 0x0000               | Return to Normal Level           |

| 0x0001               | User Margin-1 Level <sup>1</sup> |

| 0x0002               | User Margin-0 Level <sup>2</sup> |

### Table 27-55. Valid Set User Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

### Table 27-56. Set User Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                              |

|----------|-----------|------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                  |

|          |           | Set if command not available in current mode (see Table 27-27)               |

|          | ACCERR    | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 27-34) |

| FSTAT    |           | Set if an invalid margin level setting is supplied                           |

|          | FPVIOL    | None                                                                         |

|          | MGSTAT1   | None                                                                         |

|          | MGSTAT0   | None                                                                         |

### NOTE

User margin levels can be used to check that Flash memory contents have adequate margin for normal level read operations. If unexpected results are encountered when checking Flash memory contents at user margin levels, a potential loss of information has been detected.

#### 96 KByte Flash Module (S12FTMRG96K1V1)

| FCMD | Command                         | Function on P-Flash Memory                                                                                                                                                                                                                     |

|------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x02 | Erase Verify Block              | Verify that a P-Flash block is erased.                                                                                                                                                                                                         |

| 0x03 | Erase Verify<br>P-Flash Section | Verify that a given number of words starting at the address provided are erased.                                                                                                                                                               |

| 0x04 | Read Once                       | Read a dedicated 64 byte field in the nonvolatile information register in P-Flash block that was previously programmed using the Program Once command.                                                                                         |

| 0x06 | Program P-Flash                 | Program a phrase in a P-Flash block.                                                                                                                                                                                                           |

| 0x07 | Program Once                    | Program a dedicated 64 byte field in the nonvolatile information register in P-Flash block that is allowed to be programmed only once.                                                                                                         |

| 0x08 | Erase All Blocks                | Erase all P-Flash (and EEPROM) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN<br>bits in the FPROT register and the DPOPEN bit in the EEPROT register are set prior to<br>launching the command. |

| 0x09 | Erase Flash Block               | Erase a P-Flash (or EEPROM) block.<br>An erase of the full P-Flash block is only possible when FPLDIS, FPHDIS and FPOPEN<br>bits in the FPROT register are set prior to launching the command.                                                 |

| 0x0A | Erase P-Flash<br>Sector         | Erase all bytes in a P-Flash sector.                                                                                                                                                                                                           |

| 0x0B | Unsecure Flash                  | Supports a method of releasing MCU security by erasing all P-Flash (and EEPROM) blocks and verifying that all P-Flash (and EEPROM) blocks are erased.                                                                                          |

| 0x0C | Verify Backdoor<br>Access Key   | Supports a method of releasing MCU security by verifying a set of security keys.                                                                                                                                                               |

| 0x0D | Set User Margin<br>Level        | Specifies a user margin read level for all P-Flash blocks.                                                                                                                                                                                     |

| 0x0E | Set Field Margin<br>Level       | Specifies a field margin read level for all P-Flash blocks (special modes only).                                                                                                                                                               |

#### Table 28-28. P-Flash Commands

## 28.4.4.5 EEPROM Commands

Table 28-29 summarizes the valid EEPROM commands along with the effects of the commands on the EEPROM block.

| Table 28-29 | . EEPROM | Commands |

|-------------|----------|----------|

|-------------|----------|----------|

| FCMD | Command                    | Function on EEPROM Memory                               |

|------|----------------------------|---------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks | Verify that all EEPROM (and P-Flash) blocks are erased. |

| 0x02 | Erase Verify Block         | Verify that the EEPROM block is erased.                 |

## 28.4.8 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 28.4.7, "Interrupts").

## 28.4.9 Stop Mode

If a Flash command is active (CCIF = 0) when the MCU requests stop mode, the current Flash operation will be completed before the MCU is allowed to enter stop mode.

# 28.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 28-11). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x3\_FF0F. The security state out of reset can be permanently changed by programming the security byte assuming that the MCU is starting from a mode where the necessary P-Flash erase and program commands are available and that the upper region of the P-Flash is unprotected. If the Flash security byte is successfully programmed, its new value will take affect after the next MCU reset.

The following subsections describe these security-related subjects:

- Unsecuring the MCU using Backdoor Key Access

- Unsecuring the MCU in Special Single Chip Mode using BDM

- Mode and Security Effects on Flash Command Availability

# 28.5.1 Unsecuring the MCU using Backdoor Key Access

The MCU may be unsecured by using the backdoor key access feature which requires knowledge of the contents of the backdoor keys (four 16-bit words programmed at addresses 0x3\_FF00-0x3\_FF07). If the KEYEN[1:0] bits are in the enabled state (see Section 28.3.2.2), the Verify Backdoor Access Key command (see Section 28.4.6.11) allows the user to present four prospective keys for comparison to the keys stored in the Flash memory via the Memory Controller. If the keys presented in the Verify Backdoor Access Key command match the backdoor keys stored in the Flash memory, the SEC bits in the FSEC register (see Table 28-11) will be changed to unsecure the MCU. Key values of 0x0000 and 0xFFFF are not permitted as backdoor keys. While the Verify Backdoor Access Key command is active, P-Flash memory and EEPROM memory will not be available for read access and will return invalid data.

#### 240 KByte Flash Module (S12FTMRG240K2V1)

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.