Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 40                                                                      |

| Program Memory Size        | 240KB (240K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 11K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12ga240f0mlf |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Port Integration Module (S12GPIMV1)

| Global Address<br>Register Name |                             | Bit 7    | 6     | 5     | 4     | 3     | 2      | 1      | Bit 0  |

|---------------------------------|-----------------------------|----------|-------|-------|-------|-------|--------|--------|--------|

| 0x0255<br>PPSM                  | R<br>W                      | 0        | 0     | 0     | 0     | PPSM3 | PPSM2  | PPSM1  | PPSM0  |

| 0x0256<br>WOMM                  | R<br>W                      | 0        | 0     | 0     | 0     | WOMM3 | WOMM2  | WOMM1  | WOMM0  |

| 0x0257<br>PKGCR                 | R<br>W                      | APICLKS7 | 0     | 0     | 0     | 0     | PKGCR2 | PKGCR1 | PKGCR0 |

| 0x0258<br>PTP                   | R<br>W                      | PTP7     | PTP6  | PTP5  | PTP4  | PTP3  | PTP2   | PTP1   | PTP0   |

| 0x0259<br>PTIP                  | R<br>W                      | PTIP7    | PTIP6 | PTIP5 | PTIP4 | PTIP3 | PTIP2  | PTIP1  | PTIP0  |

| 0x025A<br>DDRP                  | R<br>W                      | DDRP7    | DDRP6 | DDRP5 | DDRP4 | DDRP3 | DDRP2  | DDRP1  | DDRP0  |

| 0x025B<br>Reserved              | R<br>W                      | 0        | 0     | 0     | 0     | 0     | 0      | 0      | 0      |

| 0x025C<br>PERP                  | R<br>W                      | PERP7    | PERP6 | PERP5 | PERP4 | PERP3 | PERP2  | PERP1  | PERP0  |

| 0x025D<br>PPSP                  | R<br>W                      | PPSP7    | PPSP6 | PPSP5 | PPSP4 | PPSP3 | PPSP2  | PPSP1  | PPSP0  |

| 0x025E<br>PIEP                  | R<br>W                      | PIEP7    | PIEP6 | PIEP5 | PIEP4 | PIEP3 | PIEP2  | PIEP1  | PIEP0  |

| 0x025F<br>PIFP                  | R<br>W                      | PIFP7    | PIFP6 | PIFP5 | PIFP4 | PIFP3 | PIFP2  | PIFP1  | PIFP0  |

| 0x0260–0x0267<br>Reserved       | R<br>W                      |          | 0     | 0     | 0     | 0     | 0      | 0      | 0      |

| 0x0268<br>PTJ                   | R<br>W                      | PTJ7     | PTJ6  | PTJ5  | PTJ4  | PTJ3  | PTJ2   | PTJ1   | PTJ0   |

| 0x0269<br>PTIJ                  | R<br>W                      | PTIJ7    | PTIJ6 | PTIJ5 | PTIJ4 | PTIJ3 | PTIJ2  | PTIJ1  | PTIJ0  |

| 0x026A<br>DDRJ                  | R<br>W                      | DDRJ7    | DDRJ6 | DDRJ5 | DDRJ4 | DDRJ3 | DDRJ2  | DDRJ1  | DDRJ0  |

|                                 | = Unimplemented or Reserved |          |       |       |       |       |        |        |        |

### Table 2-19. Block Register Map (G1) (continued)

Port Integration Module (S12GPIMV1)

| Global Address<br>Register Name |        | Bit 7   | 6          | 5            | 4       | 3       | 2       | 1       | Bit 0   |

|---------------------------------|--------|---------|------------|--------------|---------|---------|---------|---------|---------|

| 0x027A<br>PPS0AD                | R<br>W | PPS0AD7 | PPS0AD6    | PPS0AD5      | PPS0AD4 | PPS0AD3 | PPS0AD2 | PPS0AD1 | PPS0AD0 |

| 0x027B<br>PPS1AD                | R<br>W | PPS1AD7 | PPS1AD6    | PPS1AD5      | PPS1AD4 | PPS1AD3 | PPS1AD2 | PPS1AD1 | PPS1AD0 |

| 0x027C<br>PIE0AD                | R<br>W | PIE0AD7 | PIE0AD6    | PIE0AD5      | PIE0AD4 | PIE0AD3 | PIE0AD2 | PIE0AD1 | PIE0AD0 |

| 0x027D<br>PIE1AD                | R<br>W | PIE1AD7 | PIE1AD6    | PIE1AD5      | PIE1AD4 | PIE1AD3 | PIE1AD2 | PIE1AD1 | PIE1AD0 |

| 0x027E<br>PIF0AD                | R<br>W | PIF0AD7 | PIF0AD6    | PIF0AD5      | PIF0AD4 | PIF0AD3 | PIF0AD2 | PIF0AD1 | PIF0AD0 |

| 0x027F<br>PIF1AD                | R<br>W | PIF1AD7 | PIF1AD6    | PIF1AD5      | PIF1AD4 | PIF1AD3 | PIF1AD2 | PIF1AD1 | PIF1AD0 |

|                                 | [      |         | = Unimplem | nented or Re | served  |         |         |         |         |

### Table 2-19. Block Register Map (G1) (continued)

# 2.4.2.2 Block Register Map (G2)

### Table 2-20. Block Register Map (G2)

| Global Address<br>Register Name           |        | Bit 7                 | 6     | 5 | 4     | 3 | 2 | 1     | Bit 0  |

|-------------------------------------------|--------|-----------------------|-------|---|-------|---|---|-------|--------|

| 0x0000-0x0007                             | R      | 0                     | 0     | 0 | 0     | 0 | 0 | 0     | 0      |

| Reserved                                  | W      |                       |       |   |       |   |   |       |        |

| 0x0008                                    | R      | 0                     | 0     | 0 | 0     | 0 | 0 | PE1   | PE0    |

| PORTE                                     | W      |                       |       |   |       |   |   | FEI   | FLU    |

| 0x0009                                    | R      | 0                     | 0     | 0 | 0     | 0 | 0 | DDRE1 | DDRE0  |

| DDRE                                      | W      |                       |       |   |       |   |   | DDRET | DDILEU |

| 0x000A–0x000B<br>Non-PIM<br>Address Range | R<br>W | Non-PIM Address Range |       |   |       |   |   |       |        |

| 0x000C                                    | R      | 0                     | BKPUE | 0 | PDPEE | 0 | 0 | 0     | 0      |

| PUCR                                      | W      |                       | BRPUE |   | PDPEE |   |   |       |        |

|                                           |        |                       |       |   |       |   |   |       |        |

| 0x000D                                    | R      | 0                     | 0     | 0 | 0     | 0 | 0 | 0     | 0      |

| 0x000D<br>Reserved                        | R<br>W | 0                     | 0     | 0 | 0     | 0 | 0 | 0     | 0      |

Figure 5-10.

# 12.1.2 Modes of Operation

## 12.1.2.1 Conversion Modes

There is software programmable selection between performing **single** or **continuous conversion** on a **single channel** or **multiple channels**.

## 12.1.2.2 MCU Operating Modes

### • Stop Mode

Entering Stop Mode aborts any conversion sequence in progress and if a sequence was aborted restarts it after exiting stop mode. This has the same effect/consequences as starting a conversion sequence with write to ATDCTL5. So after exiting from stop mode with a previously aborted sequence all flags are cleared etc.

### • Wait Mode

ADC12B8C behaves same in Run and Wait Mode. For reduced power consumption continuous conversions should be aborted before entering Wait mode.

### • Freeze Mode

In Freeze Mode the ADC12B8C will either continue or finish or stop converting according to the FRZ1 and FRZ0 bits. This is useful for debugging and emulation.

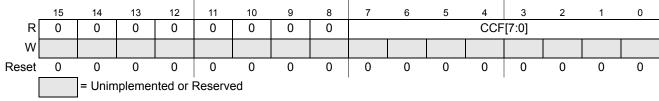

## 12.3.2.9 ATD Status Register 2 (ATDSTAT2)

This read-only register contains the Conversion Complete Flags CCF[7:0].

Module Base + 0x000A

### Read: Anytime

Write: Anytime (for details see Table 12-18 below)

#### Table 12-18. ATDSTAT2 Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>CCF[7:0] | <b>Conversion Complete Flag </b> <i>n</i> ( <i>n</i> = 7, 6, 5, 4, 3, 2, 1, 0) ( <i>n</i> conversion number, NOT channel number!)— A conversion complete flag is set at the end of each conversion in a sequence. The flags are associated with the conversion position in a sequence (and also the result register number). Therefore in non-fifo mode, CCF[4] is set when the fifth conversion in a sequence is complete and the result is available in result register ATDDR4; CCF[5] is set when the sixth conversion in a sequence is complete and the result is available in ATDDR5, and so forth.                                                                                                                                                      |

|                 | If automatic compare of conversion results is enabled (CMPE[ <i>n</i> ]=1 in ATDCMPE), the conversion complete flag<br>is only set if comparison with ATDDR <i>n</i> is true. If ACMPIE=1 a compare interrupt will be requested. In this case,<br>as the ATDDR <i>n</i> result register is used to hold the compare value, the result will not be stored there at the end of<br>the conversion but is lost.<br>A flag CCF[ <i>n</i> ] is cleared when one of the following occurs:<br>A) Write to ATDCTL5 (a new conversion sequence is started)<br>B) If AFFC=0, write "1" to CCF[ <i>n</i> ]<br>C) If AFFC=1 and CMPE[ <i>n</i> ]=0, read of result register ATDDR <i>n</i><br>D) If AFFC=1 and CMPE[ <i>n</i> ]=1, write to result register ATDDR <i>n</i> |

|                 | <ul> <li>In case of a concurrent set and clear on CCF[<i>n</i>]: The clearing by method A) will overwrite the set. The clearing by methods B) or C) or D) will be overwritten by the set.</li> <li>0 Conversion number <i>n</i> not completed or successfully compared</li> <li>1 If (CMPE[<i>n</i>]=0): Conversion number <i>n</i> has completed. Result is ready in ATDDR<i>n</i>.</li> <li>If (CMPE[<i>n</i>]=1): Compare for conversion result number <i>n</i> with compare value in ATDDR<i>n</i>, using compare operator CMPGT[<i>n</i>] is true. (No result available in ATDDR<i>n</i>)</li> </ul>                                                                                                                                                     |

# 12.4 Functional Description

The ADC12B8C consists of an analog sub-block and a digital sub-block.

# 12.4.1 Analog Sub-Block

The analog sub-block contains all analog electronics required to perform a single conversion. Separate power supplies VDDA and VSSA allow to isolate noise of other MCU circuitry from the analog sub-block.

## 12.4.1.1 Sample and Hold Machine

The Sample and Hold Machine controls the storage and charge of the sample capacitor to the voltage level of the analog signal at the selected ADC input channel.

During the sample process the analog input connects directly to the storage node.

The input analog signals are unipolar and must be within the potential range of VSSA to VDDA.

During the hold process the analog input is disconnected from the storage node.

## 12.4.1.2 Analog Input Multiplexer

The analog input multiplexer connects one of the 8 external analog input channels to the sample and hold machine.

## 12.4.1.3 Analog-to-Digital (A/D) Machine

The A/D Machine performs analog to digital conversions. The resolution is program selectable to be either 8 or 10 or 12 bits. The A/D machine uses a successive approximation architecture. It functions by comparing the sampled and stored analog voltage with a series of binary coded discrete voltages.

By following a binary search algorithm, the A/D machine identifies the discrete voltage that is nearest to the sampled and stored voltage.

When not converting the A/D machine is automatically powered down.

Only analog input signals within the potential range of VRL to VRH (A/D reference potentials) will result in a non-railed digital output code.

# 12.4.2 Digital Sub-Block

This subsection describes some of the digital features in more detail. See Section 12.3.2, "Register Descriptions" for all details.

## 12.4.2.1 External Trigger Input

The external trigger feature allows the user to synchronize ATD conversions to an external event rather than relying only on software to trigger the ATD module when a conversion is about to take place. The external trigger signal (out of reset ATD channel 7, configurable in ATDCTL1) is programmable to be edge

#### Analog-to-Digital Converter (ADC12B12CV2)

| Address | Name               | -      | Bit 7 | 6     | 5            | 4              | 3              | 2                               | 1                                     | Bit 0 |

|---------|--------------------|--------|-------|-------|--------------|----------------|----------------|---------------------------------|---------------------------------------|-------|

| 0x0003  | ATDCTL3            | R<br>W | DJM   | S8C   | S4C          | S2C            | S1C            | FIFO                            | FRZ1                                  | FRZ0  |

| 0x0004  | ATDCTL4            | R<br>W | SMP2  | SMP1  | SMP0         |                |                | PRS[4:0]                        |                                       |       |

| 0x0005  | ATDCTL5            | R<br>W | 0     | SC    | SCAN         | MULT           | CD             | CC                              | СВ                                    | CA    |

| 0x0006  | ATDSTAT0           | R<br>W | SCF   | 0     | ETORF        | FIFOR          | CC3            | CC2                             | CC1                                   | CC0   |

| 0x0007  | Unimple-<br>mented | R<br>W | 0     | 0     | 0            | 0              | 0              | 0                               | 0                                     | 0     |

| 0x0008  | ATDCMPEH           | R<br>W | 0     | 0     | 0            | 0              |                | CMPE                            | E[11:8]                               |       |

| 0x0009  | ATDCMPEL           | R<br>W |       |       |              | CM             | PE[7:0]        |                                 |                                       |       |

| 0x000A  | ATDSTAT2H          | R<br>W | 0     | 0     | 0            | 0              |                | CCF                             | [11:8]                                |       |

| 0x000B  | ATDSTAT2L          | R<br>W |       |       |              | CC             | F[7:0]         |                                 |                                       |       |

| 0x000C  | ATDDIENH           | R<br>W | 1     | 1     | 1            | 1<br>IEN[11:8] |                |                                 |                                       |       |

| 0x000D  | ATDDIENL           | R<br>W |       |       |              | IE             | N[7:0]         |                                 |                                       |       |

| 0x000E  | ATDCMPHTH          | R<br>W | 0     | 0     | 0            | 0 CMPHT[11:8]  |                |                                 |                                       |       |

| 0x000F  | ATDCMPHTL          | R      |       |       |              | CMF            | PHT[7:0]       |                                 |                                       |       |

| 0x0010  | ATDDR0             | W<br>R |       |       |              |                |                | esult Data (D                   | · · · · · · · · · · · · · · · · · · · |       |

| 0x0012  | ATDDR1             | W<br>R |       | See S | Section 14.3 | .2.12.1, "Le   | ft Justified R | tesult Data (E<br>esult Data (D | JM=0)"                                |       |

| 0x0014  | ATDDR2             | W<br>R |       | See S | Section 14.3 | .2.12.1, "Le   | ft Justified R | esult Data (E<br>esult Data (D  | JM=0)"                                |       |

| 0x0016  | ATDDR3             | W<br>R |       | See S | Section 14.3 | .2.12.1, "Le   | ft Justified R | esult Data (E<br>esult Data (D  | JM=0)"                                |       |

| 0x0018  | ATDDR4             | W<br>R |       | See S | Section 14.3 | .2.12.1, "Le   | ft Justified R | esult Data (E<br>esult Data (D  | JM=0)"                                |       |

| 0x001A  | ATDDR5             | W<br>R |       | See S | Section 14.3 | .2.12.1, "Le   | ft Justified R | esult Data (E<br>esult Data (D  | JM=0)"                                |       |

| 0x001C  | ATDDR6             | W<br>R |       | See S | Section 14.3 | .2.12.1, "Le   | ft Justified R | esult Data (E<br>esult Data (D  | JM=0)"                                |       |

| 0x001E  | ATDDR7             | W<br>R |       | See S | Section 14.3 | .2.12.1, "Le   | ft Justified R | tesult Data (E<br>esult Data (D | JM=0)"                                |       |

| 0x0020  | ATDDR8             | W<br>R |       | See S | Section 14.3 | .2.12.1, "Le   | ft Justified R | tesult Data (E<br>esult Data (D | JM=0)"                                |       |

| 0x0022  | ATDDR9             | W<br>R |       | See S | Section 14.3 | .2.12.1, "Le   | ft Justified R | tesult Data (E<br>esult Data (D | JM=0)"                                |       |

| UNUUZZ  |                    | W      |       | -     |              |                | ht Justified R | tesult Data (E                  | OJM=1)"                               |       |

|         |                    | l      |       |       | mented or R  |                | (0)            |                                 |                                       |       |

Figure 14-2. ADC12B12C Register Summary (Sheet 2 of 3)

| SC | CD | сс | СВ | СА | Analog Input<br>Channel |

|----|----|----|----|----|-------------------------|

| 1  | 0  | 0  | 0  | 0  | Internal_6,             |

|    | 0  | 0  | 0  | 1  | Internal_7              |

|    | 0  | 0  | 1  | 0  | Internal_0              |

|    | 0  | 0  | 1  | 1  | Internal_1              |

|    | 0  | 1  | 0  | 0  | VRH                     |

|    | 0  | 1  | 0  | 1  | VRL                     |

|    | 0  | 1  | 1  | 0  | (VRH+VRL) / 2           |

|    | 0  | 1  | 1  | 1  | Reserved                |

|    | 1  | 0  | 0  | 0  | Internal_2              |

|    | 1  | 0  | 0  | 1  | Internal_3              |

|    | 1  | 0  | 1  | 0  | Internal_4              |

|    | 1  | 0  | 1  | 1  | Internal_5              |

|    | 1  | 1  | Х  | Х  | Reserved                |

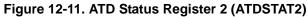

#### Scalable Controller Area Network (S12MSCANV3)

In cases of more than one buffer having the same lowest priority, the message buffer with the lower index number wins.

Figure 18-36. Transmit Buffer Priority Register (TBPR)

<sup>1</sup> Read: Anytime when TXEx flag is set (see Section 18.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 18.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

Write: Anytime when TXEx flag is set (see Section 18.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 18.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

## 18.3.3.5 Time Stamp Register (TSRH–TSRL)

If the TIME bit is enabled, the MSCAN will write a time stamp to the respective registers in the active transmit or receive buffer right after the EOF of a valid message on the CAN bus (see Section 18.3.2.1, "MSCAN Control Register 0 (CANCTL0)"). In case of a transmission, the CPU can only read the time stamp after the respective transmit buffer has been flagged empty.

The timer value, which is used for stamping, is taken from a free running internal CAN bit clock. A timer overrun is not indicated by the MSCAN. The timer is reset (all bits set to 0) during initialization mode. The CPU can only read the time stamp registers.

| Module Base - | + 0x00XE |       |       |       |         |       | Access: Us | er read/write <sup>1</sup> |

|---------------|----------|-------|-------|-------|---------|-------|------------|----------------------------|

| _             | 7        | 6     | 5     | 4     | 3       | 2     | 1          | 0                          |

| R             | TSR15    | TSR14 | TSR13 | TSR12 | TSR11   | TSR10 | TSR9       | TSR8                       |

| w             |          |       |       |       |         |       |            |                            |

| Reset:        | х        | х     | х     | х     | х       | х     | х          | х                          |

|               |          |       |       |       | · · · · | (     |            |                            |

Read: For transmit buffers: Anytime when TXEx flag is set (see Section 18.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 18.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). For receive buffers: Anytime when RXF is set. Write: Unimplemented

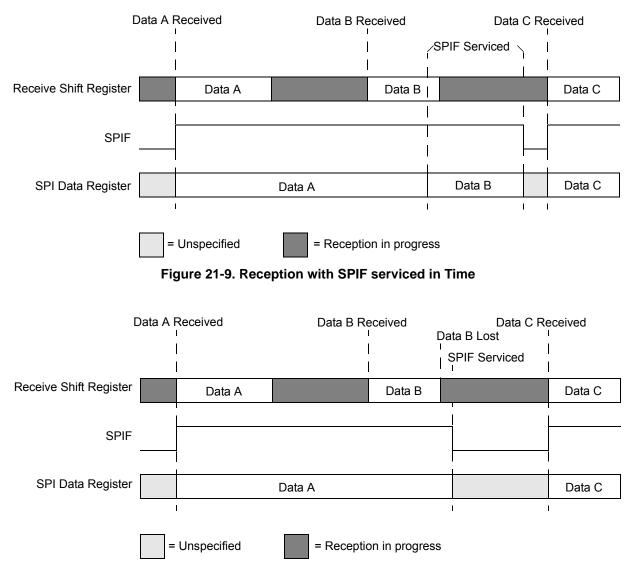

Serial Peripheral Interface (S12SPIV5)

Figure 21-10. Reception with SPIF serviced too late

# 21.4 Functional Description

The SPI module allows a duplex, synchronous, serial communication between the MCU and peripheral devices. Software can poll the SPI status flags or SPI operation can be interrupt driven.

The SPI system is enabled by setting the SPI enable (SPE) bit in SPI control register 1. While SPE is set, the four associated SPI port pins are dedicated to the SPI function as:

- Slave select  $(\overline{SS})$

- Serial clock (SCK)

- Master out/slave in (MOSI)

- Master in/slave out (MISO)

Table 26-36. Erase Verify P-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |  |  |  |  |

|-------------|----------------------------------------------------------|----------------------------------------------|--|--|--|--|

| 000         | 0x03                                                     | Global address [17:16] of<br>a P-Flash block |  |  |  |  |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |  |  |  |  |

| 010         | Number of phras                                          | ses to be verified                           |  |  |  |  |

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 26-37. Erase Verify P-Flash Section Command Error Handling

| Register | Error Bit | Error Condition                                                                                   |  |  |  |

|----------|-----------|---------------------------------------------------------------------------------------------------|--|--|--|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                                                       |  |  |  |

|          |           | Set if command not available in current mode (see Table 26-27)                                    |  |  |  |

|          | ACCERR    | Set if an invalid global address [17:0] is supplied see Table 26-3)                               |  |  |  |

|          |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                      |  |  |  |

| FSTAT    |           | Set if the requested section crosses a the P-Flash address boundary                               |  |  |  |

|          | FPVIOL    | None                                                                                              |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                 |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |  |  |  |

### 26.4.6.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once command described in Section 26.4.6.6. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

Table 26-38. Read Once Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                         |              |  |  |  |  |

|-------------|------------------------------------------|--------------|--|--|--|--|

| 000         | 0x04 Not Required                        |              |  |  |  |  |

| 001         | Read Once phrase index (0x0000 - 0x0007) |              |  |  |  |  |

| 010         | Read Once word 0 value                   |              |  |  |  |  |

| 011         | Read Once word 1 value                   |              |  |  |  |  |

| 100         | Read Once word 2 value                   |              |  |  |  |  |

| 101         | Read Once                                | word 3 value |  |  |  |  |

### CAUTION

The FCLKDIV register should never be written while a Flash command is executing (CCIF=0).

| Field            | Description                                                                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written since the last reset<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                   |

| 6<br>FDIVLCK     | <ul> <li>Clock Divider Locked</li> <li>FDIV field is open for writing</li> <li>FDIV value is locked and cannot be changed. Once the lock bit is set high, only reset can clear this bit and restore writability to the FDIV field in normal mode.</li> </ul>                                                                       |

| 5–0<br>FDIV[5:0] | <b>Clock Divider Bits</b> — FDIV[5:0] must be set to effectively divide BUSCLK down to 1 MHz to control timed events during Flash program and erase algorithms. Table 27-8 shows recommended values for FDIV[5:0] based on the BUSCLK frequency. Please refer to Section 27.4.4, "Flash Command Operations," for more information. |

| BUSCLK Frequency<br>(MHz) |                  | FDIV[5:0] | BUSCLK Frequency<br>(MHz) |                  | FDIV[5:0] |

|---------------------------|------------------|-----------|---------------------------|------------------|-----------|

| MIN <sup>1</sup>          | MAX <sup>2</sup> |           | MIN <sup>1</sup>          | MAX <sup>2</sup> |           |

| 1.0                       | 1.6              | 0x00      | 16.6                      | 17.6             | 0x10      |

| 1.6                       | 2.6              | 0x01      | 17.6                      | 18.6             | 0x11      |

| 2.6                       | 3.6              | 0x02      | 18.6                      | 19.6             | 0x12      |

| 3.6                       | 4.6              | 0x03      | 19.6                      | 20.6             | 0x13      |

| 4.6                       | 5.6              | 0x04      | 20.6                      | 21.6             | 0x14      |

| 5.6                       | 6.6              | 0x05      | 21.6                      | 22.6             | 0x15      |

| 6.6                       | 7.6              | 0x06      | 22.6                      | 23.6             | 0x16      |

| 7.6                       | 8.6              | 0x07      | 23.6                      | 24.6             | 0x17      |

| 8.6                       | 9.6              | 0x08      | 24.6                      | 25.6             | 0x18      |

| 9.6                       | 10.6             | 0x09      |                           |                  |           |

| 10.6                      | 11.6             | 0x0A      |                           |                  |           |

| 11.6                      | 12.6             | 0x0B      |                           |                  |           |

| 12.6                      | 13.6             | 0x0C      |                           |                  |           |

| 13.6                      | 14.6             | 0x0D      |                           |                  |           |

| 14.6                      | 15.6             | 0x0E      |                           |                  |           |

| 15.6                      | 16.6             | 0x0F      |                           |                  |           |

#### Table 27-8. FDIV values for various BUSCLK Frequencies

<sup>1</sup> BUSCLK is Greater Than this value.

<sup>2</sup> BUSCLK is Less Than or Equal to this value.

96 KByte Flash Module (S12FTMRG96K1V1)

#### 96 KByte Flash Module (S12FTMRG96K1V1)

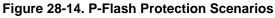

Figure 28-26. Generic Flash Command Write Sequence Flowchart

### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

The Flash memory may be read as bytes and aligned words. Read access time is one bus cycle for bytes and aligned words. For misaligned words access, the CPU has to perform twice the byte read access command. For Flash memory, an erased bit reads 1 and a programmed bit reads 0.

It is possible to read from P-Flash memory while some commands are executing on EEPROM memory. It is not possible to read from EEPROM memory while a command is executing on P-Flash memory. Simultaneous P-Flash and EEPROM operations are discussed in Section 29.4.5.

Both P-Flash and EEPROM memories are implemented with Error Correction Codes (ECC) that can resolve single bit faults and detect double bit faults. For P-Flash memory, the ECC implementation requires that programming be done on an aligned 8 byte basis (a Flash phrase). Since P-Flash memory is always read by half-phrase, only one single bit fault in an aligned 4 byte half-phrase containing the byte or word accessed will be corrected.

## 29.1.1 Glossary

**Command Write Sequence** — An MCU instruction sequence to execute built-in algorithms (including program and erase) on the Flash memory.

**EEPROM Memory** — The EEPROM memory constitutes the nonvolatile memory store for data.

**EEPROM Sector** — The EEPROM sector is the smallest portion of the EEPROM memory that can be erased. The EEPROM sector consists of 4 bytes.

**NVM Command Mode** — An NVM mode using the CPU to setup the FCCOB register to pass parameters required for Flash command execution.

**Phrase** — An aligned group of four 16-bit words within the P-Flash memory. Each phrase includes two sets of aligned double words with each set including 7 ECC bits for single bit fault correction and double bit fault detection within each double word.

**P-Flash Memory** — The P-Flash memory constitutes the main nonvolatile memory store for applications.

**P-Flash Sector** — The P-Flash sector is the smallest portion of the P-Flash memory that can be erased. Each P-Flash sector contains 512 bytes.

**Program IFR** — Nonvolatile information register located in the P-Flash block that contains the Version ID, and the Program Once field.

# 30.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 30-11). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x3\_FF0F. The security state out of reset can be permanently changed by programming the security byte assuming that the MCU is starting from a mode where the necessary P-Flash erase and program commands are available and that the upper region of the P-Flash is unprotected. If the Flash security byte is successfully programmed, its new value will take affect after the next MCU reset.

The following subsections describe these security-related subjects:

- Unsecuring the MCU using Backdoor Key Access

- Unsecuring the MCU in Special Single Chip Mode using BDM

- Mode and Security Effects on Flash Command Availability

## 30.5.1 Unsecuring the MCU using Backdoor Key Access

The MCU may be unsecured by using the backdoor key access feature which requires knowledge of the contents of the backdoor keys (four 16-bit words programmed at addresses 0x3\_FF00-0x3\_FF07). If the KEYEN[1:0] bits are in the enabled state (see Section 30.3.2.2), the Verify Backdoor Access Key command (see Section 30.4.6.11) allows the user to present four prospective keys for comparison to the keys stored in the Flash memory via the Memory Controller. If the keys presented in the Verify Backdoor Access Key command match the backdoor keys stored in the Flash memory, the SEC bits in the FSEC register (see Table 30-11) will be changed to unsecure the MCU. Key values of 0x0000 and 0xFFFF are not permitted as backdoor keys. While the Verify Backdoor Access Key command is active, P-Flash memory and EEPROM memory will not be available for read access and will return invalid data.

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 30.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 30.4.6.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0x3\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x3\_FF00-0x3\_FF07 are unaffected by the Verify Backdoor Access Key command sequence. The Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be

**Electrical Characteristics**

| CPMU REGISTER | Bit settings/Conditions                                                                       |

|---------------|-----------------------------------------------------------------------------------------------|

| CPMUOSC       | OSCE=1, External Square wave on EXTAL f <sub>EXTAL</sub> =4MHz, $V_{IH}$ = 1.8V, $V_{IL}$ =0V |

| CPMURTI       | RTDEC=0, RTR[6:4]=111, RTR[3:0]=1111;                                                         |

| CPMUCOP       | WCOP=1, CR[2:0]=111                                                                           |

Table A-12. CPMU Configuration for Pseudo Stop Current Measurement

#### Table A-13. CPMU Configuration for Run/Wait and Full Stop Current Measurement

| CPMU REGISTER                             | Bit settings/Conditions                                                                    |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| CPMUSYNR                                  | VCOFRQ[1:0]=01,SYNDIV[5:0] = 24                                                            |  |  |  |

| CPMUPOSTDIV                               | POSTDIV[4:0]=0                                                                             |  |  |  |

| CPMUCLKS                                  | PLLSEL=1                                                                                   |  |  |  |

| CPMUOSC                                   | OSCE=0,<br>Reference clock for PLL is f <sub>ref</sub> =f <sub>irc1m</sub> trimmed to 1MHz |  |  |  |

| API settings for STOP current measurement |                                                                                            |  |  |  |

| CPMUAPICTL                                | APIEA=0, APIFE=1, APIE=0                                                                   |  |  |  |

| CPMUAPITR                                 | trimmed to 10Khz                                                                           |  |  |  |

| CPMUAPIRH/RL                              | set to \$FFFF                                                                              |  |  |  |

#### Table A-14. Peripheral Configurations for Run & Wait Current Measurement

| Peripheral | Configuration                                                                                                                                      |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MSCAN      | Configured to loop-back mode using a bit rate of 1Mbit/s                                                                                           |  |  |

| SPI        | Configured to master mode, continuously transmit data (0x55 or 0xAA) at 1Mbit/s                                                                    |  |  |

| SCI        | Configured into loop mode, continuously transmit data (0x55) at speed of 57600 baud                                                                |  |  |

| PWM        | Configured to toggle its pins at the rate of 40kHz                                                                                                 |  |  |

| ADC        | The peripheral is configured to operate at its maximum specified frequency and to continuously convert voltages on all input channels in sequence. |  |  |

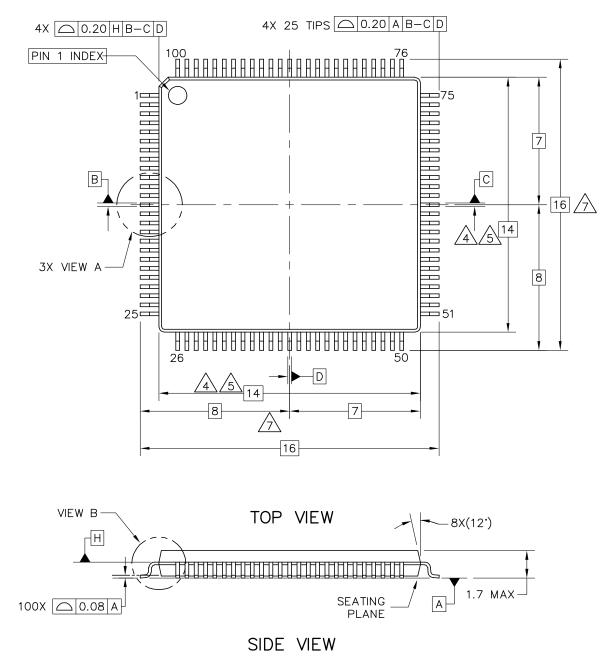

Package and Die Information

# D.1 100 LQFP Mechanical Dimensions

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |             | AL OUTLINE PRINT VERSION NOT TO SCALE |                | T TO SCALE |

|---------------------------------------------------------|-------------|---------------------------------------|----------------|------------|

| TITLE:                                                  |             | DOCUMENT NO                           | ): 98ASS23308W | REV: H     |

| 100 LEAD LQFP<br>14 X 14, 0.5 PITCH, 1.4                | CASE NUMBER | 2: 983–02                             | 25 MAY 2005    |            |

|                                                         |             | STANDARD: NO                          | DN-JEDEC       |            |