### NXP USA Inc. - S9S12GA240F0MLH Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 54                                                                      |

| Program Memory Size        | 240KB (240K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 11K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12ga240f0mlh |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | <     | Fund<br>owestPRIO |              | Power        | Internal Pull<br>Resistor |            |                |

|-------------|-------|-------------------|--------------|--------------|---------------------------|------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.      | 3rd<br>Func. | 4th<br>Func. | Supply                    | CTRL       | Reset<br>State |

| 86          | PS4   | MISO0             | _            | _            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 87          | PS5   | MOSI0             | _            | —            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 88          | PS6   | SCK0              | _            | —            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 89          | PS7   | API_EXTC<br>LK    | SS0          | _            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 90          | VSSX2 | _                 | _            | _            | —                         |            | —              |

| 91          | VDDX2 | _                 | _            | _            | —                         |            | —              |

| 92          | PM0   | RXCAN             | _            | —            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 93          | PM1   | TXCAN             | _            | _            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 94          | PD4   | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 95          | PD5   | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 96          | PD6   | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 97          | PD7   | —                 | —            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 98          | PM2   | RXD2              | —            | —            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 99          | PM3   | TXD2              | _            | —            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 100         | PJ7   | KWJ7              | SS2          |              | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

Table 1-31. 100-Pin LQFP Pinout for S12GA192 and S12GA240

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

| Global Address<br>Register Name |                             | Bit 7  | 6      | 5       | 4       | 3       | 2       | 1      | Bit 0  |  |  |

|---------------------------------|-----------------------------|--------|--------|---------|---------|---------|---------|--------|--------|--|--|

| 0x0246                          | R                           | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |  |  |

| Reserved                        | W                           |        |        |         |         |         |         |        |        |  |  |

| 0x0247<br>Reserved              | R<br>W                      | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |  |  |

| 0x0248<br>PTS                   | R<br>W                      | PTS7   | PTS6   | PTS5    | PTS4    | PTS3    | PTS2    | PTS1   | PTS0   |  |  |

| 0x0249<br>PTIS                  | R<br>W                      | PTIS7  | PTIS6  | PTIS5   | PTIS4   | PTIS3   | PTIS2   | PTIS1  | PTIS0  |  |  |

| 0x024A<br>DDRS                  | R<br>W                      | DDRS7  | DDRS6  | DDRS5   | DDRS4   | DDRS3   | DDRS2   | DDRS1  | DDRS0  |  |  |

| 0x024B<br>Reserved              | R<br>W                      | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |  |  |

| 0x024C<br>PERS                  | R<br>W                      | PERS7  | PERS6  | PERS5   | PERS4   | PERS3   | PERS2   | PERS1  | PERS0  |  |  |

| 0x024D<br>PPSS                  | R<br>W                      | PPSS7  | PPSS6  | PPSS5   | PPSS4   | PPSS3   | PPSS2   | PPSS1  | PPSS0  |  |  |

| 0x024E<br>WOMS                  | R<br>W                      | WOMS7  | WOMS6  | WOMS5   | WOMS4   | WOMS3   | WOMS2   | WOMS1  | WOMS0  |  |  |

| 0x024F<br>PRR0                  | R<br>W                      | PRR0P3 | PRR0P2 | PRR0T31 | PRR0T30 | PRR0T21 | PRR0T20 | PRR0S1 | PRR0S0 |  |  |

| 0x0250<br>PTM                   | R<br>W                      | 0      | 0      | 0       | 0       | PTM3    | PTM2    | PTM1   | PTM0   |  |  |

| 0x0251<br>PTIM                  | R<br>W                      | 0      | 0      | 0       | 0       | PTIM3   | PTIM2   | PTIM1  | PTIM0  |  |  |

| 0x0252<br>DDRM                  | R<br>W                      | 0      | 0      | 0       | 0       | DDRM3   | DDRM2   | DDRM1  | DDRM0  |  |  |

| 0x0253<br>Reserved              | R<br>W                      | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |  |  |

| 0x0254<br>PERM                  | R<br>W                      | 0      | 0      | 0       | 0       | PERM3   | PERM2   | PERM1  | PERM0  |  |  |

|                                 | = Unimplemented or Reserved |        |        |         |         |         |         |        |        |  |  |

### Table 2-19. Block Register Map (G1) (continued)

#### S12S Debug Module (S12SDBGV2)

All comparators are disabled in BDM and during BDM accesses.

The comparator match control logic (see Figure 8-23) configures comparators to monitor the buses for an exact address or an address range, whereby either an access inside or outside the specified range generates a match condition. The comparator configuration is controlled by the control register contents and the range control by the DBGC2 contents.

A match can initiate a transition to another state sequencer state (see Section 8.4.4, "State Sequence Control"). The comparator control register also allows the type of access to be included in the comparison through the use of the RWE, RW, SZE, and SZ bits. The RWE bit controls whether read or write comparison is enabled for the associated comparator and the RW bit selects either a read or write access for a valid match. Similarly the SZE and SZ bits allow the size of access (word or byte) to be considered in the compare. Only comparators A and B feature SZE and SZ.

The TAG bit in each comparator control register is used to determine the match condition. By setting TAG, the comparator qualifies a match with the output of opcode tracking logic and a state sequencer transition occurs when the tagged instruction reaches the CPU execution stage. Whilst tagging the RW, RWE, SZE, and SZ bits and the comparator data registers are ignored; the comparator address register must be loaded with the exact opcode address.

If the TAG bit is clear (forced type match) a comparator match is generated when the selected address appears on the system address bus. If the selected address is an opcode address, the match is generated when the opcode is fetched from the memory, which precedes the instruction execution by an indefinite number of cycles due to instruction pipelining. For a comparator match of an opcode at an odd address when TAG = 0, the corresponding even address must be contained in the comparator register. Thus for an opcode at odd address (n), the comparator register must contain address (n–1).

Once a successful comparator match has occurred, the condition that caused the original match is not verified again on subsequent matches. Thus if a particular data value is verified at a given address, this address may not still contain that data value when a subsequent match occurs.

Match[0, 1, 2] map directly to Comparators [A, B, C] respectively, except in range modes (see Section 8.3.2.4, "Debug Control Register2 (DBGC2)). Comparator channel priority rules are described in the priority section (Section 8.4.3.4, "Channel Priorities).

### 8.4.2.1 Single Address Comparator Match

With range comparisons disabled, the match condition is an exact equivalence of address bus with the value stored in the comparator address registers. Further qualification of the type of access (R/W, word/byte) and databus contents is possible, depending on comparator channel.

### 8.4.2.1.1 Comparator C

Comparator C offers only address and direction (R/W) comparison. The exact address is compared, thus with the comparator address register loaded with address (n) a word access of address (n-1) also accesses (n) but does not cause a match.

# **10.7** Initialization/Application Information

# **10.7.1** General Initialization information

Usually applications run in MCU Normal Mode.

It is recommended to write the CPMUCOP register in any case from the application program initialization routine after reset no matter if the COP is used in the application or not, even if a configuration is loaded via the flash memory after reset. By doing a "controlled" write access in MCU Normal Mode (with the right value for the application) the write once for the COP configuration bits (WCOP,CR[2:0]) takes place which protects these bits from further accidental change. In case of a program sequencing issue (code runaway) the COP configuration can not be accidentally modified anymore.

# 10.7.2 Application information for COP and API usage

In many applications the COP is used to check that the program is running and sequencing properly. Often the COP is kept running during Stop Mode and periodic wake-up events are needed to service the COP on time and maybe to check the system status.

For such an application it is recommended to use the ACLK as clock source for both COP and API. This guarantees lowest possible IDD current during Stop Mode. Additionally it eases software implementation using the same clock source for both, COP and API.

The Interrupt Service Routine (ISR) of the Autonomous Periodic Interrupt API should contain the write instruction to the CPMUARMCOP register. The value (byte) written is derived from the "main routine" (alternating sequence of \$55 and \$AA) of the application software.

Using this method, then in the case of a runtime or program sequencing issue the application "main routine" is not executed properly anymore and the alternating values are not provided properly. Hence the COP is written at the correct time (due to independent API interrupt request) but the wrong value is written (alternating sequence of \$55 and \$AA is no longer maintained) which causes a COP reset.

## 12.3.2.12 ATD Conversion Result Registers (ATDDRn)

The A/D conversion results are stored in 8 result registers. Results are always in unsigned data representation. Left and right justification is selected using the DJM control bit in ATDCTL3.

If automatic compare of conversions results is enabled (CMPE[n]=1 in ATDCMPE), these registers must be written with the compare values in left or right justified format depending on the actual value of the DJM bit. In this case, as the ATDDRn register is used to hold the compare value, the result will not be stored there at the end of the conversion but is lost.

### Attention, n is the conversion number, NOT the channel number!

Read: Anytime

Write: Anytime

### NOTE

For conversions not using automatic compare, results are stored in the result registers after each conversion. In this case avoid writing to ATDDRn except for initial values, because an A/D result might be overwritten.

### 12.3.2.12.1 Left Justified Result Data (DJM=0)

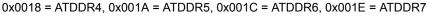

Module Base +

0x0010 = ATDDR0, 0x0012 = ATDDR1, 0x0014 = ATDDR2, 0x0016 = ATDDR3

Figure 12-14. Left justified ATD conversion result register (ATDDRn)

Table 12-21 shows how depending on the A/D resolution the conversion result is transferred to the ATD result registers for left justified data. Compare is always done using all 12 bits of both the conversion result and the compare value in ATDDRn.

| A/D<br>resolution | DJM | conversion result mapping to ATDDR <i>n</i>                   |

|-------------------|-----|---------------------------------------------------------------|

| 8-bit data        | 0   | Result-Bit[11:4] = conversion result,<br>Result-Bit[3:0]=0000 |

| 10-bit data       | 0   | Result-Bit[11:2] = conversion result,<br>Result-Bit[1:0]=00   |

| 12-bit data       | 0   | Result-Bit[11:0] = result                                     |

| Table 12-21. Conve | rsion result <b>i</b> | mapping to | ATDDRn |

|--------------------|-----------------------|------------|--------|

|--------------------|-----------------------|------------|--------|

Analog-to-Digital Converter (ADC10B16CV2)

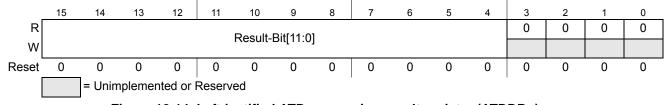

# 15.3.2.7 ATD Status Register 0 (ATDSTAT0)

This register contains the Sequence Complete Flag, overrun flags for external trigger and FIFO mode, and the conversion counter.

Module Base + 0x0006

Figure 15-9. ATD Status Register 0 (ATDSTAT0)

Read: Anytime

Write: Anytime (No effect on (CC3, CC2, CC1, CC0))

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SCF   | Sequence Complete Flag — This flag is set upon completion of a conversion sequence. If conversion sequences are continuously performed (SCAN=1), the flag is set after each one is completed. This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to SCF</li> <li>B) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>C) If AFFC=1 and a result register is read</li> </ul> <li>O Conversion sequence not completed</li> <li>1 Conversion sequence has completed</li>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5<br>ETORF | <ul> <li>External Trigger Overrun Flag — While in edge sensitive mode (ETRIGLE=0), if additional active edges are detected while a conversion sequence is in process the overrun flag is set. This flag is cleared when one of the following occurs:         <ul> <li>A) Write "1" to ETORF</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> </li> <li>No External trigger overrun error has occurred</li> <li>External trigger overrun error has occurred</li> </ul>                                                                                                                                                                                                                                                                                                                    |

| 4<br>FIFOR | Result Register Overrun Flag — This bit indicates that a result register has been written to before its associated conversion complete flag (CCF) has been cleared. This flag is most useful when using the FIFO mode because the flag potentially indicates that result registers are out of sync with the input channels. However, it is also practical for non-FIFO modes, and indicates that a result register has been overwritten before it has been read (i.e. the old data has been lost). This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to FIFOR</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> <li>No overrun has occurred</li> <li>Overrun condition exists (result register has been written while associated CCFx flag was still set)</li> |

| ETRIGSEL | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 | External trigger source is |

|----------|----------|----------|----------|----------|----------------------------|

| 0        | 0        | 0        | 0        | 0        | AN0                        |

| 0        | 0        | 0        | 0        | 1        | AN1                        |

| 0        | 0        | 0        | 1        | 0        | AN2                        |

| 0        | 0        | 0        | 1        | 1        | AN3                        |

| 0        | 0        | 1        | 0        | 0        | AN4                        |

| 0        | 0        | 1        | 0        | 1        | AN5                        |

| 0        | 0        | 1        | 1        | 0        | AN6                        |

| 0        | 0        | 1        | 1        | 1        | AN7                        |

| 0        | 1        | 0        | 0        | 0        | AN8                        |

| 0        | 1        | 0        | 0        | 1        | AN9                        |

| 0        | 1        | 0        | 1        | 0        | AN10                       |

| 0        | 1        | 0        | 1        | 1        | AN11                       |

| 0        | 1        | 1        | 0        | 0        | AN12                       |

| 0        | 1        | 1        | 0        | 1        | AN13                       |

| 0        | 1        | 1        | 1        | 0        | AN14                       |

| 0        | 1        | 1        | 1        | 1        | AN15                       |

| 1        | 0        | 0        | 0        | 0        | ETRIG0 <sup>1</sup>        |

| 1        | 0        | 0        | 0        | 1        | ETRIG1 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 0        | ETRIG2 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 1        | ETRIG3 <sup>1</sup>        |

| 1        | 0        | 1        | Х        | Х        | Reserved                   |

| 1        | 1        | Х        | Х        | х        | Reserved                   |

Table 16-5. External Trigger Channel Select Coding

<sup>1</sup> Only if ETRIG3-0 input option is available (see device specification), else ETRISEL is ignored, that means external trigger source is still on one of the AD channels selected by ETRIGCH3-0

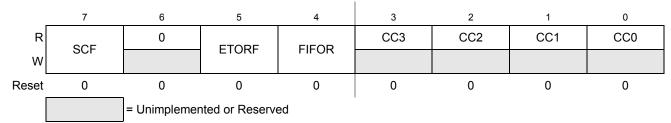

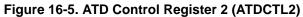

## 16.3.2.3 ATD Control Register 2 (ATDCTL2)

Writes to this register will abort current conversion sequence.

Module Base + 0x0002

Read: Anytime

Write: Anytime

## 18.3.2.17 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 18.3.3.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 18.4.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

Module Base + 0x0010 to Module Base + 0x0013

Access: User read/write<sup>1</sup>

Access: User read/write<sup>1</sup>

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 18-20. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0–CANIDAR3

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 18-22. CANIDAR0–CANIDAR3 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AC[7:0] | Acceptance Code Bits — AC[7:0] comprise a user-defined sequence of bits with which the corresponding bits of the related identifier register (IDRn) of the receive message buffer are compared. The result of this comparison is then masked with the corresponding identifier mask register. |

Module Base + 0x0018 to Module Base + 0x001B

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 18-21. MSCAN Identifier Acceptance Registers (Second Bank) — CANIDAR4–CANIDAR7

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Scalable Controller Area Network (S12MSCANV3)

In cases of more than one buffer having the same lowest priority, the message buffer with the lower index number wins.

Figure 18-36. Transmit Buffer Priority Register (TBPR)

<sup>1</sup> Read: Anytime when TXEx flag is set (see Section 18.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 18.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

Write: Anytime when TXEx flag is set (see Section 18.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 18.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

## 18.3.3.5 Time Stamp Register (TSRH–TSRL)

If the TIME bit is enabled, the MSCAN will write a time stamp to the respective registers in the active transmit or receive buffer right after the EOF of a valid message on the CAN bus (see Section 18.3.2.1, "MSCAN Control Register 0 (CANCTL0)"). In case of a transmission, the CPU can only read the time stamp after the respective transmit buffer has been flagged empty.

The timer value, which is used for stamping, is taken from a free running internal CAN bit clock. A timer overrun is not indicated by the MSCAN. The timer is reset (all bits set to 0) during initialization mode. The CPU can only read the time stamp registers.

| Module Base + 0x00XE     Access: User read/write |       |       |       |       |       |       |      |      |  |  |  |

|--------------------------------------------------|-------|-------|-------|-------|-------|-------|------|------|--|--|--|

| _                                                | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |  |  |  |

| R                                                | TSR15 | TSR14 | TSR13 | TSR12 | TSR11 | TSR10 | TSR9 | TSR8 |  |  |  |

| w                                                |       |       |       |       |       |       |      |      |  |  |  |

| Reset:                                           | х     | х     | х     | х     | х     | х     | х    | х    |  |  |  |

|                                                  |       |       |       |       |       |       |      |      |  |  |  |

Read: For transmit buffers: Anytime when TXEx flag is set (see Section 18.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 18.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). For receive buffers: Anytime when RXF is set. Write: Unimplemented

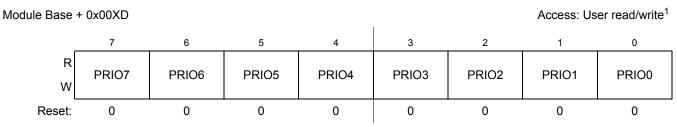

## 18.4.5.5 MSCAN Sleep Mode

The CPU can request the MSCAN to enter this low power mode by asserting the SLPRQ bit in the CANCTL0 register. The time when the MSCAN enters sleep mode depends on a fixed synchronization delay and its current activity:

- If there are one or more message buffers scheduled for transmission (TXEx = 0), the MSCAN will continue to transmit until all transmit message buffers are empty (TXEx = 1, transmitted successfully or aborted) and then goes into sleep mode.

- If the MSCAN is receiving, it continues to receive and goes into sleep mode as soon as the CAN bus next becomes idle.

- If the MSCAN is neither transmitting nor receiving, it immediately goes into sleep mode.

Figure 18-46. Sleep Request / Acknowledge Cycle

## NOTE

The application software must avoid setting up a transmission (by clearing one or more TXEx flag(s)) and immediately request sleep mode (by setting SLPRQ). Whether the MSCAN starts transmitting or goes into sleep mode directly depends on the exact sequence of operations.

If sleep mode is active, the SLPRQ and SLPAK bits are set (Figure 18-46). The application software must use SLPAK as a handshake indication for the request (SLPRQ) to go into sleep mode.

When in sleep mode (SLPRQ = 1 and SLPAK = 1), the MSCAN stops its internal clocks. However, clocks that allow register accesses from the CPU side continue to run.

If the MSCAN is in bus-off state, it stops counting the 128 occurrences of 11 consecutive recessive bits due to the stopped clocks. TXCAN remains in a recessive state. If RXF = 1, the message can be read and RXF can be cleared. Shifting a new message into the foreground buffer of the receiver FIFO (RxFG) does not take place while in sleep mode.

It is possible to access the transmit buffers and to clear the associated TXE flags. No message abort takes place while in sleep mode.

### Table 22-16. PTPSR Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTPS[7:0] | <b>Precision Timer Prescaler Select Bits</b> — These eight bits specify the division rate of the main Timer prescaler. These are effective only when the PRNT bit of TSCR1 is set to 1. Table 22-17 shows some selection examples in this case. The newly selected prescale factor will not take effect until the next synchronized edge where all prescale counter stages equal zero. |

The Prescaler can be calculated as follows depending on logical value of the PTPS[7:0] and PRNT bit:

PRNT = 1 : Prescaler = PTPS[7:0] + 1

| PTPS7 | PTPS6 | PTPS5 | PTPS4 | PTPS3 | PTPS2 | PTPS1 | PTPS0 | Prescale<br>Factor |

|-------|-------|-------|-------|-------|-------|-------|-------|--------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 2                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 3                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 4                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| 0     | 0     | 0     | 1     | 0     | 0     | 1     | 1     | 20                 |

| 0     | 0     | 0     | 1     | 0     | 1     | 0     | 0     | 21                 |

| 0     | 0     | 0     | 1     | 0     | 1     | 0     | 1     | 22                 |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 253                |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1     | 254                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 255                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 256                |

Table 22-17. Precision Timer Prescaler Selection Examples when PRNT = 1

# 22.4 Functional Description

This section provides a complete functional description of the timer TIM16B6CV3 block. Please refer to the detailed timer block diagram in Figure 22-22 as necessary.

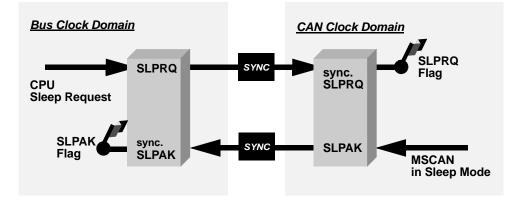

Figure 23-4. Channel 7 Output Compare/Pulse Accumulator Logic

# 23.2 External Signal Description

The TIM16B8CV3 module has a selected number of external pins. Refer to device specification for exact number.

## 23.2.1 IOC7 — Input Capture and Output Compare Channel 7

This pin serves as input capture or output compare for channel 7. This can also be configured as pulse accumulator input.

# 23.2.2 IOC6 - IOC0 — Input Capture and Output Compare Channel 6-0

Those pins serve as input capture or output compare for TIM16B8CV3 channel.

NOTE

For the description of interrupts see Section 23.6, "Interrupts".

# 23.3 Memory Map and Register Definition

This section provides a detailed description of all memory and registers.

## 23.3.1 Module Memory Map

The memory map for the TIM16B8CV3 module is given below in Figure 23-5. The address listed for each register is the address offset. The total address for each register is the sum of the base address for the TIM16B8CV3 module and the address offset for each register.

### Table 23-4. OC7M Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OC7M[7:0] | <ul> <li>Output Compare 7 Mask — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. For each OC7M bit that is set, the output compare action reflects the corresponding OC7D bit.</li> <li>0 The corresponding OC7Dx bit in the output compare 7 data register will not be transferred to the timer port on a channel 7 event, even if the corresponding pin is setup for output compare.</li> <li>1 The corresponding OC7Dx bit in the output compare 7 data register will be transferred to the timer port on a channel 7 event.</li> <li>Note: The corresponding channel must also be setup for output compare (IOSx = 1 and OCPDx = 0) for data to be transferred from the output compare 7 data register to the timer port.</li> </ul> |

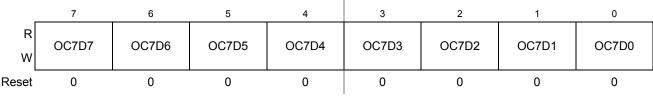

## 23.3.2.4 Output Compare 7 Data Register (OC7D)

1.

Module Base + 0x0003

Figure 23-9. Output Compare 7 Data Register (OC7D)

Read: Anytime

Write: Anytime

### Table 23-5. OC7D Field Descriptions

| Field | Description                                                                                                                                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Output Compare 7 Data</b> — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a                                                                                |

|       | successful output compare on channel 7, can cause bits in the output compare 7 data register to transfer to the timer port data register depending on the output compare 7 mask register. |

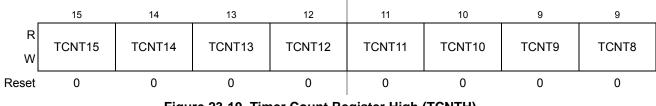

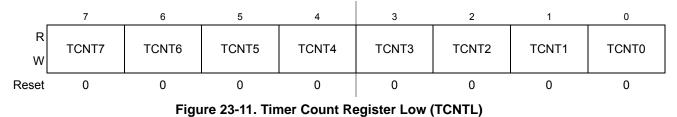

## 23.3.2.5 Timer Count Register (TCNT)

Module Base + 0x0004

Figure 23-10. Timer Count Register High (TCNTH)

#### Timer Module (TIM16B8CV3)

Module Base + 0x0005

The 16-bit main timer is an up counter.

A full access for the counter register should take place in one clock cycle. A separate read/write for high byte and low byte will give a different result than accessing them as a word.

#### Read: Anytime

Write: Has no meaning or effect in the normal mode; only writable in special modes (test\_mode = 1).

The period of the first count after a write to the TCNT registers may be a different size because the write is not synchronized with the prescaler clock.

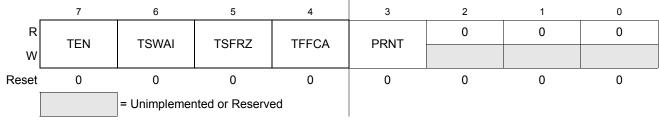

### 23.3.2.6 Timer System Control Register 1 (TSCR1)

Module Base + 0x0006

Figure 23-12. Timer System Control Register 1 (TSCR1)

Read: Anytime

Write: Anytime

### Table 23-6. TSCR1 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TEN   | <ul> <li>Timer Enable</li> <li>Disables the main timer, including the counter. Can be used for reducing power consumption.</li> <li>Allows the timer to function normally.</li> <li>If for any reason the timer is not active, there is no ÷64 clock for the pulse accumulator because the ÷64 is generated by the timer prescaler.</li> </ul> |

| 6<br>TSWAI | <ul> <li>Timer Module Stops While in Wait</li> <li>Allows the timer module to continue running during wait.</li> <li>Disables the timer module when the MCU is in the wait mode. Timer interrupts cannot be used to get the MCU out of wait.</li> <li>TSWAI also affects pulse accumulator.</li> </ul>                                         |

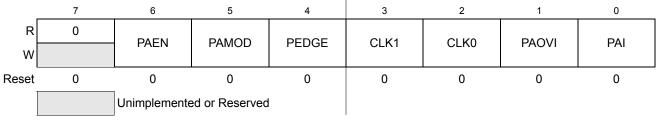

## 23.3.2.15 16-Bit Pulse Accumulator Control Register (PACTL)

Module Base + 0x0020

Read: Any time

Write: Any time

When PAEN is set, the Pulse Accumulator counter is enabled. The Pulse Accumulator counter shares the input pin with IOC7.

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>PAEN       | <ul> <li>Pulse Accumulator System Enable — PAEN is independent from TEN. With timer disabled, the pulse accumulator can function unless pulse accumulator is disabled.</li> <li>0 16-Bit Pulse Accumulator system disabled.</li> <li>1 Pulse Accumulator system enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>PAMOD      | <ul> <li>Pulse Accumulator Mode — This bit is active only when the Pulse Accumulator is enabled (PAEN = 1). See Table 23-19.</li> <li>0 Event counter mode.</li> <li>1 Gated time accumulation mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4<br>PEDGE      | <ul> <li>Pulse Accumulator Edge Control — This bit is active only when the Pulse Accumulator is enabled (PAEN = 1). For PAMOD bit = 0 (event counter mode). See Table 23-19.</li> <li>0 Falling edges on IOC7 pin cause the count to be increased.</li> <li>1 Rising edges on IOC7 pin cause the count to be increased.</li> <li>For PAMOD bit = 1 (gated time accumulation mode).</li> <li>0 IOC7 input pin high enables M (Bus clock) divided by 64 clock to Pulse Accumulator and the trailing falling edge on IOC7 sets the PAIF flag.</li> <li>1 IOC7 input pin low enables M (Bus clock) divided by 64 clock to Pulse Accumulator and the trailing rising edge on IOC7 sets the PAIF flag.</li> </ul> |

| 3:2<br>CLK[1:0] | Clock Select Bits — Refer to Table 23-20.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1<br>PAOVI      | Pulse Accumulator Overflow Interrupt Enable<br>0 Interrupt inhibited.<br>1 Interrupt requested if PAOVF is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0<br>PAI        | <ul> <li>Pulse Accumulator Input Interrupt Enable</li> <li>0 Interrupt inhibited.</li> <li>1 Interrupt requested if PAIF is set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### Table 23-18. PACTL Field Descriptions

# 24.3 Memory Map and Registers

This section describes the memory map and registers for the Flash module. Read data from unimplemented memory space in the Flash module is undefined. Write access to unimplemented or reserved memory space in the Flash module will be ignored by the Flash module.

### CAUTION

Writing to the Flash registers while a Flash command is executing (that is indicated when the value of flag CCIF reads as '0') is not allowed. If such action is attempted the write operation will not change the register value.

Writing to the Flash registers is allowed when the Flash is not busy executing commands (CCIF = 1) and during initialization right after reset, despite the value of flag CCIF in that case (refer to Section 24.6 for a complete description of the reset sequence).

| Global Address (in Bytes) | Size<br>(Bytes) | Description                                                  |  |

|---------------------------|-----------------|--------------------------------------------------------------|--|

| 0x0_0000 - 0x0_03FF       | 1,024           | Register Space                                               |  |

| 0x0_0400 - 0x0_05FF       | 512             | EEPROM Memory                                                |  |

| 0x0_0600 - 0x0_07FF       | 512             | FTMRG reserved area                                          |  |

| 0x0_4000 – 0x0_7FFF       | 16,284          | NVMRES <sup>1</sup> =1 : NVM Resource area (see Figure 24-3) |  |

| 0x3_8000 – 0x3_BFFF       | 16,384          | FTMRG reserved area                                          |  |

| 0x3_C000 - 0x3_FFFF       | 16,384          | P-Flash Memory                                               |  |

#### Table 24-2. FTMRG Memory Map

<sup>1</sup> See NVMRES description in Section 24.4.3

## 24.3.1 Module Memory Map

The S12 architecture places the P-Flash memory between global addresses 0x3\_C000 and 0x3\_FFFF as shown in Table 24-3. The P-Flash memory map is shown in Figure 24-2.

| Global Address      | Size<br>(Bytes) | Description                                                             |

|---------------------|-----------------|-------------------------------------------------------------------------|

| 0x3_C000 – 0x3_FFFF | 16 K            | P-Flash Block<br>Contains Flash Configuration Field<br>(see Table 24-4) |

#### 32 KByte Flash Module (S12FTMRG32K1V1)

During the reset sequence, fields DPOPEN and DPS of the EEPROT register are loaded with the contents of the EEPROM protection byte in the Flash configuration field at global address 0x3\_FF0D located in P-Flash memory (see Table 25-4) as indicated by reset condition F in Table 25-23. To change the EEPROM protection that will be loaded during the reset sequence, the P-Flash sector containing the EEPROM protection byte must be unprotected, then the EEPROM protection byte must be programmed. If a double bit fault is detected while reading the P-Flash phrase containing the EEPROM protection byte must be to leave the EEPROM protection byte must be programmed. If a double bit fault is detected while reading the P-Flash phrase containing the EEPROM protection byte must be memory fully protected.

Trying to alter data in any protected area in the EEPROM memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. Block erase of the EEPROM memory is not possible if any of the EEPROM sectors are protected.

| Table 25-22. EEPROT | Field Descriptions |

|---------------------|--------------------|

|---------------------|--------------------|

| Field       | Description                                                                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DPOPEN | <ul> <li>EEPROM Protection Control</li> <li>Enables EEPROM memory protection from program and erase with protected address range defined by DPS bits</li> <li>Disables EEPROM memory protection from program and erase</li> </ul> |

|             | <b>EEPROM Protection Size</b> — The DPS[4:0] bits determine the size of the protected area in the EEPROM memory as shown inTable 25-23.                                                                                           |

| DPS[4:0]                                                                                         | Global Address Range | Protected Size |  |  |

|--------------------------------------------------------------------------------------------------|----------------------|----------------|--|--|

| 00000                                                                                            | 0x0_0400 - 0x0_041F  | 32 bytes       |  |  |

| 00001                                                                                            | 0x0_0400 - 0x0_043F  | 64 bytes       |  |  |

| 00010                                                                                            | 0x0_0400 - 0x0_045F  | 96 bytes       |  |  |

| 00011                                                                                            | 0x0_0400 - 0x0_047F  | 128 bytes      |  |  |

| 00100                                                                                            | 0x0_0400 - 0x0_049F  | 160 bytes      |  |  |

| 00101                                                                                            | 0x0_0400 – 0x0_04BF  | 192 bytes      |  |  |

| The Protection Size goes on enlarging in step of 32 bytes, for each DPS value increasing of one. |                      |                |  |  |

| 11111 - to - 11111                                                                               | 0x0_0400 – 0x0_07FF  | 1,024 bytes    |  |  |

#### Table 25-23. EEPROM Protection Address Range

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                          |

|          | ACCERR    | Set if CCOBIX[2:0] > 101 at command launch                                          |

|          |           | Set if command not available in current mode (see Table 28-27)                      |

|          | ACCERK    | Set if an invalid global address [17:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          |           | Set if the requested group of words breaches the end of the EEPROM block            |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 28-63. Program EEPROM Command Error Handling

### 28.4.6.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

| CCOBIX[2:0] | FCCOB Parameters                                                                                               |                                                    |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| 000         | 0x12                                                                                                           | Global address [17:16] to identify<br>EEPROM block |  |  |  |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 28.1.2.2 for EEPROM sector size. |                                                    |  |  |  |  |  |

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 28-27)                      |  |  |  |  |  |

|          | ACCERK    | Set if an invalid global address [17:0] is suppliedsee Table 28-3)                  |  |  |  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |  |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |  |  |

Table 28-65. Erase EEPROM Sector Command Error Handling

| CCOBIX[2:0] | FCCOB Parameters                                                                                               |                                                    |  |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|

| 000         | 0x12                                                                                                           | Global address [17:16] to identify<br>EEPROM block |  |  |  |  |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 30.1.2.2 for EEPROM sector size. |                                                    |  |  |  |  |  |  |

Table 30-64. Erase EEPROM Sector Command FCCOB Requirements

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |  |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 30-27)                      |  |  |  |  |  |  |

|          | ACCERK    | Set if an invalid global address [17:0] is suppliedsee Table 30-3)                  |  |  |  |  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |  |  |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |  |  |  |

Table 30-65. Erase EEPROM Sector Command Error Handling

## 30.4.7 Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Table | 30-66. | Flash | Interrupt | Sources |

|-------|--------|-------|-----------|---------|

|-------|--------|-------|-----------|---------|

| Interrupt Source                   | Interrupt Flag              | Local Enable                | Global (CCR)<br>Mask |

|------------------------------------|-----------------------------|-----------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | l Bit                |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register) | DFDIE<br>(FERCNFG register) | l Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | l Bit                |

### 0x0180–0x023F Reserved

| Address | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0180- | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x023F  |          | W |       |       |       |       |       |       |       |       |

## 0x0240–0x025F Port Integration Module (PIM) Map 4 of 6

| Address | Name        |        | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|---------|-------------|--------|--------|--------|---------|---------|---------|---------|--------|--------|

| 0x0240  | PTT         | R<br>W | PTT7   | PTT6   | PTT5    | PTT4    | PTT3    | PTT2    | PTT1   | PTT0   |

| 0x0241  | PTIT        | R      | PTIT7  | PTIT6  | PTIT5   | PTIT4   | PTIT3   | PTIT2   | PTIT1  | PTIT0  |

|         |             | W      |        |        |         |         |         |         |        |        |

| 0x0242  | DDRT        | R<br>W | DDRT7  | DDRT6  | DDRT5   | DDRT4   | DDRT3   | DDRT2   | DDRT1  | DDRT0  |

| 0x0243  | Reserved    | R      | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |

| 070240  | Reserved    | W      |        |        |         |         |         |         |        |        |

| 0x0244  | PERT        | R<br>W | PERT7  | PERT6  | PERT5   | PERT4   | PERT3   | PERT2   | PERT1  | PERT0  |

| 0x0245  | PPST        | R<br>W | PPST7  | PPST6  | PPST5   | PPST4   | PPST3   | PPST2   | PPST1  | PPST0  |

| 0x0246- | Deserved    | R      | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |

| 0x0247  | Reserved    | W      |        |        |         |         |         |         |        |        |

| 0x0248  | PTS         | R<br>W | PTS7   | PTS6   | PTS5    | PTS4    | PTS3    | PTS2    | PTS1   | PTS0   |

| 0.0040  | DTIO        | R      | PTIS7  | PTIS6  | PTIS5   | PTIS4   | PTIS3   | PTIS2   | PTIS1  | PTIS0  |

| 0x0249  | PTIS        | W      |        |        |         |         |         |         |        |        |

| 0x024A  | DDRS        | R<br>W | DDRS7  | DDRS6  | DDRS5   | DDRS4   | DDRS3   | DDRS2   | DDRS1  | DDRS0  |

| 0,0040  | Reserved    | R      | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |

| 0x024B  |             | W      |        |        |         |         |         |         |        |        |

| 0x024C  | PERS        | R<br>W | PERS7  | PERS6  | PERS5   | PERS4   | PERS3   | PERS2   | PERS1  | PERS0  |

| 0x024D  | PPSS        | R<br>W | PPSS7  | PPSS6  | PPSS5   | PPSS4   | PPSS3   | PPSS2   | PPSS1  | PPSS0  |

| 0x024E  | WOMS        | R<br>W | WOMS7  | WOMS6  | WOMS5   | WOMS4   | WOMS3   | WOMS2   | WOMS1  | WOMS0  |

| 0x024F  | PRR0        | R<br>W | PRR0P3 | PRR0P2 | PRR0T31 | PRR0T30 | PRR0T21 | PRR0T20 | PRR0S1 | PRR0S0 |

| 0,0050  |             | R      | 0      | 0      | 0       | 0       |         |         |        | DTMO   |

| 0x0250  | PTM         | W      |        |        |         |         | PTM3    | PTM2    | PTM1   | PTM0   |

| 0x0251  | PTIM        | R      | 0      | 0      | 0       | 0       | PTIM3   | PTIM2   | PTIM1  | PTIM0  |

| 070201  | 1 1 1 1 1 1 | W      |        |        |         |         |         |         |        |        |

| 0x0252  | DDRM        | R<br>W | 0      | 0      | 0       | 0       | DDRM3   | DDRM2   | DDRM1  | DDRM0  |

| 0,0050  | Descrived   | R      | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |

| 0x0253  | Reserved    | W      |        |        |         |         |         |         |        |        |