Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | 12V1                                                         |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 25MHz                                                        |

| Connectivity               | IrDA, LINbus, SCI, SPI                                       |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 40                                                           |

| Program Memory Size        | 16KB (16K × 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 512 x 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                 |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 48-LQFP                                                      |

| Supplier Device Package    | 48-LQFP (7x7)                                                |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s12gn16f0mlfr |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | <b>Function</b><br><lowestpriorityhighest></lowestpriorityhighest> |                |              |             | Power       | Internal Pull<br>Resistor |               |                |

|-------------|--------------------------------------------------------------------|----------------|--------------|-------------|-------------|---------------------------|---------------|----------------|

| Package Pin | Pin                                                                | 2nd<br>Func.   | 3rd<br>Func. | 4th<br>Func | 5th<br>Func | Supply                    | CTRL          | Reset<br>State |

| 30          | PAD10                                                              | KWAD10         | ACMPP        |             |             | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 31          | PAD3                                                               | KWAD3          | AN3          | _           | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 32          | PAD11                                                              | KWAD11         | ACMPM        |             |             | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 33          | PAD4                                                               | KWAD4          | AN4          |             | —           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 34          | PAD5                                                               | KWAD5          | AN5          | _           | _           | V <sub>DDA</sub>          | PER1AD/PPS0AD | Disabled       |

| 35          | PAD6                                                               | KWAD6          | AN6          | _           | _           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 36          | PAD7                                                               | KWAD7          | AN7          |             | —           | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 37          | VDDA                                                               | VRH            | —            |             | —           | _                         | —             | _              |

| 38          | VSSA                                                               | _              | _            |             | —           | _                         | —             |                |

| 39          | PS0                                                                | RXD0           | _            |             | —           | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 40          | PS1                                                                | TXD0           | —            |             | —           | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 41          | PS2                                                                | _              | _            |             | —           | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 42          | PS3                                                                | _              | _            | _           | _           | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 43          | PS4                                                                | MISO0          |              | _           | │ _         | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 44          | PS5                                                                | MOSI0          |              | _           | —           | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 45          | PS6                                                                | SCK0           |              | _           | │ _         | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 46          | PS7                                                                | API_EXTC<br>LK | ECLK         | SS0         | _           | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 47          | PM0                                                                | —              | —            | _           | _           | V <sub>DDX</sub>          | PERM/PPSM     | Disabled       |

| 48          | PM1                                                                | _              | _            | —           | — —         | V <sub>DDX</sub>          | PERM/PPSM     | Disabled       |

Table 1-11. 48-Pin LQFP/QFN Pinout for S12GNA16 and S12GNA32

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

### 1.8.3 S12GN48

### 1.8.3.1 Pinout 32-Pin LQFP

|             | <     | Fund<br>owestPRIO |              | Power        | Internal Pull<br>Resistor |            |                |

|-------------|-------|-------------------|--------------|--------------|---------------------------|------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.      | 3rd<br>Func. | 4th<br>Func. | Supply                    | CTRL       | Reset<br>State |

| 86          | PS4   | MISO0             | _            | _            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 87          | PS5   | MOSI0             | _            | —            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 88          | PS6   | SCK0              | _            | —            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 89          | PS7   | API_EXTC<br>LK    | SS0          | _            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 90          | VSSX2 | _                 | _            | _            | —                         |            | —              |

| 91          | VDDX2 | _                 | _            | _            | —                         |            | —              |

| 92          | PM0   | RXCAN             | _            | —            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 93          | PM1   | TXCAN             | _            | _            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 94          | PD4   | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 95          | PD5   | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 96          | PD6   | —                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 97          | PD7   | —                 | —            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 98          | PM2   | RXD2              | —            | —            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 99          | PM3   | TXD2              | _            | —            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 100         | PJ7   | KWJ7              | SS2          | _            | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

Table 1-22.

100-Pin LQFP Pinout for S12G96 and S12G128

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

| Field       | Description                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PTIT | <b>Port T input data</b> —<br>A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

#### Table 2-36. PTIT Register Field Descriptions

### 2.4.3.17 Port T Data Direction Register (DDRT)

#### Address 0x0242 (G1, G2) Access: User read/write<sup>1</sup> 7 6 5 4 3 2 1 0 R DDRT7 DDRT6 DDRT5 DDRT4 DDRT2 DDRT3 DDRT1 DDRT0 W 0 0 0 0 0 0 0 0 Reset Address 0x0242 (G3) Access: User read/write<sup>1</sup> 7 6 5 4 3 2 1 0 R 0 0 DDRT5 DDRT4 DDRT3 DDRT2 DDRT1 DDRT0 W 0 0 0 0 0 0 0 0 Reset Figure 2-18. Port T Data Direction Register (DDRT)

<sup>1</sup> Read: Anytime

Write: Anytime

#### Table 2-37. DDRT Register Field Descriptions

| Field       | Description                                                                                                 |  |

|-------------|-------------------------------------------------------------------------------------------------------------|--|

| 7-0<br>DDRT | <b>Port T data direction</b> —<br>This bit determines whether the pin is a general-purpose input or output. |  |

|             | 1 Associated pin configured as output<br>0 Associated pin configured as input                               |  |

#### Read: Anytime

Write: Never

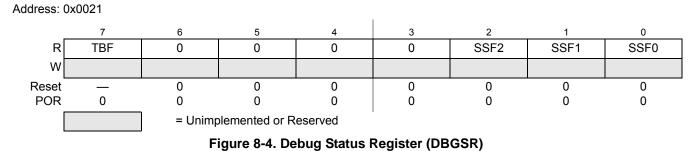

#### Table 8-5. DBGSR Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TBF        | <b>Trace Buffer Full</b> — The TBF bit indicates that the trace buffer has stored 64 or more lines of data since it was last armed. If this bit is set, then all 64 lines will be valid data, regardless of the value of DBGCNT bits. The TBF bit is cleared when ARM in DBGC1 is written to a one. The TBF is cleared by the power on reset initialization. Other system generated resets have no affect on this bit This bit is also visible at DBGCNT[7]                                                                                                                                                                                                            |

| 2–0<br>SSF[2:0] | <b>State Sequencer Flag Bits</b> — The SSF bits indicate in which state the State Sequencer is currently in. During a debug session on each transition to a new state these bits are updated. If the debug session is ended by software clearing the ARM bit, then these bits retain their value to reflect the last state of the state sequencer before disarming. If a debug session is ended by an internal event, then the state sequencer returns to state0 and these bits are cleared to indicate that state0 was entered during the session. On arming the module the state sequencer enters state1 and these bits are forced to SSF[2:0] = 001. See Table 8-6. |

#### Table 8-6. SSF[2:0] — State Sequence Flag Bit Encoding

| SSF[2:0]    | Current State     |

|-------------|-------------------|

| 000         | State0 (disarmed) |

| 001         | State1            |

| 010         | State2            |

| 011         | State3            |

| 100         | Final State       |

| 101,110,111 | Reserved          |

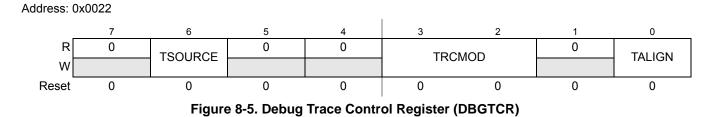

### 8.3.2.3 Debug Trace Control Register (DBGTCR)

MC9S12G Family Reference Manual Rev.1.27

Security (S12XS9SECV2)

Table 11-7 for details.

Field 6 AFFC

5

Reserved 4

ETRIGLE

3

ETRIGP

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>ATD Fast Flag Clear All</li> <li>ATD flag clearing done by write 1 to respective CCF[<i>n</i>] flag.</li> <li>Changes all ATD conversion complete flags to a fast clear sequence.<br/>For compare disabled (CMPE[<i>n</i>]=0) a read access to the result register will cause the associated CCF[<i>n</i>] flag to clear automatically.<br/>For compare enabled (CMPE[<i>n</i>]=1) a write access to the result register will cause the associated CCF[<i>n</i>] flag to clear automatically.</li> </ul> |

| Do not alter this bit from its reset value. It is for Manufacturer use only and can change the ATD behavior.                                                                                                                                                                                                                                                                                                                                                                                                      |

External Trigger Level/Edge Control — This bit controls the sensitivity of the external trigger signal. See

External Trigger Polarity — This bit controls the polarity of the external trigger signal. See Table 11-7 for details.

#### Table 11-6. ATDCTL2 Field Descriptions

| 2<br>ETRIGE | <ul> <li>External Trigger Mode Enable — This bit enables the external trigger on one of the AD channels or one of the ETRIG3-0 inputs as described in Table 11-5. If the external trigger source is one of the AD channels, the digital input buffer of this channel is enabled. The external trigger allows to synchronize the start of conversion with external events.</li> <li>0 Disable external trigger</li> <li>1 Enable external trigger</li> </ul>                                                                                                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ASCIE  | <ul> <li>ATD Sequence Complete Interrupt Enable</li> <li>0 ATD Sequence Complete interrupt requests are disabled.</li> <li>1 ATD Sequence Complete interrupt will be requested whenever SCF=1 is set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                   |

| 0<br>ACMPIE | <ul> <li>ATD Compare Interrupt Enable — If automatic compare is enabled for conversion <i>n</i> (CMPE[<i>n</i>]=1 in ATDCMPE register) this bit enables the compare interrupt. If the CCF[<i>n</i>] flag is set (showing a successful compare for conversion <i>n</i>), the compare interrupt is triggered.</li> <li>0 ATD Compare interrupt requests are disabled.</li> <li>1 For the conversions in a sequence for which automatic compare is enabled (CMPE[<i>n</i>]=1), an ATD Compare Interrupt will be requested whenever any of the respective CCF flags is set.</li> </ul> |

#### Table 11-7. External Trigger Configurations

| ETRIGLE | ETRIGP | External Trigger Sensitivity |

|---------|--------|------------------------------|

| 0       | 0      | Falling edge                 |

| 0       | 1      | Rising edge                  |

| 1       | 0      | Low level                    |

| 1       | 1      | High level                   |

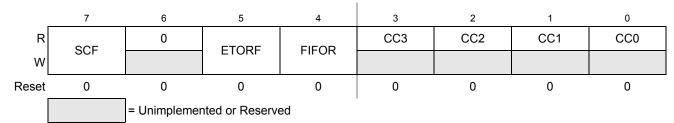

# 16.3.2.7 ATD Status Register 0 (ATDSTAT0)

This register contains the Sequence Complete Flag, overrun flags for external trigger and FIFO mode, and the conversion counter.

Module Base + 0x0006

Figure 16-9. ATD Status Register 0 (ATDSTAT0)

Read: Anytime

Write: Anytime (No effect on (CC3, CC2, CC1, CC0))

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SCF   | Sequence Complete Flag — This flag is set upon completion of a conversion sequence. If conversion sequences are continuously performed (SCAN=1), the flag is set after each one is completed. This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to SCF</li> <li>B) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>C) If AFFC=1 and a result register is read</li> <li>Conversion sequence not completed</li> <li>Conversion sequence has completed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5<br>ETORF | <ul> <li>External Trigger Overrun Flag — While in edge sensitive mode (ETRIGLE=0), if additional active edges are detected while a conversion sequence is in process the overrun flag is set. This flag is cleared when one of the following occurs:         <ul> <li>A) Write "1" to ETORF</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> </li> <li>No External trigger overrun error has occurred</li> <li>1 External trigger overrun error has occurred</li> </ul>                                                                                                                                                                                                                                                                                                                  |

| 4<br>FIFOR | Result Register Overrun Flag — This bit indicates that a result register has been written to before its associated conversion complete flag (CCF) has been cleared. This flag is most useful when using the FIFO mode because the flag potentially indicates that result registers are out of sync with the input channels. However, it is also practical for non-FIFO modes, and indicates that a result register has been overwritten before it has been read (i.e. the old data has been lost). This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to FIFOR</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>No overrun has occurred</li> <li>Overrun condition exists (result register has been written while associated CCFx flag was still set)</li> </ul> |

#### 20.5.3.1.8 BKDIF Description

The BKDIF interrupt is set when a break signal was received. Clear BKDIF by writing a "1" to the SCIASR1 SCI alternative status register 1. This flag is also cleared if break detect feature is disabled.

### 20.5.4 Recovery from Wait Mode

The SCI interrupt request can be used to bring the CPU out of wait mode.

### 20.5.5 Recovery from Stop Mode

An active edge on the receive input can be used to bring the CPU out of stop mode.

#### 32 KByte Flash Module (S12FTMRG32K1V1)

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |  |  |  |

|-------------|------|-------------------------------------------|--|--|--|

| 010         | HI   | Data 0 [15:8]                             |  |  |  |

| 010         | LO   | Data 0 [7:0]                              |  |  |  |

| 011         | HI   | Data 1 [15:8]                             |  |  |  |

|             | LO   | Data 1 [7:0]                              |  |  |  |

| 100         | HI   | Data 2 [15:8]                             |  |  |  |

| 100         | LO   | Data 2 [7:0]                              |  |  |  |

| 101         | HI   | Data 3 [15:8]                             |  |  |  |

| 101         | LO   | Data 3 [7:0]                              |  |  |  |

Table 25-24. FCCOB - NVM Command Mode (Typical Usage)

#### 25.3.2.12 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000C

Offset Module Base + 0x000D

Figure 25-18. Flash Reserved1 Register (FRSV1)

All bits in the FRSV1 register read 0 and are not writable.

### 25.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

Figure 25-19. Flash Reserved2 Register (FRSV2)

All bits in the FRSV2 register read 0 and are not writable.

#### 25.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

#### 26.4.4.2.1 Define FCCOB Contents

The FCCOB parameter fields must be loaded with all required parameters for the Flash command being executed. Access to the FCCOB parameter fields is controlled via the CCOBIX bits in the FCCOBIX register (see Section 26.3.2.3).

The contents of the FCCOB parameter fields are transferred to the Memory Controller when the user clears the CCIF command completion flag in the FSTAT register (writing 1 clears the CCIF to 0). The CCIF flag will remain clear until the Flash command has completed. Upon completion, the Memory Controller will return CCIF to 1 and the FCCOB register will be used to communicate any results. The flow for a generic command write sequence is shown in Figure 26-26.

# 26.4.6 Flash Command Description

This section provides details of all available Flash commands launched by a command write sequence. The ACCERR bit in the FSTAT register will be set during the command write sequence if any of the following illegal steps are performed, causing the command not to be processed by the Memory Controller:

- Starting any command write sequence that programs or erases Flash memory before initializing the FCLKDIV register

- Writing an invalid command as part of the command write sequence

- For additional possible errors, refer to the error handling table provided for each command

If a Flash block is read during execution of an algorithm (CCIF = 0) on that same block, the read operation will return invalid data if both flags SFDIF and DFDIF are set. If the SFDIF or DFDIF flags were not previously set when the invalid read operation occurred, both the SFDIF and DFDIF flags will be set.

If the ACCERR or FPVIOL bits are set in the FSTAT register, the user must clear these bits before starting any command write sequence (see Section 26.3.2.7).

#### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

### 26.4.6.1 Erase Verify All Blocks Command

The Erase Verify All Blocks command will verify that all P-Flash and EEPROM blocks have been erased.

Table 26-31. Erase Verify All Blocks Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |

|-------------|------------------|--------------|--|

| 000         | 0x01             | Not required |  |

Upon clearing CCIF to launch the Erase Verify All Blocks command, the Memory Controller will verify that the entire Flash memory space is erased. The CCIF flag will set after the Erase Verify All Blocks operation has completed. If all blocks are not erased, it means blank check failed, both MGSTAT bits will be set.

Table 26-32. Erase Verify All Blocks Command Error Handling

| Register | Error Bit | Error Condition                                                                                   |  |  |

|----------|-----------|---------------------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                       |  |  |

|          | FPVIOL    | None                                                                                              |  |  |

| FSTAT    | MGSTAT1   | Set if any errors have been encountered during the reador if blank check failed .                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |  |  |

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                         |  |  |

|          |           | Set if command not available in current mode (see Table 26-27)                      |  |  |

|          |           | Set if an invalid phrase index is supplied                                          |  |  |

| FSTAT    |           | Set if the requested phrase has already been programmed <sup>1</sup>                |  |  |

|          | FPVIOL    | None                                                                                |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

Table 26-43. Program Once Command Error Handling

#### 26.4.6.7 Erase All Blocks Command

The Erase All Blocks operation will erase the entire P-Flash and EEPROM memory space.

#### Table 26-44. Erase All Blocks Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters  |  |  |

|-------------|-------------------|--|--|

| 000         | 0x08 Not required |  |  |

Upon clearing CCIF to launch the Erase All Blocks command, the Memory Controller will erase the entire Flash memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag will set after the Erase All Blocks operation has completed.

|          |                                                                     | · · · · · · · · · · · · · · · · · · ·                          |

|----------|---------------------------------------------------------------------|----------------------------------------------------------------|

| Register | Error Bit                                                           | Error Condition                                                |

|          | ACCERR                                                              | Set if CCOBIX[2:0] != 000 at command launch                    |

|          | ACCERR                                                              | Set if command not available in current mode (see Table 26-27) |

| FSTAT    | FPVIOL                                                              | Set if any area of the P-Flash or EEPROM memory is protected   |

| -        | Set if any errors have been encountered during the verify operation |                                                                |

|          |                                                                     |                                                                |

Set if any non-correctable errors have been encountered during the verify

Table 26-45. Erase All Blocks Command Error Handling

#### 26.4.6.8 Erase Flash Block Command

**MGSTATO**

The Erase Flash Block operation will erase all addresses in a P-Flash or EEPROM block.

operation

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIF          | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command completion or command violation.</li> <li>0 Flash command in progress</li> <li>1 Flash command has completed</li> </ul>                                                                                                                                                                           |

| 5<br>ACCERR        | Flash Access Error Flag — The ACCERR bit indicates an illegal access has occurred to the Flash memory caused by either a violation of the command write sequence (see Section 27.4.4.2) or issuing an illegal Flash command. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR.<br>0 No access error detected<br>1 Access error detected                                        |

| 4<br>FPVIOL        | <ul> <li>Flash Protection Violation Flag — The FPVIOL bit indicates an attempt was made to program or erase an address in a protected area of P-Flash or EEPROM memory during a command write sequence. The FPVIOL bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL is set, it is not possible to launch a command or start a command write sequence.</li> <li>0 No protection violation detected</li> <li>1 Protection violation detected</li> </ul> |

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                                                                                                                                                                                                                                              |

| 2<br>RSVD          | Reserved Bit — This bit is reserved and always reads 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 27.4.6, "Flash Command Description," and Section 27.6, "Initialization" for details.                                                                                                                                                                                                                   |

#### Table 27-15. FSTAT Field Descriptions

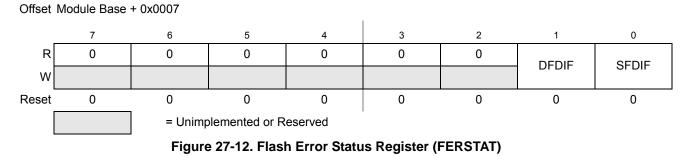

### 27.3.2.8 Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

All flags in the FERSTAT register are readable and only writable to clear the flag.

# 27.4.8 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 27.4.7, "Interrupts").

# 27.4.9 Stop Mode

If a Flash command is active (CCIF = 0) when the MCU requests stop mode, the current Flash operation will be completed before the MCU is allowed to enter stop mode.

# 27.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 27-11). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x3\_FF0F. The security state out of reset can be permanently changed by programming the security byte assuming that the MCU is starting from a mode where the necessary P-Flash erase and program commands are available and that the upper region of the P-Flash is unprotected. If the Flash security byte is successfully programmed, its new value will take affect after the next MCU reset.

The following subsections describe these security-related subjects:

- Unsecuring the MCU using Backdoor Key Access

- Unsecuring the MCU in Special Single Chip Mode using BDM

- Mode and Security Effects on Flash Command Availability

# 27.5.1 Unsecuring the MCU using Backdoor Key Access

The MCU may be unsecured by using the backdoor key access feature which requires knowledge of the contents of the backdoor keys (four 16-bit words programmed at addresses 0x3\_FF00-0x3\_FF07). If the KEYEN[1:0] bits are in the enabled state (see Section 27.3.2.2), the Verify Backdoor Access Key command (see Section 27.4.6.11) allows the user to present four prospective keys for comparison to the keys stored in the Flash memory via the Memory Controller. If the keys presented in the Verify Backdoor Access Key register (see Table 27-11) will be changed to unsecure the MCU. Key values of 0x0000 and 0xFFFF are not permitted as backdoor keys. While the Verify Backdoor Access Key command is active, P-Flash memory and EEPROM memory will not be available for read access and will return invalid data.

- Single bit fault correction and double bit fault detection within a 32-bit double word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and phrase program operation

- Ability to read the P-Flash memory while programming a word in the EEPROM memory

- Flexible protection scheme to prevent accidental program or erase of P-Flash memory

### 28.1.2.2 EEPROM Features

- 3 Kbytes of EEPROM memory composed of one 3 Kbyte Flash block divided into 768 sectors of 4 bytes

- Single bit fault correction and double bit fault detection within a word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and word program operation

- Protection scheme to prevent accidental program or erase of EEPROM memory

- Ability to program up to four words in a burst sequence

### 28.1.2.3 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

### 28.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 28-1.

| CCOBIX[2:0] | FCCOB Parameters                                                                                               |                                                    |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| 000         | 0x12                                                                                                           | Global address [17:16] to identify<br>EEPROM block |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 30.1.2.2 for EEPROM sector size. |                                                    |  |  |

Table 30-64. Erase EEPROM Sector Command FCCOB Requirements

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 30-27)                      |  |  |  |

|          | AUUERR    | Set if an invalid global address [17:0] is suppliedsee Table 30-3)                  |  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |

Table 30-65. Erase EEPROM Sector Command Error Handling

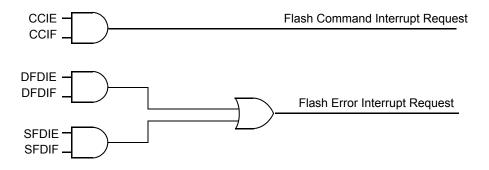

### 30.4.7 Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Table | 30-66. | Flash | Interrupt | Sources |

|-------|--------|-------|-----------|---------|

|-------|--------|-------|-----------|---------|

| Interrupt Source                   | Interrupt Flag              | Local Enable                | Global (CCR)<br>Mask |

|------------------------------------|-----------------------------|-----------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | l Bit                |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register) | DFDIE<br>(FERCNFG register) | l Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | l Bit                |

#### NOTE

Vector addresses and their relative interrupt priority are determined at the MCU level.

#### 30.4.7.1 Description of Flash Interrupt Operation

The Flash module uses the CCIF flag in combination with the CCIE interrupt enable bit to generate the Flash command interrupt request. The Flash module uses the DFDIF and SFDIF flags in combination with the DFDIE and SFDIE interrupt enable bits to generate the Flash error interrupt request. For a detailed description of the register bits involved, refer to Section 30.3.2.5, "Flash Configuration Register (FCNFG)", Section 30.3.2.6, "Flash Error Configuration Register (FERCNFG)", Section 30.3.2.7, "Flash Status Register (FSTAT)", and Section 30.3.2.8, "Flash Error Status Register (FERSTAT)".

The logic used for generating the Flash module interrupts is shown in Figure 30-27.

Figure 30-27. Flash Module Interrupts Implementation

#### 30.4.8 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 30.4.7, "Interrupts").

### 30.4.9 Stop Mode

If a Flash command is active (CCIF = 0) when the MCU requests stop mode, the current Flash operation will be completed before the MCU is allowed to enter stop mode.

#### 240 KByte Flash Module (S12FTMRG240K2V1)

| BUSCLK Frequency<br>(MHz) |                  | FDIV[5:0] | BUSCLK Frequency<br>(MHz) |                  | FDIV[5:0] |

|---------------------------|------------------|-----------|---------------------------|------------------|-----------|

| MIN <sup>1</sup>          | MAX <sup>2</sup> |           | MIN <sup>1</sup>          | MAX <sup>2</sup> |           |

| 1.0                       | 1.6              | 0x00      | 16.6                      | 17.6             | 0x10      |

| 1.6                       | 2.6              | 0x01      | 17.6                      | 18.6             | 0x11      |

| 2.6                       | 3.6              | 0x02      | 18.6                      | 19.6             | 0x12      |

| 3.6                       | 4.6              | 0x03      | 19.6                      | 20.6             | 0x13      |

| 4.6                       | 5.6              | 0x04      | 20.6                      | 21.6             | 0x14      |

| 5.6                       | 6.6              | 0x05      | 21.6                      | 22.6             | 0x15      |

| 6.6                       | 7.6              | 0x06      | 22.6                      | 23.6             | 0x16      |

| 7.6                       | 8.6              | 0x07      | 23.6                      | 24.6             | 0x17      |

| 8.6                       | 9.6              | 0x08      | 24.6                      | 25.6             | 0x18      |

| 9.6                       | 10.6             | 0x09      |                           |                  |           |

| 10.6                      | 11.6             | 0x0A      |                           |                  |           |

| 11.6                      | 12.6             | 0x0B      |                           |                  |           |

| 12.6                      | 13.6             | 0x0C      |                           |                  |           |

| 13.6                      | 14.6             | 0x0D      |                           |                  |           |

| 14.6                      | 15.6             | 0x0E      |                           |                  |           |

| 15.6                      | 16.6             | 0x0F      |                           |                  |           |

Table 31-8. FDIV values for various BUSCLK Frequencies

<sup>1</sup> BUSCLK is Greater Than this value.

<sup>2</sup> BUSCLK is Less Than or Equal to this value.

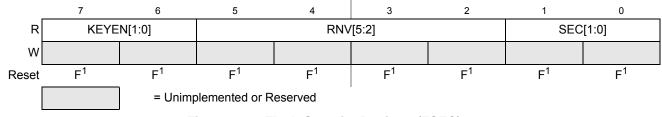

### 31.3.2.2 Flash Security Register (FSEC)

The FSEC register holds all bits associated with the security of the MCU and Flash module.

Offset Module Base + 0x0001

#### Figure 31-6. Flash Security Register (FSEC)

<sup>1</sup> Loaded from IFR Flash configuration field, during reset sequence.

All bits in the FSEC register are readable but not writable.

During the reset sequence, the FSEC register is loaded with the contents of the Flash security byte in the Flash configuration field at global address 0x3\_FF0F located in P-Flash memory (see Table 31-4) as

**Electrical Characteristics**

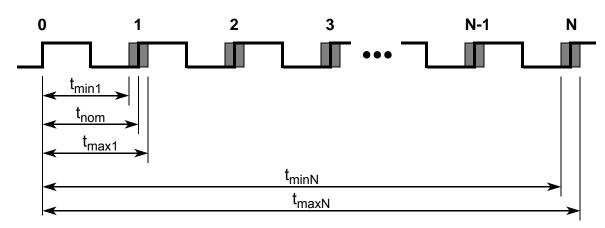

Figure A-4. Jitter Definitions

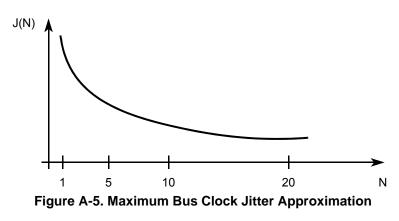

The relative deviation of  $t_{nom}$  is at its maximum for one clock period, and decreases towards zero for larger number of clock periods (N).

Defining the jitter as:

$$J(N) = max\left(\left|1 - \frac{t_{max}(N)}{N \cdot t_{nom}}\right|, \left|1 - \frac{t_{min}(N)}{N \cdot t_{nom}}\right|\right)$$

For N < 100, the following equation is a good fit for the maximum jitter:

$$J(N) = \frac{j_1}{\sqrt{N}}$$

NOTE

On timers and serial modules a prescaler will eliminate the effect of the jitter to a large extent.

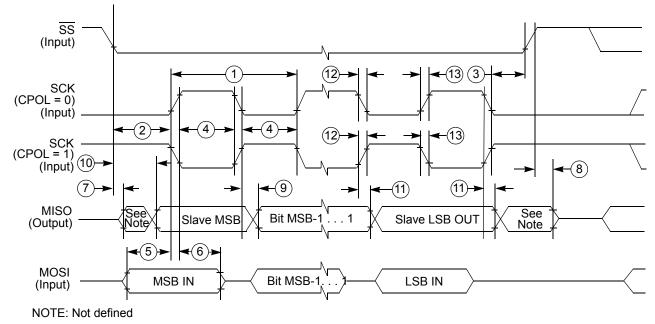

In Table A-51 the timing characteristics for master mode are listed.

| Num | С | Characteristic                    | Symbol            | Min    | Тур | Max  | Unit             |

|-----|---|-----------------------------------|-------------------|--------|-----|------|------------------|

| 1   | D | SCK Frequency                     | f <sub>sck</sub>  | 1/2048 | —   | 1/2  | f <sub>bus</sub> |

| 1   | D | SCK Period                        | t <sub>sck</sub>  | 2      | —   | 2048 | t <sub>bus</sub> |

| 2   | D | Enable Lead Time                  | tL                | —      | 1/2 | —    | t <sub>sck</sub> |

| 3   | D | Enable Trail Time                 | t <sub>T</sub>    | —      | 1/2 | —    | t <sub>sck</sub> |

| 4   | D | Clock (SCK) High or Low Time      | t <sub>wsck</sub> | —      | 1/2 | —    | t <sub>sck</sub> |

| 5   | D | Data Setup Time (Inputs)          | t <sub>su</sub>   | 8      | _   | —    | ns               |

| 6   | D | Data Hold Time (Inputs)           | t <sub>hi</sub>   | 8      | _   | —    | ns               |

| 9   | D | Data Valid after SCK Edge         | t <sub>vsck</sub> | —      | _   | 15   | ns               |

| 10  | D | Data Valid after SS fall (CPHA=0) | t <sub>vss</sub>  | —      | —   | 15   | ns               |

| 11  | D | Data Hold Time (Outputs)          | t <sub>ho</sub>   | 0      | —   | —    | ns               |

| 12  | D | Rise and Fall Time Inputs         | t <sub>rfi</sub>  | —      | —   | 9    | ns               |

| 13  | D | Rise and Fall Time Outputs        | t <sub>rfo</sub>  | —      | _   | 9    | ns               |

Table A-51. SPI Master Mode Timing Characteristics

### A.15.2 Slave Mode

In Figure A-9 the timing diagram for slave mode with transmission format CPHA = 0 is depicted.

Figure A-9. SPI Slave Timing (CPHA = 0)

MC9S12G Family Reference Manual Rev.1.27