#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                 |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 26                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12gn16f1clc |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

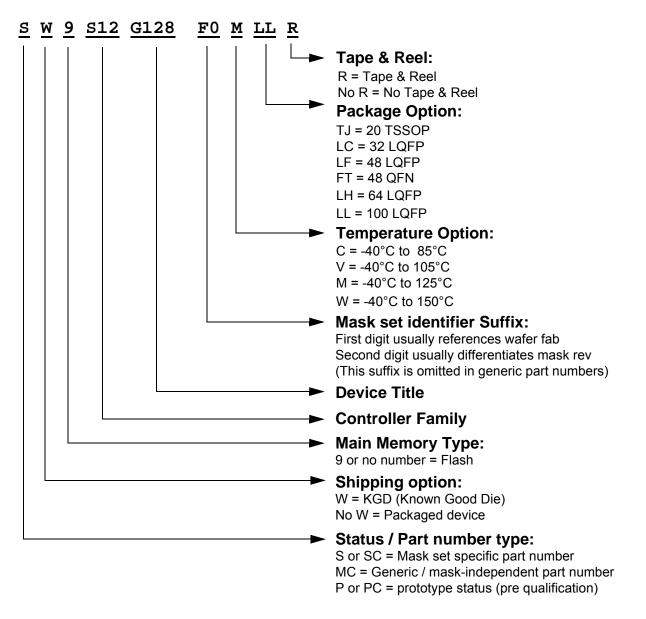

Device Overview MC9S12G-Family

|             |     | <lowest< th=""><th>Function<br/>PRIORITY-</th><th>highest&gt;</th><th>&gt;</th><th>Power</th><th colspan="2">Internal Pull<br/>Resistor</th></lowest<> | Function<br>PRIORITY- | highest>    | >           | Power            | Internal Pull<br>Resistor |                |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|-------------|------------------|---------------------------|----------------|

| Package Pin | Pin | 2nd<br>Func.                                                                                                                                           | 3rd<br>Func.          | 4th<br>Func | 5th<br>Func | Supply           | CTRL                      | Reset<br>State |

| 57          | PS5 | MOSI0                                                                                                                                                  |                       | _           | —           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 58          | PS6 | SCK0                                                                                                                                                   | _                     | _           | —           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 59          | PS7 | API_EXTC<br>LK                                                                                                                                         | ECLK                  | SS0         | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 60          | PM0 | RXCAN                                                                                                                                                  |                       | _           | —           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 61          | PM1 | TXCAN                                                                                                                                                  | _                     | _           | —           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 62          | PM2 | RXD2                                                                                                                                                   | _                     | _           | —           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 63          | PM3 | TXD2                                                                                                                                                   | _                     | _           | —           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 64          | PJ7 | KWJ7                                                                                                                                                   | SS2                   | _           | —           | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

|             |     | <lowest< th=""><th>Function<br/>PRIORITY-</th><th>highest&gt;</th><th>&gt;</th><th>Power</th><th colspan="2">Internal Pull<br/>Resistor</th></lowest<> | Function<br>PRIORITY- | highest>    | >           | Power            | Internal Pull<br>Resistor |                |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|-------------|------------------|---------------------------|----------------|

| Package Pin | Pin | 2nd<br>Func.                                                                                                                                           | 3rd<br>Func.          | 4th<br>Func | 5th<br>Func | Supply           | CTRL                      | Reset<br>State |

| 57          | PS5 | MOSI0                                                                                                                                                  |                       | _           |             | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 58          | PS6 | SCK0                                                                                                                                                   | _                     | _           | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 59          | PS7 | API_EXTC<br>LK                                                                                                                                         | ECLK                  | SS0         | —           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 60          | PM0 | RXCAN                                                                                                                                                  | _                     | _           |             | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 61          | PM1 | TXCAN                                                                                                                                                  | _                     | _           |             | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 62          | PM2 | RXD2                                                                                                                                                   | _                     | _           | _           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 63          | PM3 | TXD2                                                                                                                                                   | _                     | _           | —           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 64          | PJ7 | KWJ7                                                                                                                                                   | SS2                   | _           | —           | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

#### Port Integration Module (S12GPIMV1)

<sup>1</sup> Read: Anytime

Write:

IRQE: Once in normal mode, anytime in special mode IRQEN: Anytime

#### Table 2-34. IRQCR Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IRQE  | <ul> <li>IRQ select edge sensitive only—</li> <li>1 IRQ pin configured to respond only to falling edges. Falling edges on the IRQ pin are detected anytime when IRQE=1 and will be cleared only upon a reset or the servicing of the IRQ interrupt.</li> <li>0 IRQ pin configured for low level recognition</li> </ul> |

| 6<br>IRQEN | IRQ enable—<br>1 IRQ pin is connected to interrupt logic<br>0 IRQ pin is disconnected from interrupt logic                                                                                                                                                                                                             |

#### NOTE

If the input is driven to active level (IRQ=0) a write access to set either IRQCR[IRQEN] and IRQCR[IRQE] to 1 simultaneously or to set IRQCR[IRQEN] to 1 when IRQCR[IRQE]=1 causes an IRQ interrupt to be generated if the I-bit is cleared. Refer to Section 2.6.3, "Enabling IRQ edge-sensitive mode".

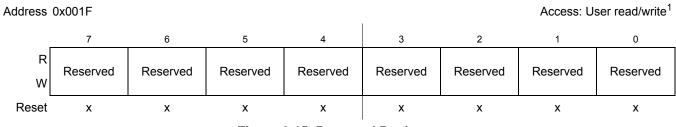

#### 2.4.3.14 Reserved Register

Figure 2-15. Reserved Register

<sup>1</sup> Read: Anytime

Write: Only in special mode

These reserved registers are designed for factory test purposes only and are not intended for general user access. Writing to these registers when in special mode can alter the module's functionality.

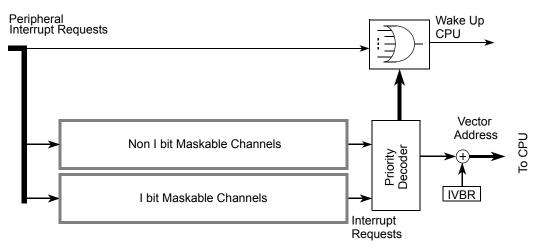

Figure 6-1. INT Block Diagram

# 6.2 External Signal Description

The INT module has no external signals.

# 6.3 Memory Map and Register Definition

This section provides a detailed description of all registers accessible in the INT module.

## 6.3.1 Register Descriptions

This section describes in address order all the INT registers and their individual bits.

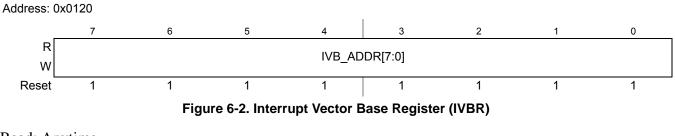

### 6.3.1.1 Interrupt Vector Base Register (IVBR)

Read: Anytime

Write: Anytime

• The Internal Reference Clock (IRC1M) provides a1MHz clock.

## 10.1.1 Features

The Pierce Oscillator (XOSCLCP) contains circuitry to dynamically control current gain in the output amplitude. This ensures a signal with low harmonic distortion, low power and good noise immunity.

- Supports quartz crystals or ceramic resonators from 4MHz to 16MHz.

- High noise immunity due to input hysteresis and spike filtering.

- Low RF emissions with peak-to-peak swing limited dynamically

- Transconductance (gm) sized for optimum start-up margin for typical crystals

- Dynamic gain control eliminates the need for external current limiting resistor

- Integrated resistor eliminates the need for external bias resistor.

- Low power consumption: Operates from internal 1.8V (nominal) supply, Amplitude control limits power

The Voltage Regulator (IVREG) has the following features:

- Input voltage range from 3.13V to 5.5V

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR)

- Low-voltage reset (LVR)

The Phase Locked Loop (PLL) has the following features:

- highly accurate and phase locked frequency multiplier

- Configurable internal filter for best stability and lock time.

- Frequency modulation for defined jitter and reduced emission

- Automatic frequency lock detector

- Interrupt request on entry or exit from locked condition

- Reference clock either external (crystal) or internal square wave (1MHz IRC1M) based.

- PLL stability is sufficient for LIN communication, even if using IRC1M as reference clock

The Internal Reference Clock (IRC1M) has the following features:

- Frequency trimming

- (A factory trim value for 1MHz is loaded from Flash Memory into the IRCTRIM register after reset, which can be overwritten by application if required)

- Temperature Coefficient (TC) trimming. (A factory trim value is loaded from Flash Memory into the IRCTRIM register to turned off TC trimming after reset. Application can trim the TC if required by overwriting the IRCTRIM register).

•

Other features of the S12CPMU include

• Clock monitor to detect loss of crystal

Analog-to-Digital Converter (ADC12B16CV2)

## 16.3.2.4 ATD Control Register 3 (ATDCTL3)

Writes to this register will abort current conversion sequence.

Module Base + 0x0003

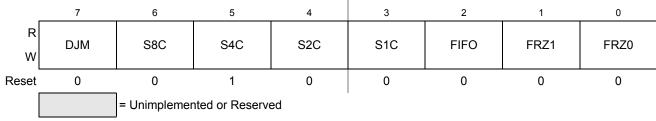

#### Figure 16-6. ATD Control Register 3 (ATDCTL3)

Read: Anytime

Write: Anytime

| Field                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DJM                     | <ul> <li>Result Register Data Justification — Result data format is always unsigned. This bit controls justification of conversion data in the result registers.</li> <li>0 Left justified data in the result registers.</li> <li>1 Right justified data in the result registers.</li> <li>Table 16-9 gives example ATD results for an input signal range between 0 and 5.12 Volts.</li> </ul>                                                                                                              |

| 6–3<br>S8C, S4C,<br>S2C, S1C | <b>Conversion Sequence Length</b> — These bits control the number of conversions per sequence. Table 16-10 shows all combinations. At reset, S4C is set to 1 (sequence length is 4). This is to maintain software continuity to HC12 family.                                                                                                                                                                                                                                                                |

| 2<br>FIFO                    | <b>Result Register FIFO Mode</b> — If this bit is zero (non-FIFO mode), the A/D conversion results map into the result registers based on the conversion sequence; the result of the first conversion appears in the first result register (ATDDR0), the second result in the second result register (ATDDR1), and so on.                                                                                                                                                                                   |

|                              | If this bit is one (FIFO mode) the conversion counter is not reset at the beginning or end of a conversion sequence; sequential conversion results are placed in consecutive result registers. In a continuously scanning conversion sequence, the result register counter will wrap around when it reaches the end of the result register file. The conversion counter value (CC3-0 in ATDSTAT0) can be used to determine where in the result register file, the current conversion result will be placed. |

|                              | Aborting a conversion or starting a new conversion clears the conversion counter even if FIFO=1. So the first result of a new conversion sequence, started by writing to ATDCTL5, will always be place in the first result register (ATDDDR0). Intended usage of FIFO mode is continuos conversion (SCAN=1) or triggered conversion (ETRIG=1).                                                                                                                                                              |

|                              | Which result registers hold valid data can be tracked using the conversion complete flags. Fast flag clear mode may be useful in a particular application to track valid data.                                                                                                                                                                                                                                                                                                                              |

|                              | If this bit is one, automatic compare of result registers is always disabled, that is ADC12B16C will behave as if ACMPIE and all CPME[ <i>n</i> ] were zero.<br>0 Conversion results are placed in the corresponding result register up to the selected sequence length.<br>1 Conversion results are placed in consecutive result registers (wrap around at end).                                                                                                                                           |

| 1–0<br>FRZ[1:0]              | <b>Background Debug Freeze Enable</b> — When debugging an application, it is useful in many cases to have the ATD pause when a breakpoint (Freeze Mode) is encountered. These 2 bits determine how the ATD will respond to a breakpoint as shown in Table 16-11. Leakage onto the storage node and comparator reference capacitors may compromise the accuracy of an immediately frozen conversion depending on the length of the freeze period.                                                            |

#### Table 16-8. ATDCTL3 Field Descriptions

# 16.4 Functional Description

The ADC12B16C consists of an analog sub-block and a digital sub-block.

## 16.4.1 Analog Sub-Block

The analog sub-block contains all analog electronics required to perform a single conversion. Separate power supplies VDDA and VSSA allow to isolate noise of other MCU circuitry from the analog sub-block.

### 16.4.1.1 Sample and Hold Machine

The Sample and Hold Machine controls the storage and charge of the sample capacitor to the voltage level of the analog signal at the selected ADC input channel.

During the sample process the analog input connects directly to the storage node.

The input analog signals are unipolar and must be within the potential range of VSSA to VDDA.

During the hold process the analog input is disconnected from the storage node.

### 16.4.1.2 Analog Input Multiplexer

The analog input multiplexer connects one of the 16 external analog input channels to the sample and hold machine.

### 16.4.1.3 Analog-to-Digital (A/D) Machine

The A/D Machine performs analog to digital conversions. The resolution is program selectable to be either 8 or 10 or 12 bits. The A/D machine uses a successive approximation architecture. It functions by comparing the sampled and stored analog voltage with a series of binary coded discrete voltages.

By following a binary search algorithm, the A/D machine identifies the discrete voltage that is nearest to the sampled and stored voltage.

When not converting the A/D machine is automatically powered down.

Only analog input signals within the potential range of VRL to VRH (A/D reference potentials) will result in a non-railed digital output code.

## 16.4.2 Digital Sub-Block

This subsection describes some of the digital features in more detail. See Section 16.3.2, "Register Descriptions" for all details.

### 16.4.2.1 External Trigger Input

The external trigger feature allows the user to synchronize ATD conversions to an external event rather than relying only on software to trigger the ATD module when a conversion is about to take place. The external trigger signal (out of reset ATD channel 15, configurable in ATDCTL1) is programmable to be

Scalable Controller Area Network (S12MSCANV3)

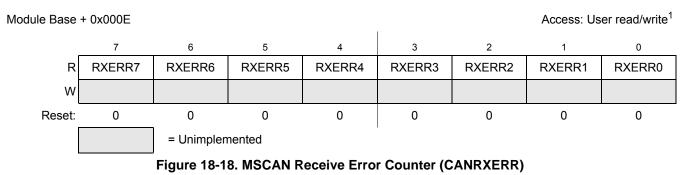

## 18.3.2.15 MSCAN Receive Error Counter (CANRXERR)

This register reflects the status of the MSCAN receive error counter.

<sup>1</sup> Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

#### NOTE

Reading this register when in any other mode other than sleep or initialization mode may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

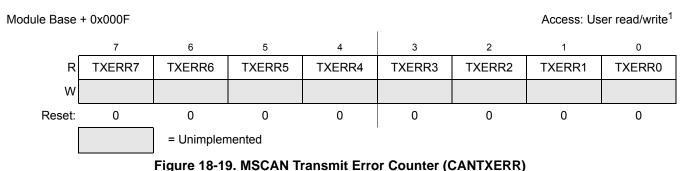

### 18.3.2.16 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

#### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

#### MC9S12G Family Reference Manual Rev.1.27

## 18.4.3.1 Protocol Violation Protection

The MSCAN protects the user from accidentally violating the CAN protocol through programming errors. The protection logic implements the following features:

- The receive and transmit error counters cannot be written or otherwise manipulated.

- All registers which control the configuration of the MSCAN cannot be modified while the MSCAN is on-line. The MSCAN has to be in Initialization Mode. The corresponding INITRQ/INITAK handshake bits in the CANCTL0/CANCTL1 registers (see Section 18.3.2.1, "MSCAN Control Register 0 (CANCTL0)") serve as a lock to protect the following registers:

- MSCAN control 1 register (CANCTL1)

- MSCAN bus timing registers 0 and 1 (CANBTR0, CANBTR1)

- MSCAN identifier acceptance control register (CANIDAC)

- MSCAN identifier acceptance registers (CANIDAR0–CANIDAR7)

- MSCAN identifier mask registers (CANIDMR0–CANIDMR7)

- The TXCAN is immediately forced to a recessive state when the MSCAN goes into the power down mode or initialization mode (see Section 18.4.5.6, "MSCAN Power Down Mode," and Section 18.4.4.5, "MSCAN Initialization Mode").

- The MSCAN enable bit (CANE) is writable only once in normal system operation modes, which provides further protection against inadvertently disabling the MSCAN.

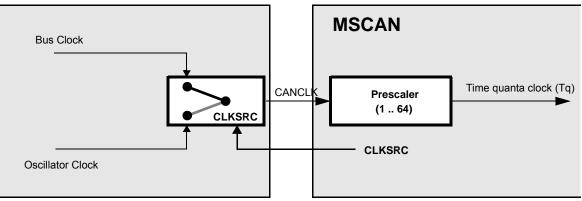

## 18.4.3.2 Clock System

Figure 18-43 shows the structure of the MSCAN clock generation circuitry.

Figure 18-43. MSCAN Clocking Scheme

The clock source bit (CLKSRC) in the CANCTL1 register (18.3.2.2/18-576) defines whether the internal CANCLK is connected to the output of a crystal oscillator (oscillator clock) or to the bus clock.

The clock source has to be chosen such that the tight oscillator tolerance requirements (up to 0.4%) of the CAN protocol are met. Additionally, for high CAN bus rates (1 Mbps), a 45% to 55% duty cycle of the clock is required.

If the bus clock is generated from a PLL, it is recommended to select the oscillator clock rather than the bus clock due to jitter considerations, especially at the faster CAN bus rates.

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | Loop Select Bit — LOOPS enables loop operation. In loop operation, the RXD pin is disconnected from the SCI and the transmitter output is internally connected to the receiver input. Both the transmitter and the receiver must be enabled to use the loop function.<br>0 Normal operation enabled<br>1 Loop operation enabled<br>The receiver input is determined by the RSRC bit.                                                                                                                                                                                    |

| 6<br>SCISWAI | <ul> <li>SCI Stop in Wait Mode Bit — SCISWAI disables the SCI in wait mode.</li> <li>0 SCI enabled in wait mode</li> <li>1 SCI disabled in wait mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>RSRC    | Receiver Source Bit — When LOOPS = 1, the RSRC bit determines the source for the receiver shift register input. See Table 20-5.         0       Receiver input internally connected to transmitter output         1       Receiver input connected externally to transmitter                                                                                                                                                                                                                                                                                            |

| 4<br>M       | <ul> <li>Data Format Mode Bit — MODE determines whether data characters are eight or nine bits long.</li> <li>0 One start bit, eight data bits, one stop bit</li> <li>1 One start bit, nine data bits, one stop bit</li> </ul>                                                                                                                                                                                                                                                                                                                                          |

| 3<br>WAKE    | <ul> <li>Wakeup Condition Bit — WAKE determines which condition wakes up the SCI: a logic 1 (address mark) in the most significant bit position of a received data character or an idle condition on the RXD pin.</li> <li>0 Idle line wakeup</li> <li>1 Address mark wakeup</li> </ul>                                                                                                                                                                                                                                                                                 |

| 2<br>ILT     | Idle Line Type Bit — ILT determines when the receiver starts counting logic 1s as idle character bits. The<br>counting begins either after the start bit or after the stop bit. If the count begins after the start bit, then a string of<br>logic 1s preceding the stop bit may cause false recognition of an idle character. Beginning the count after the<br>stop bit avoids false idle character recognition, but requires properly synchronized transmissions.0Idle character bit count begins after start bit<br>11Idle character bit count begins after stop bit |

| 1<br>PE      | <ul> <li>Parity Enable Bit — PE enables the parity function. When enabled, the parity function inserts a parity bit in the most significant bit position.</li> <li>0 Parity function disabled</li> <li>1 Parity function enabled</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| 0<br>PT      | <ul> <li>Parity Type Bit — PT determines whether the SCI generates and checks for even parity or odd parity. With even parity, an even number of 1s clears the parity bit and an odd number of 1s sets the parity bit. With odd parity, an odd number of 1s clears the parity bit and an even number of 1s sets the parity bit.</li> <li>0 Even parity</li> <li>1 Odd parity</li> </ul>                                                                                                                                                                                 |

#### Table 20-5. Loop Functions

| LOOPS | RSRC | Function                                                                 |  |

|-------|------|--------------------------------------------------------------------------|--|

| 0     | х    | Normal operation                                                         |  |

| 1     | 0    | Loop mode with transmitter output internally connected to receiver input |  |

| 1     | 1    | Single-wire mode with TXD pin connected to receiver input                |  |

### NOTE

Care must be taken when expecting data from a master while the slave is in wait or stop mode. Even though the shift register will continue to operate, the rest of the SPI is shut down (i.e., a SPIF interrupt will **not** be generated until exiting stop or wait mode). Also, the byte from the shift register will not be copied into the SPIDR register until after the slave SPI has exited wait or stop mode. In slave mode, a received byte pending in the receive shift register will be lost when entering wait or stop mode. An SPIF flag and SPIDR copy is generated only if wait mode is entered or exited during a tranmission. If the slave enters wait mode in idle mode and exits wait mode in idle mode, neither a SPIF nor a SPIDR copy will occur.

## 21.4.7.3 SPI in Stop Mode

Stop mode is dependent on the system. The SPI enters stop mode when the module clock is disabled (held high or low). If the SPI is in master mode and exchanging data when the CPU enters stop mode, the transmission is frozen until the CPU exits stop mode. After stop, data to and from the external SPI is exchanged correctly. In slave mode, the SPI will stay synchronized with the master.

The stop mode is not dependent on the SPISWAI bit.

## 21.4.7.4 Reset

The reset values of registers and signals are described in Section 21.3, "Memory Map and Register Definition", which details the registers and their bit fields.

- If a data transmission occurs in slave mode after reset without a write to SPIDR, it will transmit garbage, or the data last received from the master before the reset.

- Reading from the SPIDR after reset will always read zeros.

### 21.4.7.5 Interrupts

The SPI only originates interrupt requests when SPI is enabled (SPE bit in SPICR1 set). The following is a description of how the SPI makes a request and how the MCU should acknowledge that request. The interrupt vector offset and interrupt priority are chip dependent.

The interrupt flags MODF, SPIF, and SPTEF are logically ORed to generate an interrupt request.

### 21.4.7.5.1 MODF

MODF occurs when the master detects an error on the  $\overline{SS}$  pin. The master SPI must be configured for the MODF feature (see Table 21-2). After MODF is set, the current transfer is aborted and the following bit is changed:

• MSTR = 0, The master bit in SPICR1 resets.

The MODF interrupt is reflected in the status register MODF flag. Clearing the flag will also clear the interrupt. This interrupt will stay active while the MODF flag is set. MODF has an automatic clearing process which is described in Section 21.3.2.4, "SPI Status Register (SPISR)".

### 24.4.7 Interrupts

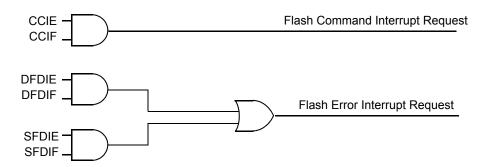

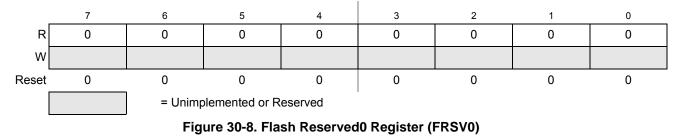

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Interrupt Source                   | Interrupt Flag              | Local Enable                | Global (CCR)<br>Mask |

|------------------------------------|-----------------------------|-----------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | l Bit                |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register) | DFDIE<br>(FERCNFG register) | l Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | l Bit                |

Table 24-64. Flash Interrupt Sources

#### NOTE

Vector addresses and their relative interrupt priority are determined at the MCU level.

### 24.4.7.1 Description of Flash Interrupt Operation

The Flash module uses the CCIF flag in combination with the CCIE interrupt enable bit to generate the Flash command interrupt request. The Flash module uses the DFDIF and SFDIF flags in combination with the DFDIE and SFDIE interrupt enable bits to generate the Flash error interrupt request. For a detailed description of the register bits involved, refer to Section 24.3.2.5, "Flash Configuration Register (FCNFG)", Section 24.3.2.6, "Flash Error Configuration Register (FERCNFG)", Section 24.3.2.7, "Flash Status Register (FSTAT)", and Section 24.3.2.8, "Flash Error Status Register (FERSTAT)".

The logic used for generating the Flash module interrupts is shown in Figure 24-26.

Figure 24-26. Flash Module Interrupts Implementation

It is possible to read from P-Flash memory while some commands are executing on EEPROM memory. It is not possible to read from EEPROM memory while a command is executing on P-Flash memory. Simultaneous P-Flash and EEPROM operations are discussed in Section 27.4.5.

Both P-Flash and EEPROM memories are implemented with Error Correction Codes (ECC) that can resolve single bit faults and detect double bit faults. For P-Flash memory, the ECC implementation requires that programming be done on an aligned 8 byte basis (a Flash phrase). Since P-Flash memory is always read by half-phrase, only one single bit fault in an aligned 4 byte half-phrase containing the byte or word accessed will be corrected.

# 27.1.1 Glossary

**Command Write Sequence** — An MCU instruction sequence to execute built-in algorithms (including program and erase) on the Flash memory.

**EEPROM Memory** — The EEPROM memory constitutes the nonvolatile memory store for data.

**EEPROM Sector** — The EEPROM sector is the smallest portion of the EEPROM memory that can be erased. The EEPROM sector consists of 4 bytes.

**NVM Command Mode** — An NVM mode using the CPU to setup the FCCOB register to pass parameters required for Flash command execution.

**Phrase** — An aligned group of four 16-bit words within the P-Flash memory. Each phrase includes two sets of aligned double words with each set including 7 ECC bits for single bit fault correction and double bit fault detection within each double word.

**P-Flash Memory** — The P-Flash memory constitutes the main nonvolatile memory store for applications.

**P-Flash Sector** — The P-Flash sector is the smallest portion of the P-Flash memory that can be erased. Each P-Flash sector contains 512 bytes.

**Program IFR** — Nonvolatile information register located in the P-Flash block that contains the Version ID, and the Program Once field.

## 27.1.2 Features

### 27.1.2.1 P-Flash Features

- 64 Kbytes of P-Flash memory composed of one 64 Kbyte Flash block divided into 128 sectors of 512 bytes

- Single bit fault correction and double bit fault detection within a 32-bit double word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

64 KByte Flash Module (S12FTMRG64K1V1)

MC9S12G Family Reference Manual Rev.1.27

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |  |  |  |

|-------------|----------------------------------------------------------|----------------------------------------------|--|--|--|

| 000         | 0x03                                                     | Global address [17:16] of<br>a P-Flash block |  |  |  |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |  |  |  |

| 010         | Number of phrases to be verified                         |                                              |  |  |  |

Table 27-36. Erase Verify P-Flash Section Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 27-37. Erase Verify P-Flash Section Command Error Handling

| Register | Error Bit   | Error Condition                                                                                   |  |  |  |

|----------|-------------|---------------------------------------------------------------------------------------------------|--|--|--|

|          |             | Set if CCOBIX[2:0] != 010 at command launch                                                       |  |  |  |

|          |             | Set if command not available in current mode (see Table 27-27)                                    |  |  |  |

|          | ACCERR      | Set if an invalid global address [17:0] is supplied see Table 27-3)                               |  |  |  |

|          |             | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                      |  |  |  |

| FSTAT    |             | Set if the requested section crosses a the P-Flash address boundary                               |  |  |  |

|          | FPVIOL None |                                                                                                   |  |  |  |

|          | MGSTAT1     | Set if any errors have been encountered during the read or if blank check failed                  |  |  |  |

|          | MGSTAT0     | Set if any non-correctable errors have been encountered during the read or if blank check failed. |  |  |  |

### 27.4.6.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once command described in Section 27.4.6.6. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                         |              |  |  |

|-------------|------------------------------------------|--------------|--|--|

| 000         | 0x04                                     | Not Required |  |  |

| 001         | Read Once phrase index (0x0000 - 0x0007) |              |  |  |

| 010         | Read Once word 0 value                   |              |  |  |

| 011         | Read Once word 1 value                   |              |  |  |

| 100         | Read Once word 2 value                   |              |  |  |

| 101         | Read Once                                | word 3 value |  |  |

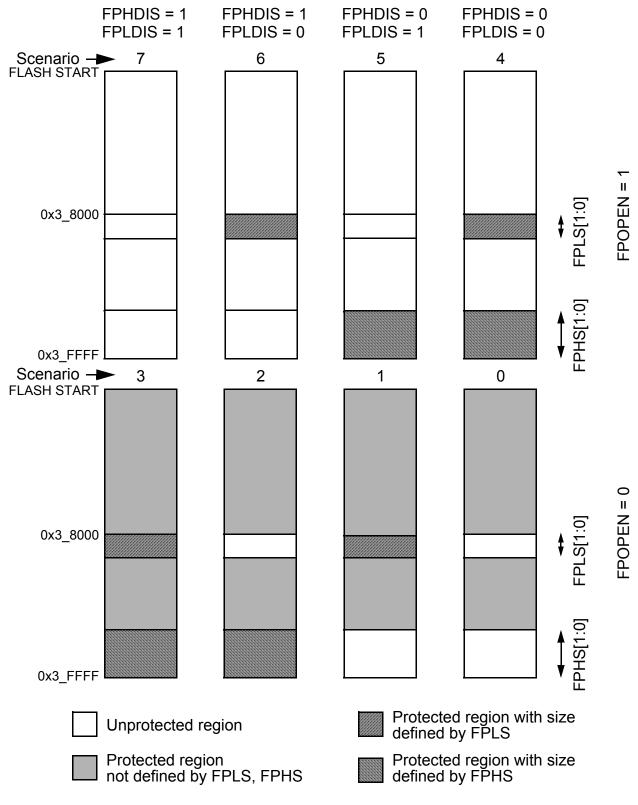

| FPHS[1:0] | Global Address Range | Protected Size |  |  |

|-----------|----------------------|----------------|--|--|

| 00        | 0x3_F800-0x3_FFFF    | 2 Kbytes       |  |  |

| 01        | 0x3_F000-0x3_FFFF    | 4 Kbytes       |  |  |

| 10        | 0x3_E000-0x3_FFFF    | 8 Kbytes       |  |  |

| 11        | 0x3_C000-0x3_FFFF    | 16 Kbytes      |  |  |

| Table 28-19. | P-Flash    | Protection   | Higher  | Address Range |

|--------------|------------|--------------|---------|---------------|

|              | 1 1 10.511 | 1 1010011011 | ingilei | Address Runge |

#### Table 28-20. P-Flash Protection Lower Address Range

| FPLS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_8000-0x3_83FF    | 1 Kbyte        |

| 01        | 0x3_8000-0x3_87FF    | 2 Kbytes       |

| 10        | 0x3_8000-0x3_8FFF    | 4 Kbytes       |

| 11        | 0x3_8000-0x3_9FFF    | 8 Kbytes       |

All possible P-Flash protection scenarios are shown in Figure 28-14. Although the protection scheme is loaded from the Flash memory at global address 0x3\_FFOC during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

#### 192 KByte Flash Module (S12FTMRG192K2V1)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

| Table 30-12 | . FCCOBIX Field | d Descriptions |

|-------------|-----------------|----------------|

|-------------|-----------------|----------------|

| Field              | Description                                                                                                                                                                                                                  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2–0<br>CCOBIX[1:0] | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See 30.3.2.11 Flash Common Command Object Register (FCCOB)," for more details. |

### 30.3.2.4 Flash Reserved0 Register (FRSV0)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000C

All bits in the FRSV0 register read 0 and are not writable.

### 30.3.2.5 Flash Configuration Register (FCNFG)

The FCNFG register enables the Flash command complete interrupt and forces ECC faults on Flash array read access from the CPU.

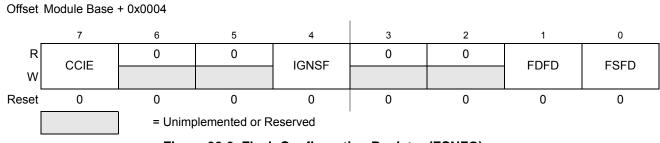

Figure 30-9. Flash Configuration Register (FCNFG)

CCIE, IGNSF, FDFD, and FSFD bits are readable and writable while remaining bits read 0 and are not writable.

All VDDX pins are internally connected by metal.

All VSSX pins are internally connected by metal.

VDDA, VDDX and VSSA, VSSX are connected by diodes for ESD protection.

### NOTE

In the following context  $V_{DD35}$  is used for either VDDA, VDDR, and VDDX;  $V_{SS35}$  is used for either VSSA and VSSX unless otherwise noted.

$I_{\text{DD35}}$  denotes the sum of the currents flowing into the VDDA, VDDX and VDDR pins.

## A.1.3 Pins

There are four groups of functional pins.

### A.1.3.1 I/O Pins

The I/O pins have a level in the range of 3.13V to 5.5V. This class of pins is comprised of all port I/O pins, the analog inputs, BKGD and the RESET pins. Some functionality may be disabled.

### A.1.3.2 Analog Reference

This group consists of the VRH pin.

### A.1.3.3 Oscillator

The pins EXTAL, XTAL dedicated to the oscillator have a nominal 1.8V level.

### A.1.3.4 TEST

This pin is used for production testing only. The TEST pin must be tied to ground in all applications.

## A.1.4 Current Injection

Power supply must maintain regulation within operating  $V_{DD35}$  or  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD35}$ ) is greater than  $I_{DD35}$ , the injection current may flow out of  $V_{DD35}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD35}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power; e.g., if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

## A.1.5 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only. A functional operation under or outside those maxima is not guaranteed. Stress beyond those limits may affect the reliability or cause permanent damage of the device.

# A.12 Electrical Specification for Voltage Regulator

| Num | С | Characteristic                                                                                                                                                                                                                                                                                                | Symbol                                 | Min          | Typical      | Мах          | Unit   |

|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|--------------|--------------|--------|

| 1   | Р | Input Voltages                                                                                                                                                                                                                                                                                                | V <sub>VDDR,A</sub>                    | 3.13         | _            | 5.5          | V      |

| 2   | Ρ | V <sub>DDA</sub> Low Voltage Interrupt Assert Level <sup>1</sup><br>V <sub>DDA</sub> Low Voltage Interrupt Deassert Level                                                                                                                                                                                     | V <sub>LVIA</sub><br>V <sub>LVID</sub> | 4.04<br>4.19 | 4.23<br>4.38 | 4.40<br>4.49 | V<br>V |

| 3   | Р | V <sub>DDX</sub> Low Voltage Reset Deassert <sup>2 3 4</sup>                                                                                                                                                                                                                                                  | V <sub>LVRXD</sub>                     | —            | 3.05         | 3.13         | V      |

| 4   | Р | V <sub>DDX</sub> Low Voltage Reset Assert <sup>2 3 4</sup>                                                                                                                                                                                                                                                    | V <sub>LVRXA</sub>                     | 2.95         | 3.02         | _            | V      |

| 5   | Т | CPMU ACLK frequency<br>(CPMUACLKTR[5:0] = %000000)                                                                                                                                                                                                                                                            | f <sub>ACLK</sub>                      | _            | 10           | _            | KHz    |

| 6   | С | Trimmed ACLK internal clock <sup>5</sup> $\Delta f$ / f <sub>nominal</sub>                                                                                                                                                                                                                                    | df <sub>ACLK</sub>                     | - 5%         | _            | + 5%         | —      |

| 7   | D | The first period after enabling the counter<br>by APIFE might be reduced by ACLK start<br>up delay                                                                                                                                                                                                            | t <sub>sdel</sub>                      | _            | _            | 100          | us     |

| 8   | D | The first period after enabling the COP might be reduced by ACLK start up delay                                                                                                                                                                                                                               | t <sub>sdel</sub>                      |              | _            | 100          | us     |

| 9   | Ρ | Output Voltage Flash<br>Full Performance Mode<br>Reduced Power Mode (MCU STOP<br>mode)                                                                                                                                                                                                                        | V <sub>DDF</sub>                       | 2.6<br>1.1   | 2.82<br>1.6  | 2.9<br>1.98  | V<br>V |

| 10  | С | $\begin{array}{l} V_{DDF} \text{ Voltage Distribution} \\ \text{over input voltage } V_{DDA}{}^6 \\ 4.5V \leq V_{DDA} \leq 5.5V, \ T_{A} = 27^{o}C \\ \text{compared to } V_{DDA} = 5.0V \end{array}$                                                                                                         |                                        | -5           | 0            | 5            | mV     |

| 11  | С | $\begin{array}{l} V_{DDF} \text{ Voltage Distribution} \\ \text{over ambient temperature } T_A \\ V_{DDA} = 5V, -40^\circ\text{C} \leq T_A \leq 125^\circ\text{C} \\ \text{compared to } V_{DDF} \text{ production test value} \\ \text{(see A.16, "ADC Conversion Result} \\ \text{Reference")} \end{array}$ | $\Delta_{VDDF}$                        | -20          | -            | +20          | mV     |

#### Table A-47. Voltage Regulator Characteristics (Junction Temperature From –40°C To +150°C)

<sup>1</sup> Monitors VDDA, active only in Full Performance Mode. Indicates I/O & ADC performance degradation due to low supply voltage.

<sup>2</sup> Device functionality is guaranteed on power down to the LVR assert level

<sup>3</sup> Monitors VDDX, active only in Full Performance Mode. MCU is monitored by the POR in RPM (see Figure A-6)

$^{4}$  V<sub>LVRXA</sub> < V<sub>LVRXD</sub>. The hysteresis is unspecified and untested.

<sup>5</sup> The ACLK Trimming CPMUACLKTR[5:0] bits must be set so that f<sub>ACLK</sub>=10KHz.

$^{6}$  VDDR  $\geq$  3.13V