# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 40                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 1K x 8                                                                  |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-TFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12gn32f0cftr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |                  | <lowest< th=""><th>Function</th><th>Power</th><th colspan="2">Internal Pull<br/>Resistor</th></lowest<> | Function     | Power          | Internal Pull<br>Resistor |                  |               |                |

|-------------|------------------|---------------------------------------------------------------------------------------------------------|--------------|----------------|---------------------------|------------------|---------------|----------------|

| Package Pin | Pin              | 2nd<br>Func.                                                                                            | 3rd<br>Func. | 4th<br>Func    | 5th<br>Func               | Supply           | CTRL          | Reset<br>State |

| 2           | VDDXR            | _                                                                                                       | —            | _              | _                         | _                | _             | _              |

| 3           | VSSX             | _                                                                                                       | —            | —              | _                         | —                | —             | _              |

| 4           | PE0 <sup>1</sup> | EXTAL                                                                                                   | —            | —              | _                         | V <sub>DDX</sub> | PUCR/PDPEE    | Down           |

| 5           | VSS              |                                                                                                         | —            | _              |                           | _                | _             | _              |

| 6           | PE1 <sup>1</sup> | XTAL                                                                                                    | —            | _              | _                         | V <sub>DDX</sub> | PUCR/PDPEE    | Down           |

| 7           | TEST             | _                                                                                                       | —            | _              | _                         | N.A.             | RESET pin     | Down           |

| 8           | PJ0              | KWJ0                                                                                                    | PWM6         | MISO1          | _                         | V <sub>DDX</sub> | PERJ/PPSJ     | Up             |

| 9           | PJ1              | KWJ1                                                                                                    | IOC6         | MOSI1          |                           | V <sub>DDX</sub> | PERJ/PPSJ     | Up             |

| 10          | PJ2              | KWJ2                                                                                                    | IOC7         | SCK1           |                           | V <sub>DDX</sub> | PERJ/PPSJ     | Up             |

| 11          | PJ3              | KWJ3                                                                                                    | PWM7         | SS1            |                           | V <sub>DDX</sub> | PERJ/PPSJ     | Up             |

| 12          | BKGD             | MODC                                                                                                    | _            | —              |                           | V <sub>DDX</sub> | PUCR/BKPUE    | Up             |

| 13          | PP0              | KWP0                                                                                                    | ETRIG0       | API_EXTC<br>LK | PWM0                      | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 14          | PP1              | KWP1                                                                                                    | ETRIG1       | ECLKX2         | PWM1                      | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 15          | PP2              | KWP2                                                                                                    | ETRIG2       | PWM2           |                           | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 16          | PP3              | KWP3                                                                                                    | ETRIG3       | PWM3           | _                         | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 17          | PP4              | KWP4                                                                                                    | PWM4         | _              |                           | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 18          | PP5              | KWP5                                                                                                    | PWM5         | _              |                           | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 19          | PT5              | IOC5                                                                                                    | —            | _              |                           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 20          | PT4              | IOC4                                                                                                    | —            | _              |                           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 21          | PT3              | IOC3                                                                                                    | —            | _              |                           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 22          | PT2              | IOC2                                                                                                    | —            | _              |                           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 23          | PT1              | IOC1                                                                                                    | IRQ          |                |                           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 24          | PT0              | IOC0                                                                                                    | XIRQ         | _              | _                         | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 25          | PAD0             | KWAD0                                                                                                   | AN0          |                |                           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 26          | PAD8             | KWAD8                                                                                                   | AN8          | _              |                           | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 27          | PAD1             | KWAD1                                                                                                   | AN1          | _              |                           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 28          | PAD9             | KWAD9                                                                                                   | AN9          |                |                           | V <sub>DDA</sub> | PER0AD/PPS0AD | Disabled       |

| 29          | PAD2             | KWAD2                                                                                                   | AN2          | —              |                           | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

Table 1-29. 48-Pin LQFP Pinout for S12GA192 and S12GA240

### 2.3.9 Pins PM3-0

| PM3 | <ul> <li>64/100 LQFP: The SCI2 TXD signal is mapped to this pin when used with the SCI function. If the SCI2 TXD signal is enabled the I/O state will depend on the SCI2 configuration.</li> <li>Signal priority:<br/>64/100 LQFP: TXD2 &gt; GPO</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PM2 | <ul> <li>64/100 LQFP: The SCI2 RXD signal is mapped to this pin when used with the SCI function. If the SCI2 RXD signal is enabled the I/O state will be forced to be input.</li> <li>Signal priority:<br/>64/100 LQFP: RXD2 &gt; GPO</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PM1 | <ul> <li>Except 20 TSSOP: The TXCAN signal is mapped to this pin when used with the CAN function. The enabled CAN forces the I/O state to be an output.</li> <li>32 LQFP: The SCI1 TXD signal is mapped to this pin when used with the SCI function. If the SCI1 TXD signal is enabled the I/O state will depend on the SCI1 configuration.</li> <li>48 LQFP: The SCI2 TXD signal is mapped to this pin when used with the SCI function. If the SCI2 TXD signal is enabled the I/O state will depend on the SCI2 configuration.</li> <li>Signal priority:<br/>32 LQFP: TXCAN &gt; TXD1 &gt; GPO<br/>48 LQFP: TXCAN &gt; TXD2 &gt; GPO<br/>64/100 LQFP: TXCAN &gt; GPO</li> </ul>                                                   |

| PM0 | <ul> <li>Except 20 TSSOP: The RXCAN signal is mapped to this pin when used with the CAN function. The enabled CAN forces the I/O state to be an input. If CAN is active the selection of a pulldown device on the RXCAN input has no effect.</li> <li>32 LQFP: The SCI1 RXD signal is mapped to this pin when used with the SCI function. The enabled SCI1 RXD signal forces the I/O state to an input.</li> <li>48 LQFP: The SCI2 RXD signal is mapped to this pin when used with the SCI function. The enabled SCI2 RXD signal forces the I/O state to an input.</li> <li>Signal priority:</li> <li>32 LQFP: RXCAN &gt; RXD1 &gt; GPO</li> <li>48 LQFP: RXCAN &gt; RXD2 &gt; GPO</li> <li>64/100 LQFP: RXCAN &gt; GPO</li> </ul> |

#### Table 2-13. Port M Pins PM3-0

# 2.3.10 Pins PP7-0

#### Table 2-14. Port P Pins PP7-0

| PP7-PP6 | <ul> <li>64/100 LQFP: The PWM channels 7 and 6 signal are mapped to these pins when used with the PWM function. The enabled PWM channel forces the I/O state to be an output.</li> <li>64/100 LQFP: Pin interrupts can be generated if enabled in input or output mode.</li> <li>Signal priority:<br/>64/100 LQFP: PWM &gt; GPO</li> </ul>          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PP5-PP4 | <ul> <li>48/64/100 LQFP: The PWM channels 5 and 4 signal are mapped to these pins when used with the PWM function. The enabled PWM channel forces the I/O state to be an output.</li> <li>48/64/100 LQFP: Pin interrupts can be generated if enabled in input or output mode.</li> <li>Signal priority:<br/>48/64/100 LQFP: PWM &gt; GPO</li> </ul> |

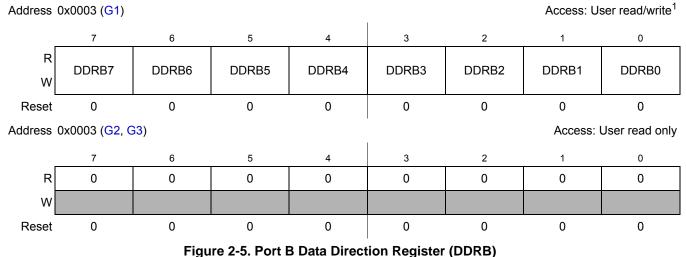

# 2.4.3.4 Port B Data Direction Register (DDRB)

<sup>1</sup> Read: Anytime

Write: Anytime

### Table 2-25. DDRB Register Field Descriptions

| Field       | Description                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------|

| 7-0<br>DDRB | Port B Data Direction—<br>This bit determines whether the associated pin is an input or output. |

|             | 1 Associated pin configured as output<br>0 Associated pin configured as input                   |

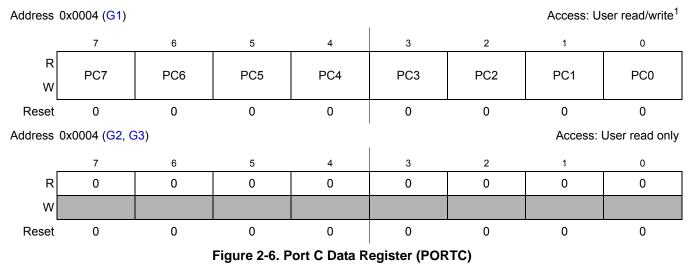

# 2.4.3.5 Port C Data Register (PORTC)

<sup>1</sup> Read: Anytime. The data source is depending on the data direction value. Write: Anytime

### NOTE

If an attempt is made to activate BDM before being enabled, the CPU resumes normal instruction execution after a brief delay. If BDM is not enabled, any hardware BACKGROUND commands issued are ignored by the BDM and the CPU is not delayed.

In active BDM, the BDM registers and standard BDM firmware lookup table are mapped to addresses 0x3\_FF00 to 0x3\_FFFF. BDM registers are mapped to addresses 0x3\_FF00 to 0x3\_FF0B. The BDM uses these registers which are readable anytime by the BDM. However, these registers are not readable by user programs.

When BDM is activated while CPU executes code overlapping with BDM firmware space the saved program counter (PC) will be auto incremented by one from the BDM firmware, no matter what caused the entry into BDM active mode (BGND instruction, BACKGROUND command or breakpoints). In such a case the PC must be set to the next valid address via a WRITE\_PC command before executing the GO command.

# 7.4.3 BDM Hardware Commands

Hardware commands are used to read and write target system memory locations and to enter active background debug mode. Target system memory includes all memory that is accessible by the CPU such as on-chip RAM, Flash, I/O and control registers.

Hardware commands are executed with minimal or no CPU intervention and do not require the system to be in active BDM for execution, although, they can still be executed in this mode. When executing a hardware command, the BDM sub-block waits for a free bus cycle so that the background access does not disturb the running application program. If a free cycle is not found within 128 clock cycles, the CPU is momentarily frozen so that the BDM can steal a cycle. When the BDM finds a free cycle, the operation does not intrude on normal CPU operation provided that it can be completed in a single cycle. However, if an operation requires multiple cycles the CPU is frozen until the operation is complete, even though the BDM found a free cycle.

The BDM hardware commands are listed in Table 7-5.

The READ\_BD and WRITE\_BD commands allow access to the BDM register locations. These locations are not normally in the system memory map but share addresses with the application in memory. To distinguish between physical memory locations that share the same address, BDM memory resources are enabled just for the READ\_BD and WRITE\_BD access cycle. This allows the BDM to access BDM locations unobtrusively, even if the addresses conflict with the application memory map.

| Command     | Opcode<br>(hex) | Data | Description                                                                                                             |

|-------------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------|

| BACKGROUND  | 90              | None | Enter background mode if BDM is enabled. If enabled, an ACK will be issued when the part enters active background mode. |

| ACK_ENABLE  | D5              | None | Enable Handshake. Issues an ACK pulse after the command is executed.                                                    |

| ACK_DISABLE | D6              | None | Disable Handshake. This command does not issue an ACK pulse.                                                            |

### Table 7-5. Hardware Commands

| CR2 | CR1 | CR0 | COPCLK<br>Cycles to Time-out<br>(COPCLK is ACLK -<br>internal RC-Oscillator clock) |

|-----|-----|-----|------------------------------------------------------------------------------------|

| 0   | 0   | 0   | COP disabled                                                                       |

| 0   | 0   | 1   | 2 <sup>7</sup>                                                                     |

| 0   | 1   | 0   | 2 <sup>9</sup>                                                                     |

| 0   | 1   | 1   | 2 <sup>11</sup>                                                                    |

| 1   | 0   | 0   | 2 <sup>13</sup>                                                                    |

| 1   | 0   | 1   | 2 <sup>15</sup>                                                                    |

| 1   | 1   | 0   | 2 <sup>16</sup>                                                                    |

| 1   | 1   | 1   | 2 <sup>17</sup>                                                                    |

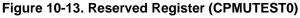

### 10.3.2.10 Reserved Register CPMUTEST0

NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU's functionality.

0x003D R W Reset = Unimplemented or Reserved

Read: Anytime

Write: Only in Special Mode

### 10.3.2.11 Reserved Register CPMUTEST1

### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU's functionality.

S12 Clock, Reset and Power Management Unit (S12CPMU)

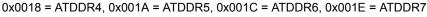

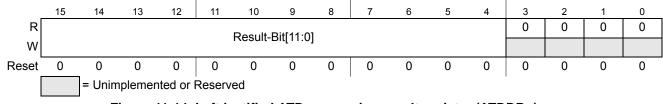

### 11.3.2.12 ATD Conversion Result Registers (ATDDRn)

The A/D conversion results are stored in 8 result registers. Results are always in unsigned data representation. Left and right justification is selected using the DJM control bit in ATDCTL3.

If automatic compare of conversions results is enabled (CMPE[n]=1 in ATDCMPE), these registers must be written with the compare values in left or right justified format depending on the actual value of the DJM bit. In this case, as the ATDDRn register is used to hold the compare value, the result will not be stored there at the end of the conversion but is lost.

### Attention, n is the conversion number, NOT the channel number!

Read: Anytime

Write: Anytime

#### NOTE

For conversions not using automatic compare, results are stored in the result registers after each conversion. In this case avoid writing to ATDDRn except for initial values, because an A/D result might be overwritten.

### 11.3.2.12.1 Left Justified Result Data (DJM=0)

Module Base +

0x0010 = ATDDR0, 0x0012 = ATDDR1, 0x0014 = ATDDR2, 0x0016 = ATDDR3

Figure 11-14. Left justified ATD conversion result register (ATDDRn)

Table 11-21 shows how depending on the A/D resolution the conversion result is transferred to the ATD result registers for left justified data. Compare is always done using all 12 bits of both the conversion result and the compare value in ATDDRn.

| A/D<br>resolution | DJM | conversion result mapping to ATDDR <i>n</i>                   |

|-------------------|-----|---------------------------------------------------------------|

| 8-bit data        | 0   | Result-Bit[11:4] = conversion result,<br>Result-Bit[3:0]=0000 |

| 10-bit data       | 0   | Result-Bit[11:2] = conversion result,<br>Result-Bit[1:0]=00   |

# Chapter 12 Analog-to-Digital Converter (ADC12B8CV2)

# **Revision History**

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                                                                                                                                                                                                             |

|-------------------|------------------|-------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V02.00            | 13 May 2009      | 13 May 2009       |        | Initial version copied from V01.05,<br>changed unused Bits in ATDDIEN to read logic 1                                                                                                                                                                                              |

| V02.01            | 17 Dec 2009      | 17 Dec 2009       |        | Updated Table 12-15 Analog Input Channel Select Coding -<br>description of internal channels.<br>Updated register ATDDR (left/right justified result) description<br>in section 12.3.2.12.1/12-449 and 12.3.2.12.2/12-450 and<br>added Table 12-21 to improve feature description. |

| V02.02            | 09 Feb 2010      | 09 Feb 2010       |        | Fixed typo in Table 12-9 - conversion result for 3mV and 10bit resolution                                                                                                                                                                                                          |

| V02.03            | 26 Feb 2010      | 26 Feb 2010       |        | Corrected Table 12-15 Analog Input Channel Select Coding - description of internal channels.                                                                                                                                                                                       |

| V02.04            | 14 Apr 2010      | 14 Apr 2010       |        | Corrected typos to be in-line with SoC level pin naming conventions for VDDA, VSSA, VRL and VRH.                                                                                                                                                                                   |

| V02.05            | 25 Aug 2010      | 25 Aug 2010       |        | Removed feature of conversion during STOP and general wording clean up done in Section 12.4, "Functional Description                                                                                                                                                               |

| V02.06            | 09 Sep 2010      | 09 Sep 2010       |        | Update of internal only information.                                                                                                                                                                                                                                               |

| V02.07            | 11 Feb 2011      | 11 Feb 2011       |        | Connectivity Information regarding internal channel_6 added to Table 12-15.                                                                                                                                                                                                        |

| V02.08            | 22. Jun 2012     | 22. Jun 2012      |        | Updated register wirte access information in section 12.3.2.9/12-447                                                                                                                                                                                                               |

| V02.09            | 29. Jun 2012     | 29 Jun 2012       |        | Removed IP name in block diagram Figure 12-1                                                                                                                                                                                                                                       |

| V02.10            | 02 Oct 2012      | 02 Oct 2012       |        | Added user information to avoid maybe false external trigger<br>events when enabling the external trigger mode<br>(Section 12.4.2.1, "External Trigger Input).                                                                                                                     |

# 12.1 Introduction

The ADC12B8C is a 8-channel, 12-bit, multiplexed input successive approximation analog-to-digital converter. Refer to device electrical specifications for ATD accuracy.

| ETRIGSEL | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 | External trigger source is |

|----------|----------|----------|----------|----------|----------------------------|

| 0        | 0        | 0        | 0        | 0        | AN0                        |

| 0        | 0        | 0        | 0        | 1        | AN1                        |

| 0        | 0        | 0        | 1        | 0        | AN2                        |

| 0        | 0        | 0        | 1        | 1        | AN3                        |

| 0        | 0        | 1        | 0        | 0        | AN4                        |

| 0        | 0        | 1        | 0        | 1        | AN5                        |

| 0        | 0        | 1        | 1        | 0        | AN6                        |

| 0        | 0        | 1        | 1        | 1        | AN7                        |

| 0        | 1        | 0        | 0        | 0        | AN7                        |

| 0        | 1        | 0        | 0        | 1        | AN7                        |

| 0        | 1        | 0        | 1        | 0        | AN7                        |

| 0        | 1        | 0        | 1        | 1        | AN7                        |

| 0        | 1        | 1        | 0        | 0        | AN7                        |

| 0        | 1        | 1        | 0        | 1        | AN7                        |

| 0        | 1        | 1        | 1        | 0        | AN7                        |

| 0        | 1        | 1        | 1        | 1        | AN7                        |

| 1        | 0        | 0        | 0        | 0        | ETRIG0 <sup>1</sup>        |

| 1        | 0        | 0        | 0        | 1        | ETRIG1 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 0        | ETRIG2 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 1        | ETRIG3 <sup>1</sup>        |

| 1        | 0        | 1        | Х        | Х        | Reserved                   |

| 1        | 1        | Х        | Х        | Х        | Reserved                   |

Table 12-5. External Trigger Channel Select Coding

<sup>1</sup> Only if ETRIG3-0 input option is available (see device specification), else ETRISEL is ignored, that means external trigger source is still on one of the AD channels selected by ETRIGCH3-0

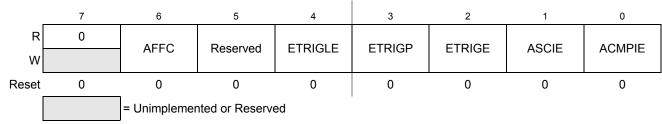

# 12.3.2.3 ATD Control Register 2 (ATDCTL2)

Writes to this register will abort current conversion sequence.

Module Base + 0x0002

Read: Anytime

Write: Anytime

Serial Peripheral Interface (S12SPIV5)

| SPPR2 | SPPR1 | SPPR0 | SPR2 | SPR1 | SPR0 | Baud Rate<br>Divisor | Baud Rate     |

|-------|-------|-------|------|------|------|----------------------|---------------|

| 1     | 1     | 0     | 0    | 0    | 1    | 28                   | 892.86 kbit/s |

| 1     | 1     | 0     | 0    | 1    | 0    | 56                   | 446.43 kbit/s |

| 1     | 1     | 0     | 0    | 1    | 1    | 112                  | 223.21 kbit/s |

| 1     | 1     | 0     | 1    | 0    | 0    | 224                  | 111.61 kbit/s |

| 1     | 1     | 0     | 1    | 0    | 1    | 448                  | 55.80 kbit/s  |

| 1     | 1     | 0     | 1    | 1    | 0    | 896                  | 27.90 kbit/s  |

| 1     | 1     | 0     | 1    | 1    | 1    | 1792                 | 13.95 kbit/s  |

| 1     | 1     | 1     | 0    | 0    | 0    | 16                   | 1.5625 Mbit/s |

| 1     | 1     | 1     | 0    | 0    | 1    | 32                   | 781.25 kbit/s |

| 1     | 1     | 1     | 0    | 1    | 0    | 64                   | 390.63 kbit/s |

| 1     | 1     | 1     | 0    | 1    | 1    | 128                  | 195.31 kbit/s |

| 1     | 1     | 1     | 1    | 0    | 0    | 256                  | 97.66 kbit/s  |

| 1     | 1     | 1     | 1    | 0    | 1    | 512                  | 48.83 kbit/s  |

| 1     | 1     | 1     | 1    | 1    | 0    | 1024                 | 24.41 kbit/s  |

| 1     | 1     | 1     | 1    | 1    | 1    | 2048                 | 12.21 kbit/s  |

Table 21-6. Example SPI Baud Rate Selection (25 MHz Bus Clock)

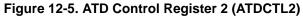

### 21.3.2.4 SPI Status Register (SPISR)

Module Base +0x0003

Figure 21-6. SPI Status Register (SPISR)

Read: Anytime

Write: Has no effect

### Table 21-7. SPISR Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIF | <ul> <li>SPIF Interrupt Flag — This bit is set after received data has been transferred into the SPI data register. For information about clearing SPIF Flag, please refer to Table 21-8.</li> <li>0 Transfer not yet complete.</li> <li>1 New data copied to SPIDR.</li> </ul> |

#### Serial Peripheral Interface (S12SPIV5)

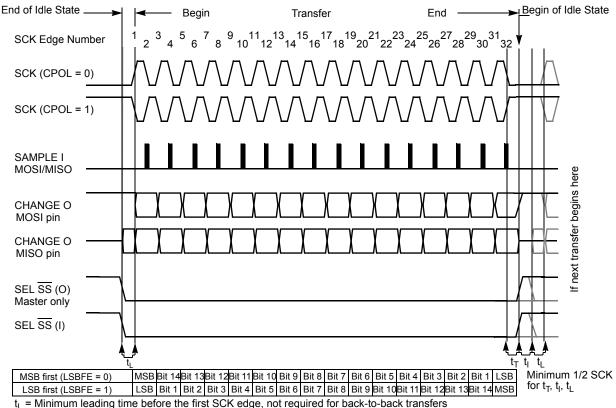

$t_{\rm T}$  = Minimum trailing time after the last SCK edge

$t_1$  = Minimum idling time between transfers (minimum  $\overline{SS}$  high time), not required for back-to-back transfers

#### Figure 21-15. SPI Clock Format 1 (CPHA = 1), with 16-Bit Transfer Width selected (XFRW = 1)

The  $\overline{SS}$  line can remain active low between successive transfers (can be tied low at all times). This format is sometimes preferred in systems having a single fixed master and a single slave that drive the MISO data line.

• Back-to-back transfers in master mode

In master mode, if a transmission has completed and new data is available in the SPI data register, this data is sent out immediately without a trailing and minimum idle time.

The SPI interrupt request flag (SPIF) is common to both the master and slave modes. SPIF gets set one half SCK cycle after the last SCK edge.

### 21.4.4 SPI Baud Rate Generation

Baud rate generation consists of a series of divider stages. Six bits in the SPI baud rate register (SPPR2, SPPR1, SPPR0, SPR2, SPR1, and SPR0) determine the divisor to the SPI module clock which results in the SPI baud rate.

The SPI clock rate is determined by the product of the value in the baud rate preselection bits (SPPR2–SPPR0) and the value in the baud rate selection bits (SPR2–SPR0). The module clock divisor equation is shown in Equation 21-3.

| Table 22-9. | Edge Detector | Circuit | Configuration |

|-------------|---------------|---------|---------------|

|-------------|---------------|---------|---------------|

| EDGnB | EDGnA | Configuration                           |

|-------|-------|-----------------------------------------|

| 1     | 1     | Capture on any edge (rising or falling) |

### 22.3.2.8 Timer Interrupt Enable Register (TIE)

Module Base + 0x000C

Figure 22-14. Timer Interrupt Enable Register (TIE)

Read: Anytime

Write: Anytime.

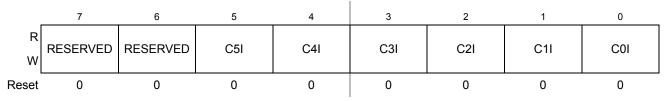

#### Table 22-10. TIE Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero

| Field          | Description                                                                                                                                                                                                                                                                                     |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5:0<br>C5I:C0I | <b>Input Capture/Output Compare "x" Interrupt Enable</b> — The bits in TIE correspond bit-for-bit with the bits in the TFLG1 status register. If cleared, the corresponding flag is disabled from causing a hardware interrupt. If set, the corresponding flag is enabled to cause a interrupt. |  |

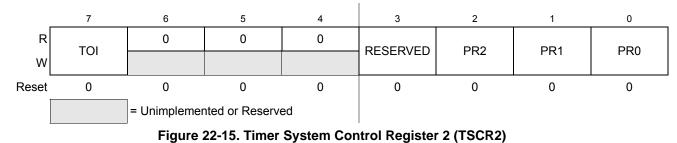

### 22.3.2.9 Timer System Control Register 2 (TSCR2)

Module Base + 0x000D

Read: Anytime

Write: Anytime.

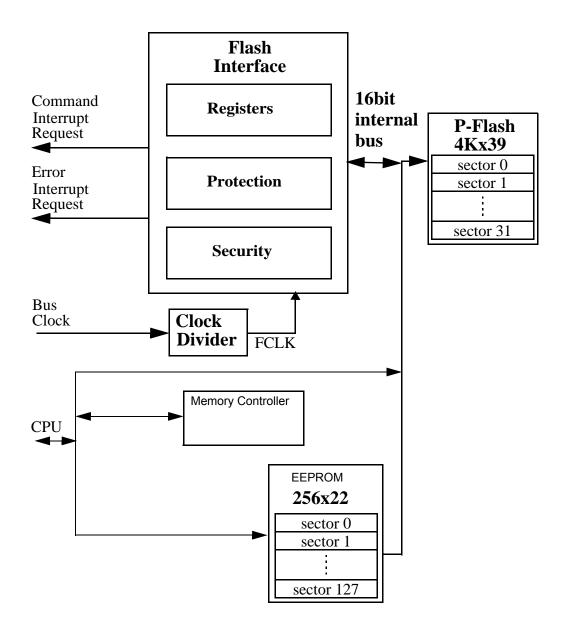

Figure 24-1. FTMRG16K1 Block Diagram

# 24.2 External Signal Description

The Flash module contains no signals that connect off-chip.

the command's execution by writing a 1 to the CCIF bit in the FSTAT register (a 1 written by the user clears the CCIF command completion flag to 0). When the user clears the CCIF bit in the FSTAT register all FCCOB parameter fields are locked and cannot be changed by the user until the command completes (as evidenced by the Memory Controller returning CCIF to 1). Some commands return information to the FCCOB register array.

The generic format for the FCCOB parameter fields in NVM command mode is shown in Table 24-22. The return values are available for reading after the CCIF flag in the FSTAT register has been returned to 1 by the Memory Controller. Writes to the unimplemented parameter fields (CCOBIX = 110 and CCOBIX = 111) are ignored with reads from these fields returning 0x0000.

Table 24-22 shows the generic Flash command format. The high byte of the first word in the CCOB array contains the command code, followed by the parameters for this specific Flash command. For details on the FCCOB settings required by each command, see the Flash command descriptions in Section 24.4.6.

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|------|-------------------------------------------|

| 000         | HI   | FCMD[7:0] defining Flash command          |

| 000         | LO   | 6'h0, Global address [17:16]              |

| 001         | HI   | Global address [15:8]                     |

| 001         | LO   | Global address [7:0]                      |

| 010         | HI   | Data 0 [15:8]                             |

| 010         | LO   | Data 0 [7:0]                              |

| 011         | HI   | Data 1 [15:8]                             |

|             | LO   | Data 1 [7:0]                              |

| 100         | HI   | Data 2 [15:8]                             |

| 100         | LO   | Data 2 [7:0]                              |

| 101         | HI   | Data 3 [15:8]                             |

|             | LO   | Data 3 [7:0]                              |

Table 24-22. FCCOB - NVM Command Mode (Typical Usage)

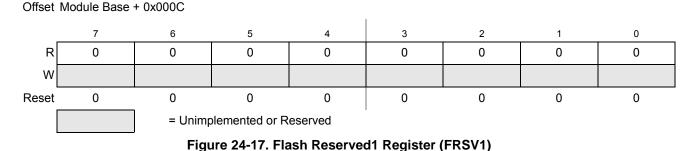

# 24.3.2.12 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

All bits in the FRSV1 register read 0 and are not writable.

# Chapter 28 96 KByte Flash Module (S12FTMRG96K1V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected                                                                          | Description of Changes                                                                            |

|--------------------|------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| V01.04             | 17 Jun 2010      | 28.4.6.1/28-100<br>2<br>28.4.6.2/28-100<br>3<br>28.4.6.3/28-100<br>4<br>28.4.6.14/28-10<br>13 | Clarify Erase Verify Commands Descriptions related to the bits MGSTAT[1:0] of the register FSTAT. |

| V01.05             | 20 aug 2010      | 28.4.6.2/28-100<br>3<br>28.4.6.12/28-10<br>10<br>28.4.6.13/28-10<br>12                        | Updated description of the commands RD1BLK, MLOADU and MLOADF                                     |

| Rev.1.27           | 31 Jan 2011      | 28.3.2.9/28-985                                                                               | Updated description of protection on Section 28.3.2.9                                             |

### Table 28-1. Revision History

# 28.1 Introduction

The FTMRG96K1 module implements the following:

- 96Kbytes of P-Flash (Program Flash) memory

- 3 Kbytes of EEPROM memory

The Flash memory is ideal for single-supply applications allowing for field reprogramming without requiring external high voltage sources for program or erase operations. The Flash module includes a memory controller that executes commands to modify Flash memory contents. The user interface to the memory controller consists of the indexed Flash Common Command Object (FCCOB) register which is written to with the command, global address, data, and any required command parameters. The memory controller must complete the execution of a command before the FCCOB register can be written to with a new command.

### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

### CAUTION

Field margin levels must only be used during verify of the initial factory programming.

### NOTE

Field margin levels can be used to check that Flash memory contents have adequate margin for data retention at the normal level setting. If unexpected results are encountered when checking Flash memory contents at field margin levels, the Flash memory contents should be erased and reprogrammed.

### 30.4.6.14 Erase Verify EEPROM Section Command

The Erase Verify EEPROM Section command will verify that a section of code in the EEPROM is erased. The Erase Verify EEPROM Section command defines the starting point of the data to be verified and the number of words.

| CCOBIX[2:0] | FCCOB Parameters                                       |                                                           |  |

|-------------|--------------------------------------------------------|-----------------------------------------------------------|--|

| 000         | 0x10                                                   | Global address [17:16] to<br>identify the EEPROM<br>block |  |

| 001         | Global address [15:0] of the first word to be verified |                                                           |  |

| 010         | Number of words to be verified                         |                                                           |  |

Table 30-60. Erase Verify EEPROM Section Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Verify EEPROM Section command, the Memory Controller will verify the selected section of EEPROM memory is erased. The CCIF flag will set after the Erase Verify EEPROM Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

| Table 30-61. Erase Verify EEPROM | Section Command Error Handling |

|----------------------------------|--------------------------------|

|                                  |                                |

| Register | Error Bit | Error Condition                                                                                   |  |

|----------|-----------|---------------------------------------------------------------------------------------------------|--|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                                                       |  |

|          |           | Set if command not available in current mode (see Table 30-27)                                    |  |

|          | ACCERR    | Set if an invalid global address [17:0] is supplied                                               |  |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)                            |  |

| FSTAT    |           | Set if the requested section breaches the end of the EEPROM block                                 |  |

|          | FPVIOL    | None                                                                                              |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |  |

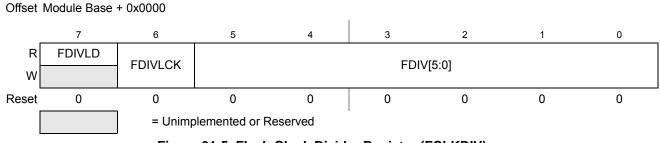

Figure 31-5. Flash Clock Divider Register (FCLKDIV)

All bits in the FCLKDIV register are readable, bit 7 is not writable, bit 6 is write-once-hi and controls the writability of the FDIV field in normal mode. In special mode, bits 6-0 are writable any number of times but bit 7 remains unwritable.

### CAUTION

The FCLKDIV register should never be written while a Flash command is executing (CCIF=0).

| Field            | Description                                                                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written since the last reset<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                   |

| 6<br>FDIVLCK     | <ul> <li>Clock Divider Locked</li> <li>FDIV field is open for writing</li> <li>FDIV value is locked and cannot be changed. Once the lock bit is set high, only reset can clear this bit and restore writability to the FDIV field in normal mode.</li> </ul>                                                                       |

| 5–0<br>FDIV[5:0] | <b>Clock Divider Bits</b> — FDIV[5:0] must be set to effectively divide BUSCLK down to 1 MHz to control timed events during Flash program and erase algorithms. Table 31-8 shows recommended values for FDIV[5:0] based on the BUSCLK frequency. Please refer to Section 31.4.4, "Flash Command Operations," for more information. |

| CCOBIX[2:0] | FCCOB Parameters                                                                                               |                                                    |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| 000 0x12    |                                                                                                                | Global address [17:16] to identify<br>EEPROM block |  |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 31.1.2.2 for EEPROM sector size. |                                                    |  |  |  |

Table 31-64. Erase EEPROM Sector Command FCCOB Requirements

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |  |

|          |           | Set if command not available in current mode (see Table 31-27)                      |  |  |  |

|          |           | Set if an invalid global address [17:0] is suppliedsee Table 31-3)                  |  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |

Table 31-65. Erase EEPROM Sector Command Error Handling

# 31.4.7 Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Table 31-66 | . Flash | Interrupt Sources | 5 |

|-------------|---------|-------------------|---|

|-------------|---------|-------------------|---|

| Interrupt Source                   | Interrupt Flag              | Local Enable                | Global (CCR)<br>Mask |  |

|------------------------------------|-----------------------------|-----------------------------|----------------------|--|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | l Bit                |  |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register) | DFDIE<br>(FERCNFG register) | l Bit                |  |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | l Bit                |  |

**Electrical Characteristics**

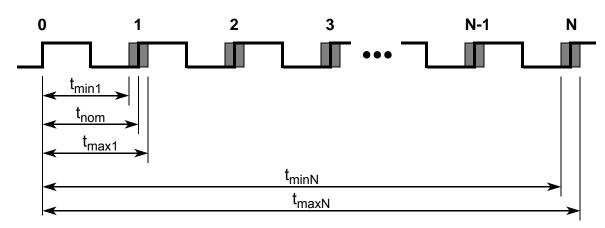

Figure A-4. Jitter Definitions

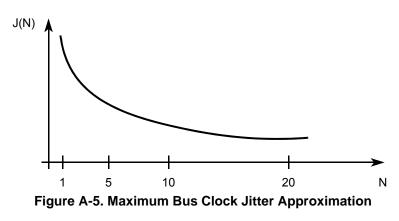

The relative deviation of  $t_{nom}$  is at its maximum for one clock period, and decreases towards zero for larger number of clock periods (N).

Defining the jitter as:

$$J(N) = max\left(\left|1 - \frac{t_{max}(N)}{N \cdot t_{nom}}\right|, \left|1 - \frac{t_{min}(N)}{N \cdot t_{nom}}\right|\right)$$

For N < 100, the following equation is a good fit for the maximum jitter:

$$J(N) = \frac{j_1}{\sqrt{N}}$$

NOTE

On timers and serial modules a prescaler will eliminate the effect of the jitter to a large extent.

**Electrical Characteristics**

# A.14 MSCAN

| Conditions are shown in Table A-4 unless otherwise noted |   |                                      |                  |     |     |     |      |

|----------------------------------------------------------|---|--------------------------------------|------------------|-----|-----|-----|------|

| Num                                                      | С | Rating                               | Symbol           | Min | Тур | Max | Unit |

| 1                                                        | Ρ | MSCAN wakeup dominant pulse filtered | t <sub>WUP</sub> | _   | —   | 1.5 | μS   |

| 2                                                        | Ρ | MSCAN wakeup dominant pulse pass     | t <sub>WUP</sub> | 5   |     |     | μS   |