Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                 |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 40                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12gn32f0mlf |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Port Integration Module (S12GPIMV1)

| Global Address<br>Register Name |                             | Bit 7   | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0   |

|---------------------------------|-----------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| 0x026C<br>PERJ                  | R<br>W                      | PERJ7   | PERJ6   | PERJ5   | PERJ4   | PERJ3   | PERJ2   | PERJ1   | PERJ0   |

| 0x026D<br>PPSJ                  | R<br>W                      | PPSJ7   | PPSJ6   | PPSJ5   | PPSJ4   | PPSJ3   | PPSJ2   | PPSJ1   | PPSJ0   |

| 0x026E<br>PIEJ                  | R<br>W                      | PIEJ7   | PIEJ6   | PIEJ5   | PIEJ4   | PIEJ3   | PIEJ2   | PIEJ1   | PIEJ0   |

| 0x026F<br>PIFJ                  | R<br>W                      | PIFJ7   | PIFJ6   | PIFJ5   | PIFJ4   | PIFJ3   | PIFJ2   | PIFJ1   | PIFJ0   |

| 0x0270<br>PT0AD                 | R<br>W                      | PT0AD7  | PT0AD6  | PT0AD5  | PT0AD4  | PT0AD3  | PT0AD2  | PT0AD1  | PT0AD0  |

| 0x0271<br>PT1AD                 | R<br>W                      | PT1AD7  | PT1AD6  | PT1AD5  | PT1AD4  | PT1AD3  | PT1AD2  | PT1AD1  | PT1AD0  |

| 0x0272<br>PTI0AD                | R<br>W                      | PTI0AD7 | PTI0AD6 | PTI0AD5 | PTI0AD4 | PTI0AD3 | PTI0AD2 | PTI0AD1 | PTI0AD0 |

| 0x0273<br>PTI1AD                | R<br>W                      | PTI1AD7 | PTI1AD6 | PTI1AD5 | PTI1AD4 | PTI1AD3 | PTI1AD2 | PTI1AD1 | PTI1AD0 |

| 0x0274<br>DDR0AD                | R<br>W                      | DDR0AD7 | DDR0AD6 | DDR0AD5 | DDR0AD4 | DDR0AD3 | DDR0AD2 | DDR0AD1 | DDR0AD0 |

| 0x0275<br>DDR1AD                | R<br>W                      | DDR1AD7 | DDR1AD6 | DDR1AD5 | DDR1AD4 | DDR1AD3 | DDR1AD2 | DDR1AD1 | DDR1AD0 |

| 0x0276<br>Reserved              | R<br>W                      | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| 0x0277<br>Reserved              | R<br>W                      | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| 0x0278<br>PER0AD                | R<br>W                      | PER0AD7 | PER0AD6 | PER0AD5 | PER0AD4 | PER0AD3 | PER0AD2 | PER0AD1 | PER0AD0 |

| 0x0279<br>PER1AD                | R<br>W                      | PER1AD7 | PER1AD6 | PER1AD5 | PER1AD4 | PER1AD3 | PER1AD2 | PER1AD1 | PER1AD0 |

| 0x027A<br>PPS0AD                | R<br>W                      | PPS0AD7 | PPS0AD6 | PPS0AD5 | PPS0AD4 | PPS0AD3 | PPS0AD2 | PPS0AD1 | PPS0AD0 |

|                                 | = Unimplemented or Reserved |         |         |         |         |         |         |         |         |

### Table 2-20. Block Register Map (G2) (continued)

| Field        | Description                                                                                                                                                                                                                                      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PRR0P3  | <b>Pin Routing Register PWM3</b> —Select alternative routing of PWM3 output, ETRIG3 input<br>This bit programs the routing of the PWM3 channel and the ETRIG3 input to a different external pin in 20 TSSOP.<br>See Table 2-47 for more details. |

| 6<br>PRR0P2  | <b>Pin Routing Register PWM2</b> —Select alternative routing of PWM2 output, ETRIG2 input<br>This bit programs the routing of the PWM2 channel and the ETRIG2 input to a different external pin in 20 TSSOP.<br>See Table 2-48 for more details. |

| 5<br>PRR0T31 | <b>Pin Routing Register IOC3</b> —Select alternative routing of IOC3 output and input<br>Those two bits program the routing of the timer IOC3 channel to different external pins in 20 TSSOP.                                                    |

| 4<br>PRR0T30 | See Table 2-49 for more details.                                                                                                                                                                                                                 |

| 3<br>PRR0T21 | <b>Pin Routing Register IOC2</b> —Select alternative routing of IOC2 output and input<br>Those two bits program the routing of the timer IOC2 channel to different external pins in 20 TSSOP.                                                    |

| 2<br>PRR0T20 | See Table 2-50 for more details.                                                                                                                                                                                                                 |

| 1<br>PRR0S1  | <b>Pin Routing Register Serial Module</b> —Select alternative routing of SCI0 pins<br>Those bits program the routing of the SCI0 module pins to different external pins in 20 TSSOP.                                                             |

| 0<br>PRR0S0  | See Table 2-51 for more details.                                                                                                                                                                                                                 |

### Table 2-46. PRR0 Register Field Descriptions

### Table 2-47. PWM3/ETRIG3 Routing Options

| PRR0P3 | PWM3/ETRIG3 Associated Pin |  |  |

|--------|----------------------------|--|--|

| 0      | PS7 - PWM3, ETRIG3         |  |  |

| 1      | PAD5 - PWM3, ETRIG3        |  |  |

### Table 2-48. PWM2/ETRIG2 Routing Options

| PRR0P2 | PWM2/ETRIG2 Associated Pin |  |  |  |

|--------|----------------------------|--|--|--|

| 0      | PS4 - PWM2, ETRIG2         |  |  |  |

| 1      | PAD4 - PWM2, ETRIG2        |  |  |  |

#### Table 2-49. IOC3 Routing Options

| PRR0T31 | PRR0T30 | IOC3 Associated Pin |

|---------|---------|---------------------|

| 0       | 0       | PS6 - IOC3          |

| 0       | 1       | PE1 - IOC3          |

| 1       | 0       | PAD5 - IOC3         |

| 1       | 1       | Reserved            |

| ETRIGSEL | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 | External trigger source is |

|----------|----------|----------|----------|----------|----------------------------|

| 0        | 0        | 0        | 0        | 0        | AN0                        |

| 0        | 0        | 0        | 0        | 1        | AN1                        |

| 0        | 0        | 0        | 1        | 0        | AN2                        |

| 0        | 0        | 0        | 1        | 1        | AN3                        |

| 0        | 0        | 1        | 0        | 0        | AN4                        |

| 0        | 0        | 1        | 0        | 1        | AN5                        |

| 0        | 0        | 1        | 1        | 0        | AN6                        |

| 0        | 0        | 1        | 1        | 1        | AN7                        |

| 0        | 1        | 0        | 0        | 0        | AN7                        |

| 0        | 1        | 0        | 0        | 1        | AN7                        |

| 0        | 1        | 0        | 1        | 0        | AN7                        |

| 0        | 1        | 0        | 1        | 1        | AN7                        |

| 0        | 1        | 1        | 0        | 0        | AN7                        |

| 0        | 1        | 1        | 0        | 1        | AN7                        |

| 0        | 1        | 1        | 1        | 0        | AN7                        |

| 0        | 1        | 1        | 1        | 1        | AN7                        |

| 1        | 0        | 0        | 0        | 0        | ETRIG0 <sup>1</sup>        |

| 1        | 0        | 0        | 0        | 1        | ETRIG1 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 0        | ETRIG2 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 1        | ETRIG3 <sup>1</sup>        |

| 1        | 0        | 1        | Х        | Х        | Reserved                   |

| 1        | 1        | Х        | Х        | Х        | Reserved                   |

Table 12-5. External Trigger Channel Select Coding

<sup>1</sup> Only if ETRIG3-0 input option is available (see device specification), else ETRISEL is ignored, that means external trigger source is still on one of the AD channels selected by ETRIGCH3-0

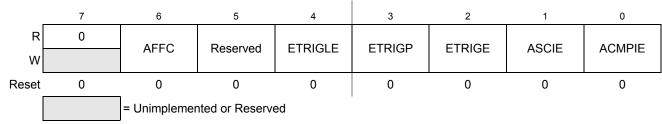

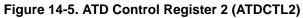

# 12.3.2.3 ATD Control Register 2 (ATDCTL2)

Writes to this register will abort current conversion sequence.

Module Base + 0x0002

Read: Anytime

Write: Anytime

#### Analog-to-Digital Converter (ADC10B12CV2)

<sup>1</sup>If only AN0 should be converted use MULT=0.

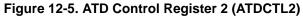

# 13.3.2.2 ATD Control Register 1 (ATDCTL1)

Writes to this register will abort current conversion sequence.

Module Base + 0x0001

Figure 13-4. ATD Control Register 1 (ATDCTL1)

Read: Anytime

Write: Anytime

| Table 13-3. | ATDCTL1 | Field | Descriptions |  |

|-------------|---------|-------|--------------|--|

|             |         |       |              |  |

| Field               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ETRIGSEL       | <b>External Trigger Source Select</b> — This bit selects the external trigger source to be either one of the AD channels or one of the ETRIG3-0 inputs. See device specification for availability and connectivity of ETRIG3-0 inputs. If a particular ETRIG3-0 input option is not available, writing a 1 to ETRISEL only sets the bit but has no effect, this means that one of the AD channels (selected by ETRIGCH3-0) is configured as the source for external trigger. The coding is summarized in Table 13-5. |

| 6–5<br>SRES[1:0]    | <b>A/D Resolution Select</b> — These bits select the resolution of A/D conversion results. See Table 13-4 for coding.                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>SMP_DIS        | <ul> <li>Discharge Before Sampling Bit</li> <li>No discharge before sampling.</li> <li>The internal sample capacitor is discharged before sampling the channel. This adds 2 ATD clock cycles to the sampling time. This can help to detect an open circuit instead of measuring the previous sampled channel.</li> </ul>                                                                                                                                                                                             |

| 3–0<br>ETRIGCH[3:0] | <b>External Trigger Channel Select</b> — These bits select one of the AD channels or one of the ETRIG3-0 inputs as source for the external trigger. The coding is summarized in Table 13-5.                                                                                                                                                                                                                                                                                                                          |

| Table | 13-4. | A/D | Resolution | Coding |

|-------|-------|-----|------------|--------|

|-------|-------|-----|------------|--------|

| SRES1 | SRES0 | A/D Resolution |

|-------|-------|----------------|

| 0     | 0     | 8-bit data     |

| 0     | 1     | 10-bit data    |

| 1     | 0     | Reserved       |

| 1     | 1     | Reserved       |

| ETRIGSEL | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 | External trigger source is |

|----------|----------|----------|----------|----------|----------------------------|

| 0        | 0        | 0        | 0        | 0        | AN0                        |

| 0        | 0        | 0        | 0        | 1        | AN1                        |

| 0        | 0        | 0        | 1        | 0        | AN2                        |

| 0        | 0        | 0        | 1        | 1        | AN3                        |

| 0        | 0        | 1        | 0        | 0        | AN4                        |

| 0        | 0        | 1        | 0        | 1        | AN5                        |

| 0        | 0        | 1        | 1        | 0        | AN6                        |

| 0        | 0        | 1        | 1        | 1        | AN7                        |

| 0        | 1        | 0        | 0        | 0        | AN8                        |

| 0        | 1        | 0        | 0        | 1        | AN9                        |

| 0        | 1        | 0        | 1        | 0        | AN10                       |

| 0        | 1        | 0        | 1        | 1        | AN11                       |

| 0        | 1        | 1        | 0        | 0        | AN11                       |

| 0        | 1        | 1        | 0        | 1        | AN11                       |

| 0        | 1        | 1        | 1        | 0        | AN11                       |

| 0        | 1        | 1        | 1        | 1        | AN11                       |

| 1        | 0        | 0        | 0        | 0        | ETRIG0 <sup>1</sup>        |

| 1        | 0        | 0        | 0        | 1        | ETRIG1 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 0        | ETRIG2 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 1        | ETRIG3 <sup>1</sup>        |

| 1        | 0        | 1        | Х        | Х        | Reserved                   |

| 1        | 1        | Х        | Х        | Х        | Reserved                   |

Table 14-5. External Trigger Channel Select Coding

<sup>1</sup> Only if ETRIG3-0 input option is available (see device specification), else ETRISEL is ignored, that means external trigger source is still on one of the AD channels selected by ETRIGCH3-0

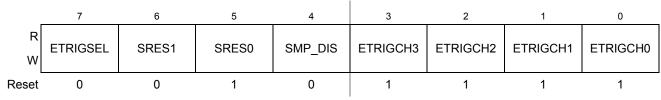

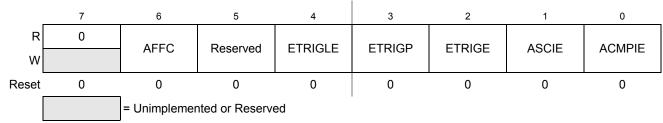

# 14.3.2.3 ATD Control Register 2 (ATDCTL2)

Writes to this register will abort current conversion sequence.

Module Base + 0x0002

Read: Anytime

Write: Anytime

#### Analog-to-Digital Converter (ADC10B16CV2)

edge or level sensitive with polarity control. Table 15-23 gives a brief description of the different combinations of control bits and their effect on the external trigger function.

In order to avoid maybe false trigger events please enable the external digital input via ATDDIEN register first and in the following enable the external trigger mode by bit ETRIGE.

| ETRIGLE | ETRIGP | ETRIGE | SCAN | Description                                                                                       |  |

|---------|--------|--------|------|---------------------------------------------------------------------------------------------------|--|

| X       | х      | 0      | 0    | Ignores external trigger. Performs one conversion sequence and stops.                             |  |

| X       | х      | 0      | 1    | Ignores external trigger. Performs continuous conversion sequences.                               |  |

| 0       | 0      | 1      | х    | Trigger falling edge sensitive. Performs one conversion sequence per trigger.                     |  |

| 0       | 1      | 1      | х    | Trigger rising edge sensitive. Performs one conversion sequence per trigger.                      |  |

| 1       | 0      | 1      | Х    | Trigger low level sensitive. Performs<br>continuous conversions while trigger level<br>is active. |  |

| 1       | 1      | 1      | х    | Trigger high level sensitive. Performs continuous conversions while trigger level is active.      |  |

Table 15-23. External Trigger Control Bits

In either level or edge sensitive mode, the first conversion begins when the trigger is received.

Once ETRIGE is enabled a conversion must be triggered externally after writing to ATDCTL5 register.

During a conversion in edge sensitive mode, if additional trigger events are detected the overrun error flag ETORF is set.

If level sensitive mode is active and the external trigger de-asserts and later asserts again during a conversion sequence, this does not constitute an overrun. Therefore, the flag is not set. If the trigger is left active in level sensitive mode when a sequence is about to complete, another sequence will be triggered immediately.

## 15.4.2.2 General-Purpose Digital Port Operation

Each ATD input pin can be switched between analog or digital input functionality. An analog multiplexer makes each ATD input pin selected as analog input available to the A/D converter.

The pad of the ATD input pin is always connected to the analog input channel of the analog mulitplexer.

Each pad input signal is buffered to the digital port register.

This buffer can be turned on or off with the ATDDIEN register for each ATD input pin. This is important so that the buffer does not draw excess current when an ATD input pin is selected as analog input to the ADC10B16C.

# 16.5 Resets

At reset the ADC12B16C is in a power down state. The reset state of each individual bit is listed within the Register Description section (see Section 16.3.2, "Register Descriptions") which details the registers and their bit-field.

# 16.6 Interrupts

The interrupts requested by the ADC12B16C are listed in Table 16-24. Refer to MCU specification for related vector address and priority.

| Interrupt Source            | CCR<br>Mask | Local Enable      |

|-----------------------------|-------------|-------------------|

| Sequence Complete Interrupt | I bit       | ASCIE in ATDCTL2  |

| Compare Interrupt           | l bit       | ACMPIE in ATDCTL2 |

### Table 16-24. ATD Interrupt Vectors

See Section 16.3.2, "Register Descriptions" for further details.

## NOTE

In single-wire operation data from the TXD pin is inverted if RXPOL is set.

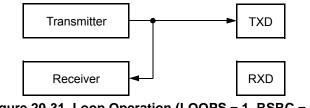

# 20.4.8 Loop Operation

In loop operation the transmitter output goes to the receiver input. The RXD pin is disconnected from the SCI.

Figure 20-31. Loop Operation (LOOPS = 1, RSRC = 0)

Enable loop operation by setting the LOOPS bit and clearing the RSRC bit in SCI control register 1 (SCICR1). Setting the LOOPS bit disables the path from the RXD pin to the receiver. Clearing the RSRC bit connects the transmitter output to the receiver input. Both the transmitter and receiver must be enabled (TE = 1 and RE = 1).

## NOTE

In loop operation data from the transmitter is not recognized by the receiver if RXPOL and TXPOL are not the same.

# 20.5 Initialization/Application Information

# 20.5.1 Reset Initialization

See Section 20.3.2, "Register Descriptions".

# 20.5.2 Modes of Operation

# 20.5.2.1 Run Mode

Normal mode of operation.

To initialize a SCI transmission, see Section 20.4.5.2, "Character Transmission".

## 20.5.2.2 Wait Mode

SCI operation in wait mode depends on the state of the SCISWAI bit in the SCI control register 1 (SCICR1).

- If SCISWAI is clear, the SCI operates normally when the CPU is in wait mode.

- If SCISWAI is set, SCI clock generation ceases and the SCI module enters a power-conservation state when the CPU is in wait mode. Setting SCISWAI does not affect the state of the receiver enable bit, RE, or the transmitter enable bit, TE.

| PAMOD | PEDGE | Pin Action                                   |

|-------|-------|----------------------------------------------|

| 0     | 0     | Falling edge                                 |

| 0     | 1     | Rising edge                                  |

| 1     | 0     | Div. by 64 clock enabled with pin high level |

| 1     | 1     | Div. by 64 clock enabled with pin low level  |

### Table 23-19. Pin Action

### NOTE

If the timer is not active (TEN = 0 in TSCR), there is no divide-by-64 because the  $\div$ 64 clock is generated by the timer prescaler.

Table 23-20. Timer Clock Selection

| CLK1 | CLK0 | Timer Clock                                      |

|------|------|--------------------------------------------------|

| 0    | 0    | Use timer prescaler clock as timer counter clock |

| 0    | 1    | Use PACLK as input to timer counter clock        |

| 1    | 0    | Use PACLK/256 as timer counter clock frequency   |

| 1    | 1    | Use PACLK/65536 as timer counter clock frequency |

For the description of PACLK please refer Figure 23-30.

If the pulse accumulator is disabled (PAEN = 0), the prescaler clock from the timer is always used as an input clock to the timer counter. The change from one selected clock to the other happens immediately after these bits are written.

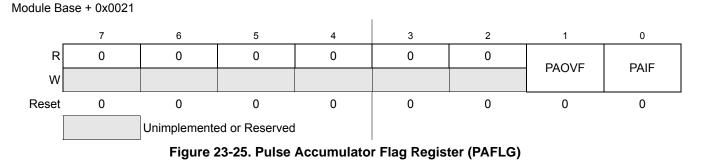

# 23.3.2.16 Pulse Accumulator Flag Register (PAFLG)

1 .

### Read: Anytime

### Write: Anytime

When the TFFCA bit in the TSCR register is set, any access to the PACNT register will clear all the flags in the PAFLG register. Timer module or Pulse Accumulator must stay enabled (TEN=1 or PAEN=1) while clearing these bits.

#### 32 KByte Flash Module (S12FTMRG32K1V1)

| CCOBIX[2:0] | FCCOB Parameters                                  |                                                   |  |

|-------------|---------------------------------------------------|---------------------------------------------------|--|

| 000         | 0x09                                              | Global address [17:16] to<br>identify Flash block |  |

| 001         | Global address [15:0] in Flash block to be erased |                                                   |  |

Table 25-46. Erase Flash Block Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Flash Block command, the Memory Controller will erase the selected Flash block and verify that it is erased. The CCIF flag will set after the Erase Flash Block operation has completed.

| Register | Error Bit                                                                                                           | Error Condition                                                                                        |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

|          | Set if command not available in current mod           ACCERR         Set if an invalid global address [17:16] is su | Set if CCOBIX[2:0] != 001 at command launch                                                            |  |  |

|          |                                                                                                                     | Set if command not available in current mode (see Table 25-27)                                         |  |  |

|          |                                                                                                                     | Set if an invalid global address [17:16] is supplied                                                   |  |  |

| FSTAT    |                                                                                                                     | Set if the supplied P-Flash address is not phrase-aligned or if the EEPROM address is not word-aligned |  |  |

|          | FPVIOL                                                                                                              | Set if an area of the selected Flash block is protected                                                |  |  |

|          | MGSTAT1                                                                                                             | Set if any errors have been encountered during the verify operation                                    |  |  |

|          | MGSTAT0                                                                                                             | Set if any non-correctable errors have been encountered during the verify operation                    |  |  |

Table 25-47. Erase Flash Block Command Error Handling

## 25.4.6.9 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

Table 25-48. Erase P-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                         |                                                                  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| 000         | 0x0A                                                                                                                     | Global address [17:16] to identify<br>P-Flash block to be erased |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 25.1.2.1 for the P-Flash sector size. |                                                                  |  |

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

48 KByte Flash Module (S12FTMRG48K1V1)

## 26.4.6.2 Erase Verify Block Command

The Erase Verify Block command allows the user to verify that an entire P-Flash or EEPROM block has been erased. The FCCOB FlashBlockSelectionCode[1:0] bits determine which block must be verified.

| Table 26-33 | . Erase Verif | y Block Command | d FCCOB Requirements |

|-------------|---------------|-----------------|----------------------|

|-------------|---------------|-----------------|----------------------|

| CCOBIX[2:0] | FCCOB Parameters |                                                         |  |

|-------------|------------------|---------------------------------------------------------|--|

| 000         | 0x02             | Flash block<br>selection code [1:0]. See<br>Table 26-34 |  |

### Table 26-34. Flash block selection code description

| Selection code[1:0] | Flash block to be verified |  |

|---------------------|----------------------------|--|

| 00                  | EEPROM                     |  |

| 01                  | Invalid (ACCERR)           |  |

| 10                  | Invalid (ACCERR)           |  |

| 11                  | P-Flash                    |  |

Upon clearing CCIF to launch the Erase Verify Block command, the Memory Controller will verify that the selected P-Flash or EEPROM block is erased. The CCIF flag will set after the Erase Verify Block operation has completed. If the block is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 26-35. Erase Verify Block Command Error Handling

| Register | Error Bit | Error Condition                                                                                   |  |

|----------|-----------|---------------------------------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                       |  |

|          |           | Set if an invalid FlashBlockSelectionCode[1:0] is supplied                                        |  |

| FSTAT    | FPVIOL    | None                                                                                              |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed                  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |  |

## 26.4.6.3 Erase Verify P-Flash Section Command

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases.

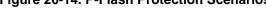

## 26.4.7 Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Interrupt Source                   | Interrupt Flag              | Local Enable                | Global (CCR)<br>Mask |

|------------------------------------|-----------------------------|-----------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | l Bit                |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register) | DFDIE<br>(FERCNFG register) | l Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | l Bit                |

| Table | 26-66. | Flash | Interrupt | Sources |

|-------|--------|-------|-----------|---------|

|-------|--------|-------|-----------|---------|

### NOTE

Vector addresses and their relative interrupt priority are determined at the MCU level.

## 26.4.7.1 Description of Flash Interrupt Operation

The Flash module uses the CCIF flag in combination with the CCIE interrupt enable bit to generate the Flash command interrupt request. The Flash module uses the DFDIF and SFDIF flags in combination with the DFDIE and SFDIE interrupt enable bits to generate the Flash error interrupt request. For a detailed description of the register bits involved, refer to Section 26.3.2.5, "Flash Configuration Register (FCNFG)", Section 26.3.2.6, "Flash Error Configuration Register (FERCNFG)", Section 26.3.2.7, "Flash Status Register (FSTAT)", and Section 26.3.2.8, "Flash Error Status Register (FERSTAT)".

The logic used for generating the Flash module interrupts is shown in Figure 26-27.

Figure 26-27. Flash Module Interrupts Implementation

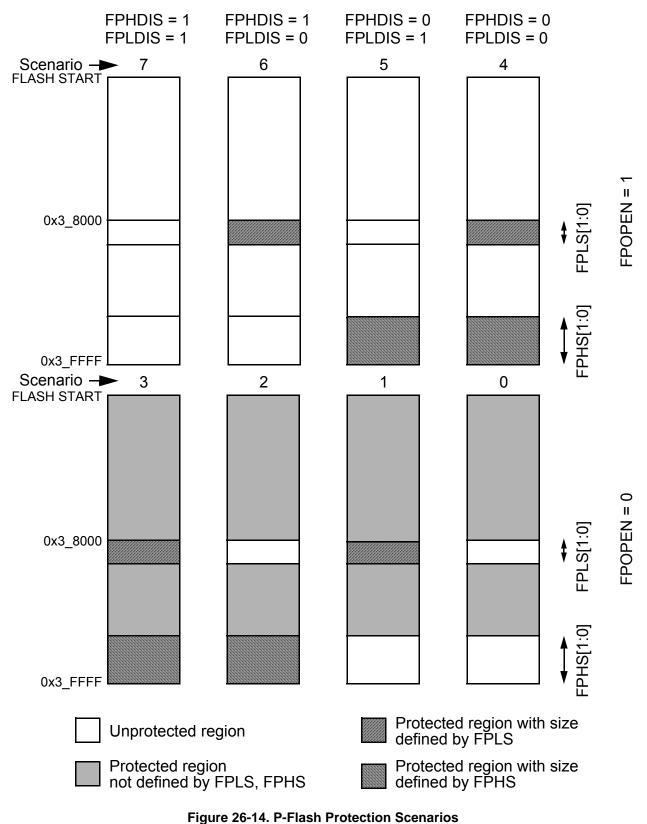

- Fast sector erase and phrase program operation

- Ability to read the P-Flash memory while programming a word in the EEPROM memory

- Flexible protection scheme to prevent accidental program or erase of P-Flash memory

## 27.1.2.2 EEPROM Features

- 2 Kbytes of EEPROM memory composed of one 2 Kbyte Flash block divided into 512 sectors of 4 bytes

- Single bit fault correction and double bit fault detection within a word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and word program operation

- Protection scheme to prevent accidental program or erase of EEPROM memory

- Ability to program up to four words in a burst sequence

## 27.1.2.3 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

## 27.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 27-1.

## CAUTION

The FCLKDIV register should never be written while a Flash command is executing (CCIF=0).

| Field            | Description                                                                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written since the last reset<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                   |

| 6<br>FDIVLCK     | <ul> <li>Clock Divider Locked</li> <li>FDIV field is open for writing</li> <li>FDIV value is locked and cannot be changed. Once the lock bit is set high, only reset can clear this bit and restore writability to the FDIV field in normal mode.</li> </ul>                                                                       |

| 5–0<br>FDIV[5:0] | <b>Clock Divider Bits</b> — FDIV[5:0] must be set to effectively divide BUSCLK down to 1 MHz to control timed events during Flash program and erase algorithms. Table 28-8 shows recommended values for FDIV[5:0] based on the BUSCLK frequency. Please refer to Section 28.4.4, "Flash Command Operations," for more information. |

| BUSCLK Frequency<br>(MHz) |                  | FDIV[5:0] |                  | Frequency<br>IHz) | FDIV[5:0] |

|---------------------------|------------------|-----------|------------------|-------------------|-----------|

| MIN <sup>1</sup>          | MAX <sup>2</sup> |           | MIN <sup>1</sup> | MAX <sup>2</sup>  |           |

| 1.0                       | 1.6              | 0x00      | 16.6             | 17.6              | 0x10      |

| 1.6                       | 2.6              | 0x01      | 17.6             | 18.6              | 0x11      |

| 2.6                       | 3.6              | 0x02      | 18.6             | 19.6              | 0x12      |

| 3.6                       | 4.6              | 0x03      | 19.6             | 20.6              | 0x13      |

| 4.6                       | 5.6              | 0x04      | 20.6             | 21.6              | 0x14      |

| 5.6                       | 6.6              | 0x05      | 21.6             | 22.6              | 0x15      |

| 6.6                       | 7.6              | 0x06      | 22.6             | 23.6              | 0x16      |

| 7.6                       | 8.6              | 0x07      | 23.6             | 24.6              | 0x17      |

| 8.6                       | 9.6              | 0x08      | 24.6             | 25.6              | 0x18      |

| 9.6                       | 10.6             | 0x09      |                  |                   | ·         |

| 10.6                      | 11.6             | 0x0A      |                  |                   |           |

| 11.6                      | 12.6             | 0x0B      |                  |                   |           |

| 12.6                      | 13.6             | 0x0C      |                  |                   |           |

| 13.6                      | 14.6             | 0x0D      |                  |                   |           |

| 14.6                      | 15.6             | 0x0E      |                  |                   |           |

| 15.6                      | 16.6             | 0x0F      |                  |                   |           |

#### Table 28-8. FDIV values for various BUSCLK Frequencies

<sup>1</sup> BUSCLK is Greater Than this value.

<sup>2</sup> BUSCLK is Less Than or Equal to this value.

<sup>1</sup> Global address [2:0] must be 000

Upon clearing CCIF to launch the Program P-Flash command, the Memory Controller will program the data words to the supplied global address and will then proceed to verify the data words read back as expected. The CCIF flag will set after the Program P-Flash operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                         |  |

|          |           | Set if command not available in current mode (see Table 28-27)                      |  |

|          |           | Set if an invalid global address [17:0] is supplied see Table 28-3) <sup>1</sup>    |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |

|          | FPVIOL    | Set if the global address [17:0] points to a protected area                         |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |

| able 28-41. Program P-Flash Command Error Handling |

|----------------------------------------------------|

|----------------------------------------------------|

<sup>1</sup> As defined by the memory map for FTMRG96K1.

## 28.4.6.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash. The Program Once reserved field can be read using the Read Once command as described in Section 28.4.6.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                            |              |  |

|-------------|---------------------------------------------|--------------|--|

| 000         | 0x07                                        | Not Required |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |              |  |

| 010         | Program Once word 0 value                   |              |  |

| 011         | Program Once word 1 value                   |              |  |

| 100         | Program Once word 2 value                   |              |  |

| 101         | Program Once word 3 value                   |              |  |

Table 28-42. Program Once Command FCCOB Requirements

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

# 29.4.6.2 Erase Verify Block Command

The Erase Verify Block command allows the user to verify that an entire P-Flash or EEPROM block has been erased. The FCCOB FlashBlockSelectionCode[1:0] bits determine which block must be verified.

| CCOBIX[2:0] | FCCOB Parameters |                                                         |  |

|-------------|------------------|---------------------------------------------------------|--|

| 000         | 0x02             | Flash block<br>selection code [1:0]. See<br>Table 29-34 |  |

### Table 29-34. Flash block selection code description

| Selection code[1:0] | Flash block to be verified |

|---------------------|----------------------------|

| 00                  | EEPROM                     |

| 01                  | Invalid (ACCERR)           |

| 10                  | P-Flash                    |

| 11                  | P-Flash                    |

Upon clearing CCIF to launch the Erase Verify Block command, the Memory Controller will verify that the selected P-Flash or EEPROM block is erased. The CCIF flag will set after the Erase Verify Block operation has completed. If the block is not erased, it means blank check failed, both MGSTAT bits will be set.

| Register | Error Bit | Error Condition                                                                                   |  |

|----------|-----------|---------------------------------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                       |  |

|          |           | Set if an invalid FlashBlockSelectionCode[1:0] is supplied                                        |  |

| FSTAT    | FPVIOL    | None                                                                                              |  |

| _        | MGSTAT1   | Set if any errors have been encountered during the read or if blank check faile                   |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |  |

# 29.4.6.3 Erase Verify P-Flash Section Command

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases.

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1<br>DFDIE | <ul> <li>Double Bit Fault Detect Interrupt Enable — The DFDIE bit controls interrupt generation when a double bit fault is detected during a Flash block read operation.</li> <li>0 DFDIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the DFDIF flag is set (see Section 30.3.2.8)</li> </ul>                                                       |  |

| 0<br>SFDIE | <ul> <li>Single Bit Fault Detect Interrupt Enable — The SFDIE bit controls interrupt generation when a single bit fault is detected during a Flash block read operation.</li> <li>0 SFDIF interrupt disabled whenever the SFDIF flag is set (see Section 30.3.2.8)</li> <li>1 An interrupt will be requested whenever the SFDIF flag is set (see Section 30.3.2.8)</li> </ul> |  |

### Table 30-14. FERCNFG Field Descriptions

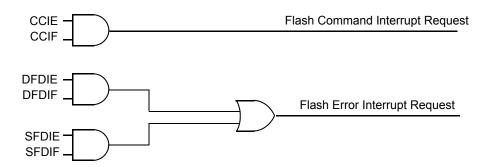

## 30.3.2.7 Flash Status Register (FSTAT)

The FSTAT register reports the operational status of the Flash module.

Offset Module Base + 0x0006

### Figure 30-11. Flash Status Register (FSTAT)

<sup>1</sup> Reset value can deviate from the value shown if a double bit fault is detected during the reset sequence (see Section 30.6).

CCIF, ACCERR, and FPVIOL bits are readable and writable, MGBUSY and MGSTAT bits are readable but not writable, while remaining bits read 0 and are not writable.

#### Table 30-15. FSTAT Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIF   | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command completion or command violation.</li> <li>0 Flash command in progress</li> <li>1 Flash command has completed</li> </ul>                                                                                                                                                                           |

| 5<br>ACCERR | <ul> <li>Flash Access Error Flag — The ACCERR bit indicates an illegal access has occurred to the Flash memory caused by either a violation of the command write sequence (see Section 30.4.4.2) or issuing an illegal Flash command. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR.</li> <li>0 No access error detected</li> <li>1 Access error detected</li> </ul>        |

| 4<br>FPVIOL | <ul> <li>Flash Protection Violation Flag — The FPVIOL bit indicates an attempt was made to program or erase an address in a protected area of P-Flash or EEPROM memory during a command write sequence. The FPVIOL bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL is set, it is not possible to launch a command or start a command write sequence.</li> <li>0 No protection violation detected</li> <li>1 Protection violation detected</li> </ul> |

#### 192 KByte Flash Module (S12FTMRG192K2V1)

Upon clearing CCIF to launch the Read Once command, a Read Once phrase is fetched and stored in the FCCOB indexed register. The CCIF flag will set after the Read Once operation has completed. Valid phrase index values for the Read Once command range from 0x0000 to 0x0007. During execution of the Read Once command, any attempt to read addresses within P-Flash block will return invalid data.

| Register | Error Bit | Error Condition                                                         |  |

|----------|-----------|-------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                             |  |

|          |           | Set if command not available in current mode (see Table 30-27)          |  |

| FSTAT    |           | Set if an invalid phrase index is supplied                              |  |

| FSTAL    | FPVIOL    | None                                                                    |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |  |

| Table 30-39. Read Once Command Error Handling |

|-----------------------------------------------|

|-----------------------------------------------|

## 30.4.6.5 Program P-Flash Command

The Program P-Flash operation will program a previously erased phrase in the P-Flash memory using an embedded algorithm.

## CAUTION

A P-Flash phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash phrase is not allowed.

Table 30-40. Program P-Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                       |                                                     |  |

|-------------|------------------------------------------------------------------------|-----------------------------------------------------|--|

| 000         | 0x06                                                                   | Global address [17:16] to<br>identify P-Flash block |  |

| 001         | Global address [15:0] of phrase location to be programmed <sup>1</sup> |                                                     |  |

| 010         | Word 0 program value                                                   |                                                     |  |

| 011         | Word 1 program value                                                   |                                                     |  |

| 100         | Word 2 program value                                                   |                                                     |  |

| 101         | Word 3 program value                                                   |                                                     |  |

Global address [2:0] must be 000

Upon clearing CCIF to launch the Program P-Flash command, the Memory Controller will program the data words to the supplied global address and will then proceed to verify the data words read back as expected. The CCIF flag will set after the Program P-Flash operation has completed.