#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                 |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 26                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12gn32f1mlc |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Device Overview MC9S12G-Family**

|             |     | <lowest< th=""><th>Function<br/>PRIORITY-</th><th>Power</th><th colspan="2">Internal Pull<br/>Resistor</th></lowest<> | Function<br>PRIORITY- | Power       | Internal Pull<br>Resistor |                  |           |                |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|---------------------------|------------------|-----------|----------------|

| Package Pin | Pin | 2nd<br>Func.                                                                                                          | 3rd<br>Func.          | 4th<br>Func | 5th<br>Func               | Supply           | CTRL      | Reset<br>State |

| 57          | PS5 | MOSI0                                                                                                                 |                       | _           | —                         | V <sub>DDX</sub> | PERS/PPSS | Up             |

| 58          | PS6 | SCK0                                                                                                                  | _                     | _           |                           | V <sub>DDX</sub> | PERS/PPSS | Up             |

| 59          | PS7 | API_EXTC<br>LK                                                                                                        | ECLK                  | SS0         |                           | V <sub>DDX</sub> | PERS/PPSS | Up             |

| 60          | PM0 | _                                                                                                                     | _                     | _           |                           | V <sub>DDX</sub> | PERM/PPSM | Disabled       |

| 61          | PM1 | _                                                                                                                     |                       | _           |                           | V <sub>DDX</sub> | PERM/PPSM | Disabled       |

| 62          | PM2 | —                                                                                                                     | _                     | _           | _                         | V <sub>DDX</sub> | PERM/PPSM | Disabled       |

| 63          | PM3 | —                                                                                                                     | _                     |             | _                         | V <sub>DDX</sub> | PERM/PPSM | Disabled       |

| 64          | PJ7 | KWJ7                                                                                                                  | _                     |             | _                         | V <sub>DDX</sub> | PERJ/PPSJ | Up             |

#### Table 1-14. 64-Pin LQFP Pinout for S12GN48

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

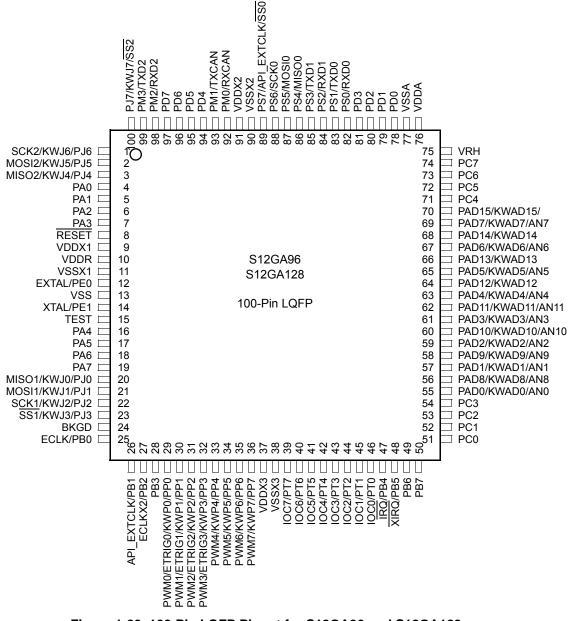

## 1.8.7.3 Pinout 100-Pin LQFP

Figure 1-20. 100-Pin LQFP Pinout for S12GA96 and S12GA128

|             | <b>Function</b><br><lowestpriorityhighest></lowestpriorityhighest> |                |              |              | Power            | Internal Pull<br>Resistor |                |

|-------------|--------------------------------------------------------------------|----------------|--------------|--------------|------------------|---------------------------|----------------|

| Package Pin | Pin                                                                | 2nd<br>Func.   | 3rd<br>Func. | 4th<br>Func. | Supply           | CTRL                      | Reset<br>State |

| 86          | PS4                                                                | MISO0          | _            | _            | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 87          | PS5                                                                | MOSI0          | _            | —            | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 88          | PS6                                                                | SCK0           | _            | —            | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 89          | PS7                                                                | API_EXTC<br>LK | SS0          | _            | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 90          | VSSX2                                                              | _              | _            | _            | —                |                           | —              |

| 91          | VDDX2                                                              | _              | _            | _            | —                |                           | —              |

| 92          | PM0                                                                | RXCAN          | _            | —            | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 93          | PM1                                                                | TXCAN          | _            | _            | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 94          | PD4                                                                | —              | _            | —            | V <sub>DDX</sub> | PUCR/PUPDE                | Disabled       |

| 95          | PD5                                                                | —              | _            | —            | V <sub>DDX</sub> | PUCR/PUPDE                | Disabled       |

| 96          | PD6                                                                | —              | _            | —            | V <sub>DDX</sub> | PUCR/PUPDE                | Disabled       |

| 97          | PD7                                                                | —              | —            | —            | V <sub>DDX</sub> | PUCR/PUPDE                | Disabled       |

| 98          | PM2                                                                | RXD2           | —            | —            | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 99          | PM3                                                                | TXD2           | _            | —            | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 100         | PJ7                                                                | KWJ7           | SS2          |              | V <sub>DDX</sub> | PERJ/PPSJ                 | Up             |

Table 1-31. 100-Pin LQFP Pinout for S12GA192 and S12GA240

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

| PAD3      | <ul> <li>20 TSSOP: The ACMPO signal of the analog comparator is mapped to this pin when used with the ACMP function. If the ACMP output is enabled (ACMPC[ACOPE]=1) the I/O state will be forced to output.</li> <li>The ADC analog input channel signal AN3 and the related digital trigger input are mapped to this pin. The ADC function has no effect on the output state. Refer to NOTE/2-172 for input buffer control.</li> <li>Pin interrupts can be generated if enabled in digital input or output mode.</li> <li>Signal priority:</li> <li>20 TSSOP: ACMPO &gt; GPO Others: GPO</li> </ul> |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAD2-PAD0 | <ul> <li>The ADC analog input channel signals AN2-0 and their related digital trigger inputs are mapped to this pin. The ADC function has no effect on the output state. Refer to NOTE/2-172 for input buffer control.</li> <li>Pin interrupts can be generated if enabled in digital input or output mode.</li> <li>Signal priority:<br/>GPO</li> </ul>                                                                                                                                                                                                                                             |

### Table 2-17. Port AD Pins AD7-0 (continued)

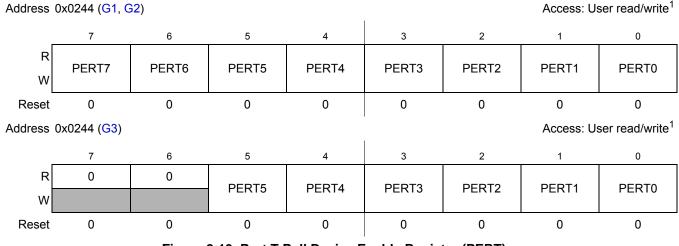

## 2.4.3.18 Port T Pull Device Enable Register (PERT)

Figure 2-19. Port T Pull Device Enable Register (PERT)

<sup>1</sup> Read: Anytime

Write: Anytime

#### Table 2-38. PERT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-2<br>PERT | <b>Port T pull device enable</b> —Enable pull device on input pin<br>This bit controls whether a pull device on the associated port input pin is active. If a pin is used as output this bit has<br>no effect. The polarity is selected by the related polarity select register bit.               |

|             | 1 Pull device enabled<br>0 Pull device disabled                                                                                                                                                                                                                                                    |

| 1<br>PERT   | <b>Port T pull device enable</b> —Enable pull device on input pin<br>This bit controls whether a pull device on the associated port input pin is active. The polarity is selected by the related<br>polarity select register bit. If this pin is used as IRQ only a pullup device can be enabled.  |

|             | 1 Pull device enabled<br>0 Pull device disabled                                                                                                                                                                                                                                                    |

| 0<br>PERT   | <b>Port T pull device enable</b> —Enable pull device on input pin<br>This bit controls whether a pull device on the associated port input pin is active. The polarity is selected by the related<br>polarity select register bit. If this pin is used as XIRQ only a pullup device can be enabled. |

|             | 1 Pull device enabled<br>0 Pull device disabled                                                                                                                                                                                                                                                    |

## 6.5 Initialization/Application Information

## 6.5.1 Initialization

After system reset, software should:

- 1. Initialize the interrupt vector base register if the interrupt vector table is not located at the default location (0xFF80–0xFFF9).

- 2. Enable I bit maskable interrupts by clearing the I bit in the CCR.

- 3. Enable the X bit maskable interrupt by clearing the X bit in the CCR.

## 6.5.2 Interrupt Nesting

The interrupt request scheme makes it possible to nest I bit maskable interrupt requests handled by the CPU.

• I bit maskable interrupt requests can be interrupted by an interrupt request with a higher priority.

I bit maskable interrupt requests cannot be interrupted by other I bit maskable interrupt requests per default. In order to make an interrupt service routine (ISR) interruptible, the ISR must explicitly clear the I bit in the CCR (CLI). After clearing the I bit, other I bit maskable interrupt requests can interrupt the current ISR.

An ISR of an interruptible I bit maskable interrupt request could basically look like this:

- 1. Service interrupt, that is clear interrupt flags, copy data, etc.

- 2. Clear I bit in the CCR by executing the instruction CLI (thus allowing other I bit maskable interrupt requests)

- 3. Process data

- 4. Return from interrupt by executing the instruction RTI

## 6.5.3 Wake Up from Stop or Wait Mode

## 6.5.3.1 CPU Wake Up from Stop or Wait Mode

Every I bit maskable interrupt request is capable of waking the MCU from stop or wait mode. To determine whether an I bit maskable interrupts is qualified to wake-up the CPU or not, the same conditions as in normal run mode are applied during stop or wait mode:

• If the I bit in the CCR is set, all I bit maskable interrupts are masked from waking-up the MCU.

Since there are no clocks running in stop mode, only interrupts which can be asserted asynchronously can wake-up the MCU from stop mode.

The X bit maskable interrupt request can wake up the MCU from stop or wait mode at anytime, even if the X bit in CCR is set<sup>1</sup>.

<sup>1.</sup> The capability of the  $\overline{\text{XIRQ}}$  pin to wake-up the MCU with the X bit set may not be available if, for example, the  $\overline{\text{XIRQ}}$  pin is shared with other peripheral modules on the device. Please refer to the Device section of the MCU reference manual for details.

If the X bit maskable interrupt request is used to wake-up the MCU with the X bit in the CCR set, the associated ISR is not called. The CPU then resumes program execution with the instruction following the WAI or STOP instruction. This features works following the same rules like any interrupt request, that is care must be taken that the X interrupt request used for wake-up remains active at least until the system begins execution of the instruction following the WAI or STOP instruction; otherwise, wake-up may not occur.

### NOTE

The ACK pulse does not provide a time out. This means for the GO\_UNTIL command that it can not be distinguished if a stop or wait has been executed (command discarded and ACK not issued) or if the "UNTIL" condition (BDM active) is just not reached yet. Hence in any case where the ACK pulse of a command is not issued the possible pending command should be aborted before issuing a new command. See the handshake abort procedure described in Section 7.4.8, "Hardware Handshake Abort Procedure".

## 7.4.8 Hardware Handshake Abort Procedure

The abort procedure is based on the SYNC command. In order to abort a command, which had not issued the corresponding ACK pulse, the host controller should generate a low pulse in the BKGD pin by driving it low for at least 128 serial clock cycles and then driving it high for one serial clock cycle, providing a speedup pulse. By detecting this long low pulse in the BKGD pin, the target executes the SYNC protocol, see Section 7.4.9, "SYNC — Request Timed Reference Pulse", and assumes that the pending command and therefore the related ACK pulse, are being aborted. Therefore, after the SYNC protocol has been completed the host is free to issue new BDM commands. For BDM firmware READ or WRITE commands it can not be guaranteed that the pending command is aborted when issuing a SYNC before the corresponding ACK pulse. There is a short latency time from the time the READ or WRITE access begins until it is finished and the corresponding ACK pulse is issued. The latency time depends on the firmware READ or WRITE command that is issued and on the selected bus clock rate. When the SYNC command starts during this latency time the READ or WRITE command will not be aborted, but the corresponding ACK pulse will be aborted. A pending GO, TRACE1 or GO\_UNTIL command can not be aborted. Only the corresponding ACK pulse can be aborted by the SYNC command.

Although it is not recommended, the host could abort a pending BDM command by issuing a low pulse in the BKGD pin shorter than 128 serial clock cycles, which will not be interpreted as the SYNC command. The ACK is actually aborted when a negative edge is perceived by the target in the BKGD pin. The short abort pulse should have at least 4 clock cycles keeping the BKGD pin low, in order to allow the negative edge to be detected by the target. In this case, the target will not execute the SYNC protocol but the pending command will be aborted along with the ACK pulse. The potential problem with this abort procedure is when there is a conflict between the ACK pulse and the short abort pulse. In this case, the target may not perceive the abort pulse. The worst case is when the pending command is a read command (i.e., READ\_BYTE). If the abort pulse is not perceived by the target the host to retrieve the accessed memory byte. In this case, host and target will run out of synchronism. However, if the command to be aborted is not a read command the short abort pulse, is the first bit of a new BDM command.

### NOTE

The details about the short abort pulse are being provided only as a reference for the reader to better understand the BDM internal behavior. It is not recommended that this procedure be used in a real application.

#### S12S Debug Module (S12SDBGV2)

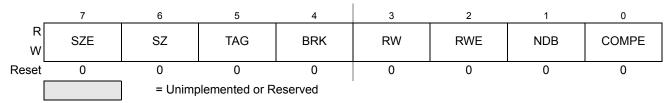

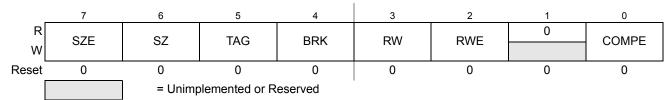

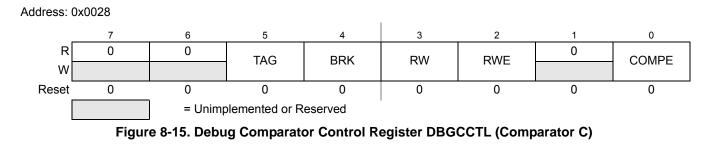

register bytes (three address bus compare registers and a control register). Comparator C consists of four register bytes (three address bus compare registers and a control register).

Each set of comparator registers can be accessed using the COMRV bits in the DBGC1 register. Unimplemented registers (e.g. Comparator B data bus and data bus masking) read as zero and cannot be written. The control register for comparator B differs from those of comparators A and C.

| 0x0028 | CONTROL              | Read/Write | Comparators A,B and C |

|--------|----------------------|------------|-----------------------|

| 0x0029 | ADDRESS HIGH         | Read/Write | Comparators A,B and C |

| 0x002A | ADDRESS MEDIUM       | Read/Write | Comparators A,B and C |

| 0x002B | ADDRESS LOW          | Read/Write | Comparators A,B and C |

| 0x002C | DATA HIGH COMPARATOR | Read/Write | Comparator A only     |

| 0x002D | DATA LOW COMPARATOR  | Read/Write | Comparator A only     |

| 0x002E | DATA HIGH MASK       | Read/Write | Comparator A only     |

| 0x002F | DATA LOW MASK        | Read/Write | Comparator A only     |

### Table 8-21. Comparator Register Layout

## 8.3.2.8.1 Debug Comparator Control Register (DBGXCTL)

The contents of this register bits 7 and 6 differ depending upon which comparator registers are visible in the 8-byte window of the DBG module register address map.

Address: 0x0028

Address: 0x0028

MC9S12G Family Reference Manual Rev.1.27

## 8.5.6 Scenario 5

Trigger if following event A, event C precedes event B. i.e. the expected execution flow is A->B->C.

Scenario 5 is possible with the S12SDBGV1 SCR encoding

## 8.5.7 Scenario 6

Trigger if event A occurs twice in succession before any of 2 other events (BC) occurs. This scenario is not possible using the S12SDBGV1 SCR encoding. S12SDBGV2 includes additions shown in red. The change in SCR1 encoding also has the advantage that a State1->State3 transition using M0 is now possible. This is advantageous because range and data bus comparisons use channel0 only.

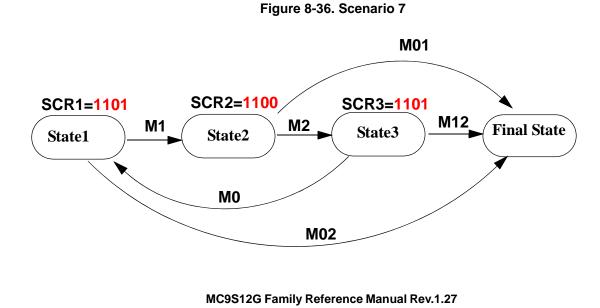

## 8.5.8 Scenario 7

Trigger when a series of 3 events is executed out of order. Specifying the event order as M1,M2,M0 to run in loops (120120120). Any deviation from that order should trigger. This scenario is not possible using the S12SDBGV1 SCR encoding because OR possibilities are very limited in the channel encoding. By adding OR forks as shown in red this scenario is possible.

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MULT      | Multi-Channel Sample Mode — When MULT is 0, the ATD sequence controller samples only from the specified analog input channel for an entire conversion sequence. The analog channel is selected by channel selection code (control bits CD/CC/CB/CA located in ATDCTL5). When MULT is 1, the ATD sequence controller samples across channels. The number of channels sampled is determined by the sequence length value (S8C, S4C, S2C, S1C). The first analog channel examined is determined by channel selection code (CD, CC, CB, CA control bits); subsequent channels sampled in the sequence are determined by incrementing the channel selection code or wrapping around to AN0 (channel 0). |

| 3–0<br>CD, CC, | Analog Input Channel Select Code — These bits select the analog input channel(s). Table 16-15 lists the coding used to select the various analog input channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CB, CA         | In the case of single channel conversions (MULT=0), this selection code specifies the channel to be examined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | In the case of multiple channel conversions (MULT=1), this selection code specifies the first channel to be examined in the conversion sequence. Subsequent channels are determined by incrementing the channel selection code or wrapping around to AN0 (after converting the channel defined by the Wrap Around Channel Select Bits WRAP3-0 in ATDCTL0). When starting with a channel number higher than the one defined by WRAP3-0 the first wrap around will be AN16 to AN0.                                                                                                                                                                                                                   |

| SC | CD | сс | СВ | СА | Analog Input<br>Channel |

|----|----|----|----|----|-------------------------|

| 0  | 0  | 0  | 0  | 0  | AN0                     |

|    | 0  | 0  | 0  | 1  | AN1                     |

|    | 0  | 0  | 1  | 0  | AN2                     |

|    | 0  | 0  | 1  | 1  | AN3                     |

|    | 0  | 1  | 0  | 0  | AN4                     |

|    | 0  | 1  | 0  | 1  | AN5                     |

|    | 0  | 1  | 1  | 0  | AN6                     |

|    | 0  | 1  | 1  | 1  | AN7                     |

|    | 1  | 0  | 0  | 0  | AN8                     |

|    | 1  | 0  | 0  | 1  | AN9                     |

|    | 1  | 0  | 1  | 0  | AN10                    |

|    | 1  | 0  | 1  | 1  | AN11                    |

|    | 1  | 1  | 0  | 0  | AN12                    |

|    | 1  | 1  | 0  | 1  | AN13                    |

|    | 1  | 1  | 1  | 0  | AN14                    |

|    | 1  | 1  | 1  | 1  | AN15                    |

Table 16-15. Analog Input Channel Select Coding

Scalable Controller Area Network (S12MSCANV3)

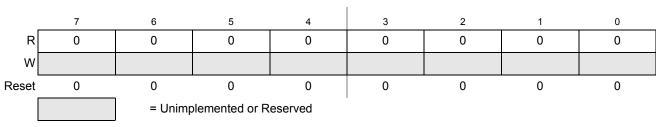

## 18.3.2.13 MSCAN Reserved Register

This register is reserved for factory testing of the MSCAN module and is not available in normal system operating modes.

#### Figure 18-16. MSCAN Reserved Register

Read: Always reads zero in normal system operation modes Write: Unimplemented in normal system operation modes

#### NOTE

Writing to this register when in special system operating modes can alter the MSCAN functionality.

## 18.3.2.14 MSCAN Miscellaneous Register (CANMISC)

This register provides additional features.

#### Figure 18-17. MSCAN Miscellaneous Register (CANMISC)

<sup>1</sup> Read: Anytime

Write: Anytime; write of '1' clears flag; write of '0' ignored

#### Table 18-21. CANMISC Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Bus-off State Hold Until User Request — If BORM is set in MSCAN Control Register 1 (CANCTL1), this bit indicates whether the module has entered the bus-off state. Clearing this bit requests the recovery from bus-off. Refer to Section 18.5.2, "Bus-Off Recovery," for details.</li> <li>Module is not bus-off or recovery has been requested by user in bus-off state</li> <li>Module is bus-off and holds this state until user request</li> </ul> |

#### MC9S12G Family Reference Manual Rev.1.27

## 20.4.4 Baud Rate Generation

A 13-bit modulus counter in the baud rate generator derives the baud rate for both the receiver and the transmitter. The value from 0 to 8191 written to the SBR12:SBR0 bits determines the bus clock divisor. The SBR bits are in the SCI baud rate registers (SCIBDH and SCIBDL). The baud rate clock is synchronized with the bus clock and drives the receiver. The baud rate clock divided by 16 drives the transmitter. The receiver has an acquisition rate of 16 samples per bit time.

Baud rate generation is subject to one source of error:

• Integer division of the bus clock may not give the exact target frequency.

Table 20-16 lists some examples of achieving target baud rates with a bus clock frequency of 25 MHz.

### When IREN = 0 then,

SCI baud rate = SCI bus clock / (16 \* SCIBR[12:0])

| Bits<br>SBR[12:0] | Receiver<br>Clock (Hz) | Transmitter<br>Clock (Hz) | Target<br>Baud Rate | Error<br>(%) |

|-------------------|------------------------|---------------------------|---------------------|--------------|

| 41                | 609,756.1              | 38,109.8                  | 38,400              | .76          |

| 81                | 308,642.0              | 19,290.1                  | 19,200              | .47          |

| 163               | 153,374.2              | 9585.9                    | 9,600               | .16          |

| 326               | 76,687.1               | 4792.9                    | 4,800               | .15          |

| 651               | 38,402.5               | 2400.2                    | 2,400               | .01          |

| 1302              | 19,201.2               | 1200.1                    | 1,200               | .01          |

| 2604              | 9600.6                 | 600.0                     | 600                 | .00          |

| 5208              | 4800.0                 | 300.0                     | 300                 | .00          |

#### Table 20-16. Baud Rates (Example: Bus Clock = 25 MHz)

#### Timer Module (TIM16B8CV3)

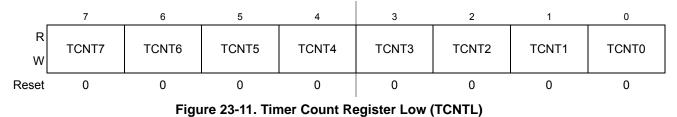

Module Base + 0x0005

The 16-bit main timer is an up counter.

A full access for the counter register should take place in one clock cycle. A separate read/write for high byte and low byte will give a different result than accessing them as a word.

#### Read: Anytime

Write: Has no meaning or effect in the normal mode; only writable in special modes (test\_mode = 1).

The period of the first count after a write to the TCNT registers may be a different size because the write is not synchronized with the prescaler clock.

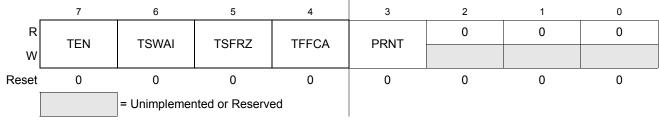

### 23.3.2.6 Timer System Control Register 1 (TSCR1)

Module Base + 0x0006

Figure 23-12. Timer System Control Register 1 (TSCR1)

Read: Anytime

Write: Anytime

#### Table 23-6. TSCR1 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TEN   | <ul> <li>Timer Enable</li> <li>Disables the main timer, including the counter. Can be used for reducing power consumption.</li> <li>Allows the timer to function normally.</li> <li>If for any reason the timer is not active, there is no ÷64 clock for the pulse accumulator because the ÷64 is generated by the timer prescaler.</li> </ul> |

| 6<br>TSWAI | <ul> <li>Timer Module Stops While in Wait</li> <li>Allows the timer module to continue running during wait.</li> <li>Disables the timer module when the MCU is in the wait mode. Timer interrupts cannot be used to get the MCU out of wait.</li> <li>TSWAI also affects pulse accumulator.</li> </ul>                                         |

#### MC9S12G Family Reference Manual Rev.1.27

## 25.3.2.9.1 P-Flash Protection Restrictions

The general guideline is that P-Flash protection can only be added and not removed. Table 25-21 specifies all valid transitions between P-Flash protection scenarios. Any attempt to write an invalid scenario to the FPROT register will be ignored. The contents of the FPROT register reflect the active protection scenario. See the FPHS and FPLS bit descriptions for additional restrictions.

| From                   | To Protection Scenario <sup>1</sup> |   |   |   |   |   |   |   |  |

|------------------------|-------------------------------------|---|---|---|---|---|---|---|--|

| Protection<br>Scenario | 0                                   | 1 | 2 | 3 | 4 | 5 | 6 | 7 |  |

| 0                      | Х                                   | Х | Х | Х |   |   |   |   |  |

| 1                      |                                     | Х |   | Х |   |   |   |   |  |

| 2                      |                                     |   | Х | Х |   |   |   |   |  |

| 3                      |                                     |   |   | Х |   |   |   |   |  |

| 4                      |                                     |   |   | Х | Х |   |   |   |  |

| 5                      |                                     |   | Х | Х | Х | Х |   |   |  |

| 6                      |                                     | Х |   | Х | Х |   | Х |   |  |

| 7                      | Х                                   | Х | Х | Х | Х | Х | Х | Х |  |

Table 25-21. P-Flash Protection Scenario Transitions

<sup>1</sup> Allowed transitions marked with X, see Figure 25-14 for a definition of the scenarios.

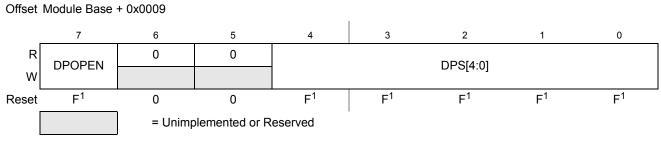

## 25.3.2.10 EEPROM Protection Register (EEPROT)

The EEPROT register defines which EEPROM sectors are protected against program and erase operations.

### Figure 25-15. EEPROM Protection Register (EEPROT)

<sup>1</sup> Loaded from IFR Flash configuration field, during reset sequence.

The (unreserved) bits of the EEPROT register are writable with the restriction that protection can be added but not removed. Writes must increase the DPS value and the DPOPEN bit can only be written from 1 (protection disabled) to 0 (protection enabled). If the DPOPEN bit is set, the state of the DPS bits is irrelevant.

#### 32 KByte Flash Module (S12FTMRG32K1V1)

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|------|-------------------------------------------|

| 010         | HI   | Data 0 [15:8]                             |

| 010         | LO   | Data 0 [7:0]                              |

| 011         | HI   | Data 1 [15:8]                             |

| 011         | LO   | Data 1 [7:0]                              |

| 100         | HI   | Data 2 [15:8]                             |

| 100         | LO   | Data 2 [7:0]                              |

| 101         | HI   | Data 3 [15:8]                             |

| 101         | LO   | Data 3 [7:0]                              |

Table 25-24. FCCOB - NVM Command Mode (Typical Usage)

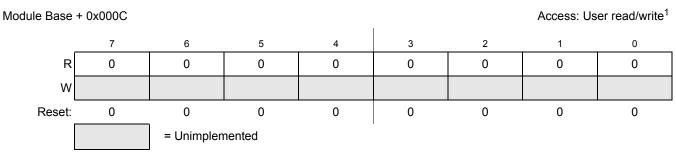

## 25.3.2.12 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000C

Offset Module Base + 0x000D

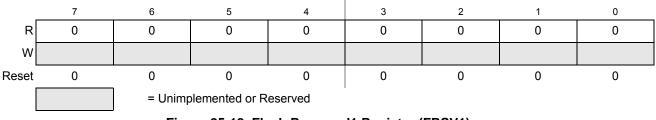

Figure 25-18. Flash Reserved1 Register (FRSV1)

All bits in the FRSV1 register read 0 and are not writable.

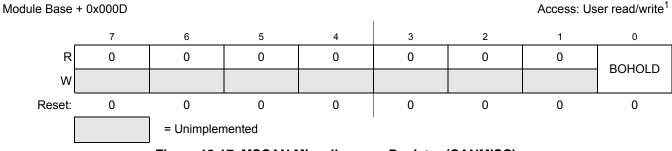

## 25.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

Figure 25-19. Flash Reserved2 Register (FRSV2)

All bits in the FRSV2 register read 0 and are not writable.

### 25.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

#### 64 KByte Flash Module (S12FTMRG64K1V1)

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 27.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 27.4.6.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0x3\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x3\_FF00-0x3\_FF07 are unaffected by the Verify Backdoor Access Key command sequence. The Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired. In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses 0x3\_FF00-0x3\_FF07 in the Flash configuration field.

## 27.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

A secured MCU can be unsecured in special single chip mode by using the following method to erase the P-Flash and EEPROM memory:

- 1. Reset the MCU into special single chip mode

- 2. Delay while the BDM executes the Erase Verify All Blocks command write sequence to check if the P-Flash and EEPROM memories are erased

- 3. Send BDM commands to disable protection in the P-Flash and EEPROM memory

- 4. Execute the Erase All Blocks command write sequence to erase the P-Flash and EEPROM memory. Alternatively the Unsecure Flash command can be executed, if so the steps 5 and 6 below are skeeped.

- 5. After the CCIF flag sets to indicate that the Erase All Blocks operation has completed, reset the MCU into special single chip mode

- 6. Delay while the BDM executes the Erase Verify All Blocks command write sequence to verify that the P-Flash and EEPROM memory are erased

If the P-Flash and EEPROM memory are verified as erased, the MCU will be unsecured. All BDM commands will now be enabled and the Flash security byte may be programmed to the unsecure state by continuing with the following steps:

7. Send BDM commands to execute the Program P-Flash command write sequence to program the Flash security byte to the unsecured state

# Chapter 31 240 KByte Flash Module (S12FTMRG240K2V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected                                                   | Description of Changes                                        |

|--------------------|------------------|------------------------------------------------------------------------|---------------------------------------------------------------|

| V01.06             | 23 Jun 2010      | 31.4.6.2/31-115<br>9<br>31.4.6.12/31-11<br>66<br>31.4.6.13/31-11<br>67 | Updated description of the commands RD1BLK, MLOADU and MLOADF |

| V01.07             | 20 aug 2010      | 31.4.6.2/31-115<br>9<br>31.4.6.12/31-11<br>66<br>31.4.6.13/31-11<br>67 | Updated description of the commands RD1BLK, MLOADU and MLOADF |

| Rev.1.27           | 31 Jan 2011      | 31.3.2.9/31-114<br>2                                                   | Updated description of protection on Section 31.3.2.9         |

#### Table 31-1. Revision History

## 31.1 Introduction

The FTMRG240K2 module implements the following:

- 240Kbytes of P-Flash (Program Flash) memory

- 4Kbytes of EEPROM memory

The Flash memory is ideal for single-supply applications allowing for field reprogramming without requiring external high voltage sources for program or erase operations. The Flash module includes a memory controller that executes commands to modify Flash memory contents. The user interface to the memory controller consists of the indexed Flash Common Command Object (FCCOB) register which is written to with the command, global address, data, and any required command parameters. The memory controller must complete the execution of a command before the FCCOB register can be written to with a new command.

### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

#### Table A-22. ADC Conversion Performance 5V range (Junction Temperature From +150°C To +160°C)

| S12GI            | NA1          | 6, S12GNA32                                                                  |                                                                                 |                                                          |                                                        |                                            |             |        |

|------------------|--------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|--------------------------------------------|-------------|--------|

| Supply<br>The va | y vo<br>alue | ltage 4.5V < V <sub>DDA</sub> < 5.5 V, +1<br>s are tested to be valid with n | 50 <sup>o</sup> C < T <sub>J</sub> < 160 <sup>o</sup> C<br>o port AD output dri | , V <sub>REF</sub> = V <sub>RH</sub> -<br>vers switching | V <sub>RL</sub> = V <sub>DDA</sub> , t<br>simultaneous | f <sub>ADCCLK</sub> = 8.0<br>with conversi | MHz<br>ons. |        |

| Num              | С            | Rating <sup>1</sup>                                                          |                                                                                 | Symbol                                                   | Min                                                    | Тур                                        | Max         | Unit   |

| 1                | М            | Resolution                                                                   | 12-Bit                                                                          | LSB                                                      |                                                        | 1.25                                       |             | mV     |

| 2                | М            | Differential Nonlinearity                                                    | 12-Bit                                                                          | DNL                                                      |                                                        | ±2                                         |             | counts |

| 3                | М            | Integral Nonlinearity                                                        | 12-Bit                                                                          | INL                                                      |                                                        | ±2.5                                       |             | counts |

| 4                | М            | Absolute Error <sup>2</sup>                                                  | 12-Bit                                                                          | AE                                                       |                                                        | ±4                                         |             | counts |

| 5                | С            | Resolution                                                                   | 10-Bit                                                                          | LSB                                                      |                                                        | 5                                          |             | mV     |

| 6                | С            | Differential Nonlinearity                                                    | 10-Bit                                                                          | DNL                                                      |                                                        | ±0.5                                       |             | counts |

| 7                | С            | Integral Nonlinearity                                                        | 10-Bit                                                                          | INL                                                      |                                                        | ±1                                         |             | counts |

| 8                | С            | Absolute Error <sup>2</sup>                                                  | 10-Bit                                                                          | AE                                                       |                                                        | ±2                                         |             | counts |

| 9                | С            | Resolution                                                                   | 8-Bit                                                                           | LSB                                                      |                                                        | 20                                         |             | mV     |

| 10               | С            | Differential Nonlinearity                                                    | 8-Bit                                                                           | DNL                                                      |                                                        | ±0.3                                       |             | counts |

| 11               | С            | Integral Nonlinearity                                                        | 8-Bit                                                                           | INL                                                      |                                                        | ±0.5                                       |             | counts |

| 12               | С            | Absolute Error <sup>2</sup>                                                  | 8-Bit                                                                           | AE                                                       |                                                        | ±1                                         |             | counts |

<sup>1</sup> The 8-bit and 10-bit mode operation is structurally tested in production test. Absolute values are tested in 12-bit mode.

$^2$  These values include the quantization error which is inherently 1/2 count for any A/D converter.

NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

3. DATUMS B, C AND D TO BE DETERMINED AT DATUM PLANE H.

$\overline{4}$ . The top package body size may be smaller than the bottom package size by a maximum of 0.1 mm.

5. DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSIONS. THE MAXIMUM ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. D1 AND E1 ARE MAXIMUM BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

6. DIMENSION & DOES NOT INCLUDE DAM BAR PROTRUSION. PROTRUSIONS SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.35. MINIMUM SPACE BETWEEN PROTRUSION AND AN ADJACENT LEAD SHALL BE 0.07 MM.

/7. DIMENSIONS D AND E ARE DETERMINED AT THE SEATING PLANE, DATUM A.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                                | PRINT VERSION NOT TO SCALE |        |  |

|---------------------------------------------------------|--------------------|--------------------------------|----------------------------|--------|--|

| TITLE:                                                  |                    | DOCUMENT NO: 98ASS23308W       |                            | REV: H |  |

| 100 LEAD LQFP<br>14 X 14, 0.5 PITCH, 1.4                | LTHICK             | CASE NUMBER: 983-02 25 MAY 200 |                            |        |  |

|                                                         | THION              | STANDARD: NON-JEDEC            |                            |        |  |