Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | 12V1                                                        |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 25MHz                                                       |

| Connectivity               | IrDA, LINbus, SCI, SPI                                      |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 40                                                          |

| Program Memory Size        | 48KB (48K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 1.5К х 8                                                    |

| RAM Size                   | 4K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                |

| Data Converters            | A/D 12x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-LQFP                                                     |

| Supplier Device Package    | 48-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s12gn48f0clf |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.7.3.1 VDDX[3:1]/VDDX, VSSX[3:1]/VSSX— Power and Ground Pins for I/O Drivers

External power and ground for I/O drivers. Bypass requirements depend on how heavily the MCU pins are loaded. All VDDX pins are connected together internally. All VSSX pins are connected together internally.

## NOTE

Not all VDDX[3:1]/VDDX and VSSX[3:1]VSSX pins are available on all packages. Refer to section 1.8 Device Pinouts for further details.

## 1.7.3.2 VDDR — Power Pin for Internal Voltage Regulator

Power supply input to the internal voltage regulator.

## NOTE

On some packages VDDR is bonded to VDDX and the pin is named VDDXR. Refer to section 1.8 Device Pinouts for further details.

## 1.7.3.3 VSS — Core Ground Pin

The voltage supply of nominally 1.8V is derived from the internal voltage regulator. The return current path is through the VSS pin.

# 1.7.3.4 VDDA, VSSA — Power Supply Pins for DAC,ACMP, RVA, ADC and Voltage Regulator

These are the power supply and ground input pins for the digital-to-analog converter, the analog comparator, the reference voltage attenuator, the analog-to-digital converter and the voltage regulator.

## NOTE

On some packages VDDA is connected with VDDXR and the common pin is named VDDXRA.

On some packages the VSSA is connected to VSSX and the common pin is named VSSXA. See section Section 1.8, "Device Pinouts" for further details.

## 1.7.3.5 VRH — Reference Voltage Input Pin

$V_{RH}$  is the reference voltage input pin for the digital-to-analog converter and the analog-to-digital converter. Refer to Section 1.18, "ADC VRH/VRL Signal Connection" for further details.

On some packages VRH is tied to VDDA or VDDXRA. Refer to section 1.8 Device Pinouts for further details.

|             |                  | <lowest< th=""><th>Function</th><th>highest&gt;</th><th>&gt;</th><th>Power</th><th>Internal P<br/>Resisto</th><th></th></lowest<> | Function     | highest>       | >           | Power            | Internal P<br>Resisto |                |

|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|-------------|------------------|-----------------------|----------------|

| Package Pin | Pin              | 2nd<br>Func.                                                                                                                      | 3rd<br>Func. | 4th<br>Func    | 5th<br>Func | Supply           | CTRL                  | Reset<br>State |

| 2           | VDDXR            | _                                                                                                                                 | _            | _              | _           | _                | —                     | _              |

| 3           | VSSX             | _                                                                                                                                 | _            | _              | _           | —                | —                     | _              |

| 4           | PE0 <sup>1</sup> | EXTAL                                                                                                                             | _            | _              | _           | V <sub>DDX</sub> | PUCR/PDPEE            | Down           |

| 5           | VSS              |                                                                                                                                   | _            | _              | _           | _                | —                     |                |

| 6           | PE1 <sup>1</sup> | XTAL                                                                                                                              | _            | _              | -           | V <sub>DDX</sub> | PUCR/PDPEE            | Down           |

| 7           | TEST             | _                                                                                                                                 | _            | _              |             | N.A.             | RESET pin             | Down           |

| 8           | PJ0              | KWJ0                                                                                                                              | _            | _              |             | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 9           | PJ1              | KWJ1                                                                                                                              | _            | _              | _           | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 10          | PJ2              | KWJ2                                                                                                                              | _            | _              | _           | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 11          | PJ3              | KWJ3                                                                                                                              | _            | _              |             | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 12          | BKGD             | MODC                                                                                                                              | _            | _              |             | V <sub>DDX</sub> | PUCR/BKPUE            | Up             |

| 13          | PP0              | KWP0                                                                                                                              | ETRIG0       | API_EXTC<br>LK | PWM0        | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 14          | PP1              | KWP1                                                                                                                              | ETRIG1       | ECLKX2         | PWM1        | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 15          | PP2              | KWP2                                                                                                                              | ETRIG2       | PWM2           | _           | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 16          | PP3              | KWP3                                                                                                                              | ETRIG3       | PWM3           | _           | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 17          | PP4              | KWP4                                                                                                                              | PWM4         | _              |             | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 18          | PP5              | KWP5                                                                                                                              | PWM5         | _              |             | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 19          | PT5              | IOC5                                                                                                                              | —            | _              | _           | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 20          | PT4              | IOC4                                                                                                                              | _            | _              |             | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 21          | PT3              | IOC3                                                                                                                              | _            | _              | _           | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 22          | PT2              | IOC2                                                                                                                              | _            | _              |             | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 23          | PT1              | IOC1                                                                                                                              | IRQ          | _              | _           | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 24          | PT0              | IOC0                                                                                                                              | XIRQ         | _              |             | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 25          | PAD0             | KWAD0                                                                                                                             | AN0          | _              | _           | V <sub>DDA</sub> | PER1AD/PPS1AD         | Disabled       |

| 26          | PAD8             | KWAD8                                                                                                                             | —            | _              | _           | V <sub>DDA</sub> | PER0AD/PPS0AD         | Disabled       |

| 27          | PAD1             | KWAD1                                                                                                                             | AN1          | _              | _           | V <sub>DDA</sub> | PER1AD/PPS1AD         | Disabled       |

| 28          | PAD9             | KWAD9                                                                                                                             | ACMPO        | _              | _           | V <sub>DDA</sub> | PER0AD/PPS0AD         | Disabled       |

| 29          | PAD2             | KWAD2                                                                                                                             | AN2          | —              | —           | V <sub>DDA</sub> | PER1AD/PPS1AD         | Disabled       |

Table 1-11. 48-Pin LQFP/QFN Pinout for S12GNA16 and S12GNA32

|             | <                | Func<br>owestPRIO |              | st>          | Power            | Internal F<br>Resisto |                |

|-------------|------------------|-------------------|--------------|--------------|------------------|-----------------------|----------------|

| Package Pin | Pin              | 2nd<br>Func.      | 3rd<br>Func. | 4th<br>Func. | Supply           | CTRL                  | Reset<br>State |

| 1           | PJ6              | KWJ6              | SCK2         | _            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 2           | PJ5              | KWJ5              | MOSI2        | —            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 3           | PJ4              | KWJ4              | MISO2        | —            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 4           | PA0              | _                 | _            | _            | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 5           | PA1              | _                 | _            |              | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 6           | PA2              | _                 | _            |              | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 7           | PA3              | _                 | _            |              | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 8           | RESET            | _                 | _            |              | V <sub>DDX</sub> | PULLU                 | P              |

| 9           | VDDX1            | _                 | _            |              | —                | _                     | _              |

| 10          | VDDR             | _                 | _            |              | —                | _                     | _              |

| 11          | VSSX1            | _                 | _            | _            | _                | _                     | _              |

| 12          | PE0 <sup>1</sup> | EXTAL             | _            |              | V <sub>DDX</sub> | PUCR/PDPEE            | Down           |

| 13          | VSS              | _                 | _            | _            |                  | _                     | _              |

| 14          | PE1 <sup>1</sup> | XTAL              | _            | _            | V <sub>DDX</sub> | PUCR/PDPEE            | Down           |

| 15          | TEST             | _                 | _            | _            | N.A.             | RESET pin             | Down           |

| 16          | PA4              | _                 | _            | _            | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 17          | PA5              | _                 | _            | _            | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 18          | PA6              | _                 | _            | _            | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 19          | PA7              | _                 | _            | _            | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 20          | PJ0              | KWJ0              | MISO1        | _            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 21          | PJ1              | KWJ1              | MOSI1        |              | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 22          | PJ2              | KWJ2              | SCK1         | _            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 23          | PJ3              | KWJ3              | SS1          | _            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 24          | BKGD             | MODC              | _            | _            | V <sub>DDX</sub> | PUCR/BKPUE            | Up             |

| 25          | PB0              | ECLK              |              |              | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

| 26          | PB1              | API_EXTC<br>LK    | _            | _            | V <sub>DDX</sub> | PUCR/PUPBE Disabled   |                |

| 27          | PB2              | ECLKX2            | _            |              | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

|             | <                | Func<br>owestPRIO |              | st>          | Power            | Internal F<br>Resisto |                |

|-------------|------------------|-------------------|--------------|--------------|------------------|-----------------------|----------------|

| Package Pin | Pin              | 2nd<br>Func.      | 3rd<br>Func. | 4th<br>Func. | Supply           | CTRL                  | Reset<br>State |

| 1           | PJ6              | KWJ6              | SCK2         | _            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 2           | PJ5              | KWJ5              | MOSI2        | _            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 3           | PJ4              | KWJ4              | MISO2        | _            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 4           | PA0              | —                 | _            | —            | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 5           | PA1              | _                 | _            | _            | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 6           | PA2              | _                 | _            | _            | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 7           | PA3              | _                 | _            |              | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 8           | RESET            | _                 | _            |              | V <sub>DDX</sub> | PULLU                 | P              |

| 9           | VDDX1            | _                 | _            | _            | —                |                       | _              |

| 10          | VDDR             | _                 | _            | _            | —                |                       | _              |

| 11          | VSSX1            | _                 | _            |              | _                | _                     | _              |

| 12          | PE0 <sup>1</sup> | EXTAL             | _            | _            | V <sub>DDX</sub> | PUCR/PDPEE            | Down           |

| 13          | VSS              | _                 | _            |              | _                | _                     | _              |

| 14          | PE1 <sup>1</sup> | XTAL              | _            |              | V <sub>DDX</sub> | PUCR/PDPEE            | Down           |

| 15          | TEST             | _                 | _            |              | N.A.             | RESET pin             | Down           |

| 16          | PA4              | _                 | _            |              | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 17          | PA5              | _                 | _            |              | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 18          | PA6              | _                 | _            |              | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 19          | PA7              | _                 | _            |              | V <sub>DDX</sub> | PUCR/PUPAE            | Disabled       |

| 20          | PJ0              | KWJ0              | MISO1        | _            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 21          | PJ1              | KWJ1              | MOSI1        |              | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 22          | PJ2              | KWJ2              | SCK1         | _            | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 23          | PJ3              | KWJ3              | SS1          |              | V <sub>DDX</sub> | PERJ/PPSJ             | Up             |

| 24          | BKGD             | MODC              | _            | _            | V <sub>DDX</sub> | PUCR/BKPUE            | Up             |

| 25          | PB0              | ECLK              | _            | _            | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

| 26          | PB1              | API_EXTC<br>LK    | _            | _            | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

| 27          | PB2              | ECLKX2            |              | _            | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

Table 1-25. 100-Pin LQFP Pinout for S12GA96 and S12GA128

|             | < (   | Fund<br>owestPRIO | <b>ction</b><br>RITYhighe | st>          | Power            | Internal P<br>Resisto |                |

|-------------|-------|-------------------|---------------------------|--------------|------------------|-----------------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.      | 3rd<br>Func.              | 4th<br>Func. | Supply           | CTRL                  | Reset<br>State |

| 28          | PB3   | —                 | —                         | —            | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

| 29          | PP0   | KWP0              | ETRIG0                    | PWM0         | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 30          | PP1   | KWP1              | ETRIG1                    | PWM1         | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 31          | PP2   | KWP2              | ETRIG2                    | PWM2         | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 32          | PP3   | KWP3              | ETRIG3                    | PWM3         | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 33          | PP4   | KWP4              | PWM4                      |              | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 34          | PP5   | KWP5              | PWM5                      |              | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 35          | PP6   | KWP6              | PWM6                      |              | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 36          | PP7   | KWP7              | PWM7                      | _            | V <sub>DDX</sub> | PERP/PPSP             | Disabled       |

| 37          | VDDX3 |                   |                           |              | _                | _                     |                |

| 38          | VSSX3 | _                 | _                         | _            | _                | _                     | _              |

| 39          | PT7   | IOC7              | _                         | _            | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 40          | PT6   | IOC6              |                           |              | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 41          | PT5   | IOC5              | _                         | _            | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 42          | PT4   | IOC4              | _                         | _            | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 43          | PT3   | IOC3              | _                         | _            | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 44          | PT2   | IOC2              | —                         | —            | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 45          | PT1   | IOC1              | _                         | _            | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 46          | PT0   | IOC0              | _                         | _            | V <sub>DDX</sub> | PERT/PPST             | Disabled       |

| 47          | PB4   | ĪRQ               | _                         | _            | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

| 48          | PB5   | XIRQ              | —                         | —            | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

| 49          | PB6   | —                 | —                         | —            | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

| 50          | PB7   | —                 | —                         | —            | V <sub>DDX</sub> | PUCR/PUPBE            | Disabled       |

| 51          | PC0   | —                 | _                         | _            | V <sub>DDA</sub> | PUCR/PUPCE            | Disabled       |

| 52          | PC1   | —                 | —                         | —            | V <sub>DDA</sub> | PUCR/PUPCE Disabl     |                |

| 53          | PC2   | _                 | _                         | _            | V <sub>DDA</sub> | PUCR/PUPCE            | Disabled       |

| 54          | PC3   | —                 | —                         | _            | V <sub>DDA</sub> | PUCR/PUPCE            | Disabled       |

| 55          | PAD0  | KWAD0             | AN0                       | _            | V <sub>DDA</sub> | PER1AD/PPS1AD         | Disabled       |

| 56          | PAD8  | KWAD8             | AN8                       |              | V <sub>DDA</sub> | PER0AD/PPS0AD         | Disabled       |

Table 1-31.

100-Pin LQFP Pinout for S12GA192 and S12GA240

0

PIX0

0

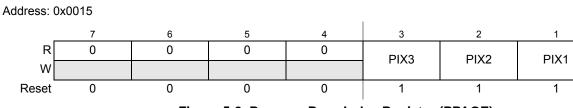

## 5.3.2.4 Program Page Index Register (PPAGE)

## Read: Anytime

## Write: Anytime

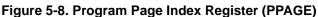

The four index bits of the PPAGE register select a 16K page in the global memory map (Figure 5-11). The selected 16K page is mapped into the paging window ranging from local address 0x8000 to 0xBFFF. Figure 5-9 illustrates the translation from local to global addresses for accesses to the paging window. The CPU has special access to read and write this register directly during execution of CALL and RTC instructions.

Figure 5-9. PPAGE Address Mapping

## NOTE

Writes to this register using the special access of the CALL and RTC instructions will be complete before the end of the instruction execution.

#### Table 5-7. PPAGE Field Descriptions

| Field | Description                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Program Page Index Bits 3–0</b> — These page index bits are used to select which of the 256 flash array pages is to be accessed in the Program Page Window. |

The fixed 16KB page from 0x0000 to 0x3FFF is the page number 0xC. Parts of this page are covered by Registers, EEPROM and RAM space. See SoC Guide for details.

The fixed 16KB page from 0x4000–0x7FFF is the page number 0xD.

|                                       | S12GN16  | S12GN32 | S12G48,<br>S12GN48 | S12G64          | S12G96             | S12G128      | S12G192  | S12G240 |

|---------------------------------------|----------|---------|--------------------|-----------------|--------------------|--------------|----------|---------|

| 0x04000-<br>0x07FFF<br>(NVMRES<br>=1) |          | In      | ternal NVM Re      | esources (for c | details refer to a | section FTMR | G)       |         |

| 0x04000-<br>0x07FFF<br>(NVMRES<br>=0) |          |         |                    |                 |                    |              | Reserved |         |

| 0x08000-<br>0x0FFFF                   |          |         |                    |                 |                    |              |          |         |

| 0x08000-<br>0x1FFFF                   |          |         |                    |                 |                    |              |          |         |

| 0x20000-<br>0x27FFF                   |          |         |                    |                 | Reserved           |              | -        |         |

| 0x28000-<br>0x2FFFF                   |          |         |                    |                 |                    |              |          |         |

| 0x30000-<br>0x33FFF                   |          |         | Reserved           |                 | 1                  |              |          |         |

| 0x34000-<br>0x37FFF                   |          |         |                    |                 |                    | Flash        |          |         |

| 0x38000-<br>0x3BFFF                   | Reserved |         |                    |                 |                    |              |          |         |

| 0x3C000-<br>0x3FFFF                   | 16k      | 32k     | 48k                | 64k             | 96k                | 128k         | 192k     | 240k    |

Table 5-8. Global Address Ranges

# 5.4.4 Prioritization of Memory Accesses

On S12G devices, the CPU and the BDM are not able to access the memory in parallel. An arbitration occurs whenever both modules attempt a memory access at the same time. CPU accesses are handled with higher priority than BDM accesses unless the BDM module has been stalled for more then 128 bus cycles. In this case the pending BDM access will be processed immediately.

# 5.4.5 Interrupts

The S12GMMC does not generate any interrupts.

Write: All modes through BDM operation when not secured

## NOTE

When BDM is made active, the CPU stores the content of its CCR register in the BDMCCR register. However, out of special single-chip reset, the BDMCCR is set to 0xD8 and not 0xD0 which is the reset value of the CCR register in this CPU mode. Out of reset in all other modes the BDMCCR register is read zero.

When entering background debug mode, the BDM CCR holding register is used to save the condition code register of the user's program. It is also used for temporary storage in the standard BDM firmware mode. The BDM CCR holding register can be written to modify the CCR value.

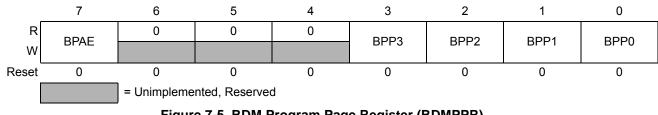

# 7.3.2.2 BDM Program Page Index Register (BDMPPR)

Register Global Address 0x3\_FF08

Figure 7-5. BDM Program Page Register (BDMPPR)

Read: All modes through BDM operation when not secured

Write: All modes through BDM operation when not secured

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>BPAE       | <ul> <li>BDM Program Page Access Enable Bit — BPAE enables program page access for BDM hardware and firmware read/write instructions The BDM hardware commands used to access the BDM registers (READ_BD and WRITE_BD) can not be used for program page accesses even if the BPAE bit is set.</li> <li>0 BDM Program Paging disabled</li> <li>1 BDM Program Paging enabled</li> </ul> |

| 3–0<br>BPP[3:0] | <b>BDM Program Page Index Bits 3–0</b> — These bits define the selected program page. For more detailed information regarding the program page window scheme, please refer to the S12S_MMC Block Guide.                                                                                                                                                                               |

# 7.3.3 Family ID Assignment

The family ID is an 8-bit value located in the BDM ROM in active BDM (at global address: 0x3\_FF0F). The read-only value is a unique family ID which is 0xC2 for devices with an HCS12S core.

# 7.4 Functional Description

The BDM receives and executes commands from a host via a single wire serial interface. There are two types of BDM commands: hardware and firmware commands.

#### S12S Debug Module (S12SDBGV2)

| SC[3:0] | Description (Unspecified matches have no effect)       |  |  |  |  |  |

|---------|--------------------------------------------------------|--|--|--|--|--|

| 1010    | Reserved                                               |  |  |  |  |  |

| 1011    | Reserved                                               |  |  |  |  |  |

| 1100    | Reserved                                               |  |  |  |  |  |

| 1101    | Either Match0 or Match2 to Final StateMatch1 to State2 |  |  |  |  |  |

| 1110    | Reserved                                               |  |  |  |  |  |

| 1111    | Reserved                                               |  |  |  |  |  |

| Table 8-16. | State1 | Sequencer | Next State | e Selection |

|-------------|--------|-----------|------------|-------------|

|-------------|--------|-----------|------------|-------------|

The priorities described in Table 8-36 dictate that in the case of simultaneous matches, a match leading to final state has priority followed by the match on the lower channel number (0,1,2). Thus with SC[3:0]=1101 a simultaneous match0/match1 transitions to final state.

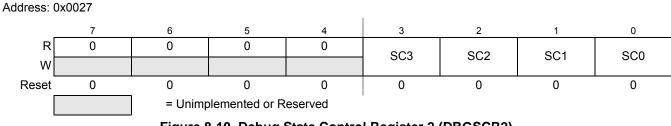

## 8.3.2.7.2 Debug State Control Register 2 (DBGSCR2)

Figure 8-10. Debug State Control Register 2 (DBGSCR2)

Read: If COMRV[1:0] = 01

Write: If COMRV[1:0] = 01 and DBG is not armed.

This register is visible at 0x0027 only with COMRV[1:0] = 01. The state control register 2 selects the targeted next state whilst in State2. The matches refer to the match channels of the comparator match control logic as depicted in Figure 8-1 and described in Section 8.3.2.8.1, "Debug Comparator Control Register (DBGXCTL). Comparators must be enabled by setting the comparator enable bit in the associated DBGXCTL control register.

#### Table 8-17. DBGSCR2 Field Descriptions

| Field          | Description                                                                             |

|----------------|-----------------------------------------------------------------------------------------|

| 3–0<br>SC[3:0] | These bits select the targeted next state whilst in State2, based upon the match event. |

#### Table 8-18. State2 — Sequencer Next State Selection

| SC[3:0] | Description (Unspecified matches have no effect) |  |  |  |

|---------|--------------------------------------------------|--|--|--|

| 0000    | Match0 to State1 Match2 to State3.               |  |  |  |

| 0001    | Match1 to State3                                 |  |  |  |

| 0010    | Match2 to State3                                 |  |  |  |

| 0011    | Match1 to State3 Match0 Final State              |  |  |  |

| 0100    | Match1 to State1 Match2 to State3.               |  |  |  |

# 10.5 Resets

## 10.5.1 General

All reset sources are listed in Table 10-26. Refer to MCU specification for related vector addresses and priorities.

| Reset Source            | Local Enable                 |

|-------------------------|------------------------------|

| Power-On Reset (POR)    | None                         |

| Low Voltage Reset (LVR) | None                         |

| External pin RESET      | None                         |

| Illegal Address Reset   | None                         |

| Clock Monitor Reset     | OSCE Bit in CPMUOSC register |

| COP Reset               | CR[2:0] in CPMUCOP register  |

| Table 10-26 | . Reset | Summary |

|-------------|---------|---------|

|-------------|---------|---------|

## 10.5.2 Description of Reset Operation

Upon detection of any reset of Table 10-26, an internal circuit drives the RESET pin low for 512 PLLCLK cycles. After 512 PLLCLK cycles the RESET pin is released. The reset generator of the S12CPMU waits for additional 256 PLLCLK cycles and then samples the RESET pin to determine the originating source. Table 10-27 shows which vector will be fetched.

| Table 10-27. Res | set Vector Selection |

|------------------|----------------------|

|------------------|----------------------|

| Sampled RESET Pin<br>(256 cycles after<br>release) | Oscillator monitor<br>fail pending | COP<br>time out<br>pending | Vector Fetch                                              |

|----------------------------------------------------|------------------------------------|----------------------------|-----------------------------------------------------------|

| 1                                                  | 0                                  | 0                          | POR<br>LVR<br>Illegal Address Reset<br>External pin RESET |

| 1                                                  | 1                                  | Х                          | Clock Monitor Reset                                       |

| 1                                                  | 0                                  | 1                          | COP Reset                                                 |

| 0                                                  | X                                  | Х                          | POR<br>LVR<br>Illegal Address Reset<br>External pin RESET |

## NOTE

While System Reset is asserted the PLLCLK runs with the frequency  $\mathbf{f}_{\text{VCORST}}$

# 13.1 Introduction

The ADC10B12C is a 12-channel, 10-bit, multiplexed input successive approximation analog-to-digital converter. Refer to device electrical specifications for ATD accuracy.

# 13.1.1 Features

- 8-, 10-bit resolution.

- Automatic return to low power after conversion sequence

- Automatic compare with interrupt for higher than or less/equal than programmable value

- Programmable sample time.

- Left/right justified result data.

- External trigger control.

- Sequence complete interrupt.

- Analog input multiplexer for 8 analog input channels.

- Special conversions for VRH, VRL, (VRL+VRH)/2.

- 1-to-12 conversion sequence lengths.

- Continuous conversion mode.

- Multiple channel scans.

- Configurable external trigger functionality on any AD channel or any of four additional trigger inputs. The four additional trigger inputs can be chip external or internal. Refer to device specification for availability and connectivity.

- Configurable location for channel wrap around (when converting multiple channels in a sequence).

edge or level sensitive with polarity control. Table 14-23 gives a brief description of the different combinations of control bits and their effect on the external trigger function.

In order to avoid maybe false trigger events please enable the external digital input via ATDDIEN register first and in the following enable the external trigger mode by bit ETRIGE.

| ETRIGLE | ETRIGP | ETRIGE | SCAN | Description                                                                                       |

|---------|--------|--------|------|---------------------------------------------------------------------------------------------------|

| X       | х      | 0      | 0    | Ignores external trigger. Performs one conversion sequence and stops.                             |

| X       | х      | 0      | 1    | Ignores external trigger. Performs continuous conversion sequences.                               |

| 0       | 0      | 1      | х    | Trigger falling edge sensitive. Performs one conversion sequence per trigger.                     |

| 0       | 1      | 1      | х    | Trigger rising edge sensitive. Performs one conversion sequence per trigger.                      |

| 1       | 0      | 1      | Х    | Trigger low level sensitive. Performs<br>continuous conversions while trigger level<br>is active. |

| 1       | 1      | 1      | х    | Trigger high level sensitive. Performs continuous conversions while trigger level is active.      |

Table 14-23. External Trigger Control Bits

In either level or edge sensitive modes, the first conversion begins when the trigger is received.

Once ETRIGE is enabled a conversion must be triggered externally after writing to ATDCTL5 register.

During a conversion in edge sensitive mode, if additional trigger events are detected the overrun error flag ETORF is set.

If level sensitive mode is active and the external trigger de-asserts and later asserts again during a conversion sequence, this does not constitute an overrun. Therefore, the flag is not set. If the trigger is left active in level sensitive mode when a sequence is about to complete, another sequence will be triggered immediately.

# 14.4.2.2 General-Purpose Digital Port Operation

Each ATD input pin can be switched between analog or digital input functionality. An analog multiplexer makes each ATD input pin selected as analog input available to the A/D converter.

The pad of the ATD input pin is always connected to the analog input channel of the analog mulitplexer.

Each pad input signal is buffered to the digital port register.

This buffer can be turned on or off with the ATDDIEN register for each ATD input pin. This is important so that the buffer does not draw excess current when an ATD input pin is selected as analog input to the ADC12B12C.

| Input Signal<br>VRL = 0 Volts<br>VRH = 5.12 Volts | 8-Bit<br>Codes<br>(resolution=20mV) | 10-Bit<br>Codes<br>(resolution=5mV) | Reserved |

|---------------------------------------------------|-------------------------------------|-------------------------------------|----------|

| 5.120 Volts                                       | 255                                 | 1023                                | Reserved |

| 0.022<br>0.020<br>0.018<br>0.016                  | <br>1<br>1<br>1                     | <br>4<br>4<br>3                     |          |

| 0.014                                             | 1                                   | 3                                   |          |

| 0.012                                             | 1                                   | 2                                   |          |

| 0.010                                             | 1                                   | 2                                   |          |

| 0.008                                             | 0                                   | 2                                   |          |

| 0.006                                             | 0                                   | 1                                   |          |

| 0.004                                             | 0                                   | 1                                   |          |

| 0.003                                             | 0                                   | 1                                   |          |

| 0.002                                             | 0                                   | 0                                   |          |

| 0.000                                             | 0                                   | 0                                   |          |

#### Table 15-10. Conversion Sequence Length Coding

| S8C | S4C | S2C | S1C | Number of Conversions per Sequence |

|-----|-----|-----|-----|------------------------------------|

| 0   | 0   | 0   | 0   | 16                                 |

| 0   | 0   | 0   | 1   | 1                                  |

| 0   | 0   | 1   | 0   | 2                                  |

| 0   | 0   | 1   | 1   | 3                                  |

| 0   | 1   | 0   | 0   | 4                                  |

| 0   | 1   | 0   | 1   | 5                                  |

| 0   | 1   | 1   | 0   | 6                                  |

| 0   | 1   | 1   | 1   | 7                                  |

| 1   | 0   | 0   | 0   | 8                                  |

| 1   | 0   | 0   | 1   | 9                                  |

| 1   | 0   | 1   | 0   | 10                                 |

| 1   | 0   | 1   | 1   | 11                                 |

| 1   | 1   | 0   | 0   | 12                                 |

| 1   | 1   | 0   | 1   | 13                                 |

| 1   | 1   | 1   | 0   | 14                                 |

| 1   | 1   | 1   | 1   | 15                                 |

| FRZ1 | FRZ0 | Behavior in Freeze Mode |  |

|------|------|-------------------------|--|

| 0    | 0    | Continue conversion     |  |

#### Digital Analog Converter (DAC\_8B5V)

The configuration registers provide all required control bits for the DAC resistor network and for the operational amplifier.

The DAC resistor network generates the desired analog output voltage. The unbuffered voltage from the DAC resistor network output can be routed to the external DACU pin. When enabled, the buffered voltage from the operational amplifier output is available on the external AMP pin.

The operational amplifier is also stand alone usable.

Figure 17-1 shows the block diagram of the DAC\_8B5V module.

## 17.2.1 Features

The DAC\_8B5V module includes these distinctive features:

- 1 digital-analog converter channel with:

- 8 bit resolution

- full and reduced output voltage range

- buffered or unbuffered analog output voltage usable

- operational amplifier stand alone usable

## 17.2.2 Modes of Operation

The DAC\_8B5V module behaves as follows in the system power modes:

1. CPU run mode

The functionality of the DAC\_8B5V module is available.

2. CPU stop mode

Independent from the mode settings, the operational amplifier is disabled, switch S1 and S2 are open.

If the "Unbuffered DAC" mode was used before entering stop mode, then the DACU pin will reach VRH voltage level during stop mode.

The content of the configuration registers is unchanged.

## NOTE

After enabling and after return from CPU stop mode, the DAC\_8B5V module needs a settling time to get fully operational, see Settling time specification of dac\_8b5V\_analog\_ll18.

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | <ul> <li>Loop Select Bit — LOOPS enables loop operation. In loop operation, the RXD pin is disconnected from the SCI and the transmitter output is internally connected to the receiver input. Both the transmitter and the receiver must be enabled to use the loop function.</li> <li>0 Normal operation enabled</li> <li>1 Loop operation enabled</li> <li>The receiver input is determined by the RSRC bit.</li> </ul>                                                                                                                                              |

| 6<br>SCISWAI | <ul> <li>SCI Stop in Wait Mode Bit — SCISWAI disables the SCI in wait mode.</li> <li>0 SCI enabled in wait mode</li> <li>1 SCI disabled in wait mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>RSRC    | Receiver Source Bit — When LOOPS = 1, the RSRC bit determines the source for the receiver shift register input. See Table 20-5.         0 Receiver input internally connected to transmitter output         1 Receiver input connected externally to transmitter                                                                                                                                                                                                                                                                                                        |

| 4<br>M       | <ul> <li>Data Format Mode Bit — MODE determines whether data characters are eight or nine bits long.</li> <li>0 One start bit, eight data bits, one stop bit</li> <li>1 One start bit, nine data bits, one stop bit</li> </ul>                                                                                                                                                                                                                                                                                                                                          |

| 3<br>WAKE    | <ul> <li>Wakeup Condition Bit — WAKE determines which condition wakes up the SCI: a logic 1 (address mark) in the most significant bit position of a received data character or an idle condition on the RXD pin.</li> <li>0 Idle line wakeup</li> <li>1 Address mark wakeup</li> </ul>                                                                                                                                                                                                                                                                                 |

| 2<br>ILT     | Idle Line Type Bit — ILT determines when the receiver starts counting logic 1s as idle character bits. The<br>counting begins either after the start bit or after the stop bit. If the count begins after the start bit, then a string of<br>logic 1s preceding the stop bit may cause false recognition of an idle character. Beginning the count after the<br>stop bit avoids false idle character recognition, but requires properly synchronized transmissions.0Idle character bit count begins after start bit<br>11Idle character bit count begins after stop bit |

| 1<br>PE      | <ul> <li>Parity Enable Bit — PE enables the parity function. When enabled, the parity function inserts a parity bit in the most significant bit position.</li> <li>0 Parity function disabled</li> <li>1 Parity function enabled</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| 0<br>PT      | <ul> <li>Parity Type Bit — PT determines whether the SCI generates and checks for even parity or odd parity. With even parity, an even number of 1s clears the parity bit and an odd number of 1s sets the parity bit. With odd parity, an odd number of 1s clears the parity bit and an even number of 1s sets the parity bit.</li> <li>0 Even parity</li> <li>1 Odd parity</li> </ul>                                                                                                                                                                                 |

#### Table 20-5. Loop Functions

| LOOPS | RSRC | Function                                                                 |

|-------|------|--------------------------------------------------------------------------|

| 0     | х    | Normal operation                                                         |

| 1     | 0    | Loop mode with transmitter output internally connected to receiver input |

| 1     | 1    | Single-wire mode with TXD pin connected to receiver input                |

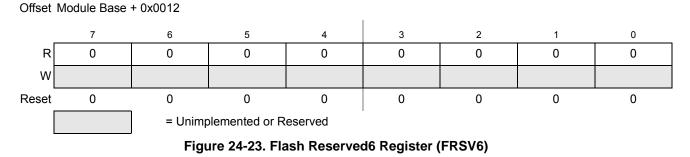

#### 16 KByte Flash Module (S12FTMRG16K1V1)

All bits in the FRSV6 register read 0 and are not writable.

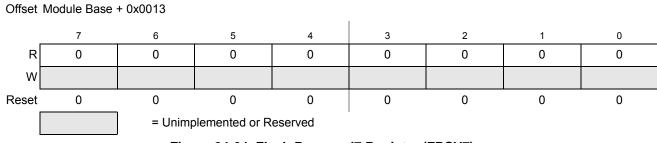

## 24.3.2.19 Flash Reserved7 Register (FRSV7)

This Flash register is reserved for factory testing.

All bits in the FRSV7 register read 0 and are not writable.

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_F800-0x3_FFFF    | 2 Kbytes       |

| 01        | 0x3_F000-0x3_FFFF    | 4 Kbytes       |

| 10        | 0x3_E000-0x3_FFFF    | 8 Kbytes       |

| 11        | 0x3_C000-0x3_FFFF    | 16 Kbytes      |

| Table 28-19. | P-Flash    | Protection   | Higher  | Address Range |

|--------------|------------|--------------|---------|---------------|

|              | 1 1 10.511 | 1 1010011011 | ingilei | Address Runge |

#### Table 28-20. P-Flash Protection Lower Address Range

| FPLS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_8000-0x3_83FF    | 1 Kbyte        |

| 01        | 0x3_8000-0x3_87FF    | 2 Kbytes       |

| 10        | 0x3_8000-0x3_8FFF    | 4 Kbytes       |

| 11        | 0x3_8000-0x3_9FFF    | 8 Kbytes       |

All possible P-Flash protection scenarios are shown in Figure 28-14. Although the protection scheme is loaded from the Flash memory at global address 0x3\_FFOC during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

#### 128 KByte Flash Module (S12FTMRG128K1V1)

#### **Electrical Characteristics**

1

| Rating                                                                                                           | Symbol                           | Min        | Тур     | Max        | Unit |

|------------------------------------------------------------------------------------------------------------------|----------------------------------|------------|---------|------------|------|

| Temperature Option V<br>Operating ambient temperature range <sup>1</sup><br>Operating junction temperature range | T <sub>A</sub><br>T <sub>J</sub> | 40<br>40   | 27      | 105<br>125 | °C   |

| Temperature Option M<br>Operating ambient temperature range <sup>1</sup><br>Operating junction temperature range | T <sub>A</sub><br>T <sub>J</sub> | 40<br>40   | 27<br>— | 125<br>150 | °C   |

| Temperature Option W<br>Operating ambient temperature range <sup>1</sup><br>Operating junction temperature range | T <sub>A</sub><br>T <sub>J</sub> | -40<br>-40 | 27<br>— | 150<br>160 | °C   |

#### Table A-4. Operating Conditions

Please refer to Section A.1.8, "Power Dissipation and Thermal Characteristics" for more details about the relation between ambient temperature  $T_A$  and device junction temperature  $T_J$ .

### NOTE

Operation is guaranteed when powering down until low voltage reset assertion.

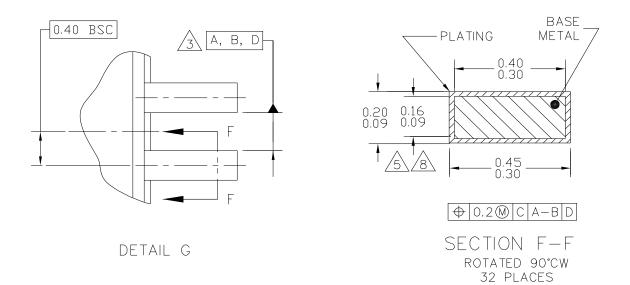

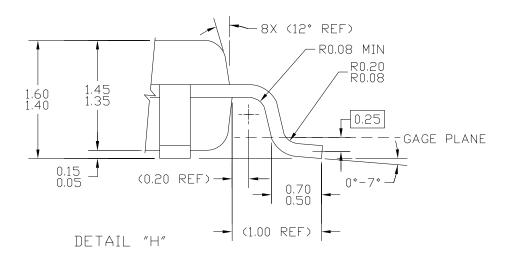

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE   |                          | PRINT VERSION NO | IT TO SCALE |

|---------------------------------------------------------|----------------------|--------------------------|------------------|-------------|

| TITLE:                                                  |                      | DOCUMENT NO: 98ASH70029A |                  | RE∨: D      |

| LOW PROFILE QUAD FLAT PA                                | CASE NUMBER: 873A-03 |                          | 19 MAY 2005      |             |

| 32 LEAD, 0.8 PITCH (7 X                                 | STANDARD: JE         | DEC MS-026 BBA           |                  |             |