Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2010.0                     |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | 12V1                                                         |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 25MHz                                                        |

| Connectivity               | IrDA, LINbus, SCI, SPI                                       |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 40                                                           |

| Program Memory Size        | 48KB (48K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 1.5K x 8                                                     |

| RAM Size                   | 4K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                 |

| Data Converters            | A/D 12x10b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 48-LQFP                                                      |

| Supplier Device Package    | 48-LQFP (7x7)                                                |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s12gn48f0vlfr |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Port                      | 20 TSSOP | 32 LQFP | 48 LQFP<br>48 QFN | 64 LQFP | 100 LQFP | KGD (Die) |

|---------------------------|----------|---------|-------------------|---------|----------|-----------|

| Sum of Ports              | 14       | 26      | 40                | 54      | 86       | 86        |

| I/O Power Pairs VDDX/VSSX | 1/1      | 1/1     | 1/1               | 1/1     | 3/3      | 3/3       |

Table 1-6. Port Availability by Package Option

### NOTE

To avoid current drawn from floating inputs, the input buffers of all non-bonded pins are disabled.

# 1.7.2 Detailed Signal Descriptions

This section describes the signal properties. The relation between signals and package pins is described in section 1.8 Device Pinouts.

# 1.7.2.1 **RESET** — External Reset Signal

The  $\overline{\text{RESET}}$  signal is an active low bidirectional control signal. It acts as an input to initialize the MCU to a known start-up state, and an output when an internal MCU function causes a reset. The  $\overline{\text{RESET}}$  pin has an internal pull-up device.

# 1.7.2.2 TEST — Test Pin

This input only pin is reserved for factory test. This pin has an internal pull-down device.

### NOTE

The TEST pin must be tied to ground in all applications.

## 1.7.2.3 BKGD / MODC — Background Debug and Mode Pin

The BKGD/MODC pin is used as a pseudo-open-drain pin for the background debug communication. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODC bit at the rising edge of  $\overrightarrow{\text{RESET}}$ . The BKGD pin has an internal pull-up device.

# 1.7.2.4 EXTAL, XTAL — Oscillator Signal

EXTAL and XTAL are the crystal driver and external clock signals. On reset all the device clocks are derived from the internal reference clock. XTAL is the oscillator output.

# 1.7.2.5 PAD[15:0] / KWAD[15:0] — Port AD Input Pins of ADC

PAD[15:0] are general-purpose input or output signals. These signals can have a pull-up or pull-down device selected and enabled on per signal basis. Out of reset the pull devices are disabled.

|                      | < 0   | Fund<br>owestPRIO | ction<br>RITYhighe | Power        | Internal Pull<br>Resistor |               |                |

|----------------------|-------|-------------------|--------------------|--------------|---------------------------|---------------|----------------|

| Wire Bond<br>Die Pad | Pin   | 2nd<br>Func.      | 3rd<br>Func.       | 4th<br>Func. | Supply                    | CTRL          | Reset<br>State |

| 56                   | PAD8  | KWAD8             | AN8                | —            | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 57                   | PAD1  | KWAD1             | AN1                | —            | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 58                   | PAD9  | KWAD9             | AN9                | —            | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 59                   | PAD2  | KWAD2             | AN2                | —            | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 60                   | PAD10 | KWAD10            | AN10               | AMP1         | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 61                   | PAD3  | KWAD3             | AN3                |              | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 62                   | PAD11 | KWAD11            | AN11               | AMP0         | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 63                   | PAD4  | KWAD4             | AN4                |              | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 64                   | PAD12 | KWAD12            | AN12               |              | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 65                   | PAD5  | KWAD5             | AN5                |              | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 66                   | PAD13 | KWAD13            | AN13               | AMPM0        | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 67                   | PAD6  | KWAD6             | AN6                |              | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 68                   | PAD14 | KWAD14            | AN14               | AMPP0        | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 69                   | PAD7  | KWAD7             | AN7                |              | V <sub>DDA</sub>          | PER1AD/PPS1AD | Disabled       |

| 70                   | PAD15 | KWAD15            | AN15               | DACU0        | V <sub>DDA</sub>          | PER0AD/PPS0AD | Disabled       |

| 71                   | PC4   | _                 |                    |              | V <sub>DDA</sub>          | PUCR/PUPCE    | Disabled       |

| 72                   | PC5   | AMPM1             | _                  |              | V <sub>DDA</sub>          | PUCR/PUPCE    | Disabled       |

| 73                   | PC6   | AMPP1             | _                  |              | V <sub>DDA</sub>          | PUCR/PUPCE    | Disabled       |

| 74                   | PC7   | DACU1             | _                  |              | V <sub>DDA</sub>          | PUCR/PUPCE    | Disabled       |

| 75                   | VRH   |                   | _                  |              |                           | —             | _              |

| 76                   | VDDA  |                   | _                  |              |                           | —             | _              |

| 77                   | VSSA  | _                 |                    |              |                           | —             | _              |

| 78                   | PD0   | _                 |                    |              | V <sub>DDX</sub>          | PUCR/PUPDE    | Disabled       |

| 79                   | PD1   | _                 | _                  | _            | V <sub>DDX</sub>          | PUCR/PUPDE    | Disabled       |

| 80                   | PD2   | —                 | —                  | _            | V <sub>DDX</sub>          | PUCR/PUPDE    | Disabled       |

| 81                   | PD3   | _                 | _                  | _            | V <sub>DDX</sub>          | PUCR/PUPDE    | Disabled       |

| 82                   | PS0   | RXD0              | _                  | _            | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 83                   | PS1   | TXD0              | —                  |              | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

| 84                   | PS2   | RXD1              | _                  | _            | V <sub>DDX</sub>          | PERS/PPSS     | Up             |

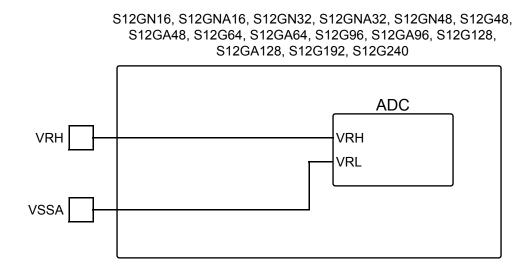

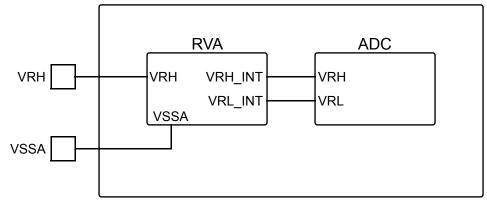

The S12GA192 and the S12GA240 contain a Reference Voltage Attenuator (RVA) module. The connection of the ADC's VRH/VRL inputs on these devices is shown in Figure 1-27.

S12GA192, S12GA240

Figure 1-27. ADC VRH/VRL Signal Connection

# 1.19 BDM Clock Source Connectivity

The BDM clock is mapped to the VCO clock divided by 8.

<sup>5</sup> Preset by factory.

<sup>6</sup> Routing register only available on G(A)240 and G(A)192 only. Takes only effect if the PKGCR is set to 100 LQFP.

# 2.4.2 Register Map

The following tables show the individual register maps of groups G1 (Table 2-19), G2 (Table 2-20) and G3 (Table 2-21).

### NOTE

To maintain SW compatibility write data to unimplemented register bits must be zero.

## 2.4.2.1 Block Register Map (G1)

| Global Address<br>Register Name |        | Bit 7 | 6                           | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|---------------------------------|--------|-------|-----------------------------|-------|-------|-------|-------|-------|-------|

| 0x0000<br>PORTA                 | R<br>W | PA7   | PA6                         | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| 0x0001<br>PORTB                 | R<br>W | PB7   | PB6                         | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   |

| 0x0002<br>DDRA                  | R<br>W | DDRA7 | DDRA6                       | DDRA5 | DDRA4 | DDRA3 | DDRA2 | DDRA1 | DDRA0 |

| 0x0003<br>DDRB                  | R<br>W | DDRB7 | DDRB6                       | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 |

| 0x0004<br>PORTC                 | R<br>W | PC7   | PC6                         | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| 0x0005<br>PORTD                 | R<br>W | PD7   | PD6                         | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| 0x0006<br>DDRC                  | R<br>W | DDRC7 | DDRC6                       | DDRC5 | DDRC4 | DDRC3 | DDRC2 | DDRC1 | DDRC0 |

| 0x0007<br>DDRD                  | R      | DDRD7 | DDRD6                       | DDRD5 | DDRD4 | DDRD3 | DDRD2 | DDRD1 | DDRD0 |

| 0x0008<br>PORTE                 | R<br>W | 0     | 0                           | 0     | 0     | 0     | 0     | PE1   | PE0   |

| 0x0009<br>DDRE                  | R<br>W | 0     | 0                           | 0     | 0     | 0     | 0     | DDRE1 | DDRE0 |

|                                 | [      |       | = Unimplemented or Reserved |       |       |       |       |       |       |

#### Table 2-19. Block Register Map (G1)

| Field | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Port AD input data—<br>A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

#### Table 2-78. PTI1AD Register Field Descriptions

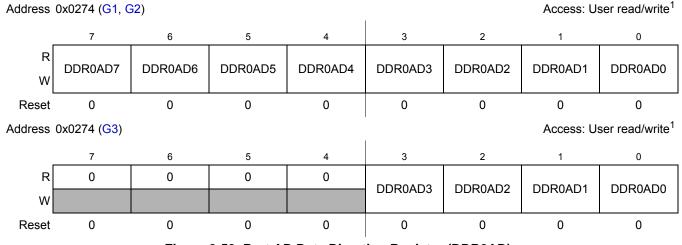

### 2.4.3.53 Port AD Data Direction Register (DDR0AD)

Figure 2-53. Port AD Data Direction Register (DDR0AD)

<sup>1</sup> Read: Anytime

Write: Anytime

#### Table 2-79. DDR0AD Register Field Descriptions

| Field         | Description                                                                                              |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7-0<br>DDR0AD | <b>Port AD data direction</b> —<br>This bit determines whether the associated pin is an input or output. |  |  |  |  |

|               | 1 Associated pin configured as output<br>0 Associated pin configured as input                            |  |  |  |  |

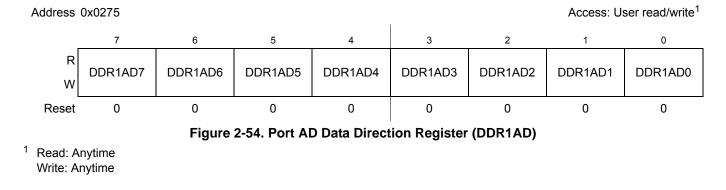

### 2.4.3.54 Port AD Data Direction Register (DDR1AD)

#### S12S Debug Module (S12SDBGV2)

| Bit       | Description                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------|

| 0<br>PC16 | <b>Program Counter bit 16</b> — In Normal and Loop1 mode this bit corresponds to program counter bit 16. |

#### Table 8-39. PCH Field Descriptions (continued)

## 8.4.5.4 Trace Buffer Organization (Compressed Pure PC mode)

Table 8-40. Trace Buffer Organization Example (Compressed PurePC mode)

| Mode         | Line<br>Number | 2-bits  | 6-bits                           | 6-bits                               | 6-bits  |  |  |  |

|--------------|----------------|---------|----------------------------------|--------------------------------------|---------|--|--|--|

| WOUE         |                | Field 3 | Field 2                          | Field 1                              | Field 0 |  |  |  |

|              | Line 1         | 00      | PC1                              | PC1 (Initial 18-bit PC Base Address) |         |  |  |  |

|              | Line 2         | 11      | PC4                              | PC3                                  | PC2     |  |  |  |

| Compressed   | Line 3         | 01      | 0                                | 0                                    | PC5     |  |  |  |

| Pure PC Mode | Line 4         | 00      | PC6 (New 18-bit PC Base Address) |                                      |         |  |  |  |

|              | Line 5         | 10      | 0                                | PC8                                  | PC7     |  |  |  |

|              | Line 6         | 00      | PC9 (New 18-bit PC Base Address) |                                      |         |  |  |  |

### NOTE

Configured for end aligned triggering in compressed PurePC mode, then after rollover it is possible that the oldest base address is overwritten. In this case all entries between the pointer and the next base address have lost their base address following rollover. For example in Table 8-40 if one line of rollover has occurred, Line 1, PC1, is overwritten with a new entry. Thus the entries on Lines 2 and 3 have lost their base address. For reconstruction of program flow the first base address following the pointer must be used, in the example, Line 4. The pointer points to the oldest entry, Line 2.

### Field3 Bits in Compressed Pure PC Modes

Table 8-41. Compressed Pure PC Mode Field 3 Information Bit Encoding

| INF1 | INF0 | TRACE BUFFER ROW CONTENT                                                              |  |  |  |

|------|------|---------------------------------------------------------------------------------------|--|--|--|

| 0    | 0    | Base PC address TB[17:0] contains a full PC[17:0] value                               |  |  |  |

| 0    | 1    | Trace Buffer[5:0] contain incremental PC relative to base address zero value          |  |  |  |

| 1    | 0    | Trace Buffer[11:0] contain next 2 incremental PCs relative to base address zero value |  |  |  |

| 1    | 1    | Trace Buffer[17:0] contain next 3 incremental PCs relative to base address zero value |  |  |  |

Each time that PC[17:6] differs from the previous base PC[17:6], then a new base address is stored. The base address zero value is the lowest address in the 64 address range

The first line of the trace buffer always gets a base PC address, this applies also on rollover.

# 8.4.6 Tagging

A tag follows program information as it advances through the instruction queue. When a tagged instruction reaches the head of the queue a tag hit occurs and can initiate a state sequencer transition.

Each comparator control register features a TAG bit, which controls whether the comparator match causes a state sequencer transition immediately or tags the opcode at the matched address. If a comparator is enabled for tagged comparisons, the address stored in the comparator match address registers must be an opcode address.

Using Begin trigger together with tagging, if the tagged instruction is about to be executed then the transition to the next state sequencer state occurs. If the transition is to the Final State, tracing is started. Only upon completion of the tracing session can a breakpoint be generated. Using End alignment, when the tagged instruction is about to be executed and the next transition is to Final State then a breakpoint is generated immediately, before the tagged instruction is carried out.

R/W monitoring, access size (SZ) monitoring and data bus monitoring are not useful if tagging is selected, since the tag is attached to the opcode at the matched address and is not dependent on the data bus nor on the type of access. Thus these bits are ignored if tagging is selected.

When configured for range comparisons and tagging, the ranges are accurate only to word boundaries.

Tagging is disabled when the BDM becomes active.

## 8.4.7 Breakpoints

It is possible to generate breakpoints from channel transitions to final state or using software to write to the TRIG bit in the DBGC1 register.

### 8.4.7.1 Breakpoints From Comparator Channels

Breakpoints can be generated when the state sequencer transitions to the Final State. If configured for tagging, then the breakpoint is generated when the tagged opcode reaches the execution stage of the instruction queue.

If a tracing session is selected by the TSOURCE bit, breakpoints are requested when the tracing session has completed, thus if Begin aligned triggering is selected, the breakpoint is requested only on completion of the subsequent trace (see Table 8-42). If no tracing session is selected, breakpoints are requested immediately.

If the BRK bit is set, then the associated breakpoint is generated immediately independent of tracing trigger alignment.

| BRK | TALIGN | DBGBRK | Breakpoint Alignment                                            |

|-----|--------|--------|-----------------------------------------------------------------|

| 0   | 0      | 0      | Fill Trace Buffer until trigger then disarm (no breakpoints)    |

| 0   | 0      | 1      | Fill Trace Buffer until trigger, then breakpoint request occurs |

| 0   | 1      | 0      | Start Trace Buffer at trigger (no breakpoints)                  |

| Table 8-42. Breakpoint Setup | For CPU Breakpoints |

|------------------------------|---------------------|

|------------------------------|---------------------|

• The Internal Reference Clock (IRC1M) provides a1MHz clock.

# 10.1.1 Features

The Pierce Oscillator (XOSCLCP) contains circuitry to dynamically control current gain in the output amplitude. This ensures a signal with low harmonic distortion, low power and good noise immunity.

- Supports quartz crystals or ceramic resonators from 4MHz to 16MHz.

- High noise immunity due to input hysteresis and spike filtering.

- Low RF emissions with peak-to-peak swing limited dynamically

- Transconductance (gm) sized for optimum start-up margin for typical crystals

- Dynamic gain control eliminates the need for external current limiting resistor

- Integrated resistor eliminates the need for external bias resistor.

- Low power consumption: Operates from internal 1.8V (nominal) supply, Amplitude control limits power

The Voltage Regulator (IVREG) has the following features:

- Input voltage range from 3.13V to 5.5V

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR)

- Low-voltage reset (LVR)

The Phase Locked Loop (PLL) has the following features:

- highly accurate and phase locked frequency multiplier

- Configurable internal filter for best stability and lock time.

- Frequency modulation for defined jitter and reduced emission

- Automatic frequency lock detector

- Interrupt request on entry or exit from locked condition

- Reference clock either external (crystal) or internal square wave (1MHz IRC1M) based.

- PLL stability is sufficient for LIN communication, even if using IRC1M as reference clock

The Internal Reference Clock (IRC1M) has the following features:

- Frequency trimming

- (A factory trim value for 1MHz is loaded from Flash Memory into the IRCTRIM register after reset, which can be overwritten by application if required)

- Temperature Coefficient (TC) trimming. (A factory trim value is loaded from Flash Memory into the IRCTRIM register to turned off TC trimming after reset. Application can trim the TC if required by overwriting the IRCTRIM register).

•

Other features of the S12CPMU include

• Clock monitor to detect loss of crystal

## 11.1.1 Features

- 8-, 10-bit resolution.

- Automatic return to low power after conversion sequence

- Automatic compare with interrupt for higher than or less/equal than programmable value

- Programmable sample time.

- Left/right justified result data.

- External trigger control.

- Sequence complete interrupt.

- Analog input multiplexer for 8 analog input channels.

- Special conversions for VRH, VRL, (VRL+VRH)/2.

- 1-to-8 conversion sequence lengths.

- Continuous conversion mode.

- Multiple channel scans.

- Configurable external trigger functionality on any AD channel or any of four additional trigger inputs. The four additional trigger inputs can be chip external or internal. Refer to device specification for availability and connectivity.

- Configurable location for channel wrap around (when converting multiple channels in a sequence).

Analog-to-Digital Converter (ADC10B12CV2)

# 13.3.2.7 ATD Status Register 0 (ATDSTAT0)

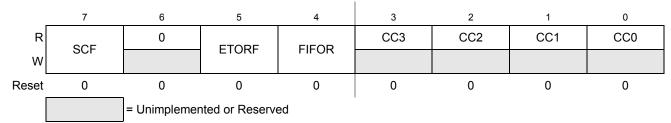

This register contains the Sequence Complete Flag, overrun flags for external trigger and FIFO mode, and the conversion counter.

Module Base + 0x0006

Figure 13-9. ATD Status Register 0 (ATDSTAT0)

Read: Anytime

Write: Anytime (No effect on (CC3, CC2, CC1, CC0))

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SCF   | Sequence Complete Flag — This flag is set upon completion of a conversion sequence. If conversion sequences are continuously performed (SCAN=1), the flag is set after each one is completed. This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to SCF</li> <li>B) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>C) If AFFC=1 and a result register is read</li> <li>Conversion sequence not completed</li> <li>Conversion sequence has completed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5<br>ETORF | <ul> <li>External Trigger Overrun Flag — While in edge sensitive mode (ETRIGLE=0), if additional active edges are detected while a conversion sequence is in process the overrun flag is set. This flag is cleared when one of the following occurs:         <ul> <li>A) Write "1" to ETORF</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> </li> <li>No External trigger overrun error has occurred</li> <li>External trigger overrun error has occurred</li> </ul>                                                                                                                                                                                                                                                                                                                    |

| 4<br>FIFOR | Result Register Overrun Flag — This bit indicates that a result register has been written to before its associated conversion complete flag (CCF) has been cleared. This flag is most useful when using the FIFO mode because the flag potentially indicates that result registers are out of sync with the input channels. However, it is also practical for non-FIFO modes, and indicates that a result register has been overwritten before it has been read (i.e. the old data has been lost). This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to FIFOR</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> </ul> <li>No overrun has occurred</li> <li>Overrun condition exists (result register has been written while associated CCFx flag was still set)</li> |

#### Scalable Controller Area Network (S12MSCANV3)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>SLPAK  | <ul> <li>Sleep Mode Acknowledge — This flag indicates whether the MSCAN module has entered sleep mode (see Section 18.4.5.5, "MSCAN Sleep Mode"). It is used as a handshake flag for the SLPRQ sleep mode request. Sleep mode is active when SLPRQ = 1 and SLPAK = 1. Depending on the setting of WUPE, the MSCAN will clear the flag if it detects activity on the CAN bus while in sleep mode.</li> <li>0 Running — The MSCAN operates normally</li> <li>1 Sleep mode active — The MSCAN has entered sleep mode</li> </ul>                                                                                                  |

| 0<br>INITAK | <ul> <li>Initialization Mode Acknowledge — This flag indicates whether the MSCAN module is in initialization mode (see Section 18.4.4.5, "MSCAN Initialization Mode"). It is used as a handshake flag for the INITRQ initialization mode request. Initialization mode is active when INITRQ = 1 and INITAK = 1. The registers CANCTL1, CANBTR0, CANBTR1, CANIDAC, CANIDAR0–CANIDAR7, and CANIDMR0–CANIDMR7 can be written only by the CPU when the MSCAN is in initialization mode.</li> <li>Running — The MSCAN operates normally</li> <li>Initialization mode active — The MSCAN has entered initialization mode</li> </ul> |

#### Table 18-4. CANCTL1 Register Field Descriptions (continued)

## 18.3.2.3 MSCAN Bus Timing Register 0 (CANBTR0)

The CANBTR0 register configures various CAN bus timing parameters of the MSCAN module.

Module Base + 0x0002

Access: User read/write<sup>1</sup>

|        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

| R<br>W | SJW1 | SJW0 | BRP5 | BRP4 | BRP3 | BRP2 | BRP1 | BRP0 |

| Reset: | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### Figure 18-6. MSCAN Bus Timing Register 0 (CANBTR0)

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 18-5. CANBTR0 Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                           |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7-6<br>SJW[1:0] | <b>Synchronization Jump Width</b> — The synchronization jump width defines the maximum number of time quanta (Tq) clock cycles a bit can be shortened or lengthened to achieve resynchronization to data transitions on the CAN bus (see Table 18-6). |  |  |

| 5-0<br>BRP[5:0] | <b>Baud Rate Prescaler</b> — These bits determine the time quanta (Tq) clock which is used to build up the bit timing (see Table 18-7).                                                                                                               |  |  |

#### Table 18-6. Synchronization Jump Width

| SJW1 | SJW0 | Synchronization Jump Width |

|------|------|----------------------------|

| 0    | 0    | 1 Tq clock cycle           |

| 0    | 1    | 2 Tq clock cycles          |

| 1    | 0    | 3 Tq clock cycles          |

| 1    | 1    | 4 Tq clock cycles          |

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0        | Abort Request — The CPU sets the ABTRQx bit to request that a scheduled message buffer (TXEx = 0) be aborted. The MSCAN grants the request if the message has not already started transmission, or if the transmission is not successful (lost arbitration or error). When a message is aborted, the associated TXE (see Section 18.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and abort acknowledge flags (ABTAK, see Section 18.3.2.10, "MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)") are set and a transmit interrupt occurs if enabled. The CPU cannot reset ABTRQx. ABTRQx is reset whenever the associated TXE flag is set. |

| ABTRQ[2:0] | 0 No abort request 1 Abort request pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Table 18-15. CANTARQ Register Field Descriptions

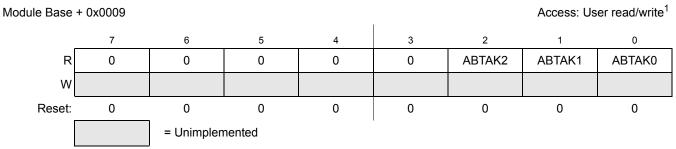

### 18.3.2.10 MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

The CANTAAK register indicates the successful abort of a queued message, if requested by the appropriate bits in the CANTARQ register.

#### Figure 18-13. MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

Read: Anytime

Write: Unimplemented

#### NOTE

The CANTAAK register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1).

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0<br>ABTAK[2:0] | <ul> <li>Abort Acknowledge — This flag acknowledges that a message was aborted due to a pending abort request from the CPU. After a particular message buffer is flagged empty, this flag can be used by the application software to identify whether the message was aborted successfully or was sent anyway. The ABTAKx flag is cleared whenever the corresponding TXE flag is cleared.</li> <li>0 The message was not aborted.</li> <li>1 The message was aborted.</li> </ul> |

## 18.3.2.11 MSCAN Transmit Buffer Selection Register (CANTBSEL)

The CANTBSEL register allows the selection of the actual transmit message buffer, which then will be accessible in the CANTXFG register space.

#### 32 KByte Flash Module (S12FTMRG32K1V1)

All bits in the FRSV7 register read 0 and are not writable.

# 25.4 Functional Description

### 25.4.1 Modes of Operation

The FTMRG32K1 module provides the modes of operation normal and special . The operating mode is determined by module-level inputs and affects the FCLKDIV, FCNFG, and EEPROT registers (see Table 25-27).

## 25.4.2 IFR Version ID Word

The version ID word is stored in the IFR at address  $0x0_40B6$ . The contents of the word are defined in Table 25-26.

| [15:4]   | [3:0]  |  |

|----------|--------|--|

| Reserved | VERNUM |  |

| Table 25-26. | IFR Y | Version | ID | Fields |

|--------------|-------|---------|----|--------|

|--------------|-------|---------|----|--------|

#### 32 KByte Flash Module (S12FTMRG32K1V1)

8. Reset the MCU

# 27.5.3 Mode and Security Effects on Flash Command Availability

The availability of Flash module commands depends on the MCU operating mode and security state as shown in Table 27-27.

# 27.6 Initialization

On each system reset the flash module executes an initialization sequence which establishes initial values for the Flash Block Configuration Parameters, the FPROT and EEPROT protection registers, and the FOPT and FSEC registers. The initialization routine reverts to built-in default values that leave the module in a fully protected and secured state if errors are encountered during execution of the reset sequence. If a double bit fault is detected during the reset sequence, both MGSTAT bits in the FSTAT register will be set.

CCIF is cleared throughout the initialization sequence. The Flash module holds off all CPU access for a portion of the initialization sequence. Flash reads are allowed once the hold is removed. Completion of the initialization sequence is marked by setting CCIF high which enables user commands.

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

# 29.4.6.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of the P-Flash or EEPROM block.

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the Table 29-57. Set Field Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                       |  |  |

|-------------|--------------------------------------------------------|--|--|

| 000         | 0x0E Flash block selection code [1:0]. See Table 29-34 |  |  |

| 001         | Margin level setting.                                  |  |  |

field margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM field margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash field margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply field margin levels to the P-Flash block only.

Valid margin level settings for the Set Field Margin Level command are defined in Table 29-58.

| CCOB<br>(CCOBIX=001) | Level Description                 |  |  |

|----------------------|-----------------------------------|--|--|

| 0x0000               | Return to Normal Level            |  |  |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |  |  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |  |  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |  |  |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |  |  |

Table 29-58. Valid Set Field Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

| Field              | Description                                                                                                                                                                                                                                                                                     |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                            |  |  |  |

| 2<br>RSVD          | <b>Reserved Bit</b> — This bit is reserved and always reads 0.                                                                                                                                                                                                                                  |  |  |  |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 30.4.6, "Flash Command Description," and Section 30.6, "Initialization" for details. |  |  |  |

#### Table 30-15. FSTAT Field Descriptions (continued)

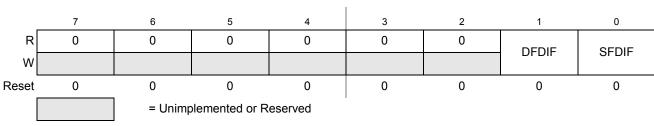

## 30.3.2.8 Flash Error Status Register (FERSTAT)

Offset Module Base + 0x0007

The FERSTAT register reflects the error status of internal Flash operations.

#### Figure 30-12. Flash Error Status Register (FERSTAT)

All flags in the FERSTAT register are readable and only writable to clear the flag.

#### Table 30-16. FERSTAT Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1<br>DFDIF | <ul> <li>Double Bit Fault Detect Interrupt Flag — The setting of the DFDIF flag indicates that a double bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The DFDIF flag is cleared by writing a 1 to DFDIF. Writing a 0 to DFDIF has no effect on DFDIF.<sup>2</sup></li> <li>0 No double bit fault detected</li> <li>1 Double bit fault detected or a Flash array read operation returning invalid data was attempted while command running</li> </ul>                                                                        |  |  |  |  |

| 0<br>SFDIF | <ul> <li>Single Bit Fault Detect Interrupt Flag — With the IGNSF bit in the FCNFG register clear, the SFDIF flag indicates that a single bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The SFDIF flag is cleared by writing a 1 to SFDIF. Writing a 0 to SFDIF has no effect on SFDIF.</li> <li>0 No single bit fault detected</li> <li>1 Single bit fault detected and corrected or a Flash array read operation returning invalid data was attempted operation returning invalid data was attempted operation.</li> </ul> |  |  |  |  |

The single bit fault and double bit fault flags are mutually exclusive for parity errors (an ECC fault occurrence can be either single fault or double fault but never both). A simultaneous access collision (Flash array read operation returning invalid data attempted while command running) is indicated when both SFDIF and DFDIF flags are high.

<sup>2</sup> There is a one cycle delay in storing the ECC DFDIF and SFDIF fault flags in this register. At least one NOP is required after a flash memory read before checking FERSTAT for the occurrence of ECC errors.

| Field              | Description                                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                            |  |  |  |  |

| 2<br>RSVD          | Reserved Bit — This bit is reserved and always reads 0.                                                                                                                                                                                                                                         |  |  |  |  |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 31.4.6, "Flash Command Description," and Section 31.6, "Initialization" for details. |  |  |  |  |

#### Table 31-15. FSTAT Field Descriptions (continued)

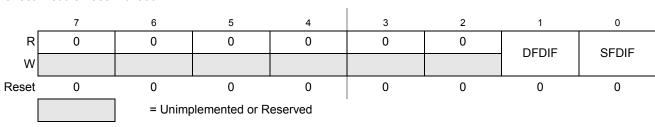

## 31.3.2.8 Flash Error Status Register (FERSTAT)

Offset Module Base + 0x0007

The FERSTAT register reflects the error status of internal Flash operations.

All flags in the FERSTAT register are readable and only writable to clear the flag.

#### Table 31-16. FERSTAT Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIF | <ul> <li>Double Bit Fault Detect Interrupt Flag — The setting of the DFDIF flag indicates that a double bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The DFDIF flag is cleared by writing a 1 to DFDIF. Writing a 0 to DFDIF has no effect on DFDIF.<sup>2</sup></li> <li>No double bit fault detected</li> <li>Double bit fault detected or a Flash array read operation returning invalid data was attempted while command running</li> </ul>                                                                                       |

| 0<br>SFDIF | <ul> <li>Single Bit Fault Detect Interrupt Flag — With the IGNSF bit in the FCNFG register clear, the SFDIF flag indicates that a single bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The SFDIF flag is cleared by writing a 1 to SFDIF. Writing a 0 to SFDIF has no effect on SFDIF.</li> <li>0 No single bit fault detected</li> <li>1 Single bit fault detected and corrected or a Flash array read operation returning invalid data was attempted operation returning invalid data was attempted while command running</li> </ul> |

The single bit fault and double bit fault flags are mutually exclusive for parity errors (an ECC fault occurrence can be either single fault or double fault but never both). A simultaneous access collision (Flash array read operation returning invalid data attempted while command running) is indicated when both SFDIF and DFDIF flags are high.

<sup>2</sup> There is a one cycle delay in storing the ECC DFDIF and SFDIF fault flags in this register. At least one NOP is required after a flash memory read before checking FERSTAT for the occurrence of ECC errors.

**Electrical Characteristics**

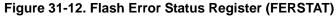

Figure A-1. ADC Accuracy Definitions

### NOTE

Figure A-1 shows only definitions, for specification values refer to Table A-21 and Table A-26.

NOTES:

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUM PLANE AB IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS T, U, AND Z TO BE DETERMINED AT DATUM PLANE AB.

VIMENSIONS TO BE DETERMINED AT SEATING PLANE AC.

DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.250 PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE AB.

THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.350.

- 8. MINIMUM SOLDER PLATE THICKNESS SHALL BE 0.0076.

- 9. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |  | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--|--------------|------------------|-------------|

| TITLE:                                                  |  |              | : 98ASH00962A    | REV: G      |

| LQFP, 48 LEAD, 0.                                       |  | CASE NUMBER  | 8: 932–03        | 14 APR 2005 |

| (7.0 X 7.0 X                                            |  | STANDARD: JE | DEC MS-026-BBC   |             |