Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 40                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 1K x 8                                                                  |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                            |

| Data Converters            | A/D 8x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12gna32f0wlf |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 9 Security (S12XS9SECV2)

| 9.1 | Introduc | ction                                    | . 347 |

|-----|----------|------------------------------------------|-------|

|     | 9.1.1    | Features                                 | . 347 |

|     | 9.1.2    | Modes of Operation                       | . 347 |

|     | 9.1.3    | Securing the Microcontroller             | . 348 |

|     | 9.1.4    | Operation of the Secured Microcontroller | . 349 |

|     | 9.1.5    | Unsecuring the Microcontroller           | . 350 |

|     | 9.1.6    | Reprogramming the Security Bits          | . 350 |

|     | 9.1.7    | Complete Memory Erase (Special Modes)    | . 351 |

# Chapter 10

# S12 Clock, Reset and Power Management Unit (S12CPMU)

| 10.1 | Introduction                                               | 353 |

|------|------------------------------------------------------------|-----|

|      | 10.1.1 Features                                            | 354 |

|      | 10.1.2 Modes of Operation                                  | 355 |

|      | 10.1.3 S12CPMU Block Diagram                               | 358 |

| 10.2 | Signal Description                                         | 359 |

|      | 10.2.1 <b>RESET</b>                                        | 359 |

|      | 10.2.2 EXTAL and XTAL                                      | 359 |

|      | 10.2.3 VDDR — Regulator Power Input Pin                    | 360 |

|      | 10.2.4 VSS — Ground Pin                                    |     |

|      | 10.2.5 VDDA, VSSA — Regulator Reference Supply Pins        | 360 |

|      | 10.2.6 VDDX, VSSX— Pad Supply Pins                         | 360 |

|      | 10.2.7 VDD — Internal Regulator Output Supply (Core Logic) | 361 |

|      | 10.2.8 VDDF — Internal Regulator Output Supply (NVM Logic) | 361 |

|      | 10.2.9 API_EXTCLK — API external clock output pin          | 361 |

| 10.3 | Memory Map and Registers                                   | 361 |

|      | 10.3.1 Module Memory Map                                   | 361 |

|      | 10.3.2 Register Descriptions                               | 363 |

| 10.4 | Functional Description                                     | 389 |

|      | 10.4.1 Phase Locked Loop with Internal Filter (PLL)        | 389 |

|      | 10.4.2 Startup from Reset                                  | 390 |

|      | 10.4.3 Stop Mode using PLLCLK as Bus Clock                 | 391 |

|      | 10.4.4 Full Stop Mode using Oscillator Clock as Bus Clock  |     |

|      | 10.4.5 External Oscillator                                 | 392 |

|      | 10.4.6 System Clock Configurations                         | 393 |

| 10.5 | Resets                                                     |     |

|      | 10.5.1 General                                             | 395 |

|      | 10.5.2 Description of Reset Operation                      | 395 |

|      | 10.5.3 Power-On Reset (POR)                                | 397 |

|      | 10.5.4 Low-Voltage Reset (LVR)                             | 397 |

| 10.6 | Interrupts                                                 | 398 |

|      | 10.6.1 Description of Interrupt Operation                  | 398 |

|             |                  | F<br>Pf      | unction<br>RIORITY | Power                       | Internal Pull<br>Resistor |                  |               |                |

|-------------|------------------|--------------|--------------------|-----------------------------|---------------------------|------------------|---------------|----------------|

| Package Pin | Pin              | 2nd<br>Func. | 3rd<br>Func.       | 4th<br>Func                 | 5th<br>Func               | Supply           | CTRL          | Reset<br>State |

| 4           | PE0 <sup>1</sup> | EXTAL        | _                  | _                           | _                         | _                | PUCR/PDPEE    | Down           |

| 5           | VSS              | _            |                    | _                           | —                         | _                | _             |                |

| 6           | PE1 <sup>1</sup> | XTAL         | _                  | _                           | —                         | _                | PUCR/PDPEE    | Down           |

| 7           | TEST             | _            | _                  | _                           | _                         | N.A.             | RESET pin     | Down           |

| 8           | BKGD             | MODC         | _                  | _                           | —                         | V <sub>DDX</sub> | PUCR/BKPUE    | Up             |

| 9           | PP0              | KWP0         | ETRIG0             | API_EXTC<br>LK              | PWM0                      | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 10          | PP1              | KWP1         | ETRIG1             | ECLKX2                      | PWM1                      | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 11          | PP2              | KWP2         | ETRIG2             | PWM2                        |                           | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 12          | PP3              | KWP3         | ETRIG3             | PWM3                        | _                         | V <sub>DDX</sub> | PERP/PPSP     | Disabled       |

| 13          | PT3              | IOC3         | —                  | —                           | _                         | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 14          | PT2              | IOC2         | _                  | _                           |                           | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 15          | PT1              | IOC1         | ĪRQ                | — — V <sub>DDX</sub> PERT/P |                           | PERT/PPST        | Disabled      |                |

| 16          | PT0              | IOC0         | XIRQ               | —                           | _                         | V <sub>DDX</sub> | PERT/PPST     | Disabled       |

| 17          | PAD0             | KWAD0        | AN0                | —                           | _                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 18          | PAD1             | KWAD1        | AN1                | —                           | —                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 19          | PAD2             | KWAD2        | AN2                | —                           | —                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 20          | PAD3             | KWAD3        | AN3                | —                           | —                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 21          | PAD4             | KWAD4        | AN4                | —                           | —                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 22          | PAD5             | KWAD5        | AN5                | ACMPO                       | —                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 23          | PAD6             | KWAD6        | AN6                | ACMPP                       | —                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 24          | PAD7             | KWAD7        | AN7                | ACMPM                       | —                         | V <sub>DDA</sub> | PER1AD/PPS1AD | Disabled       |

| 25          | PS0              | RXD0         | —                  | —                           | —                         | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 26          | PS1              | TXD0         | —                  | —                           | —                         | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 27          | PS4              | PWM4         | MISO0              | _                           | _                         | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 28          | PS5              | IOC4         | MOSI0              | —                           | —                         | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 29          | PS6              | IOC5         | SCK0               | _                           | —                         | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 30          | PS7              | API_EXTCLK   | ECLK               | PWM5                        | SS0                       | V <sub>DDX</sub> | PERS/PPSS     | Up             |

| 31          | PM0              | _            |                    | _                           | —                         | V <sub>DDX</sub> | PERM/PPSM     | Disabled       |

Table 1-9.

32-Pin LQFP OPinout for S12GN16 and S12GN32

|             |                  | <lowest< th=""><th>Function<br/>-PRIORITY-</th><th>Power</th><th colspan="3">Internal Pull<br/>Resistor</th></lowest<> | Function<br>-PRIORITY- | Power          | Internal Pull<br>Resistor |                  |            |                |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|---------------------------|------------------|------------|----------------|

| Package Pin | Pin              | 2nd<br>Func.                                                                                                           | 3rd<br>Func.           | 4th<br>Func    | 5th<br>Func               | Supply           | CTRL       | Reset<br>State |

| 1           | PJ6              | KWJ6                                                                                                                   | SCK2                   | _              | _                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 2           | PJ5              | KWJ5                                                                                                                   | MOSI2                  | _              | _                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 3           | PJ4              | KWJ4                                                                                                                   | MISO2                  | _              | _                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 4           | RESET            | _                                                                                                                      | —                      | _              | _                         | V <sub>DDX</sub> | PULLU      | P              |

| 5           | VDDX             |                                                                                                                        | _                      | _              | _                         |                  |            | _              |

| 6           | VDDR             | _                                                                                                                      | —                      | _              | _                         | —                |            | —              |

| 7           | VSSX             |                                                                                                                        | _                      | _              | _                         |                  | _          | _              |

| 8           | PE0 <sup>1</sup> | EXTAL                                                                                                                  | —                      | _              |                           | V <sub>DDX</sub> | PUCR/PDPEE | Down           |

| 9           | VSS              |                                                                                                                        | _                      | _              | _                         |                  | _          | _              |

| 10          | PE1 <sup>1</sup> | XTAL                                                                                                                   | —                      | _              | _                         | V <sub>DDX</sub> | PUCR/PDPEE | Down           |

| 11          | TEST             | _                                                                                                                      | —                      | _              | _                         | N.A.             | RESET pin  | Down           |

| 12          | PJ0              | KWJ0                                                                                                                   | MISO1                  | _              | _                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 13          | PJ1              | KWJ1                                                                                                                   | MOSI1                  | _              |                           | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 14          | PJ2              | KWJ2                                                                                                                   | SCK1                   | _              | _                         | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 15          | PJ3              | KWJ3                                                                                                                   | SS1                    | _              |                           | V <sub>DDX</sub> | PERJ/PPSJ  | Up             |

| 16          | BKGD             | MODC                                                                                                                   | —                      | _              |                           | V <sub>DDX</sub> | PUCR/BKPUE | Up             |

| 17          | PP0              | KWP0                                                                                                                   | ETRIG0                 | API_EXTC<br>LK | PWM0                      | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 18          | PP1              | KWP1                                                                                                                   | ETRIG1                 | ECLKX2         | PWM1                      | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 19          | PP2              | KWP2                                                                                                                   | ETRIG2                 | PWM2           |                           | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 20          | PP3              | KWP3                                                                                                                   | ETRIG3                 | PWM3           |                           | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 21          | PP4              | KWP4                                                                                                                   | PWM4                   | _              | _                         | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 22          | PP5              | KWP5                                                                                                                   | PWM5                   |                | _                         | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 23          | PP6              | KWP6                                                                                                                   | PWM6                   | _              | _                         | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 24          | PP7              | KWP7                                                                                                                   | PWM7                   | _              | _                         | V <sub>DDX</sub> | PERP/PPSP  | Disabled       |

| 25          | PT7              | IOC7                                                                                                                   | —                      | _              | _                         | V <sub>DDX</sub> | PERT/PPST  | Disabled       |

| 26          | PT6              | IOC6                                                                                                                   | —                      | _              |                           | V <sub>DDX</sub> | PERT/PPST  | Disabled       |

| 27          | PT5              | IOC5                                                                                                                   | _                      |                |                           | V <sub>DDX</sub> | PERT/PPST  | Disabled       |

Table 1-21. 64-Pin LQFP Pinout for S12G96 and S12G128

|             | <     | Func<br>owestPRIO                                                                                 |              | Power        | Internal Pull<br>Resistor |            |                |

|-------------|-------|---------------------------------------------------------------------------------------------------|--------------|--------------|---------------------------|------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.                                                                                      | 3rd<br>Func. | 4th<br>Func. | Supply                    | CTRL       | Reset<br>State |

| 86          | PS4   | MISO0                                                                                             | _            |              | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 87          | PS5   | MOSI0                                                                                             | _            | _            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 88          | PS6   | SCK0                                                                                              | _            | _            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 89          | PS7   | API_EXTC<br>LK                                                                                    | SS0          | —            | V <sub>DDX</sub>          | PERS/PPSS  | Up             |

| 90          | VSSX2 | _                                                                                                 | _            | _            |                           |            |                |

| 91          | VDDX2 | —                                                                                                 | _            | —            | —                         |            |                |

| 92          | PM0   | RXCAN                                                                                             | _            | —            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 93          | PM1   | TXCAN                                                                                             | _            | —            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 94          | PD4   | —                                                                                                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 95          | PD5   | —                                                                                                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 96          | PD6   | —                                                                                                 | _            | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 97          | PD7   | PD7         —         —           PM2         RXD2         —           PM3         TXD2         — |              | —            | V <sub>DDX</sub>          | PUCR/PUPDE | Disabled       |

| 98          | PM2   |                                                                                                   |              | _            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 99          | PM3   |                                                                                                   |              | —            | V <sub>DDX</sub>          | PERM/PPSM  | Disabled       |

| 100         | PJ7   | KWJ7                                                                                              | SS2          |              | V <sub>DDX</sub>          | PERJ/PPSJ  | Up             |

Table 1-25.

100-Pin LQFP Pinout for S12GA96 and S12GA128

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

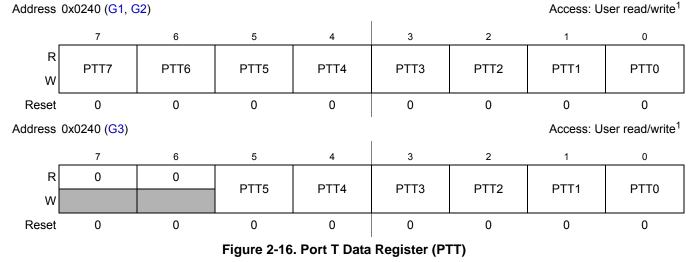

# 2.4.3.15 Port T Data Register (PTT)

Read: Anytime. The data source is depending on the data direction value. Write: Anytime

### Table 2-35. PTT Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PTT | <b>Port T general-purpose input/output data</b> —Data Register<br>When not used with an alternative signal, the associated pin can be used as general-purpose I/O. In general-purpose<br>output mode the port data register bit value is driven to the pin.<br>If the associated data direction bit is set to 1, a read returns the value of the port data register bit, otherwise the<br>buffered pin input state is read. |

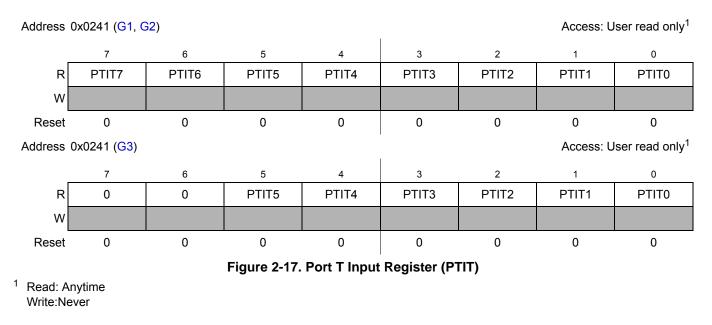

# 2.4.3.16 Port T Input Register (PTIT)

| Field       | Description                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PTIT | <b>Port T input data</b> —<br>A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

### Table 2-36. PTIT Register Field Descriptions

# 2.4.3.17 Port T Data Direction Register (DDRT)

#### Address 0x0242 (G1, G2) Access: User read/write<sup>1</sup> 7 6 5 4 3 2 1 0 R DDRT7 DDRT6 DDRT5 DDRT4 DDRT2 DDRT3 DDRT1 DDRT0 W 0 0 0 0 0 0 0 0 Reset Address 0x0242 (G3) Access: User read/write1 7 6 5 4 3 2 1 0 R 0 0 DDRT5 DDRT4 DDRT3 DDRT2 DDRT1 DDRT0 W 0 0 0 0 0 0 0 0 Reset Figure 2-18. Port T Data Direction Register (DDRT)

<sup>1</sup> Read: Anytime

Write: Anytime

### Table 2-37. DDRT Register Field Descriptions

| Field       | Description                                                                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------|

| 7-0<br>DDRT | <b>Port T data direction</b> —<br>This bit determines whether the pin is a general-purpose input or output. |

|             | 1 Associated pin configured as output<br>0 Associated pin configured as input                               |

### Security (S12XS9SECV2)

to erase the EEPROM and Flash memory without giving access to their contents. After erasing both Flash memory and EEPROM, another reset into special single chip mode will cause the blank check to succeed and the options/security byte can be programmed to "unsecured" state via BDM.

While the BDM is executing the blank check, the BDM interface is completely blocked, which means that all BDM commands are temporarily blocked.

# 9.1.5 Unsecuring the Microcontroller

Unsecuring the microcontroller can be done by three different methods:

- 1. Backdoor key access

- 2. Reprogramming the security bits

- 3. Complete memory erase (special modes)

### 9.1.5.1 Unsecuring the MCU Using the Backdoor Key Access

In normal modes (single chip and expanded), security can be temporarily disabled using the backdoor key access method. This method requires that:

- The backdoor key at 0xFF00–0xFF07 (= global addresses 0x3\_FF00–0x3\_FF07) has been programmed to a valid value.

- The KEYEN[1:0] bits within the Flash options/security byte select 'enabled'.

- In single chip mode, the application program programmed into the microcontroller must be designed to have the capability to write to the backdoor key locations.

The backdoor key values themselves would not normally be stored within the application data, which means the application program would have to be designed to receive the backdoor key values from an external source (e.g. through a serial port).

The backdoor key access method allows debugging of a secured microcontroller without having to erase the Flash. This is particularly useful for failure analysis.

### NOTE

No word of the backdoor key is allowed to have the value 0x0000 or 0xFFFF.

# 9.1.6 Reprogramming the Security Bits

In normal single chip mode (NS), security can also be disabled by erasing and reprogramming the security bits within Flash options/security byte to the unsecured value. Because the erase operation will erase the entire sector from 0xFE00–0xFFFF (0x7F\_FE00–0x7F\_FFFF), the backdoor key and the interrupt vectors will also be erased; this method is not recommended for normal single chip mode. The application software can only erase and program the Flash options/security byte if the Flash sector containing the Flash options/security byte is not protected (see Flash protection). Thus Flash protection is a useful means of preventing this method. The microcontroller will enter the unsecured state after the next reset following the programming of the security bits to the unsecured value.

| CR2 | CR1 | CR0 | COPCLK<br>Cycles to Time-out<br>(COPCLK is ACLK -<br>internal RC-Oscillator clock) |

|-----|-----|-----|------------------------------------------------------------------------------------|

| 0   | 0   | 0   | COP disabled                                                                       |

| 0   | 0   | 1   | 2 <sup>7</sup>                                                                     |

| 0   | 1   | 0   | 2 <sup>9</sup>                                                                     |

| 0   | 1   | 1   | 2 <sup>11</sup>                                                                    |

| 1   | 0   | 0   | 2 <sup>13</sup>                                                                    |

| 1   | 0   | 1   | 2 <sup>15</sup>                                                                    |

| 1   | 1   | 0   | 2 <sup>16</sup>                                                                    |

| 1   | 1   | 1   | 2 <sup>17</sup>                                                                    |

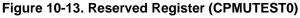

## 10.3.2.10 Reserved Register CPMUTEST0

NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU's functionality.

0x003D R W Reset = Unimplemented or Reserved

Read: Anytime

Write: Only in Special Mode

# 10.3.2.11 Reserved Register CPMUTEST1

### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU's functionality.

# 11.2 Signal Description

This section lists all inputs to the ADC10B8C block.

# 11.2.1 Detailed Signal Descriptions

### 11.2.1.1 ANx (x = 7, 6, 5, 4, 3, 2, 1, 0)

This pin serves as the analog input Channel *x*. It can also be configured as digital port or external trigger for the ATD conversion.

# 11.2.1.2 ETRIG3, ETRIG2, ETRIG1, ETRIG0

These inputs can be configured to serve as an external trigger for the ATD conversion.

Refer to device specification for availability and connectivity of these inputs!

## 11.2.1.3 VRH, VRL

VRH is the high reference voltage, VRL is the low reference voltage for ATD conversion.

### 11.2.1.4 VDDA, VSSA

These pins are the power supplies for the analog circuitry of the ADC10B8C block.

# 11.3 Memory Map and Register Definition

This section provides a detailed description of all registers accessible in the ADC10B8C.

# 11.3.1 Module Memory Map

Figure 11-2 gives an overview on all ADC10B8C registers.

### NOTE

Register Address = Base Address + Address Offset, where the Base Address is defined at the MCU level and the Address Offset is defined at the module level.

| Address | Name    | Bit 7           | 6     | 5        | 4       | 3        | 2        | 1        | Bit 0    |

|---------|---------|-----------------|-------|----------|---------|----------|----------|----------|----------|

| 0x0000  | ATDCTL0 | R<br>Reserved   | 0     | 0        | 0       | WRAP3    | WRAP2    | WRAP1    | WRAP0    |

| 0x0001  | ATDCTL1 | R<br>W ETRIGSEL | SRES1 | SRES0    | SMP_DIS | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 |

| 0x0002  | ATDCTL2 | R 0<br>W        | AFFC  | Reserved | ETRIGLE | ETRIGP   | ETRIGE   | ASCIE    | ACMPIE   |

|         |         |                 |       |          |         |          |          |          |          |

= Unimplemented or Reserved

Figure 11-2. ADC10B8C Register Summary (Sheet 1 of 2)

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>WUPIE <sup>1</sup> | Wake-Up Interrupt Enable0 No interrupt request is generated from this event.1 A wake-up event causes a Wake-Up interrupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 6<br>CSCIE              | <ul> <li>CAN Status Change Interrupt Enable</li> <li>0 No interrupt request is generated from this event.</li> <li>1 A CAN Status Change event causes an error interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 5-4<br>RSTATE[1:0<br>]  | <ul> <li>Receiver Status Change Enable — These RSTAT enable bits control the sensitivity level in which receiver state changes are causing CSCIF interrupts. Independent of the chosen sensitivity level the RSTAT flags continue to indicate the actual receiver state and are only updated if no CSCIF interrupt is pending.</li> <li>00 Do not generate any CSCIF interrupt caused by receiver state changes.</li> <li>01 Generate CSCIF interrupt only if the receiver enters or leaves "bus-off" state. Discard other receiver state changes for generating CSCIF interrupt.</li> <li>10 Generate CSCIF interrupt only if the receiver enters or leaves "RxErr" or "bus-off"<sup>2</sup> state. Discard other receiver state changes for generating CSCIF interrupt.</li> <li>11 Generate CSCIF interrupt on all state changes.</li> </ul>              |  |  |

| 3-2<br>TSTATE[1:0]      | <ul> <li>Transmitter Status Change Enable — These TSTAT enable bits control the sensitivity level in which transmitter state changes are causing CSCIF interrupts. Independent of the chosen sensitivity level, the TSTAT flags continue to indicate the actual transmitter state and are only updated if no CSCIF interrupt is pending.</li> <li>00 Do not generate any CSCIF interrupt caused by transmitter state changes.</li> <li>01 Generate CSCIF interrupt only if the transmitter enters or leaves "bus-off" state. Discard other transmitter state changes for generating CSCIF interrupt.</li> <li>10 Generate CSCIF interrupt only if the transmitter enters or leaves "TxErr" or "bus-off" state. Discard other transmitter state changes for generating CSCIF interrupt.</li> <li>11 Generate CSCIF interrupt on all state changes.</li> </ul> |  |  |

| 1<br>OVRIE              | Overrun Interrupt Enable0 No interrupt request is generated from this event.1 An overrun event causes an error interrupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 0<br>RXFIE              | <ul> <li>Receiver Full Interrupt Enable</li> <li>0 No interrupt request is generated from this event.</li> <li>1 A receive buffer full (successful message reception) event causes a receiver interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

### Table 18-12. CANRIER Register Field Descriptions

<sup>1</sup> WUPIE and WUPE (see Section 18.3.2.1, "MSCAN Control Register 0 (CANCTL0)") must both be enabled if the recovery mechanism from stop or wait is required.

<sup>2</sup> Bus-off state is only defined for transmitters by the CAN standard (see Bosch CAN 2.0A/B protocol specification). Because the only possible state change for the transmitter from bus-off to TxOK also forces the receiver to skip its current state to RxOK, the coding of the RXSTAT[1:0] flags define an additional bus-off state for the receiver (see Section 18.3.2.5, "MSCAN Receiver Flag Register (CANRFLG)").

# 18.3.2.7 MSCAN Transmitter Flag Register (CANTFLG)

The transmit buffer empty flags each have an associated interrupt enable bit in the CANTIER register.

Scalable Controller Area Network (S12MSCANV3)

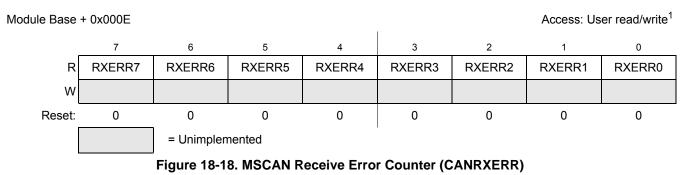

# 18.3.2.15 MSCAN Receive Error Counter (CANRXERR)

This register reflects the status of the MSCAN receive error counter.

<sup>1</sup> Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

### NOTE

Reading this register when in any other mode other than sleep or initialization mode may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

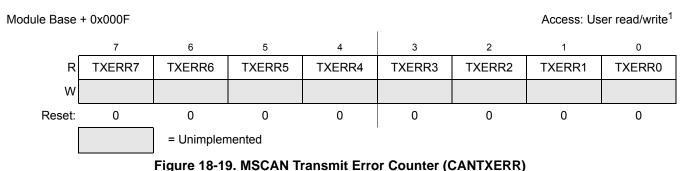

# 18.3.2.16 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

#### Scalable Controller Area Network (S12MSCANV3)

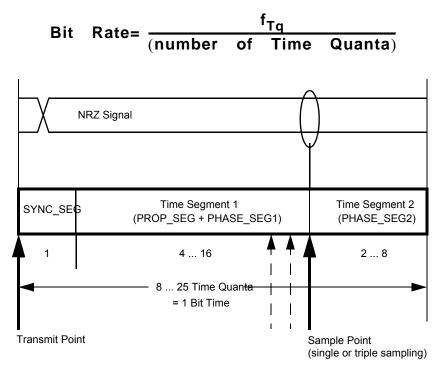

For microcontrollers without a clock and reset generator (CRG), CANCLK is driven from the crystal oscillator (oscillator clock).

A programmable prescaler generates the time quanta (Tq) clock from CANCLK. A time quantum is the atomic unit of time handled by the MSCAN.

Eqn. 18-2

| _   | fcanci     | LK    |

|-----|------------|-------|

| ۲q- | (Prescaler | value |

A bit time is subdivided into three segments as described in the Bosch CAN 2.0A/B specification. (see Figure 18-44):

- SYNC\_SEG: This segment has a fixed length of one time quantum. Signal edges are expected to happen within this section.

- Time Segment 1: This segment includes the PROP\_SEG and the PHASE\_SEG1 of the CAN standard. It can be programmed by setting the parameter TSEG1 to consist of 4 to 16 time quanta.

- Time Segment 2: This segment represents the PHASE\_SEG2 of the CAN standard. It can be programmed by setting the TSEG2 parameter to be 2 to 8 time quanta long.

Eqn. 18-3

Figure 18-44. Segments within the Bit Time

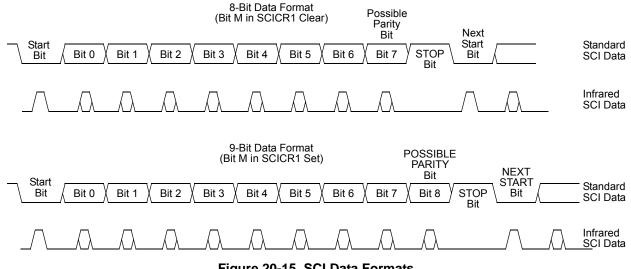

Figure 20-15. SCI Data Formats

Each data character is contained in a frame that includes a start bit, eight or nine data bits, and a stop bit. Clearing the M bit in SCI control register 1 configures the SCI for 8-bit data characters. A frame with eight data bits has a total of 10 bits. Setting the M bit configures the SCI for nine-bit data characters. A frame with nine data bits has a total of 11 bits.

| Start<br>Bit | Data<br>Bits | Address<br>Bits | Parity<br>Bits | Stop<br>Bit |

|--------------|--------------|-----------------|----------------|-------------|

| 1            | 8            | 0               | 0              | 1           |

| 1            | 7            | 0               | 1              | 1           |

| 1            | 7            | 1 <sup>1</sup>  | 0              | 1           |

Table 20-14. Example of 8-Bit Data Formats

The address bit identifies the frame as an address character. See Section 20.4.6.6, "Receiver Wakeup".

When the SCI is configured for 9-bit data characters, the ninth data bit is the T8 bit in SCI data register high (SCIDRH). It remains unchanged after transmission and can be used repeatedly without rewriting it. A frame with nine data bits has a total of 11 bits.

| Start<br>Bit | Data<br>Bits | Address<br>Bits | Parity<br>Bits | Stop<br>Bit |

|--------------|--------------|-----------------|----------------|-------------|

| 1            | 9            | 0               | 0              | 1           |

| 1            | 8            | 0               | 1              | 1           |

| 1            | 8            | 1 <sup>1</sup>  | 0              | 1           |

<sup>1</sup> The address bit identifies the frame as an address character. See Section 20.4.6.6, "Receiver Wakeup".

| When SPE = 1                   | Master Mode MSTR = 1                      | Slave Mode MSTR = 0                 |  |

|--------------------------------|-------------------------------------------|-------------------------------------|--|

| Normal Mode<br>SPC0 = 0        | Serial Out MOSI<br>SPI<br>Serial In MISO  | Serial In<br>SPI<br>Serial Out MISO |  |

| Bidirectional Mode<br>SPC0 = 1 | Serial Out<br>SPI<br>BIDIROE<br>Serial In | Serial In<br>SPI<br>Serial Out      |  |

Table 21-10. Normal Mode and Bidirectional Mode

The direction of each serial I/O pin depends on the BIDIROE bit. If the pin is configured as an output, serial data from the shift register is driven out on the pin. The same pin is also the serial input to the shift register.

- The SCK is output for the master mode and input for the slave mode.

- The  $\overline{SS}$  is the input or output for the master mode, and it is always the input for the slave mode.

- The bidirectional mode does not affect SCK and  $\overline{SS}$  functions.

### NOTE

In bidirectional master mode, with mode fault enabled, both data pins MISO and MOSI can be occupied by the SPI, though MOSI is normally used for transmissions in bidirectional mode and MISO is not used by the SPI. If a mode fault occurs, the SPI is automatically switched to slave mode. In this case MISO becomes occupied by the SPI and MOSI is not used. This must be considered, if the MISO pin is used for another purpose.

# 21.4.6 Error Conditions

The SPI has one error condition:

• Mode fault error

# 21.4.6.1 Mode Fault Error

If the  $\overline{SS}$  input becomes low while the SPI is configured as a master, it indicates a system error where more than one master may be trying to drive the MOSI and SCK lines simultaneously. This condition is not permitted in normal operation, the MODF bit in the SPI status register is set automatically, provided the MODFEN bit is set.

In the special case where the SPI is in master mode and MODFEN bit is cleared, the  $\overline{SS}$  pin is not used by the SPI. In this special case, the mode fault error function is inhibited and MODF remains cleared. In case

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 24-25)                      |

|          |           | Set if an invalid global address [17:16] is supplied see Table 24-3) <sup>1</sup>   |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

| Table 24-47. Erase P-Flash Sector Command Error Handling |

|----------------------------------------------------------|

|----------------------------------------------------------|

<sup>1</sup> As defined by the memory map for FTMRG32K1.

## 24.4.6.10 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and EEPROM memory space and, if the erase is successful, will release security.

### Table 24-48. Unsecure Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x0B             | Not required |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and EEPROM memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security state. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag is set after the Unsecure Flash operation has completed.

| Register | Error Bit | Error Condition                                                                                  |

|----------|-----------|--------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                      |

|          | AUCERR    | Set if command not available in current mode (see Table 24-25)                                   |

| FSTAT    | FPVIOL    | Set if any area of the P-Flash or EEPROM memory is protected                                     |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation <sup>1</sup>                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation <sup>1</sup> |

Table 24-49. Unsecure Flash Command Error Handling

<sup>1</sup> As found in the memory map for FTMRG32K1.

### 32 KByte Flash Module (S12FTMRG32K1V1)

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 25.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 25.4.6.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0x3\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x3\_FF00-0x3\_FF07 are unaffected by the Verify Backdoor Access Key command sequence. The Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired. In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses 0x3\_FF00-0x3\_FF07 in the Flash configuration field.

# 25.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

A secured MCU can be unsecured in special single chip mode by using the following method to erase the P-Flash and EEPROM memory:

- 1. Reset the MCU into special single chip mode

- 2. Delay while the BDM executes the Erase Verify All Blocks command write sequence to check if the P-Flash and EEPROM memories are erased

- 3. Send BDM commands to disable protection in the P-Flash and EEPROM memory

- 4. Execute the Erase All Blocks command write sequence to erase the P-Flash and EEPROM memory. Alternatively the Unsecure Flash command can be executed, if so the steps 5 and 6 below are skeeped.

- 5. After the CCIF flag sets to indicate that the Erase All Blocks operation has completed, reset the MCU into special single chip mode

- 6. Delay while the BDM executes the Erase Verify All Blocks command write sequence to verify that the P-Flash and EEPROM memory are erased

If the P-Flash and EEPROM memory are verified as erased, the MCU will be unsecured. All BDM commands will now be enabled and the Flash security byte may be programmed to the unsecure state by continuing with the following steps:

7. Send BDM commands to execute the Program P-Flash command write sequence to program the Flash security byte to the unsecured state

#### 48 KByte Flash Module (S12FTMRG48K1V1)

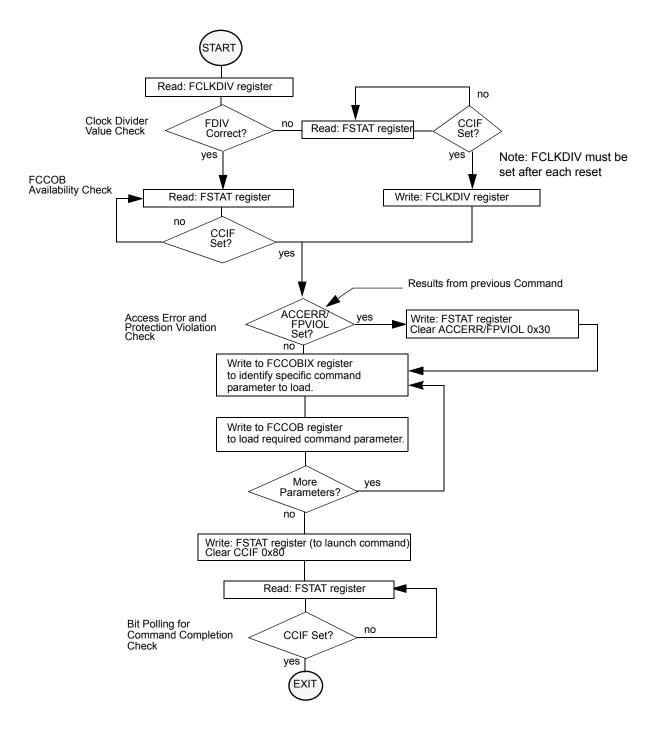

Figure 26-26. Generic Flash Command Write Sequence Flowchart

#### 128 KByte Flash Module (S12FTMRG128K1V1)

Table 29-4). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x0C             | Not required |

| 001         | Key 0            |              |

| 010         | Key 1            |              |

| 011         | Key 2            |              |

| 100         | Key 3            |              |

Table 29-52. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

Table 29-53. Verify Backdoor Access Key Command Error Handling

| Register | Error Bit | Error Condition                                                                          |

|----------|-----------|------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 100 at command launch                                              |

|          |           | Set if an incorrect backdoor key is supplied                                             |

|          |           | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 29.3.2.2) |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                              |

|          | FPVIOL    | None                                                                                     |

|          | MGSTAT1   | None                                                                                     |

|          | MGSTAT0   | None                                                                                     |

### 29.4.6.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

| CCOBIX[2:0] | FCCOB Parameters      |                                                   |  |  |  |  |

|-------------|-----------------------|---------------------------------------------------|--|--|--|--|

| 000         | 0x0D                  | Flash block selection code [1:0]. See Table 29-34 |  |  |  |  |

| 001         | Margin level setting. |                                                   |  |  |  |  |

### Table A-21. ADC Conversion Performance 5V range (Junction Temperature From -40°C To +150°C)

#### S12GNA16, S12GNA32, S12GAS48, S12GA64, S12GA96, S12GA128, S12GA192 and S12GA240

Supply voltage 4.5V <  $V_{DDA}$  < 5.5 V, -40°C <  $T_J$  < 150°C,  $V_{REF}$  =  $V_{RH}$  -  $V_{RL}$  =  $V_{DDA}$ ,  $f_{ADCCLK}$  = 8.0MHz The values are tested to be valid with no port AD output drivers switching simultaneous with conversions.

| The values are tested to be valid with no port AD output drivers switching simultaneous with conversions. |   |                             |        |        |      |      |     |        |

|-----------------------------------------------------------------------------------------------------------|---|-----------------------------|--------|--------|------|------|-----|--------|

| Num                                                                                                       | С | Rating <sup>1</sup>         |        | Symbol | Min  | Тур  | Max | Unit   |

| 1                                                                                                         | Ρ | Resolution                  | 12-Bit | LSB    |      | 1.25 |     | mV     |

| 2                                                                                                         | Ρ | Differential Nonlinearity   | 12-Bit | DNL    | -4   | ±2   | 4   | counts |

| 3                                                                                                         | Ρ | Integral Nonlinearity       | 12-Bit | INL    | -5   | ±2.5 | 5   | counts |

| 4                                                                                                         | Ρ | Absolute Error <sup>2</sup> | 12-Bit | AE     | -7   | ±4   | 7   | counts |

| 5                                                                                                         | С | Resolution                  | 10-Bit | LSB    |      | 5    |     | mV     |

| 6                                                                                                         | С | Differential Nonlinearity   | 10-Bit | DNL    | -1   | ±0.5 | 1   | counts |

| 7                                                                                                         | С | Integral Nonlinearity       | 10-Bit | INL    | -2   | ±1   | 2   | counts |

| 8                                                                                                         | С | Absolute Error <sup>2</sup> | 10-Bit | AE     | -3   | ±2   | 3   | counts |

| 9                                                                                                         | С | Resolution                  | 8-Bit  | LSB    |      | 20   |     | mV     |

| 10                                                                                                        | С | Differential Nonlinearity   | 8-Bit  | DNL    | -0.5 | ±0.3 | 0.5 | counts |

| 11                                                                                                        | С | Integral Nonlinearity       | 8-Bit  | INL    | -1   | ±0.5 | 1   | counts |

| 12                                                                                                        | С | Absolute Error <sup>2</sup> | 8-Bit  | AE     | -1.5 | ±1   | 1.5 | counts |

<sup>1</sup> The 8-bit and 10-bit mode operation is structurally tested in production test. Absolute values are tested in 12-bit mode.

<sup>2</sup> These values include the quantization error which is inherently 1/2 count for any A/D converter.

| S12G96, S12GA96, S12G128, S12GA128 |                                          |                             |                              |                        |                  |                  |                  |                    |      |

|------------------------------------|------------------------------------------|-----------------------------|------------------------------|------------------------|------------------|------------------|------------------|--------------------|------|

| Num                                | Command                                  | f <sub>NVMOP</sub><br>cycle | f <sub>NVMBUS</sub><br>cycle | Symbol                 | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>3</sup> | Lfmax <sup>4</sup> | Unit |

| 1                                  | Erase Verify All Blocks <sup>5,6</sup>   | 0                           | 35345                        | t <sub>RD1ALL</sub>    | 1.41             | 1.41             | 2.83             | 70.69              | ms   |

| 2                                  | Erase Verify Block (Pflash) <sup>5</sup> | 0                           | 33308                        | t <sub>RD1BLK_P</sub>  | 1.33             | 1.33             | 2.66             | 66.62              | ms   |

| 3                                  | Erase Verify Block (EEPROM) <sup>6</sup> | 0                           | 2536                         | t <sub>RD1BLK_</sub> D | 0.1              | 0.1              | 0.2              | 5.07               | ms   |

| 4                                  | Erase Verify P-Flash Section             | 0                           | 476                          | t <sub>RD1SEC</sub>    | 19.04            | 19.04            | 38.08            | 952                | ms   |

| 5                                  | Read Once                                | 0                           | 445                          | t <sub>RDONCE</sub>    | 17.8             | 17.8             | 17.8             | 445                | μS   |

| 6                                  | Program P-Flash (4 Word)                 | 164                         | 2925                         | t <sub>PGM_4</sub>     | 0.27             | 0.28             | 0.63             | 11.91              | ms   |

| 7                                  | Program Once                             | 164                         | 2888                         | t <sub>PGMONCE</sub>   | 0.27             | 0.28             | 0.28             | 3.09               | ms   |

| 8                                  | Erase All Blocks <sup>5,6</sup>          | 100066                      | 35681                        | t <sub>ERSALL</sub>    | 96.73            | 101.49           | 102.92           | 196.44             | ms   |

| 9                                  | Erase Flash Block (Pflash) <sup>5</sup>  | 100060                      | 33541                        | t <sub>ERSBLK_P</sub>  | 96.64            | 101.4            | 102.74           | 192.16             | ms   |

| 10                                 | Erase Flash Block (EEPROM) <sup>6</sup>  | 100060                      | 2832                         | t <sub>ERSBLK_D</sub>  | 95.41            | 100.17           | 100.29           | 130.74             | ms   |

| 11                                 | Erase P-Flash Sector                     | 20015                       | 865                          | t <sub>ERSPG</sub>     | 19.1             | 20.05            | 20.08            | 26.75              | ms   |

| 12                                 | Unsecure Flash                           | 100066                      | 35759                        | t <sub>UNSECU</sub>    | 96.73            | 101.5            | 102.93           | 196.6              | ms   |

| 13                                 | Verify Backdoor Access Key               | 0                           | 481                          | t <sub>VFYKEY</sub>    | 19.24            | 19.24            | 19.24            | 481                | μS   |

| 14                                 | Set User Margin Level                    | 0                           | 399                          | t <sub>MLOADU</sub>    | 15.96            | 15.96            | 15.96            | 399                | μS   |

| 15                                 | Set Factory Margin Level                 | 0                           | 408                          | t <sub>MLOADF</sub>    | 16.32            | 16.32            | 16.32            | 408                | μS   |

| 16                                 | Erase Verify EEPROM Section              | 0                           | 546                          | t <sub>DRD1SEC</sub>   | 0.02             | 0.02             | 0.04             | 1.09               | ms   |

| 17                                 | Program EEPROM (1 Word)                  | 68                          | 1565                         | t <sub>DPGM_1</sub>    | 0.13             | 0.13             | 0.32             | 6.35               | ms   |

| 18                                 | Program EEPROM (2 Word)                  | 136                         | 2512                         | t <sub>DPGM_2</sub>    | 0.23             | 0.24             | 0.54             | 10.22              | ms   |

| 19                                 | Program EEPROM (3 Word)                  | 204                         | 3459                         | t <sub>DPGM_3</sub>    | 0.33             | 0.34             | 0.76             | 14.09              | ms   |

| 20                                 | Program EEPROM (4 Word)                  | 272                         | 4406                         | t <sub>DPGM_4</sub>    | 0.44             | 0.45             | 0.98             | 17.96              | ms   |

| 21                                 | Erase EEPROM Sector                      | 5015                        | 753                          | t <sub>DERSPG</sub>    | 4.81             | 5.05             | 20.57            | 37.88              | ms   |

### Table A-37. NVM Timing Characteristics)

$^1\,$  Minimum times are based on maximum  $f_{NVMOP}$  and maximum  $f_{NVMBUS}$

$^2\,$  Typical times are based on typical  $f_{NVMOP}$  and typical  $f_{NVMBUS}$

$^3\,$  Maximum times are based on typical  $f_{\rm NVMOP}$  and typical  $f_{\rm NVMBUS}$  plus aging

$^4$  Lowest-frequency max times are based on minimum  $f_{\rm NVMOP}$  and minimum  $f_{\rm NVMBUS}$  plus aging

<sup>5</sup> Affected by Pflash size

<sup>6</sup> Affected by EEPROM size