Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IEBus, SIO, UART/USART                                         |

| Peripherals                | DMA, PWM, Voltage Detect, WDT                                                    |

| Number of I/O              | 39                                                                               |

| Program Memory Size        | 24KB (24K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-LQFP                                                                          |

| Supplier Device Package    | 48-LQFP (7x7)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30260f3agp-u7a |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

| (1) | Register Names, Bit Names, and Pin Names<br>Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word<br>"register," "bit," or "pin" to distinguish the three categories.<br>Examples the PM03 bit in the PM0 register<br>P3_5 pin, VCC pin                                                                                      |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (2) | Notation of Numbers<br>The indication "2" is appended to numeric values given in binary format. However, nothing is appended to the<br>values of single bits. The indication "16" is appended to numeric values given in hexadecimal format. Nothing<br>is appended to numeric values given in decimal format.<br>Examples Binary: 112<br>Hexadecimal: EFA016<br>Decimal: 1234 |  |

|                 | Item                       | Performance                                                                          |

|-----------------|----------------------------|--------------------------------------------------------------------------------------|

| CPU             | Basic instructions         | 91 instructions                                                                      |

|                 | Minimun instruction        | 41.7 ns (f(BCLK) = 24 MHz <sup>(3)</sup> , VCC = 4.2 to 5.5 V (M16C/26B)             |

|                 | execution time             | 50 ns (f(BCLK) = 20 MHz, Vcc = 3.0 to 5.5 V) (M16C/26A, M16C/26B)                    |

|                 |                            | 100 ns (f(BCLK) = 10 MHz, Vcc = 2.7 to 5.5 V) (M16C/26A, M16C/26B)                   |

|                 | Operation mode             | Single-chip mode                                                                     |

|                 | Address space              | 1M byte                                                                              |

|                 | Memory capacity            | ROM/RAM: See 1.4 Product Information                                                 |

| Peripheral      | Port                       | 33 I/O pins                                                                          |

| function        | Multifunction timer        | Timer A: 16 bits x 5 channels, Timer B: 16 bits x 3 channels                         |

|                 |                            | Three-phase motor control timer                                                      |

|                 | Serial I/O                 | 1 channel (UART, clock synchronous serial I/O)                                       |

|                 |                            | 1 channel (UART, clock synchronous, I <sup>2</sup> C bus, or IEBus <sup>(1)</sup> )  |

|                 | A/D converter              | 10 bit A/D converter: 1 circuit, 10 channels                                         |

|                 | DMAC                       | 2 channels                                                                           |

|                 | CRC calcuration circuit    | 1 circuits (CRC-CCITT and CRC-16) with MSB/LSB selectable                            |

|                 | Watchdog timer             | 15 bits x 1 channel (with prescaler)                                                 |

|                 | Interrupt                  | 18 internal and 8 external sources, 4 software sources,                              |

|                 |                            | Interrupt priority level: 7                                                          |

|                 | Clock generation circuit   | 4 circuits                                                                           |

|                 |                            | Main clock(*), Sub-clock(*)                                                          |

|                 |                            | On-chip oscillator, PLL frequency synthesizer                                        |

|                 |                            | (*)Equipped with a built-in feedback resister.                                       |

|                 | Oscillation stop detection | Main clock oscillation stop, re-oscillation detection function                       |

|                 | Voltage detection circuit  | On-chip                                                                              |

| Electrical      | Supply voltage             | $V_{CC} = 4.2 \text{ to } 5.5 \text{ V} (f(BCLK) = 24 \text{ MHz})^{(3)}$ (M16C/26B) |

| Characteristics |                            | Vcc = 3.0 to 5.5 V (f(BCLK) = 20 MHz) (M16C/26A, M16C/26B)                           |

|                 |                            | Vcc = 2.7 to 5.5 V (f(BCLK) = 10 MHz)                                                |

|                 | Power Consumption          | 20 mA (Vcc = 5 V, f(BCLK) = 24 MHz) (M16C/26B)                                       |

|                 |                            | 16 mA (Vcc = 5 V, f(BCLK) = 20 MHz)                                                  |

|                 |                            | 25 μA (f(XCIN) = 32 KHz on RAM)                                                      |

|                 |                            | 3 μA (Vcc = 3 V, f(XCIN) = 32 KHz, in wait mode)                                     |

|                 |                            | $0.7 \mu\text{A} (\text{Vcc} = 3 \text{V}, \text{ in stop mode})$                    |

| Flash memory    | Programming/erasure        | 2.7 to 5.5 V                                                                         |

|                 | voltage                    |                                                                                      |

|                 | Programming/erasure        | 100 times (all area) or 1,000 times (block 0 to 3)                                   |

|                 | endurance                  | / 10,000 times (block A, block B) <sup>(2)</sup>                                     |

| Operating Amb   | ient Temperature           | -20 to 85°C / -40 to 85°C <sup>(2)</sup>                                             |

| Package         |                            | 42-pin plastic molded SSOP                                                           |

| Table 1.2. | Performance outline o | f M16C/26A aroup   | (M16C/26A. | , M16C/26B) (42-pin packag    | ie) |

|------------|-----------------------|--------------------|------------|-------------------------------|-----|

|            |                       | - miloo/20/1 group | (          | , miloo, 200) (42 pili puokug | ,~, |

NOTES:

1. IEBus is a trademark of NEC Electronics Corporation.

2. See **Tables 1.7 and 1.8 Product Code** for the program and erase endurance, and operating ambient temperature.

3. The PLL frequency synthesizer is used to run the M16C/26B at f(BCLK) = 24 MHz.

# Table 4.4 SFR Information(4)<sup>(1)</sup>

| Address          | Register                                                                   | Symbol       | After reset              |

|------------------|----------------------------------------------------------------------------|--------------|--------------------------|

| 034016           | •                                                                          |              |                          |

| 034116           |                                                                            |              |                          |

| 034216           | Timer A1-1 register                                                        | TA11         | XX16                     |

| 034316           |                                                                            |              | XX16                     |

| 034416           | Timer A2-1 register                                                        | TA21         | XX16                     |

| 034516<br>034616 | Timer A4-1 register                                                        | TA41         | XX16<br>XX16             |

| 034018           | Timer A4-T Tegister                                                        | 1741         | XX16                     |

| 034816           | Three phase PWM control register 0                                         | INVC0        | 0016                     |

| 034916           | Three phase PWM control register 1                                         | INVC1        | 0016                     |

| 034A16           | Three phase output buffer register 0                                       | IDB0         | 001111112                |

| 034B16           | Three phase output buffer register 1                                       | IDB1         | 001111112                |

| 034C16           | Dead time timer                                                            | DTT          | XX16                     |

| 034D16           | Timer B2 Interrupt occurrence frequency set counter                        | ICTB2        | XX16                     |

| 034E16           | Position-data-retain function control register                             | PDRF         | XXXX00002                |

| 034F16           |                                                                            |              |                          |

| 035016           |                                                                            |              |                          |

| 035116           |                                                                            |              |                          |

| 035216<br>035316 |                                                                            |              |                          |

| 035316           |                                                                            |              |                          |

| 035416           |                                                                            |              |                          |

| 035616           |                                                                            |              |                          |

| 035716           |                                                                            |              |                          |

| 035816           | Port function control register                                             | PFCR         | 001111112                |

| 035916           | · · · · · · · · · · · · · · · · · · ·                                      |              |                          |

| 035A16           |                                                                            |              |                          |

| 035B16           |                                                                            |              |                          |

| 035C16           |                                                                            |              |                          |

| 035D16           |                                                                            |              |                          |

| 035E16           | Interrupt request cause select register 2                                  | IFSR2A       | XXXXXXX02 <sup>(2)</sup> |

| 035F16           | Interrupt request cause select register                                    | IFSR         | 0016                     |

| 036016           |                                                                            |              |                          |

| 036116           |                                                                            |              |                          |

| 036216<br>036316 |                                                                            |              |                          |

| 036416           |                                                                            |              |                          |

| 036516           |                                                                            |              |                          |

| 036616           |                                                                            |              |                          |

| 036716           |                                                                            |              |                          |

| 036816           |                                                                            |              |                          |

| 036916           |                                                                            |              |                          |

| 036A16           |                                                                            |              |                          |

| 036B16           |                                                                            |              |                          |

| 036C16           |                                                                            |              |                          |

| 036D16           |                                                                            |              |                          |

| 036E16           |                                                                            |              |                          |

| 036F16<br>037016 |                                                                            |              |                          |

| 037016           |                                                                            |              |                          |

| 037116           |                                                                            |              |                          |

| 037216           |                                                                            |              |                          |

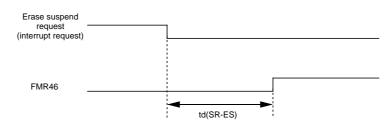

| 037416           | UART2 special mode register 4                                              | U2SMR4       | 0016                     |

| 037516           | UART2 special mode register 3                                              | U2SMR3       | 000X0X0X2                |

| 037616           | UART2 special mode register 2                                              | U2SMR2       | X0000002                 |

| 037716           | UART2 special mode register                                                | U2SMR        | X0000002                 |

| 037816           | UART2 transmit/receive mode register                                       | U2MR         | 0016                     |

| 037916           | UART2 bit rate register                                                    | U2BRG        | XX16                     |

| 037A16           | UART2 transmit buffer register                                             | U2TB         | XXXXXXXX2                |

| 037B16           |                                                                            | 11000        | XXXXXXXX2                |

| 037C16           | UART2 transmit/receive control register 0                                  | U2C0         | 000010002                |

| 037D16<br>037E16 | UART2 transmit/receive control register 1<br>UART2 receive buffer register | U2C1<br>U2RB | 000000102<br>XXXXXXX2    |

| 037E16<br>037F16 | UNITE IEVEIVE DUITET TEUSTET                                               | UZKB         | XXXXXXXX2<br>XXXXXXXX2   |

| NOTE:            |                                                                            | I            |                          |

Blank spaces are reserved. No access is allowed.

Write "1" to bit 0 after reset.

X : Undefined

# 9.2 Interrupts and Interrupt Vector

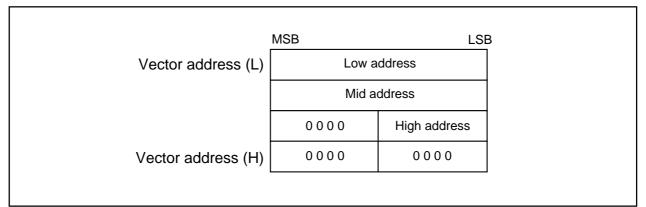

One interrupt vector consists of 4 bytes. Set the start address of each interrupt routine in the respective interrupt vectors. When an interrupt request is accepted, the CPU branches to the address set in the corresponding interrupt vector. Figure 9.2.1 shows the interrupt vector.

Figure 9.2.1. Interrupt Vector

# 9.2.1 Fixed Vector Tables

The fixed vector tables are allocated to the addresses from FFFDC16 to FFFF16. Table 9.2.1.1 lists the fixed vector tables. In the flash memory version of microcomputer, the vector addresses (H) of fixed vectors are used by the ID code check function. For details, refer to the section **17.3 Flash Memory Rewrite Disabling Function**.

| Table 9.2.1.1. | <b>Fixed Vector Tables</b> |

|----------------|----------------------------|

|                |                            |

| Interrupt source                                                 | Vector table addresses     | Remarks                                                                                                                                                  | Reference                 |

|------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|                                                                  | Address (L) to address (H) |                                                                                                                                                          |                           |

| Undefined instruction                                            | FFFDC16 to FFFDF16         | Interrupt on UND instruction                                                                                                                             | M16C/60, M16C/20          |

| Overflow                                                         | FFFE016 to FFFE316         | Interrupt on INTO instruction                                                                                                                            | serise software           |

| BRK instruction                                                  | FFFE416 to FFFE716         | If the contents of address<br>FFFE716 is FF16, program ex-<br>ecution starts from the address<br>shown by the vector in the<br>relocatable vector table. | maual                     |

| Address match                                                    | FFFE816 to FFFEB16         |                                                                                                                                                          | Address match interrupt   |

| Single step (1)                                                  | FFFEC16 to FFFEF16         |                                                                                                                                                          |                           |

| Watchdog timer                                                   | FFFF016 to FFFF316         |                                                                                                                                                          | Watchdog timer            |

| Oscillation stop and<br>re-oscillation detection<br>Voltage down |                            |                                                                                                                                                          | Clock generating circuit  |

| detection                                                        |                            |                                                                                                                                                          | Voltage detection circuit |

| DBC (1)                                                          | FFFF416 to FFFF716         |                                                                                                                                                          |                           |

| NMI                                                              | FFFF816 to FFFFB16         |                                                                                                                                                          | NMI interrupt             |

| Reset (2)                                                        | FFFFC16 to FFFFF16         |                                                                                                                                                          | Reset                     |

NOTES:

- 1. Do not normally use this interrupt because it is provided exclusively for use by development tools.

- 2. The b3 to b0 in address 0FFFF16 are reserve bits. Set these bits to "11112".

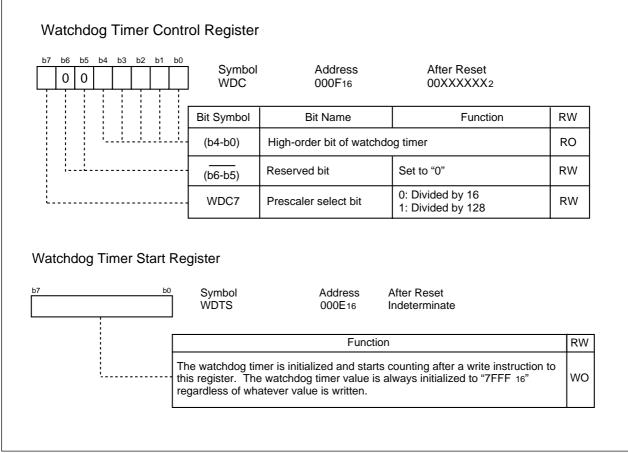

Figure 10.2 WDC Register and WDTS Register

# **10.1 Count Source Protective Mode**

In this mode, a on-chip oscillator clock is used for the watchdog timer count source. The watchdog timer can be kept being clocked even when CPU clock stops as a result of run-away.

Before this mode can be used, the following register settings are required:

(1) Set the PRC1 bit in the PRCR register to "1" (enable writes to PM1 and PM2 registers).

(2) Set the PM12 bit in the PM1 register to "1" (reset when the watchdog timer underflows).

(3) Set the PM22 bit in the PM2 register to "1" (on-chip oscillator clock used for the watchdog timer count source).

(4) Set the PRC1 bit in the PRCR register to "0" (disable writes to PM1 and PM2 registers).

(5) Write to the WDTS register (watchdog timer starts counting).

Setting the PM22 bit to "1" results in the following conditions

- The on-chip oscillator continues oscillating even if the CM21 bit in the CM2 register is set to "0" (main clock or PLL clock) (system clock of count source selected by the CM21 bit is valid)

- The on-chip oscillator starts oscillating, and the in-chip oscillator clock becomes the watchdog timer count source.

Watchdog timer period = Watchdog timer count (32768) on-chip oscillator clock

- The CM10 bit in the CM1 register is disabled against write. (Writing a "1" has no effect, nor is stop mode entered.)

- The watchdog timer does not stop when in wait mode.

# 12.1.1. Timer Mode

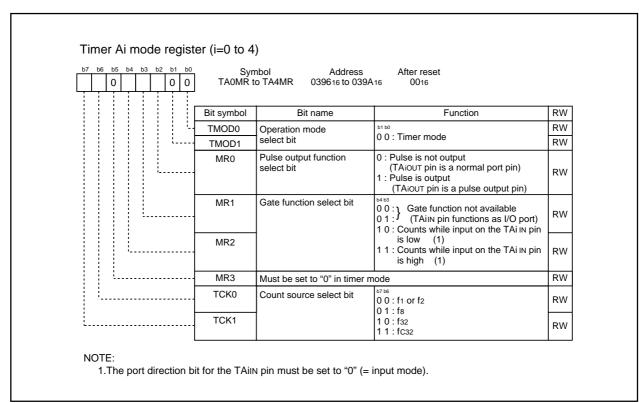

In timer mode, the timer counts a count source generated internally (see Table 12.1.1.1). Figure 1.2.1.1.1 shows TAiMR register in timer mode.

| Item                                | Specification                                                                               |

|-------------------------------------|---------------------------------------------------------------------------------------------|

| Count source                        | f1, f2, f8, f32, fC32                                                                       |

| Count operation                     | Down-count                                                                                  |

|                                     | • When the timer underflows, it reloads the reload register contents and continues counting |

| Divide ratio                        | 1/(n+1) n: set value of TAi register (i= 0 to 4) 000016 to FFFF16                           |

| Count start condition               | Set TAiS bit in the TABSR register to "1" (= start counting)                                |

| Count stop condition                | Set TAiS bit to "0" (= stop counting)                                                       |

| Interrupt request generation timing | Timer underflow                                                                             |

| TAilN pin function                  | I/O port or gate input                                                                      |

| TAio∪⊤ pin function                 | I/O port or pulse output                                                                    |

| Read from timer                     | Count value can be read by reading TAi register                                             |

| Write to timer                      | When not counting and until the 1st count source is input after counting start              |

|                                     | Value written to TAi register is written to both reload register and counter                |

|                                     | <ul> <li>When counting (after 1st count source input)</li> </ul>                            |

|                                     | Value written to TAi register is written to only reload register                            |

|                                     | (Transferred to counter when reloaded next)                                                 |

| Select function                     | Gate function                                                                               |

|                                     | Counting can be started and stopped by an input signal to TAIIN pin                         |

|                                     | Pulse output function                                                                       |

|                                     | Whenever the timer underflows, the output polarity of TAiOUT pin is inverted.               |

|                                     | When not counting, the pin outputs a low.                                                   |

Table 12.1.1.1. Specifications in Timer Mode

Figure 12.1.1.1. Timer Ai Mode Register in Timer Mode

# 12.1.2. Event Counter Mode

In event counter mode, the timer counts pulses from an external device or overflows and underflows of other timers. Timers A2, A3 and A4 can count two-phase external signals. Table 12.1.2.1 lists specifications in event counter mode (when <u>not</u> processing two-phase pulse signal). Table 12.1.2.2 lists specifications in event counter mode (when processing two-phase pulse signal with the timers A2, A3 and A4). Figure 12.1.2.1 shows TAiMR register in event counter mode (when <u>not</u> processing two-phase pulse signal). Figure 12.1.2.2 shows TA2MR to TA4MR registers in event counter mode (when processing two-phase pulse signal). Figure 12.1.2.2 shows TA2MR to TA4MR registers in event counter mode (when processing two-phase pulse signal).

| Item                                | Specification                                                                    |

|-------------------------------------|----------------------------------------------------------------------------------|

| Count source                        | • External signals input to TAiN pin (i=0 to 4) (effective edge can be selected  |

|                                     | in program)                                                                      |

|                                     | Timer B2 overflows or underflows,                                                |

|                                     | timer Aj (j=i-1, except j=4 if i=0) overflows or underflows,                     |

|                                     | timer Ak (k=i+1, except k=0 if i=4) overflows or underflows                      |

| Count operation                     | Up-count or down-count can be selected by external signal or program             |

|                                     | • When the timer overflows or underflows, it reloads the reload register con-    |

|                                     | tents and continues counting. When operating in free-running mode, the           |

|                                     | timer continues counting without reloading.                                      |

| Divided ratio                       | 1/ (FFFF16 - n + 1) for up-count                                                 |

|                                     | 1/ (n + 1) for down-count n : set value of TAi register 000016 to FFF16          |

| Count start condition               | Set TAiS bit in the TABSR register to "1" (= start counting)                     |

| Count stop condition                | Set TAiS bit to "0" (= stop counting)                                            |

| Interrupt request generation timing | Timer overflow or underflow                                                      |

| TAilN pin function                  | I/O port or count source input                                                   |

| TAIOUT pin function                 | I/O port, pulse output, or up/down-count select input                            |

| Read from timer                     | Count value can be read by reading TAi register                                  |

| Write to timer                      | • When not counting and until the 1st count source is input after counting start |

|                                     | Value written to TAi register is written to both reload register and counter     |

|                                     | <ul> <li>When counting (after 1st count source input)</li> </ul>                 |

|                                     | Value written to TAi register is written to only reload register                 |

|                                     | (Transferred to counter when reloaded next)                                      |

| Select function                     | Free-run count function                                                          |

|                                     | Even when the timer overflows or underflows, the reload register content is      |

|                                     | not reloaded to it                                                               |

|                                     | Pulse output function                                                            |

|                                     | Whenever the timer underflows or underflows, the output polarity of TAiOUT       |

|                                     | pin is inverted. When not counting, the pin outputs a low.                       |

Table 12.1.2.1. Specifications in Event Counter Mode (when not processing two-phase pulse signal)

# 12.2.1 Timer Mode

In timer mode, the timer counts a count source generated internally (see Table 12.2.1.1). Figure 12.2.1.1 shows TBiMR register in timer mode.

| Item                                | Specification                                                                    |

|-------------------------------------|----------------------------------------------------------------------------------|

| Count source                        | f1, f2, f8, f32, fC32                                                            |

| Count operation                     | Down-count                                                                       |

|                                     | • When the timer underflows, it reloads the reload register contents and         |

|                                     | continues counting                                                               |

| Divide ratio                        | 1/(n+1) n: set value of TBi register (i= 0 to 2) 000016 to FFFF16                |

| Count start condition               | Set TBiS bit <sup>(1)</sup> to "1" (= start counting)                            |

| Count stop condition                | Set TBiS bit to "0" (= stop counting)                                            |

| Interrupt request generation timing | Timer underflow                                                                  |

| TBilN pin function                  | I/O port                                                                         |

| Read from timer                     | Count value can be read by reading TBi register                                  |

| Write to timer                      | • When not counting and until the 1st count source is input after counting start |

|                                     | Value written to TBi register is written to both reload register and counter     |

|                                     | <ul> <li>When counting (after 1st count source input)</li> </ul>                 |

|                                     | Value written to TBi register is written to only reload register                 |

|                                     | (Transferred to counter when reloaded next)                                      |

| Table 12.2.1.1 | Specifications | in | Timer | Mode |

|----------------|----------------|----|-------|------|

|----------------|----------------|----|-------|------|

NOTE:

1. The TB0S to TB2S bits are assigned to the bit 5 to bit 7 in the TABSR register.

| 7         b6         b5         b4         b3         b2         b1         b0                0         0 |            | nbol Address<br>to TB2MR 039B16 to 039D                                         | After reset<br>016 00XX00002                   |    |

|-----------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------|------------------------------------------------|----|

|                                                                                                           | Bit symbol | Bit name                                                                        | Function                                       | RW |

|                                                                                                           | TMOD0      | Operation mode select bit                                                       |                                                | RW |

|                                                                                                           | TMOD1      | 1                                                                               | 0 0 : Timer mode or A/D trigger mode           | RW |

|                                                                                                           | MR0        | Has no effect in timer mode                                                     |                                                | RW |

|                                                                                                           | MR1        | Can be set to "0" or "1"                                                        |                                                | RW |

|                                                                                                           | MR2        | TB0MR register<br>Must be set to "0" in timer mode                              |                                                | RW |

|                                                                                                           |            | TB1MR, TB2MR registers<br>Nothing is assigned. When<br>content is indeterminate | write, set to "0". When read, its              |    |

| L                                                                                                         | MR3        | When write in timer mode, s content is indeterminate.                           | set to "0". When read in timer mode, its       | RO |

|                                                                                                           | TCK0       | Count source select bit                                                         | <sup>b7 b6</sup><br>0 0 : f1 or f2<br>0 1 : f8 | RW |

|                                                                                                           | TCK1       |                                                                                 | 1 0 : f32<br>1 1 : fC32                        | RW |

| Dimer Ai mode regist           b7         b6         b5         b4         b3         b2         b1         b0           0         1         0         1         0         1         0 | Symbol<br>TA1MR<br>TA2MR<br>TA4MR                                          | 039716<br>039816                                                                                                                                                             | After reset<br>0016<br>0016<br>0016                                                                                                                                                                                                                                                                                      |                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                                                                                                                                                                        | Bit symbol                                                                 | Bit name                                                                                                                                                                     | Function                                                                                                                                                                                                                                                                                                                 | RW                                                 |

|                                                                                                                                                                                        | TMOD0                                                                      | Operation mode                                                                                                                                                               | Must set to "102" (one-shot timer mode) for                                                                                                                                                                                                                                                                              | RW                                                 |

|                                                                                                                                                                                        | TMOD1                                                                      | select bit                                                                                                                                                                   | the three-phase motor control timer function                                                                                                                                                                                                                                                                             | RW                                                 |

|                                                                                                                                                                                        | MR0                                                                        | Pulse output function select bit                                                                                                                                             | Must set to "0" for the three-phase motor<br>control timer function                                                                                                                                                                                                                                                      | -                                                  |

|                                                                                                                                                                                        | MR1                                                                        | External trigger select<br>bit                                                                                                                                               | Has no effect for the three-phase motor<br>control timer function                                                                                                                                                                                                                                                        | RW                                                 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                  | MR2                                                                        | Trigger select bit                                                                                                                                                           | Must set to "1" (selected by event/trigger<br>select register) for the three-phase motor<br>control timer function                                                                                                                                                                                                       | RW                                                 |

|                                                                                                                                                                                        | MR3                                                                        | Must set to "0" for the thre                                                                                                                                                 | e-phase motor control timer function                                                                                                                                                                                                                                                                                     | RW                                                 |

| <br>                                                                                                                                                                                   | ТСК0                                                                       | Count source select bit                                                                                                                                                      | b7 b6<br>0 0 : f1 or f2<br>0 1 : f8                                                                                                                                                                                                                                                                                      | RW                                                 |

|                                                                                                                                                                                        | TCK1                                                                       |                                                                                                                                                                              | 1 0 : f32                                                                                                                                                                                                                                                                                                                | RW                                                 |

| Timer B2 mode regis                                                                                                                                                                    | ter<br>Symbo                                                               |                                                                                                                                                                              | 1 1 : fc32<br>After reset                                                                                                                                                                                                                                                                                                |                                                    |

|                                                                                                                                                                                        | ter<br>Symbo<br>TB2MF                                                      | R 039D16                                                                                                                                                                     | 1 1 : fc32<br>After reset<br>00XX00002                                                                                                                                                                                                                                                                                   |                                                    |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                                                | ter<br>Symbo<br>TB2MF<br>Bit symbol                                        | 8 039D16<br>Bit name                                                                                                                                                         | 1 1 : fc32<br>After reset<br>00XX00002<br>Function                                                                                                                                                                                                                                                                       | RW                                                 |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                                                | ter<br>Symbo<br>TB2MF                                                      | R 039D16                                                                                                                                                                     | 1 1 : fc32<br>After reset<br>00XX00002                                                                                                                                                                                                                                                                                   | RW                                                 |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                                                | ter<br>Symbo<br>TB2MF<br>Bit symbol<br>TMOD0                               | Bit name Operation mode select bit                                                                                                                                           | 1 1 : fc32         After reset         00XX00002         Function         Set to "002" (timer mode) for the three-phase motor control timer function                                                                                                                                                                     | RW<br>RW<br>RW                                     |

| <u>b7 b6 b5 b4 b3 b2 b1 b0</u>                                                                                                                                                         | ter<br>Symbo<br>TB2MF<br>Bit symbol<br>TMOD0<br>TMOD1                      | Bit name Bit name Operation mode select bit Has no effect for the three                                                                                                      | 1 1 : fc32<br>After reset<br>00XX00002<br>Function<br>Set to "002" (timer mode) for the three-                                                                                                                                                                                                                           | RW<br>RW<br>RW                                     |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                                                | ter<br>Symbo<br>TB2MF<br>Bit symbol<br>TMOD0<br>TMOD1<br>MR0               | Bit name<br>Bit name<br>Operation mode select bit<br>Has no effect for the three<br>When write, set to "0". Whe                                                              | 1 1 : fc32         After reset         00XX00002         Function         Set to "002" (timer mode) for the three-phase motor control timer function         .phase motor control timer function.                                                                                                                        | RW<br>RW<br>RW<br>RW                               |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                                                | ter<br>Symbo<br>TB2MF<br>Bit symbol<br>TMOD0<br>TMOD1<br>MR0<br>MR1        | Bit name<br>Bit name<br>Operation mode select bit<br>Has no effect for the three<br>When write, set to "0". Wh<br>Must set to "0" for the three                              | 1 1 : fc32         After reset         00XX00002         Function         Set to "002" (timer mode) for the three-phase motor control timer function         ephase motor control timer function.         e-phase motor control timer function         motor control timer function         motor control timer function | RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                                                | ter<br>Symbo<br>TB2MF<br>Bit symbol<br>TMOD0<br>TMOD1<br>MR0<br>MR1<br>MR2 | Bit name<br>Bit name<br>Operation mode select bit<br>Has no effect for the three<br>When write, set to "0". Wh<br>Must set to "0" for the three<br>When write in three-phase | 1 1 : fc32         After reset         00XX00002         Function         Set to "002" (timer mode) for the three-phase motor control timer function         ephase motor control timer function.         e-phase motor control timer function         motor control timer function         motor control timer function | RW<br>RW<br>RW<br>RW<br>RW<br>RW                   |

Figure 12.3.8. TA1MR, TA2MR, TA4MR, and TB2MR Registers

| b6 b5 b4                             | b3 b2 b1 b0                      | U                                                                                   | -,                                                                                                                                                                                                                               | dress After reset<br>, 03A816 0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

|--------------------------------------|----------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|                                      |                                  | Bit<br>symbol                                                                       | Bit name                                                                                                                                                                                                                         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RV                                     |

|                                      |                                  | SMD0                                                                                | Serial I/O mode select bit (2)                                                                                                                                                                                                   | b2b1b0<br>0 0 0 : Serial I/O disabled<br>0 0 1 : Clock synchronous serial I/O mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RV                                     |

|                                      |                                  | SMD1                                                                                |                                                                                                                                                                                                                                  | 1 0 0 : UART mode transfer data 7 bits long<br>1 0 1 : UART mode transfer data 8 bits long<br>1 1 0 : UART mode transfer data 8 bits long                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RV                                     |

|                                      |                                  | SMD2                                                                                |                                                                                                                                                                                                                                  | Do not set value other than the above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RV                                     |

|                                      |                                  | CKDIR                                                                               | Internal/external clock select bit                                                                                                                                                                                               | 0 : Internal clock<br>1 : External clock (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RV                                     |

|                                      |                                  | STPS                                                                                | Stop bit length select bit                                                                                                                                                                                                       | 0 : One stop bit<br>1 : Two stop bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RV                                     |

|                                      |                                  | PRY                                                                                 | Odd/even parity select bit                                                                                                                                                                                                       | Effective when PRYE = 1<br>0 : Odd parity<br>1 : Even parity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RV                                     |

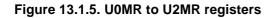

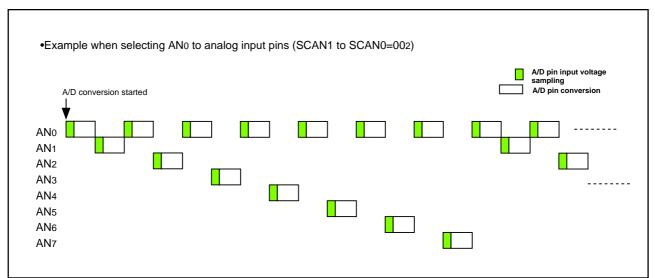

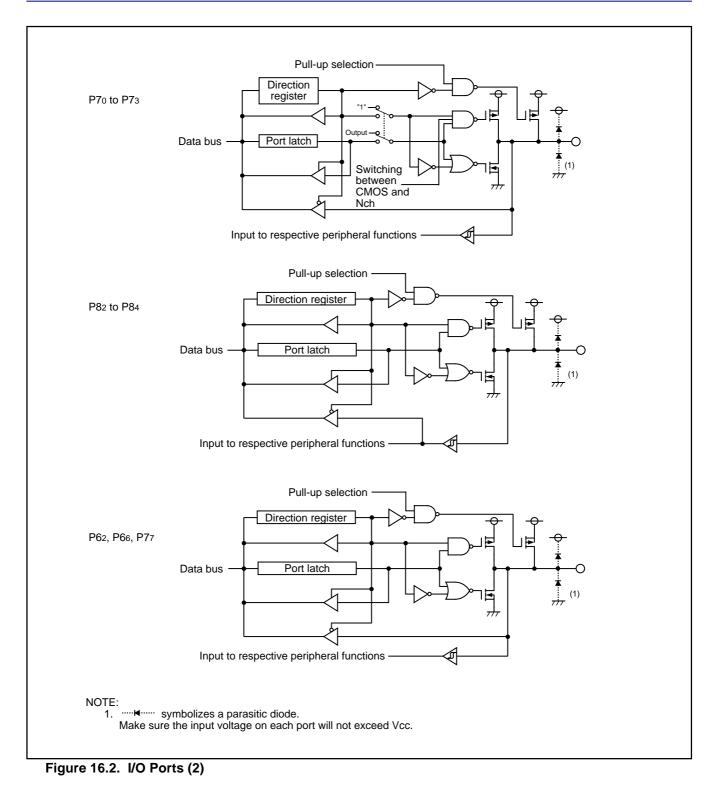

| L                                    |                                  | PRYE                                                                                | Parity enable bit                                                                                                                                                                                                                | 0 : Parity disabled<br>1 : Parity enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RV                                     |