Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                             |

|----------------------------|--------------------------------------------------------------------|

| Core Processor             | ARM7®                                                              |

| Core Size                  | 16/32-Bit                                                          |

| Speed                      | 44MHz                                                              |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                         |

| Peripherals                | PLA, PWM, PSM, Temp Sensor, WDT                                    |

| Number of I/O              | 13                                                                 |

| Program Memory Size        | 32KB (16K x 16)                                                    |

| Program Memory Type        | FLASH                                                              |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 1K x 32                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                        |

| Data Converters            | A/D 8x12b; D/A 2x12b                                               |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 40-VFQFN Exposed Pad, CSP                                          |

| Supplier Device Package    | 40-LFCSP-VQ (6x6)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7021bcpz32 |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

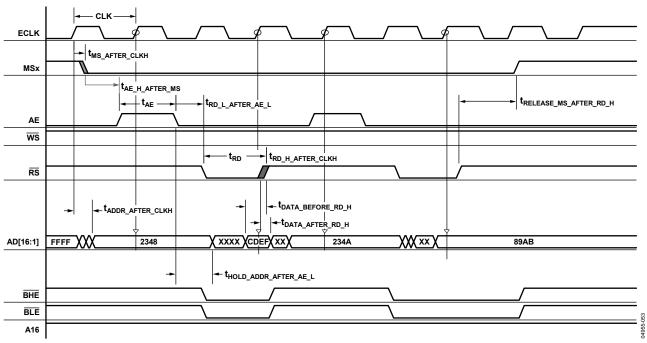

## Table 3. External Memory Read Cycle

| Parameter                          | Min        | Тур                                          | Max | Unit |

|------------------------------------|------------|----------------------------------------------|-----|------|

| CLK <sup>1</sup>                   | 1/MD clock | ns typ $\times$ (POWCON[2:0] + 1)            |     |      |

| tms_after_clkh                     | 4          |                                              | 8   | ns   |

| <b>t</b> ADDR_AFTER_CLKH           | 4          |                                              | 16  | ns   |

| t <sub>AE_H_AFTER_MS</sub>         |            | ½ CLK                                        |     |      |

| t <sub>AE</sub>                    |            | $(XMxPAR[14:12] + 1) \times CLK$             |     |      |

| thold_addr_after_ae_l              |            | 1/2 CLK + (! XMxPAR[10] ) × CLK              |     |      |

| trd_l_after_ae_l                   |            | 1/2 CLK + (! XMxPAR[10]+ ! XMxPAR[9] ) × CLK |     |      |

| trd_h_after_clkh                   | 0          |                                              | 4   |      |

| t <sub>RD</sub>                    |            | $(XMxPAR[3:0] + 1) \times CLK$               |     |      |

| tdata_before_rd_h                  | 16         |                                              |     | ns   |

| tdata_after_rd_h                   | 8          | + (! XMxPAR[9]) $\times$ CLK                 |     |      |

| t <sub>RELEASE_MS_AFTER_RD_H</sub> |            | 1 × CLK                                      |     |      |

<sup>1</sup> See Table 78.

Figure 13. External Memory Read Cycle (See Table 78)

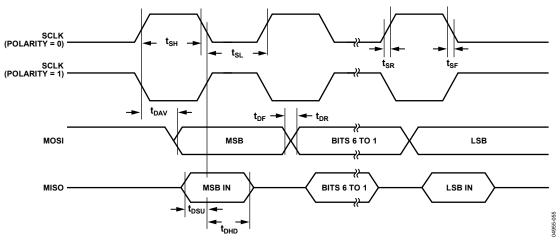

| Parameter        | Description                                         | Min                   | Тур                            | Мах  | Unit |

|------------------|-----------------------------------------------------|-----------------------|--------------------------------|------|------|

| t <sub>sL</sub>  | SCLK low pulse width <sup>1</sup>                   |                       | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>sH</sub>  | SCLK high pulse width <sup>1</sup>                  |                       | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>DAV</sub> | Data output valid after SCLK edge                   |                       |                                | 25   | ns   |

| t <sub>DSU</sub> | Data input setup time before SCLK edge <sup>2</sup> | 1 × t <sub>UCLK</sub> |                                |      | ns   |

| <b>t</b> DHD     | Data input hold time after SCLK edge <sup>2</sup>   | $2 	imes t_{UCLK}$    |                                |      | ns   |

| t <sub>DF</sub>  | Data output fall time                               |                       | 5                              | 12.5 | ns   |

| t <sub>DR</sub>  | Data output rise time                               |                       | 5                              | 12.5 | ns   |

| t <sub>sr</sub>  | SCLK rise time                                      |                       | 5                              | 12.5 | ns   |

| t <sub>SF</sub>  | SCLK fall time                                      |                       | 5                              | 12.5 | ns   |

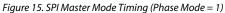

#### Table 6. SPI Master Mode Timing (Phase Mode = 1)

<sup>1</sup> t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCONMMR. t<sub>HCLK</sub> =  $t_{UCLK}/2^{CD}$ ; see Figure 67. <sup>2</sup> t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider; see Figure 67.

## Table 12. Pin Function Descriptions (ADuC7024/ADuC7025 64-Lead LFCSP\_VQ and 64-Lead LQFP)

| Pin No. | Mnemonic                                | Description                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ADC4                                    | Single-Ended or Differential Analog Input 4.                                                                                                                                                                                                                                           |

| 2       | ADC5                                    | Single-Ended or Differential Analog Input 5.                                                                                                                                                                                                                                           |

| 3       | ADC6                                    | Single-Ended or Differential Analog Input 6.                                                                                                                                                                                                                                           |

| 4       | ADC7                                    | Single-Ended or Differential Analog Input 7.                                                                                                                                                                                                                                           |

| 5       | ADC8                                    | Single-Ended or Differential Analog Input 8.                                                                                                                                                                                                                                           |

| 6       | ADC9                                    | Single-Ended or Differential Analog Input 9.                                                                                                                                                                                                                                           |

| 7       | GND <sub>REF</sub>                      | Ground Voltage Reference for the ADC. For optimal performance, the analog power supply should be separated from IOGND and DGND.                                                                                                                                                        |

| 8       | ADCNEG                                  | Bias Point or Negative Analog Input of the ADC in Pseudo Differential Mode. Must be connected<br>to the ground of the signal to convert. This bias point must be between 0 V and 1 V.                                                                                                  |

| 9       | DAC0/ADC12                              | DAC0 Voltage Output/Single-Ended or Differential Analog Input 12. DAC outputs are not present on the ADuC7025.                                                                                                                                                                         |

| 10      | DAC1/ADC13                              | DAC1 Voltage Output/Single-Ended or Differential Analog Input 13. DAC outputs are not present on the ADuC7025.                                                                                                                                                                         |

| 11      | тмѕ                                     | JTAG Test Port Input, Test Mode Select. Debug and download access.                                                                                                                                                                                                                     |

| 12      | TDI                                     | JTAG Test Port Input, Test Data In. Debug and download access                                                                                                                                                                                                                          |

| 13      | P4.6/PLAO[14]                           | General-Purpose Input and Output Port 4.6/Programmable Logic Array Output Element 14.                                                                                                                                                                                                  |

| 14      | P4.7/PLAO[15]                           | General-Purpose Input and Output Port 4.7/Programmable Logic Array Output Element 15.                                                                                                                                                                                                  |

| 15      | BM/P0.0/CMP <sub>out</sub> /PLAI[7]     | Multifunction I/O Pin. Boot mode. The ADuC7024/ADuC7025 enter download mode if BM is low at reset and execute code if BM is pulled high at reset through a 1 kΩ resistor/General-Purpose Input and Output Port 0.0/Voltage Comparator Output/Programmable Logic Array Input Element 7. |

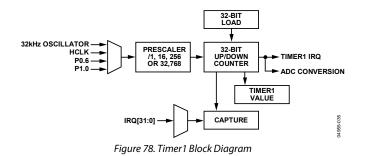

| 16      | P0.6/T1/MRST/PLAO[3]                    | Multifunction Pin, Driven Low After Reset. General-Purpose Output Port 0.6/Timer1 Input/Power-<br>On Reset Output/Programmable Logic Array Output Element 3.                                                                                                                           |

| 17      | тск                                     | JTAG Test Port Input, Test Clock. Debug and download access.                                                                                                                                                                                                                           |

| 18      | TDO                                     | JTAG Test Port Output, Test Data Out. Debug and download access.                                                                                                                                                                                                                       |

| 19      | IOGND                                   | Ground for GPIO (see Table 78). Typically connected to DGND.                                                                                                                                                                                                                           |

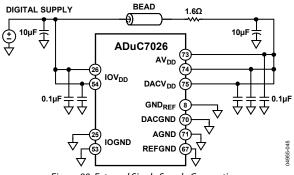

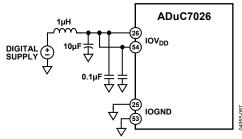

| 20      | IOV <sub>DD</sub>                       | 3.3 V Supply for GPIO (see Table 78) and Input of the On-Chip Voltage Regulator.                                                                                                                                                                                                       |

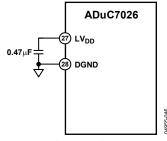

| 21      | LV <sub>DD</sub>                        | 2.6 V Output of the On-Chip Voltage Regulator. This output must be connected to a 0.47 $\mu F$ capacitor to DGND only.                                                                                                                                                                 |

| 22      | DGND                                    | Ground for Core Logic.                                                                                                                                                                                                                                                                 |

| 23      | P3.0/PWM0 <sub>H</sub> /PLAI[8]         | General-Purpose Input and Output Port 3.0/PWM Phase 0 High-Side Output/Programmable Logic<br>Array Input Element 8.                                                                                                                                                                    |

| 24      | P3.1/PWM0∟/PLAI[9]                      | General-Purpose Input and Output Port 3.1/PWM Phase 0 Low-Side Output/Programmable Logic Array Input Element 9.                                                                                                                                                                        |

| 25      | P3.2/PWM1 <sub>H</sub> /PLAI[10]        | General-Purpose Input and Output Port 3.2/PWM Phase 1 High-Side Output/Programmable Logic<br>Array Input Element 10.                                                                                                                                                                   |

| 26      | P3.3/PWM1L/PLAI[11]                     | General-Purpose Input and Output Port 3.3/PWM Phase 1 Low-Side Output/Programmable Logic Array Input Element 11.                                                                                                                                                                       |

| 27      | P0.3/TRST/ADC <sub>BUSY</sub>           | General-Purpose Input and Output Port 0.3/JTAG Test Port Input, Test Reset/ADC <sub>BUSY</sub> Signal Output.                                                                                                                                                                          |

| 28      | RST                                     | Reset Input, Active Low.                                                                                                                                                                                                                                                               |

| 29      | P3.4/PWM2 <sub>H</sub> /PLAI[12]        | General-Purpose Input and Output Port 3.4/PWM Phase 2 High-Side Output/Programmable Logic Array Input 12.                                                                                                                                                                              |

| 30      | P3.5/PWM2L/PLAI[13]                     | General-Purpose Input and Output Port 3.5/PWM Phase 2 Low-Side Output/Programmable Logic Array Input Element 13.                                                                                                                                                                       |

| 31      | IRQ0/P0.4/PWM <sub>TRIP</sub> /PLAO[1]  | Multifunction I/O Pin. External Interrupt Request 0, Active High/General-Purpose Input and<br>Output Port 0.4/PWM Trip External Input/Programmable Logic Array Output Element 1.                                                                                                       |

| 32      | IRQ1/P0.5/ADC <sub>BUSY</sub> /PLAO[2]  | Multifunction I/O Pin. External Interrupt Request 1, Active High/General-Purpose Input and Output Port 0.5/ADC <sub>BUSY</sub> Signal Output/Programmable Logic Array Output Element 2.                                                                                                |

| 33      | P2.0/SPM9/PLAO[5]/CONV <sub>START</sub> | Serial Port Multiplexed. General-Purpose Input and Output Port 2.0/UART/Programmable Logic<br>Array Output Element 5/Start Conversion Input Signal for ADC.                                                                                                                            |

| 34      | P0.7/ECLK/XCLK/SPM8/PLAO[4]             | Serial Port Multiplexed. General-Purpose Input and Output Port 0.7/Output for External Clock<br>Signal/Input to the Internal Clock Generator Circuits/UART/Programmable Logic Array Output<br>Element 4.                                                                               |

| 35      | XCLKO                                   | Output from the Crystal Oscillator Inverter.                                                                                                                                                                                                                                           |

| 36      | XCLKI                                   | Input to the Crystal Oscillator Inverter and Input to the Internal Clock Generator Circuits.                                                                                                                                                                                           |

| Pin No. | Mnemonic                               | Description                                                                                                                                                         |

|---------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46      | P3.6/AD6/PWM <sub>TRIP</sub> /PLAI[14] | General-Purpose Input and Output Port 3.6/External Memory Interface/PWM Safety Cutoff/<br>Programmable Logic Array Input Element 14.                                |

| 47      | P3.7/AD7/PWM <sub>SYNC</sub> /PLAI[15] | General-Purpose Input and Output Port 3.7/External Memory Interface/PWM Synchronization/<br>Programmable Logic Array Input Element 15.                              |

| 48      | P2.7/PWM1L/MS3                         | General-Purpose Input and Output Port 2.7/PWM Phase 1 Low-Side Output/External Memory Select 3.                                                                     |

| 49      | P2.1/WS/PWM0 <sub>H</sub> /PLAO[6]     | General-Purpose Input and Output Port 2.1/External Memory Write Strobe/PWM Phase 0 High-<br>Side Output/Programmable Logic Array Output Element 6.                  |

| 50      | P2.2/RS/PWM0L/PLAO[7]                  | General-Purpose Input and Output Port 2.2/External Memory Read Strobe/PWM Phase 0 Low-<br>Side Output/Programmable Logic Array Output Element 7.                    |

| 51      | P1.7/SPM7/PLAO[0]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.7/UART, SPI/Programmable Logic Array Output Element 0.                                             |

| 52      | P1.6/SPM6/PLAI[6]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.6/UART, SPI/Programmable Logic<br>Array Input Element 6.                                           |

| 53      | IOGND                                  | Ground for GPIO (see Table 78). Typically connected to DGND.                                                                                                        |

| 54      | IOV <sub>DD</sub>                      | 3.3 V Supply for GPIO (see Table 78) and Input of the On-Chip Voltage Regulator.                                                                                    |

| 55      | P4.0/AD8/PLAO[8]                       | General-Purpose Input and Output Port 4.0/External Memory Interface/Programmable Logic<br>Array Output Element 8.                                                   |

| 56      | P4.1/AD9/PLAO[9]                       | General-Purpose Input and Output Port 4.1/External Memory Interface/Programmable Logic<br>Array Output Element 9.                                                   |

| 57      | P1.5/SPM5/PLAI[5]/IRQ3                 | Serial Port Multiplexed. General-Purpose Input and Output Port 1.5/UART, SPI/Programmable Logic Array Input Element 5/External Interrupt Request 3, Active High.    |

| 58      | P1.4/SPM4/PLAI[4]/IRQ2                 | Serial Port Multiplexed. General-Purpose Input and Output Port 1.4/UART, SPI/Programmable Logic<br>Array Input Element 4/External Interrupt Request 2, Active High. |

| 59      | P1.3/SPM3/PLAI[3]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.3/UART, I2C1/Programmable Logic Array Input Element 3.                                             |

| 60      | P1.2/SPM2/PLAI[2]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.2/UART, I2C1/Programmable Logic Array Input Element 2.                                             |

| 61      | P1.1/SPM1/PLAI[1]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.1/UART, I2C0/Programmable<br>Logic Array Input Element 1.                                          |

| 62      | P1.0/T1/SPM0/PLAI[0]                   | Serial Port Multiplexed. General-Purpose Input and Output Port 1.0/Timer1 Input/UART, I2C0/<br>Programmable Logic Array Input Element 0.                            |

| 63      | P4.2/AD10/PLAO[10]                     | General-Purpose Input and Output Port 4.2/External Memory Interface/Programmable Logic Array Output Element 10.                                                     |

| 64      | P4.3/AD11/PLAO[11]                     | General-Purpose Input and Output Port 4.3/External Memory Interface/Programmable Logic Array Output Element 11.                                                     |

| 65      | P4.4/AD12/PLAO[12]                     | General-Purpose Input and Output Port 4.4/External Memory Interface/Programmable Logic Array Output Element 12.                                                     |

| 66      | P4.5/AD13/PLAO[13]                     | General-Purpose Input and Output Port 4.5/External Memory Interface/Programmable Logic Array Output Element 13.                                                     |

| 67      | REFGND                                 | Ground for the Reference. Typically connected to AGND.                                                                                                              |

| 68      | V <sub>REF</sub>                       | 2.5 V Internal Voltage Reference. Must be connected to a 0.47 $\mu\text{F}$ capacitor when using the internal reference.                                            |

| 69      | DAC <sub>REF</sub>                     | External Voltage Reference for the DACs. Range: DACGND to DACVDD.                                                                                                   |

| 70      | DACGND                                 | Ground for the DAC. Typically connected to AGND.                                                                                                                    |

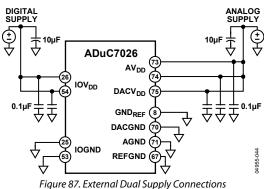

| 71, 72  | AGND                                   | Analog Ground. Ground reference point for the analog circuitry.                                                                                                     |

| 73, 74  | AV <sub>DD</sub>                       | 3.3 V Analog Power.                                                                                                                                                 |

| 75      | DACV <sub>DD</sub>                     | 3.3 V Power Supply for the DACs. Must be connected to AV <sub>DD</sub> .                                                                                            |

| 76      | ADC11                                  | Single-Ended or Differential Analog Input 11.                                                                                                                       |

| 77      | ADC0                                   | Single-Ended or Differential Analog Input 0.                                                                                                                        |

| 78      | ADC1                                   | Single-Ended or Differential Analog Input 1.                                                                                                                        |

| 79      | ADC2/CMP0                              | Single-Ended or Differential Analog Input 2/Comparator Positive Input.                                                                                              |

| 80      | ADC3/CMP1                              | Single-Ended or Differential Analog Input 3/Comparator Negative Input.                                                                                              |

| Pin No. | Mnemonic                                | Description                                                                                                                                                                                                                                                                                  |

|---------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1      | TMS                                     | JTAG Test Port Input, Test Mode Select. Debug and download access.                                                                                                                                                                                                                           |

| E2      | BM/P0.0/CMP <sub>OUT</sub> /PLAI[7]     | Multifunction I/O Pin. Boot mode. The ADuC7029 enters UART download mode if BM is low at reset and executes code if BM is pulled high at reset through a 1 k $\Omega$ resistor/General-Purpose Input and Output Port 0.0/Voltage Comparator Output/Programmable Logic Array Input Element 7. |

| E3      | DAC2/ADC14                              | DAC2 Voltage Output/ADC Input 14.                                                                                                                                                                                                                                                            |

| E4      | IOV <sub>DD</sub>                       | 3.3 V Supply for GPIO (see Table 78) and Input of the On-Chip Voltage Regulator.                                                                                                                                                                                                             |

| E5      | P3.2/PWM1 <sub>H</sub> /PLAI[10]        | General-Purpose Input and Output Port 3.2/PWM Phase 1 High-Side Output/Programmable Logic Array Input Element 10.                                                                                                                                                                            |

| E6      | P3.5/PWM2L/PLAI[13]                     | General-Purpose Input and Output Port 3.5/PWM Phase 2 Low-Side Output/Programmable Logic Array Input Element 13.                                                                                                                                                                             |

| E7      | P0.7/ECLK/XCLK/SPM8/PLAO[4]             | Serial Port Multiplexed. General-Purpose Input and Output Port 0.7/Output for External Clock Signal/Input to the Internal Clock Generator Circuits/UART/Programmable Logic Array Output Element 4.                                                                                           |

| F1      | TDI                                     | JTAG Test Port Input, Test Data In. Debug and download access.                                                                                                                                                                                                                               |

| F2      | P0.6/T1/MRST/PLAO[3]                    | Multifunction Pin, Driven Low After Reset. General-Purpose Output Port 0.6/Timer1 Input/<br>Power-On Reset Output/Programmable Logic Array Output Element 3.                                                                                                                                 |

| F3      | IOGND                                   | Ground for GPIO (see Table 78). Typically connected to DGND.                                                                                                                                                                                                                                 |

| F4      | P3.1/PWM0L/PLAI[9]                      | General-Purpose Input and Output Port 3.1/PWM Phase 0 Low-Side Output/Programmable<br>Logic Array Input Element 9.                                                                                                                                                                           |

| F5      | P3.0/PWM0 <sub>H</sub> /PLAI[8]         | General-Purpose Input and Output Port 3.0/PWM Phase 0 High-Side Output/Programmable Logic Array Input Element 8.                                                                                                                                                                             |

| F6      | RST                                     | Reset Input, Active Low.                                                                                                                                                                                                                                                                     |

| F7      | P2.0/SPM9/PLAO[5]/CONV <sub>START</sub> | Serial Port Multiplexed. General-Purpose Input and Output Port 2.0/UART/Programmable Logic Array Output Element 5/Start Conversion Input Signal for ADC.                                                                                                                                     |

| G1      | тск                                     | JTAG Test Port Input, Test Clock. Debug and download access.                                                                                                                                                                                                                                 |

| G2      | TDO                                     | JTAG Test Port Output, Test Data Out. Debug and download access.                                                                                                                                                                                                                             |

| G3      | LV <sub>DD</sub>                        | 2.6 V Output of the On-Chip Voltage Regulator. This output must be connected to a 0.47 $\mu\text{F}$ capacitor to DGND only.                                                                                                                                                                 |

| G4      | DGND                                    | Ground for Core Logic.                                                                                                                                                                                                                                                                       |

| G5      | P0.3/TRST/ADC <sub>BUSY</sub>           | General-Purpose Input and Output Port 0.3/JTAG Test Port Input, Test Reset/ADC $_{\mbox{\scriptsize BUSY}}$ Signal Output.                                                                                                                                                                   |

| G6      | IRQ0/P0.4/PWMTRIP/PLAO[1]               | Multifunction I/O Pin. External Interrupt Request 0, Active High/General-Purpose Input and Output Port 0.4/PWM Trip External Input/Programmable Logic Array Output Element 1.                                                                                                                |

| G7      | IRQ1/P0.5/ADC <sub>BUSY</sub> /PLAO[2]  | Multifunction I/O Pin. External Interrupt Request 1, Active High/General-Purpose Input and Output Port 0.5/ADC <sub>BUSY</sub> Signal Output/Programmable Logic Array Output Element 2.                                                                                                      |

|                              |          |      |                | Defects          |      |  |  |

|------------------------------|----------|------|----------------|------------------|------|--|--|

| Address                      | Name     | Byte | Access<br>Type | Default<br>Value | Page |  |  |

| PLA Base Address = 0xFFF0B00 |          |      |                |                  |      |  |  |

| 0x0B00                       | PLAELMO  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B04                       | PLAELM1  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B08                       | PLAELM2  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B0C                       | PLAELM3  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B10                       | PLAELM4  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B14                       | PLAELM5  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B18                       | PLAELM6  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B1C                       | PLAELM7  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B20                       | PLAELM8  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B24                       | PLAELM9  | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B28                       | PLAELM10 | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B2C                       | PLAELM11 | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B30                       | PLAELM12 | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B34                       | PLAELM13 | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B38                       | PLAELM14 | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B3C                       | PLAELM15 | 2    | R/W            | 0x0000           | 80   |  |  |

| 0x0B40                       | PLACLK   | 1    | R/W            | 0x00             | 81   |  |  |

| 0x0B44                       | PLAIRQ   | 4    | R/W            | 0x00000000       | 81   |  |  |

| 0x0B48                       | PLAADC   | 4    | R/W            | 0x0000000        | 82   |  |  |

| 0x0B4C                       | PLADIN   | 4    | R/W            | 0x00000000       | 82   |  |  |

| 0x0B50                       | PLADOUT  | 4    | R              | 0x00000000       | 82   |  |  |

| 0x0B54                       | PLALCK   | 1    | W              | 0x00             | 82   |  |  |

External Memory Base Address = 0xFFFF000

|        | ,      |   |     |        |    |

|--------|--------|---|-----|--------|----|

| 0xF000 | XMCFG  | 1 | R/W | 0x00   | 90 |

| 0xF010 | XM0CON | 1 | R/W | 0x00   | 90 |

| 0xF014 | XM1CON | 1 | R/W | 0x00   | 90 |

| 0xF018 | XM2CON | 1 | R/W | 0x00   | 90 |

| 0xF01C | XM3CON | 1 | R/W | 0x00   | 90 |

| 0xF020 | XMOPAR | 2 | R/W | 0x70FF | 90 |

| 0xF024 | XM1PAR | 2 | R/W | 0x70FF | 90 |

| 0xF028 | XM2PAR | 2 | R/W | 0x70FF | 90 |

| 0xF02C | XM3PAR | 2 | R/W | 0x70FF | 90 |

|        |        |   |     |        |    |

| Address              | Name           | Byte     | Access<br>Type | Default<br>Value        | Page |

|----------------------|----------------|----------|----------------|-------------------------|------|

| GPIO Base            | e Address = 0x | FFFFF40  | 00             |                         |      |

| 0xF400               | <b>GP0CON</b>  | 4        | R/W            | 0x00000000              | 68   |

| 0xF404               | GP1CON         | 4        | R/W            | 0x00000000              | 68   |

| 0xF408               | GP2CON         | 4        | R/W            | 0x00000000              | 68   |

| 0xF40C               | GP3CON         | 4        | R/W            | 0x00000000              | 68   |

| 0xF410               | GP4CON         | 4        | R/W            | 0x00000000              | 68   |

| 0xF420               | GP0DAT         | 4        | R/W            | 0x000000XX1             | 70   |

| 0xF424               | GP0SET         | 4        | W              | 0x000000XX1             | 70   |

| 0xF428               | GP0CLR         | 4        | W              | 0x000000XX1             | 70   |

| 0xF42C               | GPOPAR         | 4        | R/W            | 0x20000000              | 68   |

| 0xF430               | GP1DAT         | 4        | R/W            | 0x000000XX1             | 69   |

| 0xF434               | GP1SET         | 4        | W              | 0x000000XX1             | 70   |

| 0xF438               | GP1CLR         | 4        | W              | 0x000000XX1             | 70   |

| 0xF43C               | GP1PAR         | 4        | R/W            | 0x00000000              | 68   |

| 0xF440               | GP2DAT         | 4        | R/W            | 0x000000XX1             | 69   |

| 0xF444               | GP2SET         | 4        | W              | 0x000000XX1             | 70   |

| 0xF448               | GP2CLR         | 4        | W              | 0x000000XX1             | 70   |

| 0xF450               | <b>GP3DAT</b>  | 4        | R/W            | 0x000000XX1             | 69   |

| 0xF454               | <b>GP3SET</b>  | 4        | Ŵ              | 0x000000XX1             | 70   |

| 0xF458               | GP3CLR         | 4        | w              | 0x000000XX1             | 70   |

| 0xF460               | GP4DAT         | 4        | R/W            | 0x000000XX <sup>1</sup> | 69   |

| 0xF464               | GP4SET         | 4        | W              | 0x000000XX <sup>1</sup> | 70   |

| 0xF468               | GP4CLR         | 4        | W              | 0x000000XX1             | 70   |

| $^{1}X = 0, 1, 2, 1$ | or 3.          |          |                |                         |      |

|                      | Base Address = | = 0xFFFF | F800           |                         |      |

| 0xF800               | FEESTA         | 1        | R              | 0x20                    | 52   |

| 0xF804               | FEEMOD         | 2        | R/W            | 0x0000                  | 52   |

| 0xF808               | FEECON         | 1        | R/W            | 0x07                    | 53   |

| 0xF80C               | FEEDAT         | 2        | R/W            | 0xXXXX <sup>1</sup>     | 53   |

| 0xF810               | FEEADR         | 2        | R/W            | 0x0000                  | 53   |

| 0xF818               | FEESIGN        | 3        | R              | 0xFFFFFF                | 53   |

| 0xF81C               | FEEPRO         | 4        | R/W            | 0x00000000              | 53   |

| 0xF820               | FEEHIDE        | 4        | R/W            | 0xFFFFFFFF              | 53   |

| $^{1}X = 0, 1, 2, -$ |                | <u> </u> | 1              | 1                       |      |

|                      | e Address = 0x | FFFFC    | 00             |                         |      |

| 0xFC00               | PWMCON         | 2        | R/W            | 0x0000                  | 66   |

| 0xFC04               | PWMSTA         | 2        | R/W            | 0x0000                  | 66   |

| 0xFC08               | PWMDAT0        | 2        | R/W            | 0x0000                  | 67   |

| 0xFC0C               | PWMDAT1        | 2        | R/W            | 0x0000                  | 67   |

| 0xFC10               | PWMCFG         | 2        | R/W            | 0x0000                  | 67   |

| 0xFC14               | PWMCH0         | 2        | R/W            | 0x0000                  | 67   |

| 0xFC18               | PWMCH1         | 2        | R/W            | 0x0000                  | 67   |

| 0xFC1C               | PWMCH2         | 2        | R/W            | 0x0000                  | 67   |

| 0xFC20               | PWMEN          | 2        | R/W            | 0x0000                  | 67   |

| UNI C20              |                | <b>_</b> | 10, 14         | 5,0000                  | 0,   |

2

R/W

0x0000

67

PWMDAT2

# Data Sheet

0xFC24

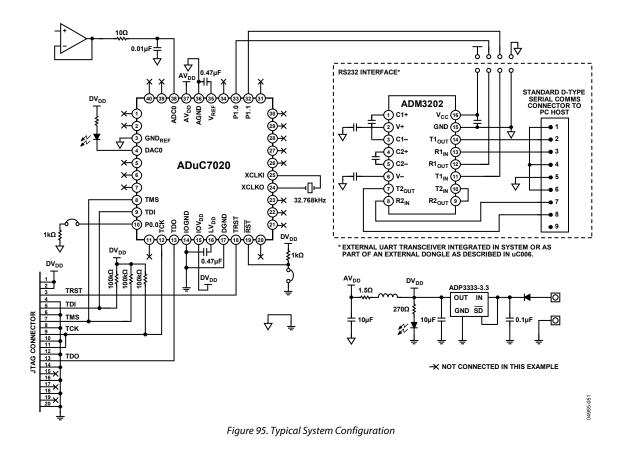

## **TYPICAL OPERATION**

Once configured via the ADC control and channel selection registers, the ADC converts the analog input and provides a 12-bit result in the ADC data register.

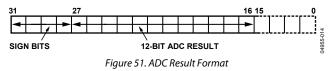

The top four bits are the sign bits. The 12-bit result is placed from Bit 16 to Bit 27, as shown in Figure 51. Again, it should be noted that, in fully differential mode, the result is represented in twos complement format. In pseudo differential and singleended modes, the result is represented in straight binary format.

The same format is used in DACxDAT, simplifying the software.

## **Current Consumption**

The ADC in standby mode, that is, powered up but not converting, typically consumes 640  $\mu$ A. The internal reference adds 140  $\mu$ A. During conversion, the extra current is 0.3  $\mu$ A multiplied by the sampling frequency (in kilohertz (kHz)). Figure 43 shows the current consumption vs. the sampling frequency of the ADC.

## Timing

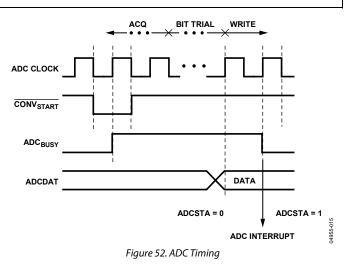

Figure 52 gives details of the ADC timing. Users control the ADC clock speed and the number of acquisition clocks in the ADCCON MMR. By default, the acquisition time is eight clocks and the clock divider is 2. The number of extra clocks (such as bit trial or write) is set to 19, which gives a sampling rate of 774 kSPS. For conversion on the temperature sensor, the ADC acquisition time is automatically set to 16 clocks, and the ADC clock divider is set to 32. When using multiple channels, including the temperature sensor, the timing settings revert to the user-defined settings after reading the temperature sensor channel.

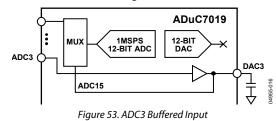

## ADuC7019

The ADuC7019 is identical to the ADuC7020 except for one buffered ADC channel, ADC3, and it has only three DACs. The output buffer of the fourth DAC is internally connected to the ADC3 channel as shown in Figure 53.

Note that the DAC3 output pin must be connected to a 10 nF capacitor to AGND. This channel should be used to measure dc voltages only. ADC calibration may be necessary on this channel.

## **MMRS INTERFACE**

The ADC is controlled and configured via the eight MMRs described in this section.

## Table 17. ADCCON Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| ADCCON | 0xFFFF0500 | 0x0600        | R/W    |

ADCCON is an ADC control register that allows the programmer to enable the ADC peripheral, select the mode of operation of the ADC (in single-ended mode, pseudo differential mode, or fully differential mode), and select the conversion type. This MMR is described in Table 18.

## Table 18. ADCCON MMR Bit Designations

| Bit   | Value        | Description                                                                                             |

|-------|--------------|---------------------------------------------------------------------------------------------------------|

| 15:13 |              | Reserved.                                                                                               |

| 12:10 |              | ADC clock speed.                                                                                        |

|       | 000          | fADC/1. This divider is provided to obtain                                                              |

|       |              | 1 MSPS ADC with an external clock <41.78 MHz.                                                           |

|       | 001          | fADC/2 (default value).                                                                                 |

|       | 010          | fADC/4.                                                                                                 |

|       | 011          | fADC/8.                                                                                                 |

|       | 100          | fADC/16.                                                                                                |

|       | 101          | fADC/32.                                                                                                |

| 9:8   |              | ADC acquisition time.                                                                                   |

|       | 00           | Two clocks.                                                                                             |

|       | 01           | Four clocks.                                                                                            |

|       | 10           | Eight clocks (default value).                                                                           |

|       | 11           | 16 clocks.                                                                                              |

| 7     |              | Enable start conversion.                                                                                |

|       |              | Set by the user to start any type of conversion                                                         |

|       |              | command. Cleared by the user to disable a                                                               |

|       |              | start conversion (clearing this bit does not stop the ADC when continuously converting).                |

| 6     |              | Reserved.                                                                                               |

| 0     |              | Reserved.                                                                                               |

| 5     |              | ADC power control.                                                                                      |

| J     |              | Set by the user to place the ADC in normal                                                              |

|       |              | mode (the ADC must be powered up for at least                                                           |

|       |              | 5 µs before it converts correctly). Cleared by the                                                      |

|       |              | user to place the ADC in power-down mode.                                                               |

| 4:3   |              | Conversion mode.                                                                                        |

|       | 00           | Single-ended mode.                                                                                      |

|       | 01           | Differential mode.                                                                                      |

|       | 10           | Pseudo differential mode.                                                                               |

|       | 11           | Reserved.                                                                                               |

| 2:0   |              | Conversion type.                                                                                        |

|       | 000          | Enable CONV <sub>START</sub> pin as a conversion input.                                                 |

|       | 001          | Enable Timer1 as a conversion input.                                                                    |

|       | 010          | Enable Timer0 as a conversion input.                                                                    |

|       | 011          | Single software conversion. Sets to 000 after                                                           |

|       |              | conversion (note that Bit 7 of ADCCON MMR                                                               |

|       |              | should be cleared after starting a single                                                               |

|       |              | software conversion to avoid <u>further</u><br>conversions triggered by the CONV <sub>START</sub> pin). |

|       | 100          |                                                                                                         |

|       | 100          | Continuous software conversion.                                                                         |

|       | 101<br>Other | PLA conversion.                                                                                         |

|       | Other        | Reserved.                                                                                               |

## Table 19. ADCCP Register

\_

| ADCCP 0xFFFF0504 0x00 R/W | Name  | Address    | Default Value | Access |

|---------------------------|-------|------------|---------------|--------|

|                           | ADCCP | 0xFFFF0504 | 0x00          | R/W    |

ADCCP is an ADC positive channel selection register. This MMR is described in Table 20.

## Table 20. ADCCP<sup>1</sup> MMR Bit Designation

| Bit | Value       | Description                                   |  |  |

|-----|-------------|-----------------------------------------------|--|--|

| 7:5 |             | Reserved.                                     |  |  |

| 4:0 |             | Positive channel selection bits.              |  |  |

|     | 00000       | ADC0.                                         |  |  |

|     | 00001       | ADC1.                                         |  |  |

|     | 00010       | ADC2.                                         |  |  |

|     | 00011       | ADC3.                                         |  |  |

|     | 00100       | ADC4.                                         |  |  |

|     | 00101       | ADC5.                                         |  |  |

|     | 00110 ADC6. |                                               |  |  |

|     | 00111       | ADC7.                                         |  |  |

|     | 01000       | ADC8.                                         |  |  |

|     | 01001       | ADC9.                                         |  |  |

|     | 01010       | ADC10.                                        |  |  |

|     | 01011       | ADC11.                                        |  |  |

|     | 01100       | DAC0/ADC12.                                   |  |  |

|     | 01101       | DAC1/ADC13.                                   |  |  |

|     | 01110       | DAC2/ADC14.                                   |  |  |

|     | 01111       | DAC3/ADC15.                                   |  |  |

|     | 10000       | Temperature sensor.                           |  |  |

|     | 10001       | AGND (self-diagnostic feature).               |  |  |

|     | 10010       | Internal reference (self-diagnostic feature). |  |  |

|     | 10011       | AV <sub>DD</sub> /2.                          |  |  |

|     | Others      | Reserved.                                     |  |  |

<sup>1</sup> ADC and DAC channel availability depends on the part model. See Ordering Guide for details.

## Table 21. ADCCN Register

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| ADCCN | 0xFFFF0508 | 0x01          | R/W    |

ADCCN is an ADC negative channel selection register. This MMR is described in Table 22.

## Table 22. ADCCN MMR Bit Designation

| Bit          | Value       | Description                                   |

|--------------|-------------|-----------------------------------------------|

| 7:5          |             | Reserved.                                     |

| 4:0          |             | Negative channel selection bits.              |

|              | 00000       | ADC0.                                         |

|              | 00001       | ADC1.                                         |

|              | 00010       | ADC2.                                         |

|              | 00011       | ADC3.                                         |

|              | 00100       | ADC4.                                         |

|              | 00101 ADC5. |                                               |

|              | 00110 ADC6. |                                               |

|              | 00111 ADC7. |                                               |

|              | 01000       | ADC8.                                         |

|              | 01001       | ADC9.                                         |

|              | 01010       | ADC10.                                        |

| 01011 ADC11. |             | ADC11.                                        |

|              | 01100       | DAC0/ADC12.                                   |

|              | 01101       | DAC1/ADC13.                                   |

|              | 01110       | DAC2/ADC14.                                   |

|              | 01111       | DAC3/ADC15.                                   |

|              | 10000       | Internal reference (self-diagnostic feature). |

|              | Others      | Reserved.                                     |

### Table 23. ADCSTA Register

| Name   | Address    | Default Value | Access |  |

|--------|------------|---------------|--------|--|

| ADCSTA | 0xFFFF050C | 0x00          | R      |  |

ADCSTA is an ADC status register that indicates when an ADC conversion result is ready. The ADCSTA register contains only one bit, ADCReady (Bit 0), representing the status of the ADC. This bit is set at the end of an ADC conversion, generating an ADC interrupt. It is cleared automatically by reading the ADCDAT MMR. When the ADC is performing a conversion, the status of the ADC can be read externally via the ADC<sub>BUSY</sub> pin. This pin is high during a conversion. When the conversion is finished,  $ADC_{BUSY}$  goes back low. This information can be available on P0.5 (see the General-Purpose Input/Output section) if enabled in the ADCCON register.

### Table 24. ADCDAT Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| ADCDAT | 0xFFFF0510 | 0x0000000     | R      |

ADCDAT is an ADC data result register. It holds the 12-bit ADC result as shown in Figure 51.

#### Table 25. ADCRST Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| ADCRST | 0xFFFF0514 | 0x00          | R/W    |

ADCRST resets the digital interface of the ADC. Writing any value to this register resets all the ADC registers to their default values.

### Table 26. ADCGN Register

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| ADCGN | 0xFFFF0530 | 0x0200        | R/W    |

ADCGN is a 10-bit gain calibration register.

### Table 27. ADCOF Register

| Name Address |            | Default Value | Access |  |

|--------------|------------|---------------|--------|--|

| ADCOF        | 0xFFFF0534 | 0x0200        | R/W    |  |

ADCOF is a 10-bit offset calibration register.

## **CONVERTER OPERATION**

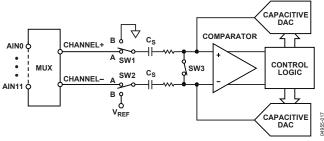

The ADC incorporates a successive approximation (SAR) architecture involving a charge-sampled input stage. This architecture can operate in three modes: differential, pseudo differential, and single-ended.

## **Differential Mode**

The ADuC7019/20/21/22/24/25/26/27/28/29 each contain a successive approximation ADC based on two capacitive DACs. Figure 54 and Figure 55 show simplified schematics of the ADC in acquisition and conversion phase, respectively. The ADC comprises control logic, a SAR, and two capacitive DACs. In Figure 54 (the acquisition phase), SW3 is closed and SW1 and SW2 are in Position A. The comparator is held in a balanced condition, and the sampling capacitor arrays acquire the differential signal on the input.

Figure 54. ADC Acquisition Phase

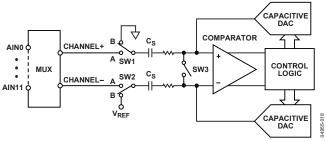

When the ADC starts a conversion, as shown in Figure 55, SW3 opens, and then SW1 and SW2 move to Position B. This causes the comparator to become unbalanced. Both inputs are disconnected once the conversion begins. The control logic and the charge redistribution DACs are used to add and subtract fixed amounts of charge from the sampling capacitor arrays to bring the comparator back into a balanced condition. When the comparator is rebalanced, the conversion is complete. The control logic generates the ADC output code. The output impedances of the sources driving the  $V_{IN+}$  and  $V_{IN-}$  input voltage pins must be matched; otherwise, the two inputs have different settling times, resulting in errors.

Figure 55. ADC Conversion Phase

## EXECUTION TIME FROM SRAM AND FLASH/EE

## **Execution from SRAM**

Fetching instructions from SRAM takes one clock cycle; the access time of the SRAM is 2 ns, and a clock cycle is 22 ns minimum. However, if the instruction involves reading or writing data to memory, one extra cycle must be added if the data is in SRAM (or three cycles if the data is in Flash/EE): one cycle to execute the instruction, and two cycles to get the 32-bit data from Flash/EE. A control flow instruction (a branch instruction, for example) takes one cycle to fetch but also takes two cycles to fill the pipeline with the new instructions.

## **Execution from Flash/EE**

Because the Flash/EE width is 16 bits and access time for 16-bit words is 22 ns, execution from Flash/EE cannot be done in one cycle (as can be done from SRAM when the CD Bit = 0). Also, some dead times are needed before accessing data for any value of the CD bit.

In ARM mode, where instructions are 32 bits, two cycles are needed to fetch any instruction when CD = 0. In thumb mode, where instructions are 16 bits, one cycle is needed to fetch any instruction.

Timing is identical in both modes when executing instructions that involve using the Flash/EE for data memory. If the instruction to be executed is a control flow instruction, an extra cycle is needed to decode the new address of the program counter, and then four cycles are needed to fill the pipeline. A data-processing instruction involving only the core register does not require any extra clock cycles. However, if it involves data in Flash/EE, an extra clock cycle is needed to decode the address of the data, and two cycles are needed to get the 32-bit data from Flash/EE. An extra cycle must also be added before fetching another instruction. Data transfer instructions are more complex and are summarized in Table 43.

| Instructions     | Fetch<br>Cycles | Dead<br>Time   | Data Access                         | Dead<br>Time |

|------------------|-----------------|----------------|-------------------------------------|--------------|

| LD <sup>1</sup>  | 2/1             | 1              | 2                                   | 1            |

| LDH              | 2/1             | 1              | 1                                   | 1            |

| LDM/PUSH         | 2/1             | N <sup>2</sup> | $2 \times N^2$                      | $N^1$        |

| STR <sup>1</sup> | 2/1             | 1              | 2 × 20 ns                           | 1            |

| STRH             | 2/1             | 1              | 20 ns                               | 1            |

| STRM/POP         | 2/1             | $N^1$          | $2 \times N \times 20 \text{ ns}^1$ | $N^1$        |

### Table 43. Execution Cycles in ARM/Thumb Mode

<sup>1</sup>The SWAP instruction combines an LD and STR instruction with only one fetch, giving a total of eight cycles + 40 ns.

$^2N$  is the amount of data to load or store in the multiple load/store instruction (1 < N  $\leq$  16).

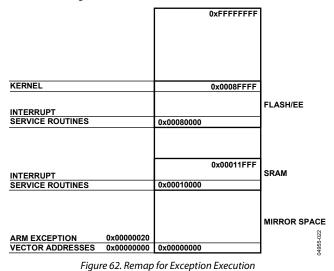

## **RESET AND REMAP**

The ARM exception vectors are all situated at the bottom of the memory array, from Address 0x00000000 to Address 0x00000020, as shown in Figure 62.

By default, and after any reset, the Flash/EE is mirrored at the bottom of the memory array. The remap function allows the programmer to mirror the SRAM at the bottom of the memory array, which facilitates execution of exception routines from SRAM instead of from Flash/EE. This means exceptions are executed twice as fast, being executed in 32-bit ARM mode with 32-bit wide SRAM instead of 16-bit wide Flash/EE memory.

## **Remap Operation**

When a reset occurs on the ADuC7019/20/21/22/24/25/26/27/ 28/29, execution automatically starts in the factory-programmed, internal configuration code. This kernel is hidden and cannot be accessed by user code. If the part is in normal mode (the BM pin is high), it executes the power-on configuration routine of the kernel and then jumps to the reset vector address, 0x00000000, to execute the user's reset exception routine.

Because the Flash/EE is mirrored at the bottom of the memory array at reset, the reset interrupt routine must always be written in Flash/EE.

The remap is done from Flash/EE by setting Bit 0 of the REMAP register. Caution must be taken to execute this command from Flash/EE, above Address 0x00080020, and not from the bottom of the array because this is replaced by the SRAM.

This operation is reversible. The Flash/EE can be remapped at Address 0x00000000 by clearing Bit 0 of the REMAP MMR. Caution must again be taken to execute the remap function from outside the mirrored area. Any type of reset remaps the Flash/EE memory at the bottom of the array.

### Example source code

```

t2val_old= T2VAL;

T2LD = 5;

TCON = 0x480;

while ((T2VAL == t2val_old) || (T2VAL >

3)) //ensures timer value loaded

IRQEN = 0x10;

//enable T2 interrupt

PLLKEY1 = 0xAA;

PLLCON = 0x01;

PLLKEY2 = 0x55;

POWKEY1 = 0x01;

POWCON = 0x27;

// Set Core into Nap mode

POWKEY2 = 0xF4;

```

In noisy environments, noise can couple to the external crystal pins, and PLL may lose lock momentarily. A PLL interrupt is provided in the interrupt controller. The core clock is immediately halted, and this interrupt is only serviced when the lock is restored.

In case of crystal loss, the watchdog timer should be used. During initialization, a test on the RSTSTA register can determine if the reset came from the watchdog timer.

## **External Clock Selection**

To switch to an external clock on P0.7, configure P0.7 in Mode 1. The external clock can be up to 44 MHz, providing the tolerance is 1%.

| Table 57. Operating | Modes |

|---------------------|-------|

|---------------------|-------|

## ADuC7019/20/21/22/24/25/26/27/28/29

#### Example source code

```

t2val_old= T2VAL;

T2LD = 5;

TCON = 0x480;

```

while ((T2VAL == t2val\_old) || (T2VAL

> 3)) //ensures timer value loaded

IRQEN = 0x10;

//enable T2 interrupt

PLLKEY1 = 0xAA;

PLLCON = 0x03; //Select external clock

PLLKEY2 = 0x55;

POWKEY1 = 0x01;

POWCON = 0x27;

// Set Core into Nap mode POWKEY2 = 0xF4;

## **Power Control System**

A choice of operating modes is available on the ADuC7019/20/ 21/22/24/25/26/27/28/29. Table 57 describes what part is powered on in the different modes and indicates the power-up time.

Table 58 gives some typical values of the total current consumption (analog + digital supply currents) in the different modes, depending on the clock divider bits. The ADC is turned off. Note that these values also include current consumption of the regulator and other parts on the test board where these values are measured.

|        | - I · · · · · | 9           |     |            |              |                                      |

|--------|---------------|-------------|-----|------------|--------------|--------------------------------------|

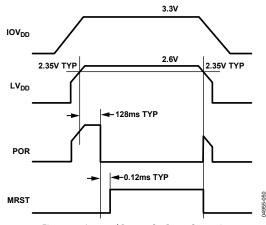

| Mode   | Core          | Peripherals | PLL | XTAL/T2/T3 | IRQ0 to IRQ3 | Start-Up/Power-On Time               |

| Active | Х             | Х           | Х   | Х          | Х            | 130 ms at CD = 0                     |

| Pause  |               | Х           | Х   | Х          | Х            | 24 ns at CD = 0; 3 $\mu$ s at CD = 7 |

| Nap    |               |             | Х   | Х          | Х            | 24 ns at CD = 0; 3 μs at CD = 7      |

| Sleep  |               |             |     | Х          | Х            | 1.58 ms                              |

| Stop   |               |             |     |            | Х            | 1.7 ms                               |

<sup>1</sup> X indicates that the part is powered on.

## Table 58. Typical Current Consumption at 25°C in Milliamperes

| /1      |        | 1      |        | 1      |        |        |        |        |        |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| PC[2:0] | Mode   | CD = 0 | CD = 1 | CD = 2 | CD = 3 | CD = 4 | CD = 5 | CD = 6 | CD = 7 |

| 000     | Active | 33.1   | 21.2   | 13.8   | 10     | 8.1    | 7.2    | 6.7    | 6.45   |

| 001     | Pause  | 22.7   | 13.3   | 8.5    | 6.1    | 4.9    | 4.3    | 4      | 3.85   |

| 010     | Nap    | 3.8    | 3.8    | 3.8    | 3.8    | 3.8    | 3.8    | 3.8    | 3.8    |

| 011     | Sleep  | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    |

| 100     | Stop   | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    |

### Table 70. PWMCFG Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| PWMCFG | 0xFFFFFC10 | 0x0000        | R/W    |

PWMCFG is a gate chopping register.

#### Table 71. PWMCFG MMR Bit Descriptions

| Bit   | Name   | Description                          |

|-------|--------|--------------------------------------|

| 15:10 |        | Reserved.                            |

| 9     | CHOPLO | Low-side gate chopping enable bit.   |

| 8     | CHOPHI | High-side gate chopping enable bit.  |

| 7:0   | GDCLK  | PWM gate chopping period (unsigned). |

#### Table 72. PWMEN Register

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| PWMEN | 0xFFFFFC20 | 0x0000        | R/W    |

PWMEN allows enabling of channel outputs and crossover. See its bit definitions in Table 73.

#### Table 73. PWMEN MMR Bit Descriptions

| Bit | Name      | Description                                                                                                                                                        |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | 0H0L_XOVR | Channel 0 output crossover enable bit.<br>Set to 1 by user to enable Channel 0 output<br>crossover. Cleared to 0 by user to disable<br>Channel 0 output crossover. |

| 7   | 1H1L_XOVR | Channel 1 output crossover enable bit.<br>Set to 1 by user to enable Channel 1 output<br>crossover. Cleared to 0 by user to disable<br>Channel 1 output crossover. |

| 6   | 2H2L_XOVR | Channel 2 output crossover enable bit.<br>Set to 1 by user to enable Channel 2 output<br>crossover. Cleared to 0 by user to disable<br>Channel 2 output crossover. |

| 5   | OL_EN     | 0L output enable bit. Set to 1 by user to<br>disable the 0L output of the PWM. Cleared to 0<br>by user to enable the 0L output of the PWM.                         |

| 4   | OH_EN     | 0H output enable bit. Set to 1 by user to<br>disable the 0H output of the PWM. Cleared to<br>0 by user to enable the 0H output of the PWM.                         |

| 3   | 1L_EN     | 1L output enable bit. Set to 1 by user to disable the 1L output of the PWM. Cleared to 0 by user to enable the 1L output of the PWM.                               |

| 2   | 1H_EN     | 1H Output Enable Bit. Set to 1 by user to disable the 1H output of the PWM. Cleared to 0 by user to enable the 1H output of the PWM.                               |

| 1   | 2L_EN     | 2L output enable bit. Set to 1 by user to disable the 2L output of the PWM. Cleared to 0 by user to enable the 2L output of the PWM.                               |

| 0   | 2H_EN     | 2H output enable bit. Set to 1 by user to disable the 2H output of the PWM. Cleared to 0 by user to enable the 2H output of the PWM.                               |

### Table 74. PWMDAT0 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| PWMDAT0 | 0xFFFFFC08 | 0x0000        | R/W    |

PWMDAT0 is an unsigned 16-bit register for switching period.

#### Table 75. PWMDAT1 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| PWMDAT1 | 0xFFFFFC0C | 0x0000        | R/W    |

PWMDAT1 is an unsigned 10-bit register for dead time.

#### Table 76. PWMCHx Registers

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| PWMCH0 | 0xFFFFFC14 | 0x0000        | R/W    |

| PWMCH1 | 0xFFFFFC18 | 0x0000        | R/W    |

| PWMCH2 | 0xFFFFFC1C | 0x0000        | R/W    |

PWMCH0, PWMCH1, and PWMCH2 are channel duty cycles for the three phases.

#### Table 77. PWMDAT2 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| PWMDAT2 | 0xFFFFFC24 | 0x0000        | R/W    |

PWMDAT2 is an unsigned 10-bit register for PWM sync pulse width.

## **GENERAL-PURPOSE INPUT/OUTPUT**

The ADuC7019/20/21/22/24/25/26/27/28/29 provide 40 general-purpose, bidirectional I/O (GPIO) pins. All I/O pins are 5 V tolerant, meaning the GPIOs support an input voltage of 5 V.

In general, many of the GPIO pins have multiple functions (see Table 78 for the pin function definitions). By default, the GPIO pins are configured in GPIO mode.

All GPIO pins have an internal pull-up resistor (of about 100 k $\Omega$ ), and their drive capability is 1.6 mA. Note that a maximum of 20 GPIOs can drive 1.6 mA at the same time. Using the GPxPAR registers, it is possible to enable/disable the pull-up resistors for the following ports: P0.0, P0.4, P0.5, P0.6, P0.7, and the eight GPIOs of P1.

The 40 GPIOs are grouped in five ports, Port 0 to Port 4 (Port x). Each port is controlled by four or five MMRs.

Note that the kernel changes P0.6 from its default configuration at reset (MRST) to GPIO mode. If MRST is used for external circuitry, an external pull-up resistor should be used to ensure that the level on P0.6 does not drop when the kernel switches mode. Otherwise, P0.6 goes low for the reset period. For example, if MRST is required for power-down, it can be reconfigured in GP0CON MMR.

The input level of any GPIO can be read at any time in the GPxDAT MMR, even when the pin is configured in a mode other than GPIO. The PLA input is always active.

When the ADuC7019/20/21/22/24/25/26/27/28/29 part enters a power-saving mode, the GPIO pins retain their state.

|      |      | Configuration |                        |      |          |

|------|------|---------------|------------------------|------|----------|

| Port | Pin  | 00            | 01                     | 10   | 11       |

| 0    | P0.0 | GPIO          | CMP                    | MS0  | PLAI[7]  |

|      | P0.1 | GPIO          | PWM2 <sub>H</sub>      | BLE  |          |

|      | P0.2 | GPIO          | PWM2∟                  | BHE  |          |

|      | P0.3 | GPIO          | TRST                   | A16  | ADCBUSY  |

|      | P0.4 | GPIO/IRQ0     | PWMTRIP                | MS1  | PLAO[1]  |

|      | P0.5 | GPIO/IRQ1     | ADCBUSY                | MS2  | PLAO[2]  |

|      | P0.6 | GPIO/T1       | MRST                   |      | PLAO[3]  |

|      | P0.7 | GPIO          | ECLK/XCLK <sup>1</sup> | SIN  | PLAO[4]  |

| 1    | P1.0 | GPIO/T1       | SIN                    | SCL0 | PLAI[0]  |

|      | P1.1 | GPIO          | SOUT                   | SDA0 | PLAI[1]  |

|      | P1.2 | GPIO          | RTS                    | SCL1 | PLAI[2]  |

|      | P1.3 | GPIO          | CTS                    | SDA1 | PLAI[3]  |

|      | P1.4 | GPIO/IRQ2     | RI                     | SCLK | PLAI[4]  |

|      | P1.5 | GPIO/IRQ3     | DCD                    | MISO | PLAI[5]  |

|      | P1.6 | GPIO          | DSR                    | MOSI | PLAI[6]  |

|      | P1.7 | GPIO          | DTR                    | CS   | PLAO[0]  |

| 2    | P2.0 | GPIO          |                        | SOUT | PLAO[5]  |

|      | P2.1 | GPIO          | PWM0 <sub>H</sub>      | WS   | PLAO[6]  |

|      | P2.2 | GPIO          | PWM0⊾                  | RS   | PLAO[7]  |

|      | P2.3 | GPIO          |                        | AE   |          |

|      | P2.4 | GPIO          | PWM0 <sub>H</sub>      | MS0  |          |

|      | P2.5 | GPIO          | PWM0∟                  | MS1  |          |

|      | P2.6 | GPIO          | PWM1 <sub>H</sub>      | MS2  |          |

|      | P2.7 | GPIO          | PWM1∟                  | MS3  |          |

| 3    | P3.0 | GPIO          | PWM0 <sub>H</sub>      | AD0  | PLAI[8]  |

|      | P3.1 | GPIO          | PWM0∟                  | AD1  | PLAI[9]  |

|      | P3.2 | GPIO          | PWM1 <sub>H</sub>      | AD2  | PLAI[10] |

|      | P3.3 | GPIO          | PWM1∟                  | AD3  | PLAI[11] |

|      | P3.4 | GPIO          | PWM2 <sub>H</sub>      | AD4  | PLAI[12] |

|      | P3.5 | GPIO          | PWM2∟                  | AD5  | PLAI[13] |

|      | P3.6 | GPIO          | PWM <sub>TRIP</sub>    | AD6  | PLAI[14] |

|      | P3.7 | GPIO          | PWM <sub>SYNC</sub>    | AD7  | PLAI[15] |

| 4    | P4.0 | GPIO          |                        | AD8  | PLAO[8]  |

|      | P4.1 | GPIO          |                        | AD9  | PLAO[9]  |

|      | P4.2 | GPIO          |                        | AD10 | PLAO[10] |

|      | P4.3 | GPIO          |                        | AD11 | PLAO[11] |

|      | P4.4 | GPIO          |                        | AD12 | PLAO[12] |

|      | P4.5 | GPIO          |                        | AD13 | PLAO[13] |

|      | P4.6 | GPIO          |                        | AD14 | PLAO[14] |

|      | P4.7 | GPIO          |                        | AD15 | PLAO[15] |

## Table 78. GPIO Pin Function Descriptions