Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                  |

| Core Size                  | 16/32-Bit                                                              |

| Speed                      | 44MHz                                                                  |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                             |

| Peripherals                | PLA, PWM, PSM, Temp Sensor, WDT                                        |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 62KB (31K x16)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 32                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                            |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 40-VFQFN Exposed Pad, CSP                                              |

| Supplier Device Package    | 40-LFCSP-VQ (6x6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7021bcpz62i-rl |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

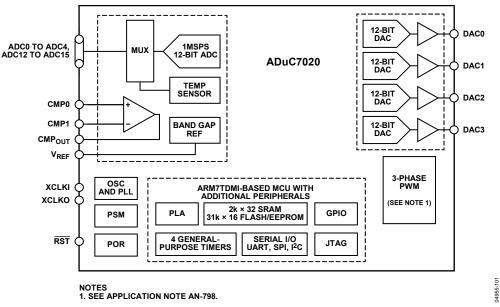

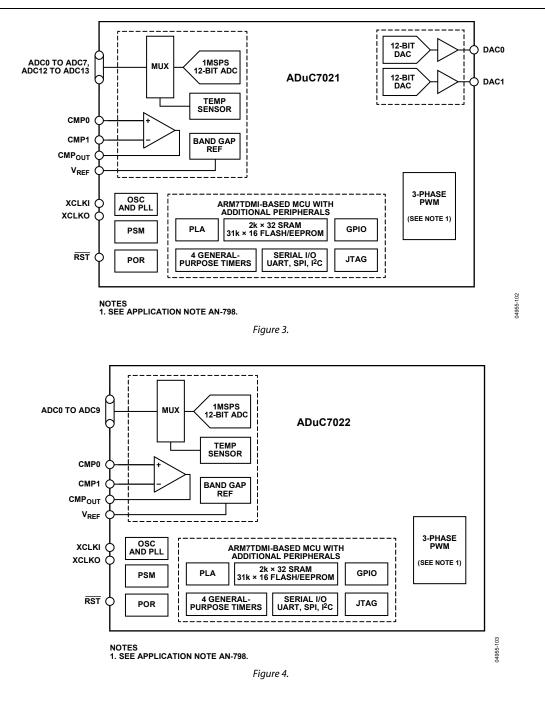

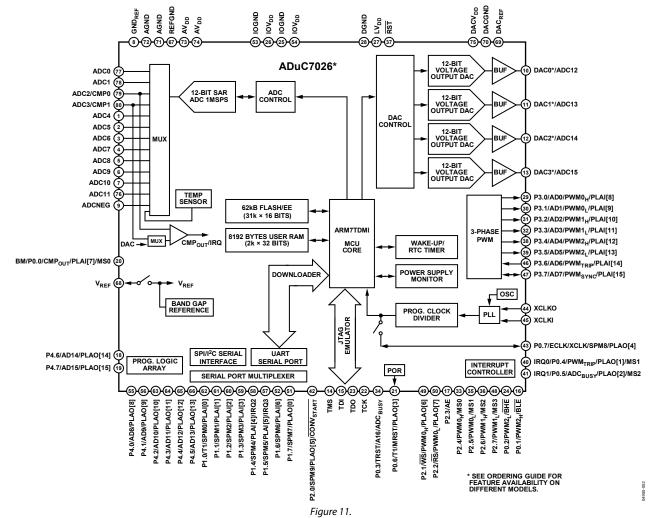

## **GENERAL DESCRIPTION**

The ADuC7019/20/21/22/24/25/26/27/28/29 are fully integrated, 1 MSPS, 12-bit data acquisition systems incorporating high performance multichannel ADCs, 16-bit/32-bit MCUs, and Flash\*/EE memory on a single chip.

The ADC consists of up to 12 single-ended inputs. An additional four inputs are available but are multiplexed with the four DAC output pins. The four DAC outputs are available only on certain models (ADuC7020, ADuC7026, ADuC7028, and ADuC7029). However, in many cases where the DAC outputs are not present, these pins can still be used as additional ADC inputs, giving a maximum of 16 ADC input channels. The ADC can operate in single-ended or differential input mode. The ADC input voltage is 0 V to  $V_{REF}$ . A low drift band gap reference, temperature sensor, and voltage comparator complete the ADC peripheral set.

Depending on the part model, up to four buffered voltage output DACs are available on-chip. The DAC output range is programmable to one of three voltage ranges. The devices operate from an on-chip oscillator and a PLL generating an internal high frequency clock of 41.78 MHz (UCLK). This clock is routed through a programmable clock divider from which the MCU core clock operating frequency is generated. The microcontroller core is an ARM7TDMI\*, 16-bit/32-bit RISC machine, which offers up to 41 MIPS peak performance. Eight kilobytes of SRAM and 62 kilobytes of nonvolatile Flash/EE memory are provided on-chip. The ARM7TDMI core views all memory and registers as a single linear array.

On-chip factory firmware supports in-circuit serial download via the UART or I<sup>2</sup>C serial interface port; nonintrusive emulation is also supported via the JTAG interface. These features are incorporated into a low cost QuickStart<sup>™</sup> development system supporting this MicroConverter<sup>\*</sup> family.

The parts operate from 2.7 V to 3.6 V and are specified over an industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. When operating at 41.78 MHz, the power dissipation is typically 120 mW. The ADuC7019/20/21/22/24/25/26/27/28/29 are available in a variety of memory models and packages (see Ordering Guide).

Figure 2.

### DETAILED BLOCK DIAGRAM

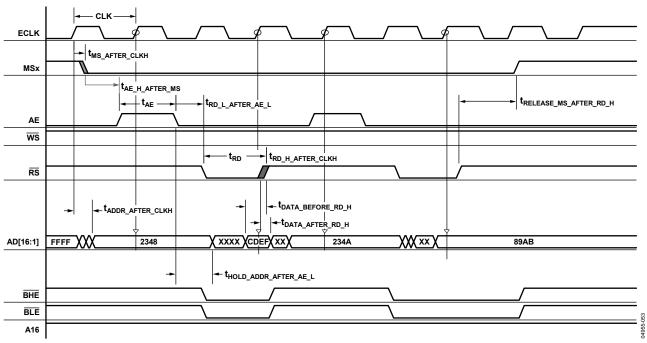

### Table 3. External Memory Read Cycle

| Parameter                          | Min        | Тур                                          | Max | Unit |

|------------------------------------|------------|----------------------------------------------|-----|------|

| CLK <sup>1</sup>                   | 1/MD clock | ns typ $\times$ (POWCON[2:0] + 1)            |     |      |

| tms_after_clkh                     | 4          |                                              | 8   | ns   |

| <b>t</b> ADDR_AFTER_CLKH           | 4          |                                              | 16  | ns   |

| t <sub>AE_H_AFTER_MS</sub>         |            | ½ CLK                                        |     |      |

| t <sub>AE</sub>                    |            | $(XMxPAR[14:12] + 1) \times CLK$             |     |      |

| thold_addr_after_ae_l              |            | 1/2 CLK + (! XMxPAR[10] ) × CLK              |     |      |

| trd_l_after_ae_l                   |            | 1/2 CLK + (! XMxPAR[10]+ ! XMxPAR[9] ) × CLK |     |      |

| trd_h_after_clkh                   | 0          |                                              | 4   |      |

| t <sub>RD</sub>                    |            | $(XMxPAR[3:0] + 1) \times CLK$               |     |      |

| tdata_before_rd_h                  | 16         |                                              |     | ns   |

| tdata_after_rd_h                   | 8          | + (! XMxPAR[9]) $\times$ CLK                 |     |      |

| t <sub>RELEASE_MS_AFTER_RD_H</sub> |            | $1 \times CLK$                               |     |      |

<sup>1</sup> See Table 78.

Figure 13. External Memory Read Cycle (See Table 78)

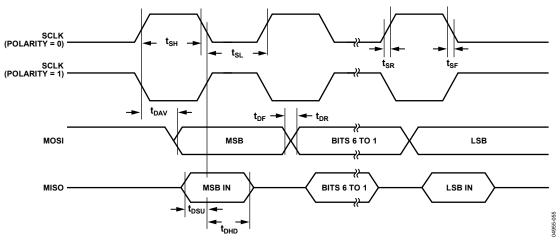

| Parameter               | Description                                         | Min                   | Тур                            | Мах  | Unit |

|-------------------------|-----------------------------------------------------|-----------------------|--------------------------------|------|------|

| t <sub>sL</sub>         | SCLK low pulse width <sup>1</sup>                   |                       | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>sH</sub>         | SCLK high pulse width <sup>1</sup>                  |                       | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>DAV</sub>        | Data output valid after SCLK edge                   |                       |                                | 25   | ns   |

| t <sub>DSU</sub>        | Data input setup time before SCLK edge <sup>2</sup> | 1 × t <sub>UCLK</sub> |                                |      | ns   |

| <b>t</b> <sub>DHD</sub> | Data input hold time after SCLK edge <sup>2</sup>   | $2 	imes t_{UCLK}$    |                                |      | ns   |

| t <sub>DF</sub>         | Data output fall time                               |                       | 5                              | 12.5 | ns   |

| t <sub>DR</sub>         | Data output rise time                               |                       | 5                              | 12.5 | ns   |

| t <sub>sr</sub>         | SCLK rise time                                      |                       | 5                              | 12.5 | ns   |

| t <sub>SF</sub>         | SCLK fall time                                      |                       | 5                              | 12.5 | ns   |

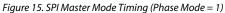

#### Table 6. SPI Master Mode Timing (Phase Mode = 1)

<sup>1</sup> t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCONMMR. t<sub>HCLK</sub> =  $t_{UCLK}/2^{CD}$ ; see Figure 67. <sup>2</sup> t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider; see Figure 67.

| Parameter         | Description                                         | Min                                         | Тур                            | Max  | Unit |

|-------------------|-----------------------------------------------------|---------------------------------------------|--------------------------------|------|------|

| t <sub>cs</sub>   | CS to SCLK edge <sup>1</sup>                        | $(2 \times t_{HCLK}) + (2 \times t_{UCLK})$ |                                |      | ns   |

| t <sub>sL</sub>   | SCLK low pulse width <sup>2</sup>                   |                                             | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>sн</sub>   | SCLK high pulse width <sup>2</sup>                  |                                             | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>DAV</sub>  | Data output valid after SCLK edge                   |                                             |                                | 25   | ns   |

| tdsu              | Data input setup time before SCLK edge <sup>1</sup> | $1 \times t_{UCLK}$                         |                                |      | ns   |

| t <sub>DHD</sub>  | Data input hold time after SCLK edge <sup>1</sup>   | $2 \times t_{UCLK}$                         |                                |      | ns   |

| t <sub>DF</sub>   | Data output fall time                               |                                             | 5                              | 12.5 | ns   |

| t <sub>DR</sub>   | Data output rise time                               |                                             | 5                              | 12.5 | ns   |

| t <sub>sr</sub>   | SCLK rise time                                      |                                             | 5                              | 12.5 | ns   |

| t <sub>sF</sub>   | SCLK fall time                                      |                                             | 5                              | 12.5 | ns   |

| t <sub>DOCS</sub> | Data output valid after CS edge                     |                                             |                                | 25   | ns   |

| t <sub>SFS</sub>  | CS high after SCLK edge                             | 0                                           |                                |      | ns   |

#### Table 9. SPI Slave Mode Timing (Phase Mode = 0)

<sup>1</sup> t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider; see Figure 67. <sup>2</sup> t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCONMMR. t<sub>HCLK</sub> = t<sub>UCLK</sub>/2<sup>CD</sup>; see Figure 67.

Figure 18. SPI Slave Mode Timing (Phase Mode = 0)

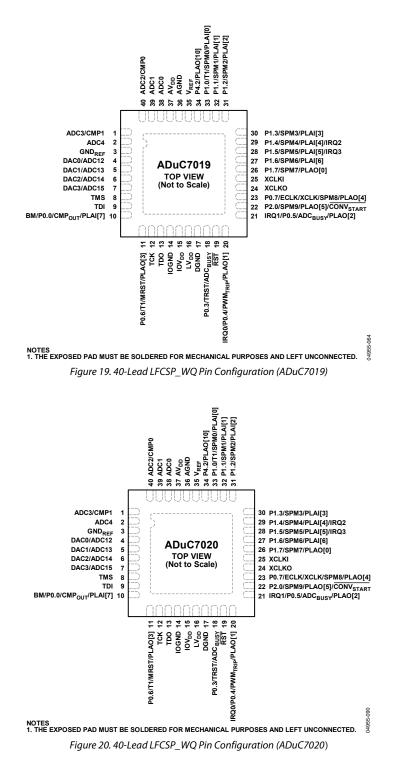

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

## ADuC7019/ADuC7020/ADuC7021/ADuC7022

| Pin No. | Mnemonic                           | Description                                                                                                                                                         |

|---------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37      | P3.6/PWM <sub>TRIP</sub> /PLAI[14] | General-Purpose Input and Output Port 3.6/PWM Safety Cutoff/Programmable Logic Array Input Element 14.                                                              |

| 38      | P3.7/PWM <sub>SYNC</sub> /PLAI[15] | General-Purpose Input and Output Port 3.7/PWM Synchronization Input and Output/<br>Programmable Logic Array Input Element 15.                                       |

| 39      | P1.7/SPM7/PLAO[0]                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.7/UART, SPI/Programmable Logic Array Output Element 0.                                             |

| 40      | P1.6/SPM6/PLAI[6]                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.6/UART, SPI/Programmable<br>Logic Array Input Element 6.                                           |

| 41      | IOGND                              | Ground for GPIO (see Table 78). Typically connected to DGND.                                                                                                        |

| 42      | IOV <sub>DD</sub>                  | 3.3 V Supply for GPIO (see Table 78) and Input of the On-Chip Voltage Regulator.                                                                                    |

| 43      | P4.0/PLAO[8]                       | General-Purpose Input and Output Port 4.0/Programmable Logic Array Output Element 8.                                                                                |

| 44      | P4.1/PLAO[9]                       | General-Purpose Input and Output Port 4.1/Programmable Logic Array Output Element 9.                                                                                |

| 45      | P1.5/SPM5/PLAI[5]/IRQ3             | Serial Port Multiplexed. General-Purpose Input and Output Port 1.5/UART, SPI/Programmable<br>Logic Array Input Element 5/External Interrupt Request 3, Active High. |

| 46      | P1.4/SPM4/PLAI[4]/IRQ2             | Serial Port Multiplexed. General-Purpose Input and Output Port 1.4/UART, SPI/Programmable<br>Logic Array Input Element 4/External Interrupt Request 2, Active High. |

| 47      | P1.3/SPM3/PLAI[3]                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.3/UART, I2C1/Programmable Logic Array Input Element 3.                                             |

| 48      | P1.2/SPM2/PLAI[2]                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.2/UART, I2C1/Programmable Logic Array Input Element 2.                                             |

| 49      | P1.1/SPM1/PLAI[1]                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.1/UART, I2C0/Programmable Logic Array Input Element 1.                                             |

| 50      | P1.0/T1/SPM0/PLAI[0]               | Serial Port Multiplexed. General-Purpose Input and Output Port 1.0/Timer1 Input/UART, I2C0/<br>Programmable Logic Array Input Element 0.                            |

| 51      | P4.2/PLAO[10]                      | General-Purpose Input and Output Port 4.2/Programmable Logic Array Output Element 10.                                                                               |

| 52      | P4.3/PLAO[11]                      | General-Purpose Input and Output Port 4.3/Programmable Logic Array Output Element 11.                                                                               |

| 53      | P4.4/PLAO[12]                      | General-Purpose Input and Output Port 4.4/Programmable Logic Array Output Element 12.                                                                               |

| 54      | P4.5/PLAO[13]                      | General-Purpose Input and Output Port 4.5/Programmable Logic Array Output Element 13.                                                                               |

| 55      | VREF                               | 2.5 V Internal Voltage Reference. Must be connected to a 0.47 $\mu$ F capacitor when using the internal reference.                                                  |

| 56      | DAC <sub>REF</sub>                 | External Voltage Reference for the DACs. Range: DACGND to DACV <sub>DD</sub> .                                                                                      |

| 57      | DACGND                             | Ground for the DAC. Typically connected to AGND.                                                                                                                    |

| 58      | AGND                               | Analog Ground. Ground reference point for the analog circuitry.                                                                                                     |

| 59      | AV <sub>DD</sub>                   | 3.3 V Analog Power.                                                                                                                                                 |

| 60      | DACVDD                             | 3.3 V Power Supply for the DACs. Must be connected to AV <sub>DD</sub> .                                                                                            |

| 61      | ADC0                               | Single-Ended or Differential Analog Input 0.                                                                                                                        |

| 62      | ADC1                               | Single-Ended or Differential Analog Input 1.                                                                                                                        |

| 63      | ADC2/CMP0                          | Single-Ended or Differential Analog Input 2/Comparator Positive Input.                                                                                              |

| 64      | ADC3/CMP1                          | Single-Ended or Differential Analog Input 3/Comparator Negative Input.                                                                                              |

| 0       | EP                                 | Exposed Pad. The pin configuration for the ADuC7024/ADuC7025 LFCSP_VQ has an exposed pad that must be soldered for mechanical purposes and left unconnected.        |

| Pin No. | Mnemonic                               | Description                                                                                                                                                         |

|---------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46      | P3.6/AD6/PWM <sub>TRIP</sub> /PLAI[14] | General-Purpose Input and Output Port 3.6/External Memory Interface/PWM Safety Cutoff/<br>Programmable Logic Array Input Element 14.                                |

| 47      | P3.7/AD7/PWM <sub>SYNC</sub> /PLAI[15] | General-Purpose Input and Output Port 3.7/External Memory Interface/PWM Synchronization/<br>Programmable Logic Array Input Element 15.                              |

| 48      | P2.7/PWM1L/MS3                         | General-Purpose Input and Output Port 2.7/PWM Phase 1 Low-Side Output/External Memory Select 3.                                                                     |

| 49      | P2.1/WS/PWM0 <sub>H</sub> /PLAO[6]     | General-Purpose Input and Output Port 2.1/External Memory Write Strobe/PWM Phase 0 High-<br>Side Output/Programmable Logic Array Output Element 6.                  |

| 50      | P2.2/RS/PWM0L/PLAO[7]                  | General-Purpose Input and Output Port 2.2/External Memory Read Strobe/PWM Phase 0 Low-<br>Side Output/Programmable Logic Array Output Element 7.                    |

| 51      | P1.7/SPM7/PLAO[0]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.7/UART, SPI/Programmable Logic Array Output Element 0.                                             |

| 52      | P1.6/SPM6/PLAI[6]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.6/UART, SPI/Programmable Logic<br>Array Input Element 6.                                           |

| 53      | IOGND                                  | Ground for GPIO (see Table 78). Typically connected to DGND.                                                                                                        |

| 54      | IOV <sub>DD</sub>                      | 3.3 V Supply for GPIO (see Table 78) and Input of the On-Chip Voltage Regulator.                                                                                    |

| 55      | P4.0/AD8/PLAO[8]                       | General-Purpose Input and Output Port 4.0/External Memory Interface/Programmable Logic<br>Array Output Element 8.                                                   |

| 56      | P4.1/AD9/PLAO[9]                       | General-Purpose Input and Output Port 4.1/External Memory Interface/Programmable Logic<br>Array Output Element 9.                                                   |

| 57      | P1.5/SPM5/PLAI[5]/IRQ3                 | Serial Port Multiplexed. General-Purpose Input and Output Port 1.5/UART, SPI/Programmable Logic Array Input Element 5/External Interrupt Request 3, Active High.    |

| 58      | P1.4/SPM4/PLAI[4]/IRQ2                 | Serial Port Multiplexed. General-Purpose Input and Output Port 1.4/UART, SPI/Programmable Logic<br>Array Input Element 4/External Interrupt Request 2, Active High. |

| 59      | P1.3/SPM3/PLAI[3]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.3/UART, I2C1/Programmable Logic Array Input Element 3.                                             |

| 60      | P1.2/SPM2/PLAI[2]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.2/UART, I2C1/Programmable Logic Array Input Element 2.                                             |

| 61      | P1.1/SPM1/PLAI[1]                      | Serial Port Multiplexed. General-Purpose Input and Output Port 1.1/UART, I2C0/Programmable<br>Logic Array Input Element 1.                                          |

| 62      | P1.0/T1/SPM0/PLAI[0]                   | Serial Port Multiplexed. General-Purpose Input and Output Port 1.0/Timer1 Input/UART, I2C0/<br>Programmable Logic Array Input Element 0.                            |

| 63      | P4.2/AD10/PLAO[10]                     | General-Purpose Input and Output Port 4.2/External Memory Interface/Programmable Logic Array Output Element 10.                                                     |

| 64      | P4.3/AD11/PLAO[11]                     | General-Purpose Input and Output Port 4.3/External Memory Interface/Programmable Logic Array Output Element 11.                                                     |

| 65      | P4.4/AD12/PLAO[12]                     | General-Purpose Input and Output Port 4.4/External Memory Interface/Programmable Logic Array Output Element 12.                                                     |

| 66      | P4.5/AD13/PLAO[13]                     | General-Purpose Input and Output Port 4.5/External Memory Interface/Programmable Logic Array Output Element 13.                                                     |

| 67      | REFGND                                 | Ground for the Reference. Typically connected to AGND.                                                                                                              |

| 68      | V <sub>REF</sub>                       | 2.5 V Internal Voltage Reference. Must be connected to a 0.47 $\mu\text{F}$ capacitor when using the internal reference.                                            |

| 69      | DAC <sub>REF</sub>                     | External Voltage Reference for the DACs. Range: DACGND to DACVDD.                                                                                                   |

| 70      | DACGND                                 | Ground for the DAC. Typically connected to AGND.                                                                                                                    |

| 71, 72  | AGND                                   | Analog Ground. Ground reference point for the analog circuitry.                                                                                                     |

| 73, 74  | AV <sub>DD</sub>                       | 3.3 V Analog Power.                                                                                                                                                 |

| 75      | DACV <sub>DD</sub>                     | 3.3 V Power Supply for the DACs. Must be connected to AV <sub>DD</sub> .                                                                                            |

| 76      | ADC11                                  | Single-Ended or Differential Analog Input 11.                                                                                                                       |

| 77      | ADC0                                   | Single-Ended or Differential Analog Input 0.                                                                                                                        |

| 78      | ADC1                                   | Single-Ended or Differential Analog Input 1.                                                                                                                        |

| 79      | ADC2/CMP0                              | Single-Ended or Differential Analog Input 2/Comparator Positive Input.                                                                                              |

| 80      | ADC3/CMP1                              | Single-Ended or Differential Analog Input 3/Comparator Negative Input.                                                                                              |

Input offset voltage ( $V_{OS}$ ) is the difference between the center of the hysteresis range and the ground level. This can either be positive or negative. The hysteresis voltage ( $V_H$ ) is one-half the width of the hysteresis range.

### **Comparator Interface**

The comparator interface consists of a 16-bit MMR, CMPCON, which is described in Table 56.

#### Table 55. CMPCON Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| CMPCON | 0xFFFF0444 | 0x0000        | R/W    |

| Bit   | Name    | Value | Description                                                                                                                                                                                                                                               |

|-------|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 |         |       | Reserved.                                                                                                                                                                                                                                                 |

| 10    | CMPEN   |       | Comparator enable bit. Set by user<br>to enable the comparator. Cleared<br>by user to disable the comparator.                                                                                                                                             |

| 9:8   | CMPIN   |       | Comparator negative input select bits.                                                                                                                                                                                                                    |

|       |         | 00    | AV <sub>DD</sub> /2.                                                                                                                                                                                                                                      |

|       |         | 01    | ADC3 input.                                                                                                                                                                                                                                               |

|       |         | 10    | DAC0 output.                                                                                                                                                                                                                                              |

|       |         | 11    | Reserved.                                                                                                                                                                                                                                                 |

| 7:6   | CMPOC   |       | Comparator output configuration bits.                                                                                                                                                                                                                     |

|       |         | 00    | Reserved.                                                                                                                                                                                                                                                 |

|       |         | 01    | Reserved.                                                                                                                                                                                                                                                 |

|       |         | 10    | Output on CMP <sub>out</sub> .                                                                                                                                                                                                                            |

|       |         | 11    | IRQ.                                                                                                                                                                                                                                                      |

| 5     | CMPOL   |       | Comparator output logic state bit.<br>When low, the comparator output<br>is high if the positive input (CMP0)<br>is above the negative input (CMP1).<br>When high, the comparator output<br>is high if the positive input is below<br>the negative input. |

| 4:3   | CMPRES  |       | Response time.                                                                                                                                                                                                                                            |

|       |         | 00    | 5 μs response time is typical for<br>large signals (2.5 V differential).<br>17 μs response time is typical for<br>small signals (0.65 mV differential).                                                                                                   |

|       |         | 11    | 3 μs typical.                                                                                                                                                                                                                                             |

|       |         | 01/10 | Reserved.                                                                                                                                                                                                                                                 |

| 2     | CMPHYST |       | Comparator hysteresis bit. Set by<br>user to have a hysteresis of about<br>7.5 mV. Cleared by user to have no<br>hysteresis.                                                                                                                              |

| 1     | CMPORI  |       | Comparator output rising edge<br>interrupt. Set automatically when a<br>rising edge occurs on the moni-<br>tored voltage (CMP0). Cleared by<br>user by writing a 1 to this bit.                                                                           |

| 0     | CMPOFI  |       | Comparator output falling edge<br>interrupt. Set automatically when a<br>falling edge occurs on the monitored<br>voltage (CMP0). Cleared by user.                                                                                                         |

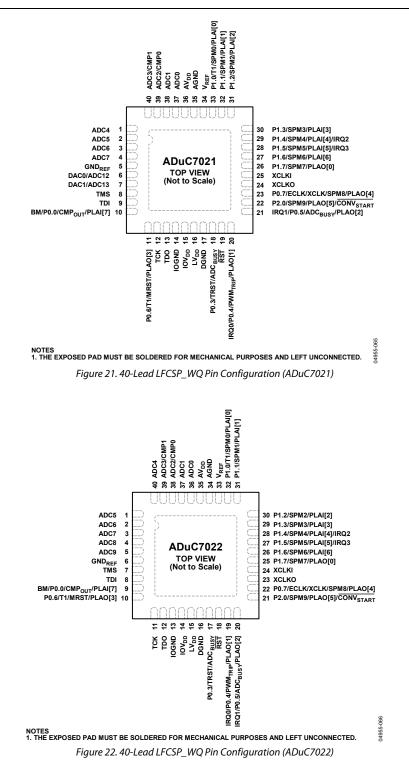

## OSCILLATOR AND PLL—POWER CONTROL

#### **Clocking System**

### Each ADuC7019/20/21/22/24/25/26/27/28/29 integrates a

32.768 kHz  $\pm$ 3% oscillator, a clock divider, and a PLL. The PLL locks onto a multiple (1275) of the internal oscillator or an external 32.768 kHz crystal to provide a stable 41.78 MHz clock (UCLK) for the system. To allow power saving, the core can operate at this frequency, or at binary submultiples of it. The actual core operating frequency, UCLK/2<sup>CD</sup>, is refered to as HCLK. The default core clock is the PLL clock divided by 8 (CD = 3) or 5.22 MHz. The core clock frequency can also come from an external clock on the ECLK pin as described in Figure 67. The core clock can be outputted on ECLK when using an internal oscillator or external crystal.

Note that when the ECLK pin is used to output the core clock, the output signal is not buffered and is not suitable for use as a clock source to an external device without an external buffer.

The selection of the clock source is in the PLLCON register. By default, the part uses the internal oscillator feeding the PLL.

### **External Crystal Selection**

To switch to an external crystal, the user must do the following:

- 1. Enable the Timer2 interrupt and configure it for a timeout period of >120  $\mu s.$

- 2. Follow the write sequence to the PLLCON register, setting the MDCLK bits to 01 and clearing the OSEL bit.

- 3. Force the part into NAP mode by following the correct write sequence to the POWCON register.

When the part is interrupted from NAP mode by the Timer2 interrupt source, the clock source has switched to the external clock.

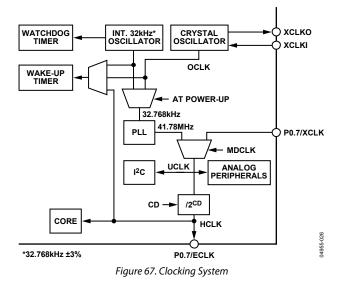

## **DESCRIPTION OF THE PWM BLOCK**

A functional block diagram of the PWM controller is shown in Figure 68. The generation of the six output PWM signals on Pin PWM0<sub>H</sub> to Pin PWM2<sub>L</sub> is controlled by the following four important blocks:

- The 3-phase PWM timing unit. The core of the PWM controller, this block generates three pairs of complemented and dead-time-adjusted, center-based PWM signals. This unit also generates the internal synchronization pulse, PWMSYNC. It also controls whether the external PWM<sub>SYNC</sub> pin is used.

- The output control unit. This block can redirect the outputs of the 3-phase timing unit for each channel to either the high-side or low-side output. In addition, the output control unit allows individual enabling/disabling of each of the six PWM output signals.

- The gate drive unit. This block can generate the high frequency chopping and its subsequent mixing with the PWM signals.

- The PWM shutdown controller. This block controls the PWM shutdown via the PWM<sub>TRIP</sub> pin and generates the correct reset signal for the timing unit.

The PWM controller is driven by the ADuC7019/20/21/22/24/ 25/26/27/28/29 core clock frequency and is capable of generating two interrupts to the ARM core. One interrupt is generated on the occurrence of a PWMSYNC pulse, and the other is generated on the occurrence of any PWM shutdown action.

## 3-Phase Timing Unit

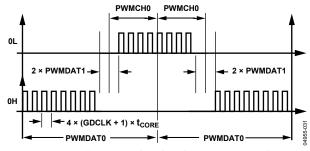

## PWM Switching Frequency (PWMDAT0 MMR)

The PWM switching frequency is controlled by the PWM period register, PWMDAT0. The fundamental timing unit of the PWM controller is

$t_{CORE} = 1/f_{CORE}$

where  $f_{CORE}$  is the core frequency of the MicroConverter.

Therefore, for a 41.78 MHz  $f_{\rm CORE}$ , the fundamental time increment is 24 ns. The value written to the PWMDAT0 register is effectively the number of  $f_{\rm CORE}$  clock increments in one-half a PWM period. The required PWMDAT0 value is a function of the desired PWM switching frequency ( $f_{\rm PWN}$ ) and is given by

$PWMDAT0 = f_{CORE}/(2 \times f_{PWM})$

Therefore, the PWM switching period, ts, can be written as

$t_S = 2 \times PWMDAT0 \times t_{CORE}$

The largest value that can be written to the 16-bit PWMDAT0 MMR is 0xFFFF = 65,535, which corresponds to a minimum PWM switching frequency of

$f_{PWM(min)} = 41.78 \times 10^{6}/(2 \times 65,535) = 318.75 \text{ Hz}$

Note that PWMDAT0 values of 0 and 1 are not defined and should not be used.

## PWM Switching Dead Time (PWMDAT1 MMR)

The second important parameter that must be set up in the initial configuration of the PWM block is the switching dead time. This is a short delay time introduced between turning off one PWM signal (0H, for example) and turning on the complementary signal (0L). This short time delay is introduced to permit the power switch to be turned off (in this case, 0H) to completely recover its blocking capability before the complementary switch is turned on. This time delay prevents a potentially destructive short-circuit condition from developing across the dc link capacitor of a typical voltage source inverter.

The dead time is controlled by the 10-bit, read/write PWMDAT1 register. There is only one dead-time register that controls the dead time inserted into all three pairs of PWM output signals. The dead time,  $t_D$ , is related to the value in the PWMDAT1 register by

#### $t_D = PWMDAT1 \times 2 \times t_{CORE}$

Therefore, a PWMDAT1 value of 0x00A (= 10), introduces a 426 ns delay between the turn-off on any PWM signal (0H, for example) and the turn-on of its complementary signal (0L). The amount of the dead time can, therefore, be programmed in increments of  $2t_{CORE}$  (or 49 ns for a 41.78 MHz core clock).

Figure 68. Overview of the PWM Controller

The GDCLK value can range from 0 to 255, corresponding to a programmable chopping frequency rate of 40.8 kHz to 10.44 MHz for a 41.78 MHz core frequency. The gate drive features must be programmed before operation of the PWM controller and are typically not changed during normal operation of the PWM controller. Following a reset, all bits of the PWMCFG register are cleared so that high frequency chopping is disabled, by default.

Figure 72. Typical PWM Signals with High Frequency Gate Chopping Enabled on Both High-Side and Low-Side Switches

## **PWM Shutdown**

In the event of external fault conditions, it is essential that the PWM system be instantaneously shut down in a safe fashion. A low level on the PWM<sub>TRIP</sub> pin provides an instantaneous, asynchronous (independent of the MicroConverter core clock) shutdown of the PWM controller. All six PWM outputs are placed in the off state, that is, in low state. In addition, the PWMSYNC pulse is disabled. The PWM<sub>TRIP</sub> pin has an internal pull-down resistor to disable the PWM if the pin becomes disconnected. The state of the PWM<sub>TRIP</sub> pin can be read from Bit 3 of the PWMSTA register.

If a PWM shutdown command occurs, a PWMTRIP interrupt is generated, and internal timing of the 3-phase timing unit of the PWM controller is stopped. Following a PWM shutdown, the PWM can be reenabled (in a PWMTRIP interrupt service routine, for example) only by writing to all of the PWMDAT0, PWMCH0, PWMCH1, and PWMCH2 registers. Provided that the external fault is cleared and the PWMTRIP is returned to a high level, the internal timing of the 3-phase timing unit resumes, and new duty-cycle values are latched on the next PWMSYNC boundary.

Note that the PWMTRIP interrupt is available in IRQ only, and the PWMSYNC interrupt is available in FIQ only. Both interrupts share the same bit in the interrupt controller. Therefore, only one of the interrupts can be used at a time. See the Interrupt System section for further details.

## **PWM MMRs Interface**

The PWM block is controlled via the MMRs described in this section.

#### Table 66. PWMCON Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| PWMCON | 0xFFFFFC00 | 0x0000        | R/W    |

PWMCON is a control register that enables the PWM and chooses the update rate.

| Table 67. PWMCON MMR Bit Description |

|--------------------------------------|

|--------------------------------------|

|     | Tuble 07:1 WhiteOIN Minik Bit Descriptions |                                                                                                                                                                |  |

|-----|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit | Name                                       | Description                                                                                                                                                    |  |

| 7:5 |                                            | Reserved.                                                                                                                                                      |  |

| 4   | PWM_SYNCSEL                                | External sync select. Set to use external sync. Cleared to use internal sync.                                                                                  |  |

| 3   | PWM_EXTSYNC                                | External sync select. Set to select<br>external synchronous sync signal.<br>Cleared for asynchronous sync signal.                                              |  |

| 2   | PWMDBL                                     | Double update mode. Set to 1 by user<br>to enable double update mode.<br>Cleared to 0 by the user to enable<br>single update mode.                             |  |

| 1   | PWM_SYNC_EN                                | PWM synchronization enable. Set by<br>user to enable synchronization. Cleared<br>by user to disable synchronization.                                           |  |

| 0   | PWMEN                                      | PWM enable bit. Set to 1 by user to<br>enable the PWM. Cleared to 0 by user<br>to disable the PWM. Also cleared<br>automatically with PWMTRIP<br>(PWMSTA MMR). |  |

#### Table 68. PWMSTA Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| PWMSTA | 0xFFFFFC04 | 0x0000        | R/W    |

PWMSTA reflects the status of the PWM.

## Table 69. PWMSTA MMR Bit Descriptions

| Bit   | Name       | Description                                                                                                                                                                               |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:10 |            | Reserved.                                                                                                                                                                                 |

| 9     | PWMSYNCINT | PWM sync interrupt bit. Writing a 1 to this bit clears this interrupt.                                                                                                                    |

| 8     | PWMTRIPINT | PWM trip interrupt bit. Writing a 1 to this bit clears this interrupt.                                                                                                                    |

| 3     | PWMTRIP    | Raw signal from the PWM <sub>TRIP</sub> pin.                                                                                                                                              |

| 2:1   |            | Reserved.                                                                                                                                                                                 |

| 0     | PWMPHASE   | PWM phase bit. Set to 1 by the Micro-<br>Converter when the timer is counting<br>down (first half). Cleared to 0 by the<br>MicroConverter when the timer is<br>counting up (second half). |

|      |      | Configuration |                        |      |          |  |

|------|------|---------------|------------------------|------|----------|--|

| Port | Pin  | 00            | 01                     | 10   | 11       |  |

| 0    | P0.0 | GPIO          | CMP                    | MS0  | PLAI[7]  |  |

|      | P0.1 | GPIO          | PWM2 <sub>H</sub>      | BLE  |          |  |

|      | P0.2 | GPIO          | PWM2∟                  | BHE  |          |  |

|      | P0.3 | GPIO          | TRST                   | A16  | ADCBUSY  |  |

|      | P0.4 | GPIO/IRQ0     | PWMTRIP                | MS1  | PLAO[1]  |  |

|      | P0.5 | GPIO/IRQ1     | ADCBUSY                | MS2  | PLAO[2]  |  |

|      | P0.6 | GPIO/T1       | MRST                   |      | PLAO[3]  |  |

|      | P0.7 | GPIO          | ECLK/XCLK <sup>1</sup> | SIN  | PLAO[4]  |  |

| 1    | P1.0 | GPIO/T1       | SIN                    | SCL0 | PLAI[0]  |  |

|      | P1.1 | GPIO          | SOUT                   | SDA0 | PLAI[1]  |  |

|      | P1.2 | GPIO          | RTS                    | SCL1 | PLAI[2]  |  |

|      | P1.3 | GPIO          | CTS                    | SDA1 | PLAI[3]  |  |

|      | P1.4 | GPIO/IRQ2     | RI                     | SCLK | PLAI[4]  |  |

|      | P1.5 | GPIO/IRQ3     | DCD                    | MISO | PLAI[5]  |  |

|      | P1.6 | GPIO          | DSR                    | MOSI | PLAI[6]  |  |

|      | P1.7 | GPIO          | DTR                    | CS   | PLAO[0]  |  |

| 2    | P2.0 | GPIO          |                        | SOUT | PLAO[5]  |  |

|      | P2.1 | GPIO          | PWM0 <sub>H</sub>      | WS   | PLAO[6]  |  |

|      | P2.2 | GPIO          | PWM0⊾                  | RS   | PLAO[7]  |  |

|      | P2.3 | GPIO          |                        | AE   |          |  |

|      | P2.4 | GPIO          | PWM0 <sub>H</sub>      | MS0  |          |  |

|      | P2.5 | GPIO          | PWM0∟                  | MS1  |          |  |

|      | P2.6 | GPIO          | PWM1 <sub>H</sub>      | MS2  |          |  |

|      | P2.7 | GPIO          | PWM1∟                  | MS3  |          |  |

| 3    | P3.0 | GPIO          | PWM0 <sub>H</sub>      | AD0  | PLAI[8]  |  |

|      | P3.1 | GPIO          | PWM0∟                  | AD1  | PLAI[9]  |  |

|      | P3.2 | GPIO          | PWM1 <sub>H</sub>      | AD2  | PLAI[10] |  |

|      | P3.3 | GPIO          | PWM1∟                  | AD3  | PLAI[11] |  |

|      | P3.4 | GPIO          | PWM2 <sub>H</sub>      | AD4  | PLAI[12] |  |

|      | P3.5 | GPIO          | PWM2∟                  | AD5  | PLAI[13] |  |

|      | P3.6 | GPIO          | PWM <sub>TRIP</sub>    | AD6  | PLAI[14] |  |

|      | P3.7 | GPIO          | PWM <sub>SYNC</sub>    | AD7  | PLAI[15] |  |

| 4    | P4.0 | GPIO          |                        | AD8  | PLAO[8]  |  |

|      | P4.1 | GPIO          |                        | AD9  | PLAO[9]  |  |

|      | P4.2 | GPIO          |                        | AD10 | PLAO[10] |  |

|      | P4.3 | GPIO          |                        | AD11 | PLAO[11] |  |

|      | P4.4 | GPIO          |                        | AD12 | PLAO[12] |  |

|      | P4.5 | GPIO          |                        | AD13 | PLAO[13] |  |

|      | P4.6 | GPIO          |                        | AD14 | PLAO[14] |  |

|      | P4.7 | GPIO          |                        | AD15 | PLAO[15] |  |

## Table 78. GPIO Pin Function Descriptions

<sup>1</sup>When configured in Mode 1, P0.7 is ECLK by default, or core clock output. To configure it as a clock input, the MDCLK bits in PLLCON must be set to 11. <sup>2</sup> The CONV<sub>START</sub> signal is active in all modes of P2.0.

#### Table 79. GPxCON Registers

| Name   | Address    | Default Value | Access |  |  |

|--------|------------|---------------|--------|--|--|

| GP0CON | 0xFFFFF400 | 0x0000000     | R/W    |  |  |

| GP1CON | 0xFFFFF404 | 0x0000000     | R/W    |  |  |

| GP2CON | 0xFFFFF408 | 0x0000000     | R/W    |  |  |

| GP3CON | 0xFFFFF40C | 0x0000000     | R/W    |  |  |

| GP4CON | 0xFFFFF410 | 0x0000000     | R/W    |  |  |

GPxCON are the Port x control registers, which select the function of each pin of Port x as described in Table 80.

#### Table 80. GPxCON MMR Bit Descriptions

| -     |                                  |

|-------|----------------------------------|

| Bit   | Description                      |

| 31:30 | Reserved.                        |

| 29:28 | Select function of the Px.7 pin. |

| 27:26 | Reserved.                        |

| 25:24 | Select function of the Px.6 pin. |

| 23:22 | Reserved.                        |

| 21:20 | Select function of the Px.5 pin. |

| 19:18 | Reserved.                        |

| 17:16 | Select function of the Px.4 pin. |

| 15:14 | Reserved.                        |

| 13:12 | Select function of the Px.3 pin. |

| 11:10 | Reserved.                        |

| 9:8   | Select function of the Px.2 pin. |

| 7:6   | Reserved.                        |

| 5:4   | Select function of the Px.1 pin. |

| 3:2   | Reserved.                        |

| 1:0   | Select function of the Px.0 pin. |

|       |                                  |

#### Table 81. GPxPAR Registers

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| GPOPAR | 0xFFFFF42C | 0x20000000    | R/W    |

| GP1PAR | 0xFFFFF43C | 0x0000000     | R/W    |

GPxPAR program the parameters for Port 0 and Port 1. Note that the GPxDAT MMR must always be written after changing the GPxPAR MMR.

#### Table 82. GPxPAR MMR Bit Descriptions

| Bit   | Description           |

|-------|-----------------------|

| 31    | Reserved.             |

| 30:29 | Drive strength Px.7.  |

| 28    | Pull-Up Disable Px.7. |

| 27    | Reserved.             |

| 26:25 | Drive strength Px.6.  |

| 24    | Pull-Up Disable Px.6. |

| 23    | Reserved.             |

| 22:21 | Drive strength Px.5.  |

| 20    | Pull-Up Disable Px.5. |

| 19    | Reserved.             |

| 18:17 | Drive strength Px.4.  |

| 16    | Pull-Up Disable Px.4. |

| 15    | Reserved.             |

| 14:13 | Drive strength Px.3.  |

| 12    | Pull-Up Disable Px.3. |

| 11    | Reserved.             |

| 10:9  | Drive strength Px.2.  |

| 8     | Pull-Up Disable Px.2. |

| 7     | Reserved.             |

| 6:5   | Drive strength Px.1.  |

| 4     | Pull-Up Disable Px.1. |

| 3     | Reserved.             |

| 2:1   | Drive strength Px.0.  |

| 0     | Pull-Up Disable Px.0. |

#### Table 116. COMIID1 MMR Bit Descriptions

| Bit 3:1<br>Status<br>Bits | Bit 0<br>NINT | Priority | Definition                              | Clearing<br>Operation                     |

|---------------------------|---------------|----------|-----------------------------------------|-------------------------------------------|

| 000                       | 1             |          | No interrupt                            |                                           |

| 110                       | 0             | 2        | Matching network<br>address             | Read COMRX                                |

| 101                       | 0             | 3        | Address<br>transmitted,<br>buffer empty | Write data to<br>COMTX or<br>read COMIID0 |

| 011                       | 0             | 1        | Receive line status<br>interrupt        | Read<br>COMSTA0                           |

| 010                       | 0             | 2        | Receive buffer full<br>interrupt        | Read COMRX                                |

| 001                       | 0             | 3        | Transmit buffer<br>empty interrupt      | Write data to<br>COMTX or<br>read COMIID0 |

| 000                       | 0             | 4        | Modem status<br>interrupt               | Read<br>COMSTA1                           |

Note that to receive a network address interrupt, the slave must ensure that Bit 0 of COMIEN0 (enable receive buffer full interrupt) is set to 1.

#### Table 117. COMADR Register

| Name   | Address    | Default Value | Access |  |

|--------|------------|---------------|--------|--|

| COMADR | 0xFFFF0728 | 0xAA          | R/W    |  |

COMADR is an 8-bit, read/write network address register that holds the address checked for by the network addressable UART. Upon receiving this address, the device interrupts the processor and/or sets the appropriate status bit in COMIID1.

### SERIAL PERIPHERAL INTERFACE

The ADuC7019/20/21/22/24/25/26/27/28/29 integrate a complete hardware serial peripheral interface (SPI) on-chip. SPI is an industry standard, synchronous serial interface that allows eight bits of data to be synchronously transmitted and simultaneously received, that is, full duplex up to a maximum bit rate of 3.48 Mb, as shown in Table 118. The SPI interface is not operational with core clock divider (CD) bits. POWCON[2:0] = 6 or 7 in master mode.

The SPI port can be configured for master or slave operation. and typically consists of four pins: MISO (P1.5), MOSI (P1.6), SCLK (P1.4), and  $\overline{CS}$  (P1.7).

On the transmit side, the SPITX register (and a TX shift register outside it) loads data onto the transmit pin (in slave mode, MISO; in master mode, MOSI). The transmit status bit, Bit 0, in SPISTA indicates whether there is valid data in the SPITX register.

Similarly, the receive data path consists of the SPIRX register (and an RX shift register). SPISTA, Bit 3 indicates whether there is valid data in the SPIRX register. If valid data in the SPIRX register is overwritten or if valid data in the RX shift register is discarded, SPISTA, Bit 5 (the overflow bit) is set.

#### MISO (Master In, Slave Out) Pin

The MISO pin is configured as an input line in master mode and an output line in slave mode. The MISO line on the master (data in) should be connected to the MISO line in the slave device (data out). The data is transferred as byte wide (8-bit) serial data, MSB first.

### MOSI (Master Out, Slave In) Pin

The MOSI pin is configured as an output line in master mode and an input line in slave mode. The MOSI line on the master (data out) should be connected to the MOSI line in the slave device (data in). The data is transferred as byte wide (8-bit) serial data, MSB first.

#### SCLK (Serial Clock I/O) Pin

The master serial clock (SCLK) is used to synchronize the data being transmitted and received through the MOSI SCLK period. Therefore, a byte is transmitted/received after eight SCLK periods. The SCLK pin is configured as an output in master mode and as an input in slave mode.

In master mode, the polarity and phase of the clock are controlled by the SPICON register, and the bit rate is defined in the SPIDIV register as follows:

$$f_{SERIAL CLOCK} = \frac{f_{UCLK}}{2 \times (1 + SPIDIV)}$$

The maximum speed of the SPI clock is dependent on the clock divider bits and is summarized in Table 118.

| CD Bits             | 0     | 1     | 2     | 3     | 4     | 5     |

|---------------------|-------|-------|-------|-------|-------|-------|

| SPIDIV in Hex       | 0x05  | 0x0B  | 0x17  | 0x2F  | 0x5F  | 0xBF  |

| SPI dpeed<br>in MHz | 3.482 | 1.741 | 0.870 | 0.435 | 0.218 | 0.109 |

In slave mode, the SPICON register must be configured with the phase and polarity of the expected input clock. The slave accepts data from an external master up to 10.4 Mb at CD = 0. The formula to determine the maximum speed is as follows:

$$f_{SERIAL CLOCK} = \frac{f_{HCLK}}{4}$$

In both master and slave modes, data is transmitted on one edge of the SCL signal and sampled on the other. Therefore, it is important that the polarity and phase be configured the same for the master and slave devices.

## Chip Select (CS Input) Pin

In SPI slave mode, a transfer is initiated by the assertion of CS, which is an active low input signal. The SPI port then transmits and receives 8-bit data until the transfer is concluded by deassertion of  $\overline{\text{CS}}$ . In slave mode,  $\overline{\text{CS}}$  is always an input.

### Table 140. I2CxDIV Registers

| Name Address |            | Default Value | Access |

|--------------|------------|---------------|--------|

| I2C0DIV      | 0xFFFF0830 | 0x1F1F        | R/W    |

| I2C1DIV      | 0xFFFF0930 | 0x1F1F        | R/W    |

I2CxDIV are the clock divider registers.

#### Table 141. I2CxIDx Registers

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| I2C0ID0 | 0xFFFF0838 | 0x00          | R/W    |

| I2C0ID1 | 0xFFFF083C | 0x00          | R/W    |

| I2C0ID2 | 0xFFFF0840 | 0x00          | R/W    |

| I2C0ID3 | 0xFFFF0844 | 0x00          | R/W    |

| I2C1ID0 | 0xFFFF0938 | 0x00          | R/W    |

| I2C1ID1 | 0xFFFF093C | 0x00          | R/W    |

| I2C1ID2 | 0xFFFF0940 | 0x00          | R/W    |

| I2C1ID3 | 0xFFFF0944 | 0x00          | R/W    |

|         |            |               |        |

I2CxID0, I2CxID1, I2CxID2, and I2CxID3 are slave address device ID registers of I2Cx.

#### Table 142. I2CxCCNT Registers

| Name     | Address    | Default Value | Access |

|----------|------------|---------------|--------|

| I2C0CCNT | 0xFFFF0848 | 0x01          | R/W    |

| I2C1CCNT | 0xFFFF0948 | 0x01          | R/W    |

I2CxCCNT are 8-bit start/stop generation counters. They hold off SDA low for start and stop conditions.

#### Table 143. I2CxFSTA Registers

| Name     | Address    | Default Value | Access |

|----------|------------|---------------|--------|

| I2C0FSTA | 0xFFFF084C | 0x0000        | R/W    |

| I2C1FSTA | 0xFFFF094C | 0x0000        | R/W    |

I2CxFSTA are FIFO status registers.

| Bit   | Access<br>Type | Value | Description                                                                                                                                                                                  |

|-------|----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:10 |                |       | Reserved.                                                                                                                                                                                    |

| 9     | R/W            |       | Master transmit FIFO flush. Set by the<br>user to flush the master Tx FIFO.<br>Cleared automatically when the<br>master Tx FIFO is flushed. This bit<br>also flushes the slave receive FIFO. |

| 8     | R/W            |       | Slave transmit FIFO flush. Set by the<br>user to flush the slave Tx FIFO. Cleared<br>automatically after the slave Tx FIFO<br>is flushed.                                                    |

| 7:6   | R              |       | Master Rx FIFO status bits.                                                                                                                                                                  |

|       |                | 00    | FIFO empty.                                                                                                                                                                                  |

|       |                | 01    | Byte written to FIFO.                                                                                                                                                                        |

|       |                | 10    | One byte in FIFO.                                                                                                                                                                            |

|       |                | 11    | FIFO full.                                                                                                                                                                                   |

| 5:4   | R              |       | Master Tx FIFO status bits.                                                                                                                                                                  |

|       |                | 00    | FIFO empty.                                                                                                                                                                                  |

|       |                | 01    | Byte written to FIFO.                                                                                                                                                                        |

|       |                | 10    | One byte in FIFO.                                                                                                                                                                            |

|       |                | 11    | FIFO full.                                                                                                                                                                                   |

| 3:2   | R              |       | Slave Rx FIFO status bits.                                                                                                                                                                   |

|       |                | 00    | FIFO empty.                                                                                                                                                                                  |

|       |                | 01    | Byte written to FIFO.                                                                                                                                                                        |

|       |                | 10    | One byte in FIFO.                                                                                                                                                                            |

|       |                | 11    | FIFO full.                                                                                                                                                                                   |

| 1:0   | R              |       | Slave Tx FIFO status bits.                                                                                                                                                                   |

|       |                | 00    | FIFO empty.                                                                                                                                                                                  |

|       |                | 01    | Byte written to FIFO.                                                                                                                                                                        |

|       |                | 10    | One byte in FIFO.                                                                                                                                                                            |

|       |                | 11    | FIFO full.                                                                                                                                                                                   |

## Table 144. I2C0FSTA MMR Bit Descriptions

## PROCESSOR REFERENCE PERIPHERALS INTERRUPT SYSTEM

There are 23 interrupt sources on the ADuC7019/20/21/22/ 24/25/26/27/28/29 that are controlled by the interrupt controller. Most interrupts are generated from the on-chip peripherals, such as ADC and UART. Four additional interrupt sources are generated from external interrupt request pins, IRQ0, IRQ1, IRQ2, and IRQ3. The ARM7TDMI CPU core only recognizes interrupts as one of two types: a normal interrupt request IRQ or a fast interrupt request FIQ. All the interrupts can be masked separately.

The control and configuration of the interrupt system are managed through nine interrupt-related registers, four dedicated to IRQ, and four dedicated to FIQ. An additional MMR is used to select the programmed interrupt source. The bits in each IRQ and FIQ register (except for Bit 23) represent the same interrupt source as described in Table 160.

#### Table 160. IRQ/FIQ MMRs Bit Description

|     | 100. Ing/IIg minits bit Description                                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Description                                                                                                                         |

| 0   | All interrupts OR'ed (FIQ only)                                                                                                     |

| 1   | SWI                                                                                                                                 |

| 2   | Timer0                                                                                                                              |

| 3   | Timer1                                                                                                                              |

| 4   | Wake-up timer (Timer2)                                                                                                              |

| 5   | Watchdog timer (Timer3)                                                                                                             |

| 6   | Flash control                                                                                                                       |

| 7   | ADC channel                                                                                                                         |

| 8   | PLL lock                                                                                                                            |

| 9   | I2C0 slave                                                                                                                          |

| 10  | I2C0 master                                                                                                                         |

| 11  | I2C1 master                                                                                                                         |

| 12  | SPI slave                                                                                                                           |

| 13  | SPI master                                                                                                                          |

| 14  | UART                                                                                                                                |

| 15  | External IRQ0                                                                                                                       |

| 16  | Comparator                                                                                                                          |

| 17  | PSM                                                                                                                                 |

| 18  | External IRQ1                                                                                                                       |

| 19  | PLA IRQ0                                                                                                                            |

| 20  | PLA IRQ1                                                                                                                            |

| 21  | External IRQ2                                                                                                                       |

| 22  | External IRQ3                                                                                                                       |

| 23  | PWM trip (IRQ only)/PWM sync (FIQ only)                                                                                             |

|     | Bit<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22 |

## IRQ

The interrupt request (IRQ) is the exception signal to enter the IRQ mode of the processor. It is used to service general-purpose interrupt handling of internal and external events.

The four 32-bit registers dedicated to IRQ are IRQSTA, IRQSIG, IRQEN, and IRQCLR.

#### Table 161. IRQSTA Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| IRQSTA | 0xFFFF0000 | 0x0000000     | R      |

IRQSTA (read-only register) provides the current-enabled IRQ source status. When set to 1, that source should generate an active IRQ request to the ARM7TDMI core. There is no priority encoder or interrupt vector generation. This function is implemented in software in a common interrupt handler routine. All 32 bits are logically ORed to create the IRQ signal to the ARM7TDMI core.

#### Table 162. IRQSIG Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| IRQSIG | 0xFFFF0004 | 0x00XXX0001   | R      |

<sup>1</sup>X indicates an undefined value.

IRQSIG reflects the status of the different IRQ sources. If a peripheral generates an IRQ signal, the corresponding bit in the IRQSIG is set; otherwise, it is cleared. The IRQSIG bits are cleared when the interrupt in the particular peripheral is cleared. All IRQ sources can be masked in the IRQEN MMR. IRQSIG is read only.

#### Table 163. IRQEN Register

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| IRQEN | 0xFFFF0008 | 0x0000000     | R/W    |

IRQEN provides the value of the current enable mask. When each bit is set to 1, the source request is enabled to create an IRQ exception. When each bit is set to 0, the source request is disabled or masked, which does not create an IRQ exception.

Note that to clear an already enabled interrupt source, the user must set the appropriate bit in the IRQCLR register. Clearing an interrupt's IRQEN bit does not disable the interrupt.

#### Table 164. IRQCLR Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| IRQCLR | 0xFFFF000C | 0x0000000     | W      |

IRQCLR (write-only register) clears the IRQEN register in order to mask an interrupt source. Each bit set to 1 clears the corresponding bit in the IRQEN register without affecting the remaining bits. The pair of registers, IRQEN and IRQCLR, independently manipulates the enable mask without requiring an atomic read-modify-write.

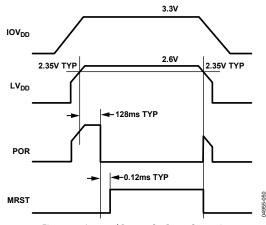

## **POWER-ON RESET OPERATION**

An internal power-on reset (POR) is implemented on the ADuC7019/20/21/22/24/25/26/27/28/29. For LV<sub>DD</sub> below 2.35 V typical, the internal POR holds the part in reset. As LV<sub>DD</sub> rises above 2.35 V, an internal timer times out for, typically, 128 ms before the part is released from reset. The user must ensure that the power supply IOV<sub>DD</sub> reaches a stable 2.7 V minimum level by this time. Likewise, on power-down, the internal POR holds the part in reset until LV<sub>DD</sub> drops below 2.35 V.

Figure 94 illustrates the operation of the internal POR in detail.

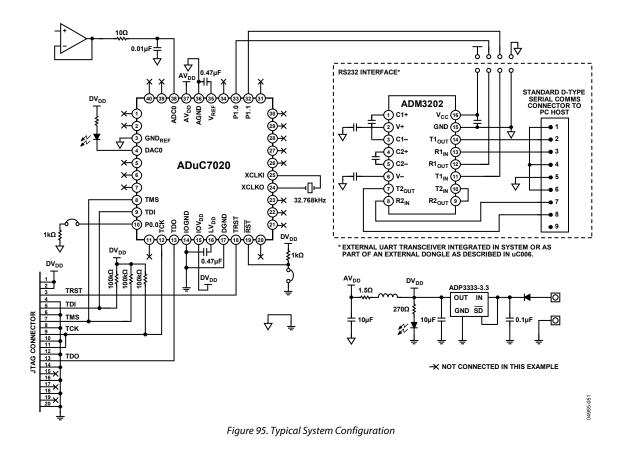

## **TYPICAL SYSTEM CONFIGURATION**

A typical ADuC7020 configuration is shown in Figure 95. It summarizes some of the hardware considerations discussed in the previous sections. The bottom of the CSP package has an exposed pad that must be soldered to a metal plate on the board for mechanical reasons. The metal plate of the board can be connected to ground.

Figure 94. Internal Power-On Reset Operation

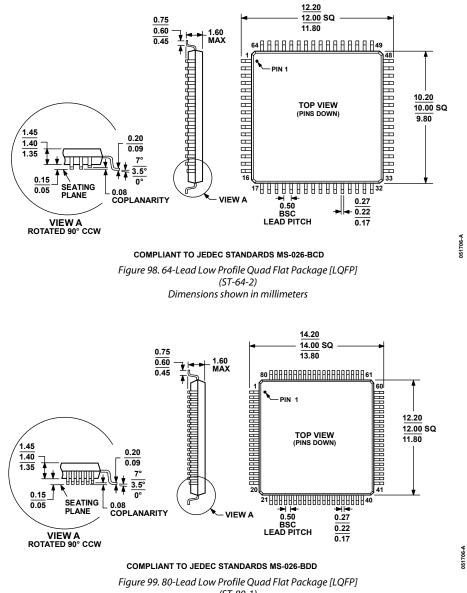

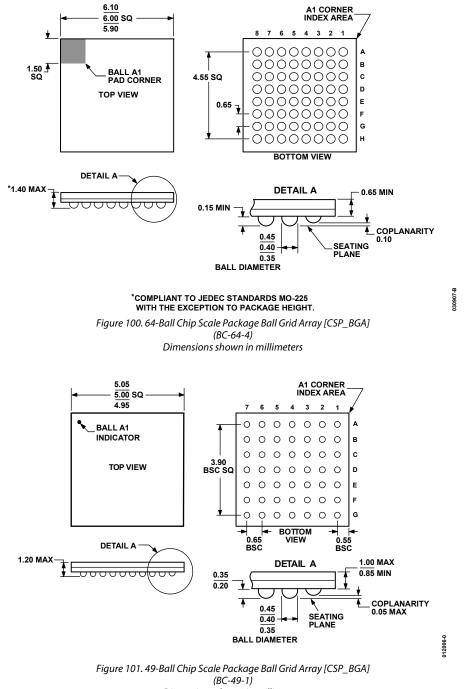

(ST-80-1) Dimensions shown in millimeters

## **Data Sheet**

## ADuC7019/20/21/22/24/25/26/27/28/29

Dimensions shown in millimeters