Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                    |

|----------------------------|--------------------------------------------------------------------|

| Product Status             | Active                                                             |

| Core Processor             | ARM7®                                                              |

| Core Size                  | 16/32-Bit                                                          |

| Speed                      | 44MHz                                                              |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                         |

| Peripherals                | PLA, PWM, PSM, Temp Sensor, WDT                                    |

| Number of I/O              | 30                                                                 |

| Program Memory Size        | 62KB (31K x16)                                                     |

| Program Memory Type        | FLASH                                                              |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 2K x 32                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                        |

| Data Converters            | A/D 10x12b; D/A 2x12b                                              |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 64-LQFP                                                            |

| Supplier Device Package    | 64-LQFP (10x10)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7024bstz62 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **GENERAL DESCRIPTION**

The ADuC7019/20/21/22/24/25/26/27/28/29 are fully integrated, 1 MSPS, 12-bit data acquisition systems incorporating high performance multichannel ADCs, 16-bit/32-bit MCUs, and Flash\*/EE memory on a single chip.

The ADC consists of up to 12 single-ended inputs. An additional four inputs are available but are multiplexed with the four DAC output pins. The four DAC outputs are available only on certain models (ADuC7020, ADuC7026, ADuC7028, and ADuC7029). However, in many cases where the DAC outputs are not present, these pins can still be used as additional ADC inputs, giving a maximum of 16 ADC input channels. The ADC can operate in single-ended or differential input mode. The ADC input voltage is 0 V to  $V_{\rm REF}$ . A low drift band gap reference, temperature sensor, and voltage comparator complete the ADC peripheral set.

Depending on the part model, up to four buffered voltage output DACs are available on-chip. The DAC output range is programmable to one of three voltage ranges.

The devices operate from an on-chip oscillator and a PLL generating an internal high frequency clock of 41.78 MHz (UCLK). This clock is routed through a programmable clock divider from which the MCU core clock operating frequency is generated. The microcontroller core is an ARM7TDMI\*, 16-bit/32-bit RISC machine, which offers up to 41 MIPS peak performance. Eight kilobytes of SRAM and 62 kilobytes of nonvolatile Flash/EE memory are provided on-chip. The ARM7TDMI core views all memory and registers as a single linear array.

On-chip factory firmware supports in-circuit serial download via the UART or  $I^2C$  serial interface port; nonintrusive emulation is also supported via the JTAG interface. These features are incorporated into a low cost QuickStart<sup> $\infty$ </sup> development system supporting this MicroConverter<sup> $\infty$ </sup> family.

The parts operate from 2.7 V to 3.6 V and are specified over an industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. When operating at 41.78 MHz, the power dissipation is typically 120 mW. The ADuC7019/20/21/22/24/25/26/27/28/29 are available in a variety of memory models and packages (see Ordering Guide).

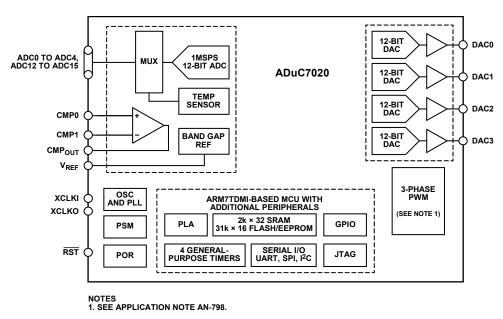

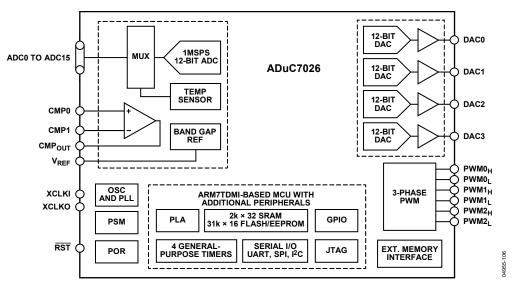

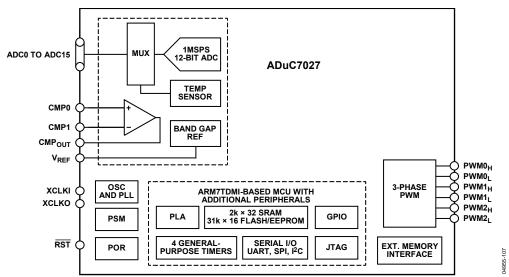

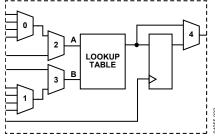

Figure 2.

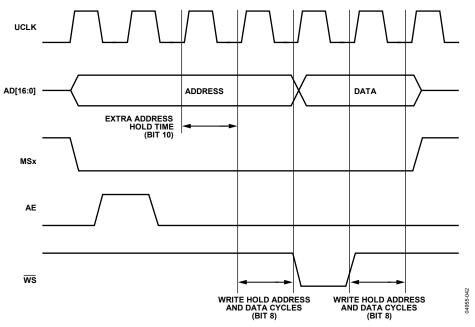

Figure 7.

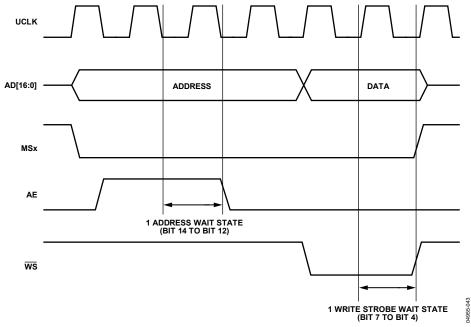

Figure 8.

| Parameter                                          | Min    | Тур    | Max             | Unit   | Test Conditions/Comments                                                                                        |

|----------------------------------------------------|--------|--------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------|

| DAC AC CHARACTERISTICS                             |        |        |                 |        |                                                                                                                 |

| Voltage Output Settling Time                       |        | 10     |                 | μs     |                                                                                                                 |

| Digital-to-Analog Glitch Energy                    |        | ±20    |                 | nV-sec | 1 LSB change at major carry (where maximum<br>number of bits simultaneously changes in the<br>DACxDAT register) |

| COMPARATOR                                         |        |        |                 |        |                                                                                                                 |

| Input Offset Voltage                               |        | ±15    |                 | mV     |                                                                                                                 |

| Input Bias Current                                 |        | 1      |                 | μΑ     |                                                                                                                 |

| Input Voltage Range                                | AGND   |        | $AV_{DD} - 1.2$ | V      |                                                                                                                 |

| Input Capacitance                                  |        | 7      |                 | pF     |                                                                                                                 |

| Hysteresis <sup>4, 6</sup>                         | 2      |        | 15              | mV     | Hysteresis turned on or off via the CMPHYST bit in the CMPCON register                                          |

| Response Time                                      |        | 3      |                 | μs     | 100 mV overdrive and configured with CMPRES = 11                                                                |

| TEMPERATURE SENSOR                                 |        |        |                 |        |                                                                                                                 |

| Voltage Output at 25°C                             |        | 780    |                 | mV     |                                                                                                                 |

| Voltage TC                                         |        | -1.3   |                 | mV/°C  |                                                                                                                 |

| Accuracy                                           |        | ±3     |                 | °C     |                                                                                                                 |

| POWER SUPPLY MONITOR (PSM)                         |        |        |                 |        |                                                                                                                 |

| IOV <sub>DD</sub> Trip Point Selection             |        | 2.79   |                 | V      | Two selectable trip points                                                                                      |

|                                                    |        | 3.07   |                 | V      |                                                                                                                 |

| Power Supply Trip Point Accuracy                   |        | ±2.5   |                 | %      | Of the selected nominal trip point voltage                                                                      |

| POWER-ON-RESET                                     |        | 2.36   |                 | V      |                                                                                                                 |

| GLITCH IMMUNITY ON RESET PIN <sup>4</sup>          |        | 50     |                 | μs     |                                                                                                                 |

| WATCHDOG TIMER (WDT)                               |        |        |                 |        |                                                                                                                 |

| Timeout Period                                     | 0      |        | 512             | sec    |                                                                                                                 |

| FLASH/EE MEMORY                                    |        |        |                 |        |                                                                                                                 |

| Endurance <sup>9</sup>                             | 10,000 |        |                 | Cycles |                                                                                                                 |

| Data Retention <sup>10</sup>                       | 20     |        |                 | Years  | T <sub>J</sub> = 85°C                                                                                           |

| DIGITAL INPUTS                                     |        |        |                 |        | All digital inputs excluding XCLKI and XCLKO                                                                    |

| Logic 1 Input Current                              |        | ±0.2   | ±1              | μΑ     | $V_{IH} = IOV_{DD}$ or $V_{IH} = 5 V$                                                                           |

| Logic 0 Input Current                              |        | -40    | -60             | μΑ     | V <sub>IL</sub> = 0 V; except TDI on<br>ADuC7019/20/21/22/24/25/29                                              |

|                                                    |        | -80    | -120            | μΑ     | V <sub>IL</sub> = 0 V; TDI on ADuC7019/20/21/22/24/25/29                                                        |

| Input Capacitance                                  |        | 10     |                 | pF     |                                                                                                                 |

| LOGIC INPUTS <sup>3</sup>                          |        |        |                 |        | All logic inputs excluding XCLKI                                                                                |

| V <sub>INL</sub> , Input Low Voltage               |        |        | 0.8             | V      |                                                                                                                 |

| V <sub>INH</sub> , Input High Voltage              | 2.0    |        |                 | V      |                                                                                                                 |

| LOGIC OUTPUTS                                      |        |        |                 |        | All digital outputs excluding XCLKO                                                                             |

| V <sub>OH</sub> , Output High Voltage              | 2.4    |        |                 | V      | I <sub>SOURCE</sub> = 1.6 mA                                                                                    |

| V <sub>OL</sub> , Output Low Voltage <sup>11</sup> |        |        | 0.4             | V      | $I_{SINK} = 1.6 \text{ mA}$                                                                                     |

| CRYSTAL INPUTS XCLKI and XCLKO                     |        |        |                 |        |                                                                                                                 |

| Logic Inputs, XCLKI Only                           |        |        |                 |        |                                                                                                                 |

| V <sub>INL</sub> , Input Low Voltage               |        | 1.1    |                 | V      |                                                                                                                 |

| V <sub>INH</sub> , Input High Voltage              |        | 1.7    |                 | V      |                                                                                                                 |

| XCLKI Input Capacitance                            |        | 20     |                 | pF     |                                                                                                                 |

| XCLKO Output Capacitance                           |        | 20     |                 | pF     |                                                                                                                 |

| INTERNAL OSCILLATOR                                |        | 32.768 |                 | kHz    |                                                                                                                 |

|                                                    |        |        | ±3              | %      |                                                                                                                 |

|                                                    |        |        | ±2 <sup>4</sup> | %      | $T_A = 0$ °C to 85°C range                                                                                      |

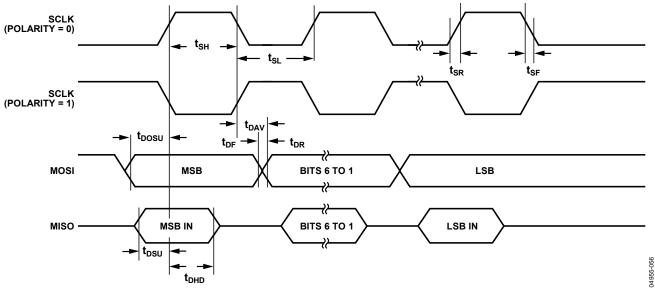

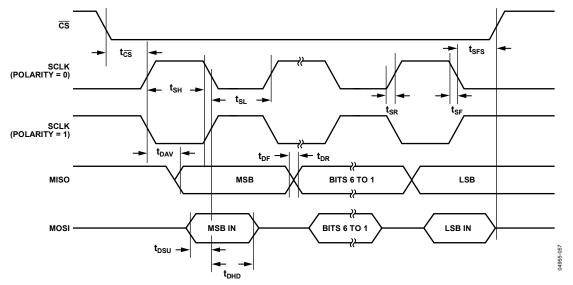

Table 7. SPI Master Mode Timing (Phase Mode = 0)

| Parameter         | Description                                         | Min                 | Тур                            | Max  | Unit |

|-------------------|-----------------------------------------------------|---------------------|--------------------------------|------|------|

| t <sub>SL</sub>   | SCLK low pulse width <sup>1</sup>                   |                     | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>SH</sub>   | SCLK high pulse width <sup>1</sup>                  |                     | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| $t_{DAV}$         | Data output valid after SCLK edge                   |                     |                                | 25   | ns   |

| t <sub>DOSU</sub> | Data output setup before SCLK edge                  |                     |                                | 75   | ns   |

| t <sub>DSU</sub>  | Data input setup time before SCLK edge <sup>2</sup> | 1 × tuclk           |                                |      | ns   |

| $t_{DHD}$         | Data input hold time after SCLK edge <sup>2</sup>   | $2 \times t_{UCLK}$ |                                |      | ns   |

| $t_{DF}$          | Data output fall time                               |                     | 5                              | 12.5 | ns   |

| $t_{DR}$          | Data output rise time                               |                     | 5                              | 12.5 | ns   |

| $t_{SR}$          | SCLK rise time                                      |                     | 5                              | 12.5 | ns   |

| t <sub>SF</sub>   | SCLK fall time                                      |                     | 5                              | 12.5 | ns   |

$<sup>^{1}</sup>$  t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCONMMR. t<sub>HCLK</sub> = t<sub>UCLK</sub>/ $^{2CD}$ ; see Figure 67.

$<sup>^{2}</sup>$  t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider; see Figure 67.

Figure 16. SPI Master Mode Timing (Phase Mode = 0)

**Table 8. SPI Slave Mode Timing (Phsae Mode = 1)**

| Parameter        | Description                                         | Min                                         | Тур                            | Max  | Unit |

|------------------|-----------------------------------------------------|---------------------------------------------|--------------------------------|------|------|

| t <sub>cs</sub>  | CS to SCLK edge <sup>1</sup>                        | $(2 \times t_{HCLK}) + (2 \times t_{UCLK})$ |                                |      | ns   |

| $t_{SL}$         | SCLK low pulse width <sup>2</sup>                   |                                             | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>SH</sub>  | SCLK high pulse width <sup>2</sup>                  |                                             | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| $t_{DAV}$        | Data output valid after SCLK edge                   |                                             |                                | 25   | ns   |

| t <sub>DSU</sub> | Data input setup time before SCLK edge <sup>1</sup> | 1 × tuclk                                   |                                |      | ns   |

| $t_{DHD}$        | Data input hold time after SCLK edge <sup>1</sup>   | $2 \times t_{UCLK}$                         |                                |      | ns   |

| t <sub>DF</sub>  | Data output fall time                               |                                             | 5                              | 12.5 | ns   |

| $t_{DR}$         | Data output rise time                               |                                             | 5                              | 12.5 | ns   |

| t <sub>SR</sub>  | SCLK rise time                                      |                                             | 5                              | 12.5 | ns   |

| $t_{SF}$         | SCLK fall time                                      |                                             | 5                              | 12.5 | ns   |

| t <sub>SFS</sub> | CS high after SCLK edge                             | 0                                           |                                |      | ns   |

$<sup>^{1}</sup>$  t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider; see Figure 67.  $^{2}$  t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCONMMR. t<sub>HCLK</sub> = t<sub>UCLK</sub>/2<sup>CD</sup>; see Figure 67.

Figure 17. SPI Slave Mode Timing (Phase Mode = 1)

### **ABSOLUTE MAXIMUM RATINGS**

$AGND = REFGND = DACGND = GND_{REF}, T_A = 25 ^{\circ}C, unless otherwise noted.$

Table 10.

| Table 10.                                            |                                                                    |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|

| Parameter                                            | Rating                                                             |  |  |  |  |

| AV <sub>DD</sub> to IOV <sub>DD</sub>                | -0.3 V to +0.3 V                                                   |  |  |  |  |

| AGND to DGND                                         | −0.3 V to +0.3 V                                                   |  |  |  |  |

| IOV <sub>DD</sub> to IOGND, AV <sub>DD</sub> to AGND | −0.3 V to +6 V                                                     |  |  |  |  |

| Digital Input Voltage to IOGND                       | −0.3 V to +5.3 V                                                   |  |  |  |  |

| Digital Output Voltage to IOGND                      | $-0.3 \mathrm{V}$ to $\mathrm{IOV}_{\mathrm{DD}} + 0.3 \mathrm{V}$ |  |  |  |  |

| V <sub>REF</sub> to AGND                             | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                        |  |  |  |  |

| Analog Inputs to AGND                                | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                        |  |  |  |  |

| Analog Outputs to AGND                               | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                        |  |  |  |  |

| Operating Temperature Range, Industrial              | -40°C to +125°C                                                    |  |  |  |  |

| Storage Temperature Range                            | −65°C to +150°C                                                    |  |  |  |  |

| Junction Temperature                                 | 150°C                                                              |  |  |  |  |

| $\theta_{JA}$ Thermal Impedance                      |                                                                    |  |  |  |  |

| 40-Lead LFCSP                                        | 26°C/W                                                             |  |  |  |  |

| 49-Ball CSP_BGA                                      | 80°C/W                                                             |  |  |  |  |

| 64-Lead LFCSP                                        | 24°C/W                                                             |  |  |  |  |

| 64-Ball CSP_BGA                                      | 75°C/W                                                             |  |  |  |  |

| 64-Lead LQFP                                         | 47°C/W                                                             |  |  |  |  |

| 80-Lead LQFP                                         | 38°C/W                                                             |  |  |  |  |

| Peak Solder Reflow Temperature                       |                                                                    |  |  |  |  |

| SnPb Assemblies (10 sec to 30 sec)                   | 240°C                                                              |  |  |  |  |

| RoHS Compliant Assemblies                            | 260°C                                                              |  |  |  |  |

| (20 sec to 40 sec)                                   |                                                                    |  |  |  |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

| Pin No.   |      |      |                                         |                                                                                                                                                                                                            |

|-----------|------|------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7019/7020 | 7021 | 7022 | Mnemonic                                | Description                                                                                                                                                                                                |

| 22        | 22   | 21   | P2.0/SPM9/PLAO[5]/CONV <sub>START</sub> | Serial Port Multiplexed. General-Purpose Input and Output Port 2.0/UART/<br>Programmable Logic Array Output Element 5/Start Conversion Input Signal<br>for ADC.                                            |

| 23        | 23   | 22   | P0.7/ECLK/XCLK/SPM8/PLAO[4]             | Serial Port Multiplexed. General-Purpose Input and Output Port 0.7/<br>Output for External Clock Signal/Input to the Internal Clock Generator<br>Circuits/UART/ Programmable Logic Array Output Element 4. |

| 24        | 24   | 23   | XCLKO                                   | Output from the Crystal Oscillator Inverter.                                                                                                                                                               |

| 25        | 25   | 24   | XCLKI                                   | Input to the Crystal Oscillator Inverter and Input to the Internal Clock<br>Generator Circuits.                                                                                                            |

| 26        | 26   | 25   | P1.7/SPM7/PLAO[0]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.7/UART, SPI/Programmable Logic Array Output Element 0.                                                                                    |

| 27        | 27   | 26   | P1.6/SPM6/PLAI[6]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.6/UART, SPI/Programmable Logic Array Input Element 6.                                                                                     |

| 28        | 28   | 27   | P1.5/SPM5/PLAI[5]/IRQ3                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.5/UART, SPI/Programmable Logic Array Input Element 5/External Interrupt Request 3, Active High.                                           |

| 29        | 29   | 28   | P1.4/SPM4/PLAI[4]/IRQ2                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.4/UART, SPI/Programmable Logic Array Input Element 4/External Interrupt Request 2, Active High.                                           |

| 30        | 30   | 29   | P1.3/SPM3/PLAI[3]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.3/UART, I2C1/Programmable Logic Array Input Element 3.                                                                                    |

| 31        | 31   | 30   | P1.2/SPM2/PLAI[2]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.2/UART, I2C1/Programmable Logic Array Input Element 2.                                                                                    |

| 32        | 32   | 31   | P1.1/SPM1/PLAI[1]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.1/UART, I2CO/Programmable Logic Array Input Element 1.                                                                                    |

| 33        | 33   | 32   | P1.0/T1/SPM0/PLAI[0]                    | Serial Port Multiplexed. General-Purpose Input and Output Port 1.0/<br>Timer1 Input/UART, I2C0/Programmable Logic Array Input Element 0.                                                                   |

| 34        | -    | -    | P4.2/PLAO[10]                           | General-Purpose Input and Output Port 4.2/Programmable Logic Array Output Element 10.                                                                                                                      |

| 35        | 34   | 33   | V <sub>REF</sub>                        | 2.5 V Internal Voltage Reference. Must be connected to a 0.47 µF capacitor when using the internal reference.                                                                                              |

| 36        | 35   | 34   | AGND                                    | Analog Ground. Ground reference point for the analog circuitry.                                                                                                                                            |

| 37        | 36   | 35   | AV <sub>DD</sub>                        | 3.3 V Analog Power.                                                                                                                                                                                        |

| 0         | 0    | 0    | EP                                      | Exposed Pad. The pin configuration for the ADuC7019/ADuC7020/<br>ADuC7021/ADuC7022 has an exposed pad that must be soldered for<br>mechanical purposes and left unconnected.                               |

### **ADUC7028**

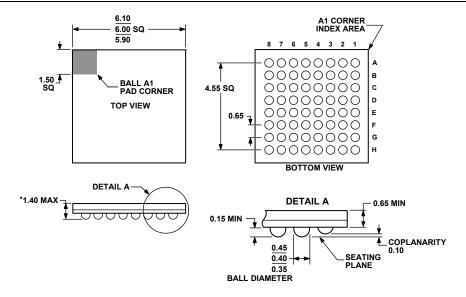

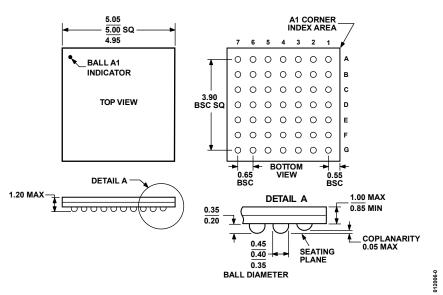

Figure 26. 64-Ball CSP\_BGA Pin Configuration (ADuC7028)

Table 14. Pin Function Descriptions (ADuC7028)

| Pin No. | Mnemonic                           | Description                                                                                                                                                                        |

|---------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | ADC3/CMP1                          | Single-Ended or Differential Analog Input 3/Comparator Negative Input.                                                                                                             |

| A2      | DACV <sub>DD</sub>                 | 3.3 V Power Supply for the DACs. Must be connected to AV <sub>DD</sub> .                                                                                                           |

| А3      | AV <sub>DD</sub>                   | 3.3 V Analog Power.                                                                                                                                                                |

| A4      | AGND                               | Analog Ground. Ground reference point for the analog circuitry.                                                                                                                    |

| A5      | DACGND                             | Ground for the DAC. Typically connected to AGND.                                                                                                                                   |

| A6      | P4.2/PLAO[10]                      | General-Purpose Input and Output Port 4.2/Programmable Logic Array Output Element 10.                                                                                              |

| A7      | P1.1/SPM1/PLAI[1]                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.1/UART, I2C0/Programmable Logic Array Input Element 1.                                                            |

| A8      | P1.2/SPM2/PLAI[2]                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.2/UART, I2C1/Programmable Logic Array Input Element 2.                                                            |

| B1      | ADC4                               | Single-Ended or Differential Analog Input 4.                                                                                                                                       |

| B2      | ADC2/CMP0                          | Single-Ended or Differential Analog Input 2/Comparator Positive Input.                                                                                                             |

| В3      | ADC1                               | Single-Ended or Differential Analog Input 1.                                                                                                                                       |

| B4      | DAC <sub>REF</sub>                 | External Voltage Reference for the DACs. Range: DACGND to DACV <sub>DD</sub> .                                                                                                     |

| B5      | V <sub>REF</sub>                   | 2.5 V Internal Voltage Reference. Must be connected to a 0.47 $\mu F$ capacitor when using the internal reference.                                                                 |

| B6      | P1.0/T1/SPM0/PLAI[0]               | Serial Port Multiplexed. General-Purpose Input and Output Port 1.0/Timer1 Input/UART, I2CO/<br>Programmable Logic Array Input Element 0.                                           |

| B7      | P1.4/SPM4/PLAI[4]/IRQ2             | Serial Port Multiplexed. General-Purpose Input and Output Port 1.4/UART, SPI/Programmable Logic Array Input Element 4/External Interrupt Request 2, Active High.                   |

| B8      | P1.3/SPM3/PLAI[3]                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.3/UART, I2C1/Programmable Logic Array Input Element 3.                                                            |

| C1      | ADC6                               | Single-Ended or Differential Analog Input 6.                                                                                                                                       |

| C2      | ADC5                               | Single-Ended or Differential Analog Input 5.                                                                                                                                       |

| C3      | ADC0                               | Single-Ended or Differential Analog Input 0.                                                                                                                                       |

| C4      | P4.5/PLAO[13]                      | General-Purpose Input and Output Port 4.5/Programmable Logic Array Output Element 13.                                                                                              |

| C5      | P4.3/PLAO[11]                      | General-Purpose Input and Output Port 4.3/Programmable Logic Array Output Element 11.                                                                                              |

| C6      | P4.0/PLAO[8]                       | General-Purpose Input and Output Port 4.0/Programmable Logic Array Output Element 8.                                                                                               |

| C7      | P4.1/PLAO[9]                       | General-Purpose Input and Output Port 4.1/Programmable Logic Array Output Element 9.                                                                                               |

| C8      | IOGND                              | Ground for GPIO (see Table 78). Typically connected to DGND.                                                                                                                       |

| D1      | ADCNEG                             | Bias Point or Negative Analog Input of the ADC in Pseudo Differential Mode. Must be connected to the ground of the signal to convert. This bias point must be between 0 V and 1 V. |

| D2      | GND <sub>REF</sub>                 | Ground Voltage Reference for the ADC. For optimal performance, the analog power supply should be separated from IOGND and DGND.                                                    |

| D3      | ADC7                               | Single-Ended or Differential Analog Input 7.                                                                                                                                       |

| D4      | P4.4/PLAO[12]                      | General-Purpose Input and Output Port 4.4/Programmable Logic Array Output Element 12.                                                                                              |

| D5      | P3.6/PWM <sub>TRIP</sub> /PLAI[14] | General-Purpose Input and Output Port 3.6/PWM Safety Cutoff/Programmable Logic Array Input Element 14.                                                                             |

| D6      | P1.7/SPM7/PLAO[0]                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.7/UART, SPI/Programmable Logic Array Output Element 0.                                                            |

| Pin No. | Mnemonic                                | Description                                                                                                                                                                                                                                                                                  |

|---------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1      | TMS                                     | JTAG Test Port Input, Test Mode Select. Debug and download access.                                                                                                                                                                                                                           |

| E2      | BM/P0.0/CMP <sub>OUT</sub> /PLAI[7]     | Multifunction I/O Pin. Boot mode. The ADuC7029 enters UART download mode if BM is low at reset and executes code if BM is pulled high at reset through a 1 k $\Omega$ resistor/General-Purpose Input and Output Port 0.0/Voltage Comparator Output/Programmable Logic Array Input Element 7. |

| E3      | DAC2/ADC14                              | DAC2 Voltage Output/ADC Input 14.                                                                                                                                                                                                                                                            |

| E4      | IOV <sub>DD</sub>                       | 3.3 V Supply for GPIO (see Table 78) and Input of the On-Chip Voltage Regulator.                                                                                                                                                                                                             |

| E5      | P3.2/PWM1 <sub>H</sub> /PLAI[10]        | General-Purpose Input and Output Port 3.2/PWM Phase 1 High-Side Output/Programmable Logic Array Input Element 10.                                                                                                                                                                            |

| E6      | P3.5/PWM2 <sub>L</sub> /PLAI[13]        | General-Purpose Input and Output Port 3.5/PWM Phase 2 Low-Side Output/Programmable Logic Array Input Element 13.                                                                                                                                                                             |

| E7      | P0.7/ECLK/XCLK/SPM8/PLAO[4]             | Serial Port Multiplexed. General-Purpose Input and Output Port 0.7/Output for External Clock Signal/Input to the Internal Clock Generator Circuits/UART/Programmable Logic Array Output Element 4.                                                                                           |

| F1      | TDI                                     | JTAG Test Port Input, Test Data In. Debug and download access.                                                                                                                                                                                                                               |

| F2      | P0.6/T1/MRST/PLAO[3]                    | Multifunction Pin, Driven Low After Reset. General-Purpose Output Port 0.6/Timer1 Input/<br>Power-On Reset Output/Programmable Logic Array Output Element 3.                                                                                                                                 |

| F3      | IOGND                                   | Ground for GPIO (see Table 78). Typically connected to DGND.                                                                                                                                                                                                                                 |

| F4      | P3.1/PWM0 <sub>L</sub> /PLAI[9]         | General-Purpose Input and Output Port 3.1/PWM Phase 0 Low-Side Output/Programmable Logic Array Input Element 9.                                                                                                                                                                              |

| F5      | P3.0/PWM0 <sub>H</sub> /PLAI[8]         | General-Purpose Input and Output Port 3.0/PWM Phase 0 High-Side Output/Programmable Logic Array Input Element 8.                                                                                                                                                                             |

| F6      | RST                                     | Reset Input, Active Low.                                                                                                                                                                                                                                                                     |

| F7      | P2.0/SPM9/PLAO[5]/CONV <sub>START</sub> | Serial Port Multiplexed. General-Purpose Input and Output Port 2.0/UART/Programmable Logic Array Output Element 5/Start Conversion Input Signal for ADC.                                                                                                                                     |

| G1      | TCK                                     | JTAG Test Port Input, Test Clock. Debug and download access.                                                                                                                                                                                                                                 |

| G2      | TDO                                     | JTAG Test Port Output, Test Data Out. Debug and download access.                                                                                                                                                                                                                             |

| G3      | LV <sub>DD</sub>                        | 2.6 V Output of the On-Chip Voltage Regulator. This output must be connected to a 0.47 $\mu$ F capacitor to DGND only.                                                                                                                                                                       |

| G4      | DGND                                    | Ground for Core Logic.                                                                                                                                                                                                                                                                       |

| G5      | P0.3/TRST/ADC <sub>BUSY</sub>           | General-Purpose Input and Output Port 0.3/JTAG Test Port Input, Test Reset/ADC <sub>BUSY</sub> Signal Output.                                                                                                                                                                                |

| G6      | IRQ0/P0.4/PWM <sub>TRIP</sub> /PLAO[1]  | Multifunction I/O Pin. External Interrupt Request 0, Active High/General-Purpose Input and Output Port 0.4/PWM Trip External Input/Programmable Logic Array Output Element 1.                                                                                                                |

| G7      | IRQ1/P0.5/ADC <sub>BUSY</sub> /PLAO[2]  | Multifunction I/O Pin. External Interrupt Request 1, Active High/General-Purpose Input and Output Port 0.5/ADC <sub>BUSY</sub> Signal Output/Programmable Logic Array Output Element 2.                                                                                                      |

## **Data Sheet**

| Address                             | Name           | Byte    | Access<br>Type | Default<br>Value | Page |  |  |

|-------------------------------------|----------------|---------|----------------|------------------|------|--|--|

| Reference Address Base = 0xFFFF0480 |                |         |                |                  |      |  |  |

| 0x048C                              | REFCON         | 1       | R/W            | 0x00             | 50   |  |  |

| ADC Addr                            | ess Base = 0xF | FFF050  | 0              |                  |      |  |  |

| 0x0500                              | ADCCON         | 2       | R/W            | 0x0600           | 46   |  |  |

| 0x0504                              | ADCCP          | 1       | R/W            | 0x00             | 47   |  |  |

| 0x0508                              | ADCCN          | 1       | R/W            | 0x01             | 47   |  |  |

| 0x050C                              | ADCSTA         | 1       | R              | 0x00             | 48   |  |  |

| 0x0510                              | ADCDAT         | 4       | R              | 0x00000000       | 48   |  |  |

| 0x0514                              | ADCRST         | 1       | R/W            | 0x00             | 48   |  |  |

| 0x0530                              | ADCGN          | 2       | R/W            | 0x0200           | 48   |  |  |

| 0x0534                              | ADCOF          | 2       | R/W            | 0x0200           | 48   |  |  |

| DAC Addr                            | ess Base = 0xF | FFF060  | 0              |                  |      |  |  |

| 0x0600                              | DAC0CON        | 1       | R/W            | 0x00             | 56   |  |  |

| 0x0604                              | DAC0DAT        | 4       | R/W            | 0x00000000       | 56   |  |  |

| 0x0608                              | DAC1CON        | 1       | R/W            | 0x00             | 56   |  |  |

| 0x060C                              | DAC1DAT        | 4       | R/W            | 0x00000000       | 56   |  |  |

| 0x0610                              | DAC2CON        | 1       | R/W            | 0x00             | 56   |  |  |

| 0x0614                              | DAC2DAT        | 4       | R/W            | 0x00000000       | 56   |  |  |

| 0x0618                              | DAC3CON        | 1       | R/W            | 0x00             | 56   |  |  |

| 0x061C                              | DAC3DAT        | 4       | R/W            | 0x00000000       | 56   |  |  |

| UART Base                           | e Address = 0x | (FFFF07 | 00             |                  |      |  |  |

| 0x0700                              | COMTX          | 1       | R/W            | 0x00             | 71   |  |  |

|                                     | COMRX          | 1       | R              | 0x00             | 71   |  |  |

|                                     | COMDIV0        | 1       | R/W            | 0x00             | 71   |  |  |

| 0x0704                              | COMIEN0        | 1       | R/W            | 0x00             | 71   |  |  |

|                                     | COMDIV1        | 1       | R/W            | 0x00             | 72   |  |  |

| 0x0708                              | COMIID0        | 1       | R              | 0x01             | 72   |  |  |

| 0x070C                              | COMCON0        | 1       | R/W            | 0x00             | 72   |  |  |

| 0x0710                              | COMCON1        | 1       | R/W            | 0x00             | 72   |  |  |

| 0x0714                              | COMSTA0        | 1       | R              | 0x60             | 72   |  |  |

| 0x0718                              | COMSTA1        | 1       | R              | 0x00             | 73   |  |  |

| 0x071C                              | COMSCR         | 1       | R/W            | 0x00             | 73   |  |  |

| 0x0720                              | COMIEN1        | 1       | R/W            | 0x04             | 73   |  |  |

| 0x0724                              | COMIID1        | 1       | R              | 0x01             | 73   |  |  |

|                                     | COMADR         | 1       | R/W            | 0xAA             | 74   |  |  |

| 0x0728                              | COMADA         |         | 11/ 44         | 0,7,7,7          | / -  |  |  |

|            |                |         | Access | Default | T_   |

|------------|----------------|---------|--------|---------|------|

| Address    | Name           | Byte    | Type   | Value   | Page |

|            | Address = 0xl  |         |        | T a aa  |      |

| 0x0800     | I2COMSTA       | 1       | R/W    | 0x00    | 76   |

| 0x0804     | I2COSSTA       | 1       | R      | 0x01    | 76   |

| 0x0808     | I2COSRX        | 1       | R      | 0x00    | 77   |

| 0x080C     | I2C0STX        | 1       | W      | 0x00    | 77   |

| 0x0810     | I2COMRX        | 1       | R      | 0x00    | 77   |

| 0x0814     | I2C0MTX        | 1       | W      | 0x00    | 77   |

| 0x0818     | I2C0CNT        | 1       | R/W    | 0x00    | 77   |

| 0x081C     | I2C0ADR        | 1       | R/W    | 0x00    | 77   |

| 0x0824     | I2C0BYTE       | 1       | R/W    | 0x00    | 77   |

| 0x0828     | I2C0ALT        | 1       | R/W    | 0x00    | 78   |

| 0x082C     | I2C0CFG        | 1       | R/W    | 0x00    | 78   |

| 0x0830     | I2C0DIV        | 2       | R/W    | 0x1F1F  | 79   |

| 0x0838     | I2C0ID0        | 1       | R/W    | 0x00    | 79   |

| 0x083C     | I2C0ID1        | 1       | R/W    | 0x00    | 79   |

| 0x0840     | I2C0ID2        | 1       | R/W    | 0x00    | 79   |

| 0x0844     | I2C0ID3        | 1       | R/W    | 0x00    | 79   |

| 0x0848     | I2C0CCNT       | 1       | R/W    | 0x01    | 79   |

| 0x084C     | I2C0FSTA       | 2       | R/W    | 0x0000  | 79   |

| I2C1 Base  | Address = 0xl  | FFFF090 | 0      |         |      |

| 0x0900     | I2C1MSTA       | 1       | R/W    | 0x00    | 76   |

| 0x0904     | I2C1SSTA       | 1       | R      | 0x01    | 76   |

| 0x0908     | I2C1SRX        | 1       | R      | 0x00    | 77   |

| 0x090C     | I2C1STX        | 1       | W      | 0x00    | 77   |

| 0x0910     | I2C1MRX        | 1       | R      | 0x00    | 77   |

| 0x0914     | I2C1MTX        | 1       | W      | 0x00    | 77   |

| 0x0918     | I2C1CNT        | 1       | R/W    | 0x00    | 77   |

| 0x091C     | I2C1ADR        | 1       | R/W    | 0x00    | 77   |

| 0x0924     | I2C1BYTE       | 1       | R/W    | 0x00    | 77   |

| 0x0928     | I2C1ALT        | 1       | R/W    | 0x00    | 78   |

| 0x092C     | I2C1CFG        | 1       | R/W    | 0x00    | 78   |

| 0x0930     | I2C1DIV        | 2       | R/W    | 0x1F1F  | 79   |

| 0x0938     | I2C1ID0        | 1       | R/W    | 0x00    | 79   |

| 0x093C     | I2C1ID1        | 1       | R/W    | 0x00    | 79   |

| 0x0940     | I2C1ID2        | 1       | R/W    | 0x00    | 79   |

| 0x0944     | I2C1ID3        | 1       | R/W    | 0x00    | 79   |

| 0x0948     | I2C1CCNT       | 1       | R/W    | 0x01    | 79   |

| 0x094C     | I2C1FSTA       | 2       | R/W    | 0x0000  | 79   |

| SPI Base A | .ddress = 0xFF | FF0A00  | 1      |         |      |

| 0x0A00     | SPISTA         | 1       | R      | 0x00    | 75   |

| 0x0A04     | SPIRX          | 1       | R      | 0x00    | 75   |

| 0x0A08     | SPITX          | 1       | W      | 0x00    | 75   |

| 0x0A0C     | SPIDIV         | 1       | R/W    | 0x1B    | 75   |

| 0x0A10     | SPICON         | 2       | R/W    | 0x0000  | 75   |

|            |                | 1       | ı      | 1       |      |

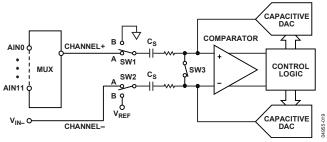

#### **Pseudo Differential Mode**

In pseudo differential mode, Channel— is linked to the  $V_{\rm IN-}$  pin of the ADuC7019/20/21/22/24/25/26/27/28/29. SW2 switches between A (Channel—) and B (V\_{REF}). The  $V_{\rm IN-}$  pin must be connected to ground or a low voltage. The input signal on  $V_{\rm IN+}$  can then vary from  $V_{\rm IN-}$  to  $V_{\rm REF}+V_{\rm IN-}$ . Note that  $V_{\rm IN-}$  must be chosen so that  $V_{\rm REF}+V_{\rm IN-}$  does not exceed  $AV_{\rm DD}$ .

Figure 56. ADC in Pseudo Differential Mode

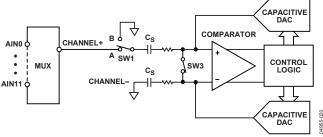

### Single-Ended Mode

In single-ended mode, SW2 is always connected internally to ground. The  $V_{\rm IN-}$  pin can be floating. The input signal range on  $V_{\rm IN+}$  is 0 V to  $V_{\rm REF}.$

Figure 57. ADC in Single-Ended Mode

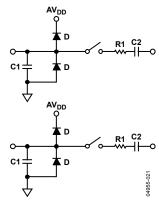

### **Analog Input Structure**

Figure 58 shows the equivalent circuit of the analog input structure of the ADC. The four diodes provide ESD protection for the analog inputs. Care must be taken to ensure that the analog input signals never exceed the supply rails by more than 300 mV; exceeding 300 mV causes these diodes to become forward-biased and start conducting into the substrate. These diodes can conduct up to 10 mA without causing irreversible damage to the part.

The C1 capacitors in Figure 58 are typically 4 pF and can be primarily attributed to pin capacitance. The resistors are lumped components made up of the on resistance of the switches. The value of these resistors is typically about 100  $\Omega$ . The C2 capacitors are the ADC's sampling capacitors and typically have a capacitance of 16 pF.

Figure 58. Equivalent Analog Input Circuit Conversion Phase: Switches Open, Track Phase: Switches Closed

For ac applications, removing high frequency components from the analog input signal is recommended by using an RC low-pass filter on the relevant analog input pins. In applications where harmonic distortion and signal-to-noise ratio are critical, the analog input should be driven from a low impedance source. Large source impedances significantly affect the ac performance of the ADC. This can necessitate the use of an input buffer amplifier. The choice of the op amp is a function of the particular application. Figure 59 and Figure 60 give an example of an ADC front end.

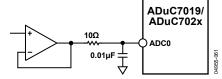

Figure 59. Buffering Single-Ended/Pseudo Differential Input

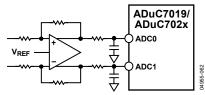

Figure 60. Buffering Differential Inputs

When no amplifier is used to drive the analog input, the source impedance should be limited to values lower than 1 k $\Omega$ . The maximum source impedance depends on the amount of total harmonic distortion (THD) that can be tolerated. The THD increases as the source impedance increases and the performance degrades.

### **DRIVING THE ANALOG INPUTS**

Internal or external references can be used for the ADC. In the differential mode of operation, there are restrictions on the common-mode input signal ( $V_{\text{CM}}$ ), which is dependent upon the reference value and supply voltage used to ensure that the signal remains within the supply rails. Table 28 gives some calculated  $V_{\text{CM}}$  minimum and  $V_{\text{CM}}$  maximum values.

### **Output Control Unit**

The operation of the output control unit is controlled by the 9-bit read/write PWMEN register. This register controls two distinct features of the output control unit that are directly useful in the control of electronic counter measures (ECM) or binary decimal counter measures (BDCM). The PWMEN register contains three crossover bits, one for each pair of PWM outputs. Setting Bit 8 of the PWMEN register enables the crossover mode for the 0H/0L pair of PWM signals, setting Bit 7 enables crossover on the 1H/1L pair of PWM signals, and setting Bit 6 enables crossover on the 2H/2L pair of PWM signals. If crossover mode is enabled for any pair of PWM signals, the high-side PWM signal from the timing unit (0H, for example) is diverted to the associated low-side output of the output control unit so that the signal ultimately appears at the PWM0<sub>L</sub> pin. Of course, the corresponding low-side output of the timing unit is also diverted to the complementary high-side output of the output control unit so that the signal appears at the PWM0<sub>H</sub> pin. Following a reset, the three crossover bits are cleared, and the crossover mode is disabled on all three pairs of PWM signals. The PWMEN register also contains six bits (Bit 0 to Bit 5) that can be used to individually enable or disable each of the six PWM outputs. If the associated bit of the PWMEN register is set, the corresponding PWM output is disabled regardless of the corresponding value of the duty cycle register. This PWM output signal remains in the off state as long as the corresponding enable/disable bit of the PWMEN register is set. The implementation of this output enable function is implemented after the crossover function.

Following a reset, all six enable bits of the PWMEN register are cleared, and all PWM outputs are enabled by default. In a manner identical to the duty cycle registers, the PWMEN is latched on the rising edge of the PWMSYNC signal. As a result, changes to this register become effective only at the start of each PWM cycle in single update mode. In double update mode, the PWMEN register can also be updated at the midpoint of the PWM cycle.

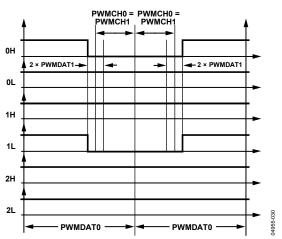

In the control of an ECM, only two inverter legs are switched at any time, and often the high-side device in one leg must be switched on at the same time as the low-side driver in a second leg. Therefore, by programming identical duty cycle values for two PWM channels (for example, PWMCH0 = PWMCH1) and setting Bit 7 of the PWMEN register to cross over the 1H/1L pair of PWM signals, it is possible to turn on the high-side switch of Phase A and the low-side switch of Phase B at the same time. In the control of ECM, it is usual for the third inverter leg (Phase C in this example) to be disabled for a number of PWM cycles. This function is implemented by disabling both the 2H and 2L PWM outputs by setting Bit 0 and Bit 1 of the PWMEN register.

This situation is illustrated in Figure 71, where it can be seen that both the 0H and 1L signals are identical because PWMCH0 = PWMCH1 and the crossover bit for Phase B is set.

Figure 71. Active Low PWM Signals Suitable for ECM Control, PWMCH0 = PWMCH1, Crossover 1H/1L Pair and Disable 0L, 1H, 2H, and 2L Outputs in Single Update Mode.

In addition, the other four signals (0L, 1H, 2H, and 2L) have been disabled by setting the appropriate enable/disable bits of the PWMEN register. In Figure 71, the appropriate value for the PWMEN register is 0x00A7. In normal ECM operation, each inverter leg is disabled for certain periods of time to change the PWMEN register based on the position of the rotor shaft (motor commutation).

#### **Gate Drive Unit**

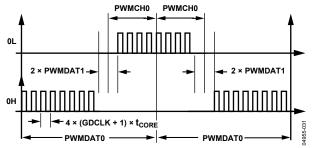

The gate drive unit of the PWM controller adds features that simplify the design of isolated gate-drive circuits for PWM inverters. If a transformer-coupled, power device, gate-drive amplifier is used, the active PWM signal must be chopped at a high frequency. The 16-bit read/write PWMCFG register programs this high frequency chopping mode. The chopped active PWM signals can be required for the high-side drivers only, the low-side drivers only, or both the high-side and low-side switches. Therefore, independent control of this mode for both high-side and low-side switches is included with two separate control bits in the PWMCFG register.

Typical PWM output signals with high frequency chopping enabled on both high-side and low-side signals are shown in Figure 72. Chopping of the high-side PWM outputs (0H, 1H, and 2H) is enabled by setting Bit 8 of the PWMCFG register. Chopping of the low-side PWM outputs (0L, 1L, and 2L) is enabled by setting Bit 9 of the PWMCFG register. The high chopping frequency is controlled by the 8-bit word (GDCLK) placed in Bit 0 to Bit 7 of the PWMCFG register. The period of this high frequency carrier is

$$t_{CHOP} = (4 \times (GDCLK + 1)) \times t_{CORE}$$

The chopping frequency is, therefore, an integral subdivision of the MicroConverter core frequency

$$f_{CHOP} = f_{CORE}/(4 \times (GDCLK + 1))$$

The GDCLK value can range from 0 to 255, corresponding to a programmable chopping frequency rate of 40.8 kHz to 10.44 MHz for a 41.78 MHz core frequency. The gate drive features must be programmed before operation of the PWM controller and are typically not changed during normal operation of the PWM controller. Following a reset, all bits of the PWMCFG register are cleared so that high frequency chopping is disabled, by default.

Figure 72. Typical PWM Signals with High Frequency Gate Chopping Enabled on Both High-Side and Low-Side Switches

#### **PWM Shutdown**

In the event of external fault conditions, it is essential that the PWM system be instantaneously shut down in a safe fashion. A low level on the PWM $_{\text{TRIP}}$  pin provides an instantaneous, asynchronous (independent of the MicroConverter core clock) shutdown of the PWM controller. All six PWM outputs are placed in the off state, that is, in low state. In addition, the PWMSYNC pulse is disabled. The PWM $_{\text{TRIP}}$  pin has an internal pull-down resistor to disable the PWM if the pin becomes disconnected. The state of the PWM $_{\text{TRIP}}$  pin can be read from Bit 3 of the PWMSTA register.

If a PWM shutdown command occurs, a PWMTRIP interrupt is generated, and internal timing of the 3-phase timing unit of the PWM controller is stopped. Following a PWM shutdown, the PWM can be reenabled (in a PWMTRIP interrupt service routine, for example) only by writing to all of the PWMDATO, PWMCHO, PWMCH1, and PWMCH2 registers. Provided that the external fault is cleared and the PWMTRIP is returned to a high level, the internal timing of the 3-phase timing unit resumes, and new duty-cycle values are latched on the next PWMSYNC boundary.

Note that the PWMTRIP interrupt is available in IRQ only, and the PWMSYNC interrupt is available in FIQ only. Both interrupts share the same bit in the interrupt controller. Therefore, only one of the interrupts can be used at a time. See the Interrupt System section for further details.

#### **PWM MMRs Interface**

The PWM block is controlled via the MMRs described in this section.

Table 66. PWMCON Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| PWMCON | 0xFFFFFC00 | 0x0000        | R/W    |

PWMCON is a control register that enables the PWM and chooses the update rate.

Table 67. PWMCON MMR Bit Descriptions

| -   |             |                                                                                                                                                    |  |  |  |  |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit | Name        | Description                                                                                                                                        |  |  |  |  |

| 7:5 |             | Reserved.                                                                                                                                          |  |  |  |  |

| 4   | PWM_SYNCSEL | External sync select. Set to use external sync. Cleared to use internal sync.                                                                      |  |  |  |  |

| 3   | PWM_EXTSYNC | External sync select. Set to select external synchronous sync signal. Cleared for asynchronous sync signal.                                        |  |  |  |  |

| 2   | PWMDBL      | Double update mode. Set to 1 by user to enable double update mode. Cleared to 0 by the user to enable single update mode.                          |  |  |  |  |

| 1   | PWM_SYNC_EN | PWM synchronization enable. Set by user to enable synchronization. Cleared by user to disable synchronization.                                     |  |  |  |  |

| 0   | PWMEN       | PWM enable bit. Set to 1 by user to enable the PWM. Cleared to 0 by user to disable the PWM. Also cleared automatically with PWMTRIP (PWMSTA MMR). |  |  |  |  |

### Table 68. PWMSTA Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| PWMSTA | 0xFFFFFC04 | 0x0000        | R/W    |

PWMSTA reflects the status of the PWM.

Table 69. PWMSTA MMR Bit Descriptions

| Table 65.1 WM5171 WMW Dit Descriptions |            |                                                                                                                                                                              |

|----------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit                                    | Name       | Description                                                                                                                                                                  |

| 15:10                                  |            | Reserved.                                                                                                                                                                    |

| 9                                      | PWMSYNCINT | PWM sync interrupt bit. Writing a 1 to this bit clears this interrupt.                                                                                                       |

| 8                                      | PWMTRIPINT | PWM trip interrupt bit. Writing a 1 to this bit clears this interrupt.                                                                                                       |

| 3                                      | PWMTRIP    | Raw signal from the PWM <sub>TRIP</sub> pin.                                                                                                                                 |

| 2:1                                    |            | Reserved.                                                                                                                                                                    |

| 0                                      | PWMPHASE   | PWM phase bit. Set to 1 by the Micro-Converter when the timer is counting down (first half). Cleared to 0 by the MicroConverter when the timer is counting up (second half). |

### **SPI Registers**

The following MMR registers are used to control the SPI interface: SPISTA, SPIRX, SPITX, SPIDIV, and SPICON.

### **Table 119. SPISTA Register**

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| SPISTA | 0xFFFF0A00 | 0x00          | R      |

SPISTA is an 8-bit read-only status register. Only Bit 1 or Bit 4 of this register generates an interrupt. Bit 6 of the SPICON register determines which bit generates the interrupt.

### **Table 120. SPISTA MMR Bit Descriptions**

|     | - 120, 01 10 111 1111 210 2 000 11P 110 110                                                                                                                           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Description                                                                                                                                                           |

| 7:6 | Reserved.                                                                                                                                                             |

| 5   | SPIRX data register overflow status bit. Set if SPIRX is overflowing. Cleared by reading the SPIRX register.                                                          |

| 4   | SPIRX data register IRQ. Set automatically if Bit 3 or Bit 5 is set. Cleared by reading the SPIRX register.                                                           |

| 3   | SPIRX data register full status bit. Set automatically if a valid data is present in the SPIRX register. Cleared by reading the SPIRX register.                       |

| 2   | SPITX data register underflow status bit. Set automatically if SPITX is underflowing. Cleared by writing in the SPITX register.                                       |

| 1   | SPITX data register IRQ. Set automatically if Bit 0 is clear or Bit 2 is set. Cleared by writing in the SPITX register or if finished transmission disabling the SPI. |

| 0   | SPITX data register empty status bit. Set by writing to SPITX to send data. This bit is set during transmission of data. Cleared when SPITX is empty.                 |

### Table 121. SPIRX Register

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| SPIRX | 0xFFFF0A04 | 0x00          | R      |

SPIRX is an 8-bit, read-only receive register.

### **Table 122. SPITX Register**

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| SPITX | 0xFFFF0A08 | 0x00          | W      |

SPITX is an 8-bit, write-only transmit register.

### Table 123. SPIDIV Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| SPIDIV | 0xFFFF0A0C | 0x1B          | R/W    |

SPIDIV is an 8-bit, serial clock divider register.

#### **Table 124. SPICON Register**

|  | Name   | Address    | Default Value | Access |

|--|--------|------------|---------------|--------|

|  | SPICON | 0xFFFF0A10 | 0x0000        | R/W    |

SPICON is a 16-bit control register.

### **Table 125. SPICON MMR Bit Descriptions**

| Bit   | Description                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:13 | Reserved                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12    | Continuous transfer enable      | Set by user to enable continuous transfer. In master mode, the transfer continues until no valid data is available in the TX register. CS is asserted and remains asserted for the duration of each 8-bit serial transfer until TX is empty. Cleared by user to disable continuous transfer. Each transfer consists of a single 8-bit serial transfer. If valid data exists in the SPITX register, then a new transfer is initiated after a stall period. |

| 11    | Loop back enable                | Set by user to connect MISO to MOSI and test software. Cleared by user to be in normal mode.                                                                                                                                                                                                                                                                                                                                                              |

| 10    | Slave MISO output enable        | Set this bit to disable the output driver on the MISO pin. The MISO pin becomes open drain when this bit is set. Clear this bit for MISO to operate as normal.                                                                                                                                                                                                                                                                                            |

| 9     | Clip select output enable       | Set by user in master mode to disable the chip select output. cleared by user to enable the chip select output.  P1.7 should be configured as CS before SPICON is configured as a master when the chip select output enabled is also selected.                                                                                                                                                                                                            |

| 8     | SPIRX overflow overwrite enable | Set by user, the valid data in the RX register is overwritten by the new serial byte received. Cleared by user, the new serial byte received is discarded.                                                                                                                                                                                                                                                                                                |

| 7     | SPITX underflow mode            | Set by user to transmit 0. Cleared by user to transmit the previous data.                                                                                                                                                                                                                                                                                                                                                                                 |

| 6     | Transfer and interrupt mode     | Set by user to initiate transfer with a write to the SPITX register. Interrupt occurs only when TX is empty. Cleared by user to initiate transfer with a read of the SPIRX register. Interrupt occurs only when RX is full.                                                                                                                                                                                                                               |

| 5     | LSB first transfer enable bit   | Set by user, the LSB is transmitted first. Cleared by user, the MSB is transmitted first.                                                                                                                                                                                                                                                                                                                                                                 |

| 4     | Reserved                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3     | Serial clock polarity mode bit  | Set by user, the serial clock idles high. Cleared by user, the serial clock idles low.                                                                                                                                                                                                                                                                                                                                                                    |

| 2     | Serial clock phase mode bit     | Set by user, the serial clock pulses at the beginning of each serial bit transfer. Cleared by user, the serial clock pulses at the end of each serial bit transfer.                                                                                                                                                                                                                                                                                       |