Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | ARM7®                                                                 |

| Core Size                  | 16/32-Bit                                                             |

| Speed                      | 44MHz                                                                 |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                            |

| Peripherals                | PLA, PWM, PSM, Temp Sensor, WDT                                       |

| Number of I/O              | 40                                                                    |

| Program Memory Size        | 62KB (31K x16)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 32                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 80-LQFP                                                               |

| Supplier Device Package    | 80-LQFP (12x12)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7027bstz62-rl |

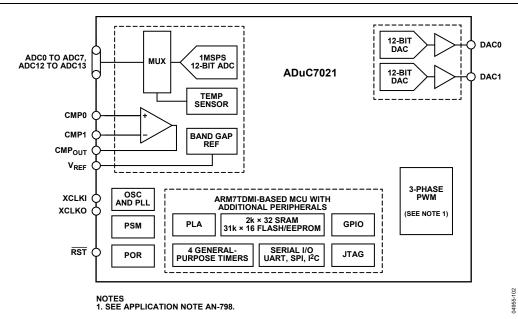

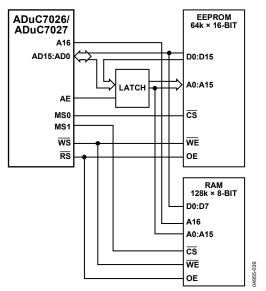

Figure 3.

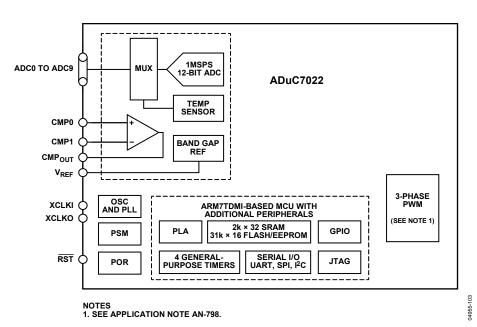

Figure 4.

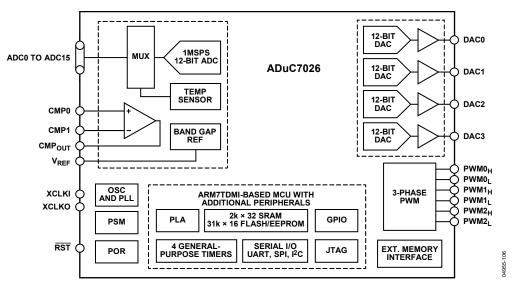

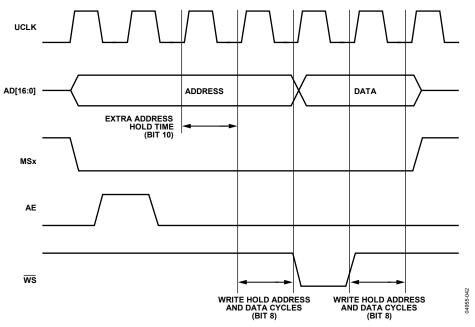

Figure 7.

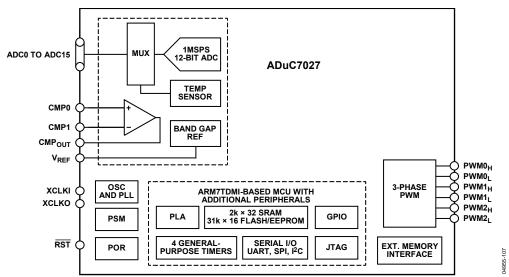

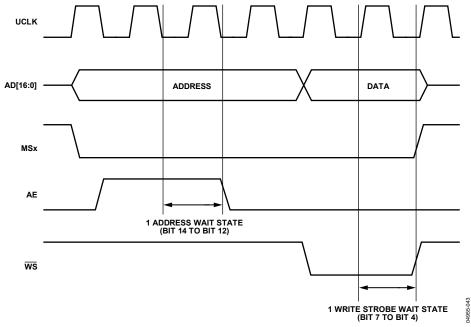

Figure 8.

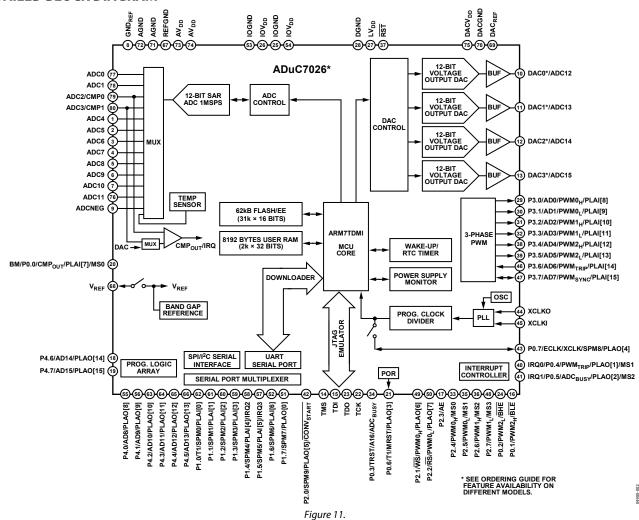

#### **DETAILED BLOCK DIAGRAM**

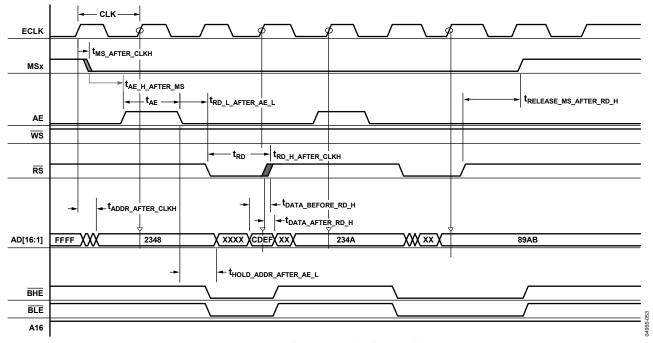

**Table 3. External Memory Read Cycle**

| Parameter                          | Min        | Тур                                                    | Max | Unit |

|------------------------------------|------------|--------------------------------------------------------|-----|------|

| CLK <sup>1</sup>                   | 1/MD clock | ns typ $\times$ (POWCON[2:0] + 1)                      |     |      |

| tms_after_clkh                     | 4          |                                                        | 8   | ns   |

| taddr_after_clkh                   | 4          |                                                        | 16  | ns   |

| tae_h_after_ms                     |            | ½ CLK                                                  |     |      |

| tae                                |            | $(XMxPAR[14:12] + 1) \times CLK$                       |     |      |

| thold_addr_after_ae_l              |            | $\frac{1}{2}$ CLK + (! XMxPAR[10] ) × CLK              |     |      |

| trd_l_after_ae_l                   |            | $\frac{1}{2}$ CLK + (! XMxPAR[10]+ ! XMxPAR[9] ) × CLK |     |      |

| trd_h_after_clkh                   | 0          |                                                        | 4   |      |

| $t_{RD}$                           |            | $(XMxPAR[3:0] + 1) \times CLK$                         |     |      |

| tdata_before_rd_h                  | 16         |                                                        |     | ns   |

| tdata_after_rd_h                   | 8          | $+ (! XMxPAR[9]) \times CLK$                           |     |      |

| t <sub>release_ms_after_rd_h</sub> |            | 1 × CLK                                                |     |      |

<sup>&</sup>lt;sup>1</sup> See Table 78.

Figure 13. External Memory Read Cycle (See Table 78)

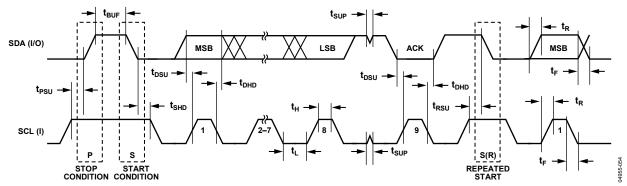

Table 4. I<sup>2</sup>C Timing in Fast Mode (400 kHz)

|                  |                                                              |     | Slave | Master |      |

|------------------|--------------------------------------------------------------|-----|-------|--------|------|

| Parameter        | Description                                                  | Min | Max   | Тур    | Unit |

| t <sub>L</sub>   | SCL low pulse width <sup>1</sup>                             | 200 |       | 1360   | ns   |

| t <sub>H</sub>   | SCL high pulse width <sup>1</sup>                            | 100 |       | 1140   | ns   |

| $t_{SHD}$        | Start condition hold time                                    | 300 |       |        | ns   |

| t <sub>DSU</sub> | Data setup time                                              | 100 |       | 740    | ns   |

| $t_{DHD}$        | Data hold time                                               | 0   |       | 400    | ns   |

| t <sub>RSU</sub> | Setup time for repeated start                                | 100 |       |        | ns   |

| t <sub>PSU</sub> | Stop condition setup time                                    | 100 |       | 400    | ns   |

| t <sub>BUF</sub> | Bus-free time between a stop condition and a start condition | 1.3 |       |        | μs   |

| $t_R$            | Rise time for both SCL and SDA                               |     | 300   | 200    | ns   |

| $t_{F}$          | Fall time for both SCL and SDA                               |     | 300   |        | ns   |

| $t_{SUP}$        | Pulse width of spike suppressed                              |     | 50    |        | ns   |

$<sup>^{1}</sup>$  t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCON MMR. t<sub>HCLK</sub> = t<sub>UCLK</sub>/ $2^{\text{CD}}$ ; see Figure 67.

Table 5. I<sup>2</sup>C Timing in Standard Mode (100 kHz)

|                  |                                                              | S   | lave | Master |      |

|------------------|--------------------------------------------------------------|-----|------|--------|------|

| Parameter        | Description                                                  | Min | Max  | Тур    | Unit |

| t∟               | SCL low pulse width <sup>1</sup>                             | 4.7 |      |        | μs   |

| t <sub>H</sub>   | SCL high pulse width <sup>1</sup>                            | 4.0 |      |        | ns   |

| t <sub>SHD</sub> | Start condition hold time                                    | 4.0 |      |        | μs   |

| $t_{DSU}$        | Data setup time                                              | 250 |      |        | ns   |

| t <sub>DHD</sub> | Data hold time                                               | 0   | 3.45 |        | μs   |

| t <sub>RSU</sub> | Setup time for repeated start                                | 4.7 |      |        | μs   |

| t <sub>PSU</sub> | Stop condition setup time                                    | 4.0 |      |        | μs   |

| $t_{BUF}$        | Bus-free time between a stop condition and a start condition | 4.7 |      |        | μs   |

| t <sub>R</sub>   | Rise time for both SCL and SDA                               |     | 1    |        | μs   |

| $t_{F}$          | Fall time for both SCL and SDA                               |     | 300  |        | ns   |

$<sup>^{1}</sup>$  t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCON MMR. t<sub>HCLK</sub> = t<sub>UCLK</sub>/ $2^{CD}$ ; see Figure 67.

Figure 14. I<sup>2</sup>C Compatible Interface Timing

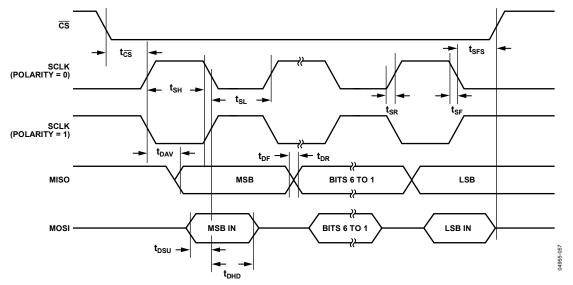

**Table 8. SPI Slave Mode Timing (Phsae Mode = 1)**

| Parameter        | Description                                         | Min                                         | Тур                            | Max  | Unit |

|------------------|-----------------------------------------------------|---------------------------------------------|--------------------------------|------|------|

| t <sub>cs</sub>  | CS to SCLK edge <sup>1</sup>                        | $(2 \times t_{HCLK}) + (2 \times t_{UCLK})$ |                                |      | ns   |

| $t_{SL}$         | SCLK low pulse width <sup>2</sup>                   |                                             | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>SH</sub>  | SCLK high pulse width <sup>2</sup>                  |                                             | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| $t_{DAV}$        | Data output valid after SCLK edge                   |                                             |                                | 25   | ns   |

| t <sub>DSU</sub> | Data input setup time before SCLK edge <sup>1</sup> | 1 × tuclk                                   |                                |      | ns   |

| $t_{DHD}$        | Data input hold time after SCLK edge <sup>1</sup>   | $2 \times t_{UCLK}$                         |                                |      | ns   |

| t <sub>DF</sub>  | Data output fall time                               |                                             | 5                              | 12.5 | ns   |

| $t_{DR}$         | Data output rise time                               |                                             | 5                              | 12.5 | ns   |

| t <sub>SR</sub>  | SCLK rise time                                      |                                             | 5                              | 12.5 | ns   |

| $t_{SF}$         | SCLK fall time                                      |                                             | 5                              | 12.5 | ns   |

| t <sub>SFS</sub> | CS high after SCLK edge                             | 0                                           |                                |      | ns   |

$<sup>^{1}</sup>$  t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider; see Figure 67.  $^{2}$  t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCONMMR. t<sub>HCLK</sub> = t<sub>UCLK</sub>/2<sup>CD</sup>; see Figure 67.

Figure 17. SPI Slave Mode Timing (Phase Mode = 1)

## **ABSOLUTE MAXIMUM RATINGS**

$AGND = REFGND = DACGND = GND_{REF}, T_A = 25 ^{\circ}C, unless otherwise noted.$

Table 10.

| Table 10.                                            |                                                                    |  |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|

| Parameter                                            | Rating                                                             |  |  |  |  |  |

| AV <sub>DD</sub> to IOV <sub>DD</sub>                | -0.3 V to +0.3 V                                                   |  |  |  |  |  |

| AGND to DGND                                         | −0.3 V to +0.3 V                                                   |  |  |  |  |  |

| IOV <sub>DD</sub> to IOGND, AV <sub>DD</sub> to AGND | −0.3 V to +6 V                                                     |  |  |  |  |  |

| Digital Input Voltage to IOGND                       | −0.3 V to +5.3 V                                                   |  |  |  |  |  |

| Digital Output Voltage to IOGND                      | $-0.3 \mathrm{V}$ to $\mathrm{IOV}_{\mathrm{DD}} + 0.3 \mathrm{V}$ |  |  |  |  |  |

| V <sub>REF</sub> to AGND                             | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                        |  |  |  |  |  |

| Analog Inputs to AGND                                | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                        |  |  |  |  |  |

| Analog Outputs to AGND                               | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                        |  |  |  |  |  |

| Operating Temperature Range, Industrial              | -40°C to +125°C                                                    |  |  |  |  |  |

| Storage Temperature Range                            | −65°C to +150°C                                                    |  |  |  |  |  |

| Junction Temperature                                 | 150°C                                                              |  |  |  |  |  |

| $\theta_{JA}$ Thermal Impedance                      |                                                                    |  |  |  |  |  |

| 40-Lead LFCSP                                        | 26°C/W                                                             |  |  |  |  |  |

| 49-Ball CSP_BGA                                      | 80°C/W                                                             |  |  |  |  |  |

| 64-Lead LFCSP                                        | 24°C/W                                                             |  |  |  |  |  |

| 64-Ball CSP_BGA                                      | 75°C/W                                                             |  |  |  |  |  |

| 64-Lead LQFP                                         | 47°C/W                                                             |  |  |  |  |  |

| 80-Lead LQFP                                         | 38°C/W                                                             |  |  |  |  |  |

| Peak Solder Reflow Temperature                       |                                                                    |  |  |  |  |  |

| SnPb Assemblies (10 sec to 30 sec)                   | 240°C                                                              |  |  |  |  |  |

| RoHS Compliant Assemblies                            | 260°C                                                              |  |  |  |  |  |

| (20 sec to 40 sec)                                   |                                                                    |  |  |  |  |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## NONVOLATILE FLASH/EE MEMORY

The ADuC7019/20/21/22/24/25/26/27/28/29 incorporate Flash/EE memory technology on-chip to provide the user with nonvolatile, in-circuit reprogrammable memory space.

Like EEPROM, flash memory can be programmed in-system at a byte level, although it must first be erased. The erase is performed in page blocks. As a result, flash memory is often and more correctly referred to as Flash/EE memory.

Overall, Flash/EE memory represents a step closer to the ideal memory device that includes nonvolatility, in-circuit programmability, high density, and low cost. Incorporated in the ADuC7019/20/21/22/24/25/26/27/28/29, Flash/EE memory technology allows the user to update program code space incircuit, without the need to replace one-time programmable (OTP) devices at remote operating nodes.

Each part contains a 64 kB array of Flash/EE memory. The lower 62 kB is available to the user and the upper 2 kB contain permanently embedded firmware, allowing in-circuit serial download. These 2 kB of embedded firmware also contain a power-on configuration routine that downloads factory-calibrated coefficients to the various calibrated peripherals (such as ADC, temperature sensor, and band gap references). This 2 kB embedded firmware is hidden from user code.

### Flash/EE Memory Reliability

The Flash/EE memory arrays on the parts are fully qualified for two key Flash/EE memory characteristics: Flash/EE memory cycling endurance and Flash/EE memory data retention.

Endurance quantifies the ability of the Flash/EE memory to be cycled through many program, read, and erase cycles. A single endurance cycle is composed of four independent, sequential events, defined as

- 1. Initial page erase sequence

- 2. Read/verify sequence (single Flash/EE)

- 3. Byte program sequence memory

- 4. Second read/verify sequence (endurance cycle)

In reliability qualification, every half word (16-bit wide) location of the three pages (top, middle, and bottom) in the Flash/EE memory is cycled 10,000 times from 0x0000 to 0xFFFF. As indicated in Table 1, the Flash/EE memory endurance qualification is carried out in accordance with JEDEC Retention Lifetime Specification A117 over the industrial temperature range of  $-40^{\circ}$  to  $+125^{\circ}$ C. The results allow the specification of a minimum endurance figure over a supply temperature of 10,000 cycles.

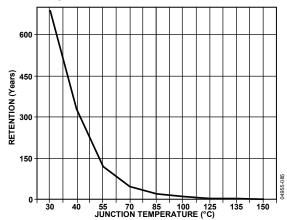

Retention quantifies the ability of the Flash/EE memory to retain its programmed data over time. Again, the parts are qualified in accordance with the formal JEDEC Retention Lifetime Specification (A117) at a specific junction temperature ( $T_J = 85^{\circ}$ C). As part of this qualification procedure, the Flash/EE memory is cycled to its specified endurance limit, described in Table 1, before data retention is characterized. This means that the Flash/EE memory is guaranteed to retain its data for its fully specified retention lifetime every time the Flash/EE memory is reprogrammed. In addition, note that retention lifetime, based on an activation energy of 0.6 eV, derates with  $T_J$  as shown in Figure 61.

Figure 61. Flash/EE Memory Data Retention

#### **PROGRAMMING**

The 62 kB of Flash/EE memory can be programmed in-circuit, using the serial download mode or the provided JTAG mode.

#### Serial Downloading (In-Circuit Programming)

The ADuC7019/20/21/22/24/25/26/27/28/29 facilitate code download via the standard UART serial port or via the I²C port. The parts enter serial download mode after a reset or power cycle if the BM pin is pulled low through an external 1 k $\Omega$  resistor. After a part is in serial download mode, the user can download code to the full 62 kB of Flash/EE memory while the device is in-circuit in its target application hardware. An executable PC serial download is provided as part of the development system for serial downloading via the UART. The AN-806 Application Note describes the protocol for serial downloading via the I²C.

#### JTAG Access

The JTAG protocol uses the on-chip JTAG interface to facilitate code download and debug.

#### Example source code

```

t2val_old= T2VAL;

T2LD = 5;

TCON = 0x480;

while ((T2VAL == t2val_old) || (T2VAL >

3)) //ensures timer value loaded

IRQEN = 0x10;

//enable T2 interrupt

PLLKEY1 = 0xAA;

PLLCON = 0x01;

PLLKEY2 = 0x55;

POWKEY1 = 0x01;

POWCON = 0x27;

// Set Core into Nap mode

POWKEY2 = 0xF4;

```

In noisy environments, noise can couple to the external crystal pins, and PLL may lose lock momentarily. A PLL interrupt is provided in the interrupt controller. The core clock is immediately halted, and this interrupt is only serviced when the lock is restored.

In case of crystal loss, the watchdog timer should be used. During initialization, a test on the RSTSTA register can determine if the reset came from the watchdog timer.

#### **External Clock Selection**

To switch to an external clock on P0.7, configure P0.7 in Mode 1. The external clock can be up to 44 MHz, providing the tolerance is 1%.

Table 57. Operating Modes<sup>1</sup>

```

t2val_old= T2VAL;

T2LD = 5;

TCON = 0x480;

while ((T2VAL == t2val_old) || (T2VAL

> 3)) //ensures timer value loaded

IRQEN = 0x10;

//enable T2 interrupt

PLLKEY1 = 0xAA;

PLLCON = 0x03; //Select external clock

PLLKEY2 = 0x55;

POWKEY1 = 0x01;

POWCON = 0x27;

// Set Core into Nap mode

POWKEY2 = 0xF4;

```

#### **Power Control System**

A choice of operating modes is available on the ADuC7019/20/21/22/24/25/26/27/28/29. Table 57 describes what part is powered on in the different modes and indicates the power-up time.

Table 58 gives some typical values of the total current consumption (analog + digital supply currents) in the different modes, depending on the clock divider bits. The ADC is turned off. Note that these values also include current consumption of the regulator and other parts on the test board where these values are measured.

| Table 37. Operating Modes |      |             |     |            |              |                                      |   |

|---------------------------|------|-------------|-----|------------|--------------|--------------------------------------|---|

| Mode                      | Core | Peripherals | PLL | XTAL/T2/T3 | IRQ0 to IRQ3 | Start-Up/Power-On Time               | _ |

| Active                    | Х    | Х           | Х   | Х          | Х            | 130 ms at CD = 0                     | _ |

| Pause                     |      | X           | X   | X          | Х            | 24 ns at CD = 0; 3 $\mu$ s at CD = 7 |   |

| Nap                       |      |             | Х   | Х          | Х            | 24 ns at CD = 0; 3 $\mu$ s at CD = 7 |   |

| Sleep                     |      |             |     | Х          | Х            | 1.58 ms                              |   |

| Stop                      |      |             |     |            | Χ            | 1.7 ms                               |   |

<sup>&</sup>lt;sup>1</sup> X indicates that the part is powered on.

Table 58. Typical Current Consumption at 25°C in Milliamperes

| 7.1     |        |        |        |        |        |        |        |        |        |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| PC[2:0] | Mode   | CD = 0 | CD = 1 | CD = 2 | CD = 3 | CD = 4 | CD = 5 | CD = 6 | CD = 7 |

| 000     | Active | 33.1   | 21.2   | 13.8   | 10     | 8.1    | 7.2    | 6.7    | 6.45   |

| 001     | Pause  | 22.7   | 13.3   | 8.5    | 6.1    | 4.9    | 4.3    | 4      | 3.85   |

| 010     | Nap    | 3.8    | 3.8    | 3.8    | 3.8    | 3.8    | 3.8    | 3.8    | 3.8    |

| 011     | Sleep  | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    |

| 100     | Stop   | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    | 0.4    |

#### **Output Control Unit**

The operation of the output control unit is controlled by the 9-bit read/write PWMEN register. This register controls two distinct features of the output control unit that are directly useful in the control of electronic counter measures (ECM) or binary decimal counter measures (BDCM). The PWMEN register contains three crossover bits, one for each pair of PWM outputs. Setting Bit 8 of the PWMEN register enables the crossover mode for the 0H/0L pair of PWM signals, setting Bit 7 enables crossover on the 1H/1L pair of PWM signals, and setting Bit 6 enables crossover on the 2H/2L pair of PWM signals. If crossover mode is enabled for any pair of PWM signals, the high-side PWM signal from the timing unit (0H, for example) is diverted to the associated low-side output of the output control unit so that the signal ultimately appears at the PWM0<sub>L</sub> pin. Of course, the corresponding low-side output of the timing unit is also diverted to the complementary high-side output of the output control unit so that the signal appears at the PWM0<sub>H</sub> pin. Following a reset, the three crossover bits are cleared, and the crossover mode is disabled on all three pairs of PWM signals. The PWMEN register also contains six bits (Bit 0 to Bit 5) that can be used to individually enable or disable each of the six PWM outputs. If the associated bit of the PWMEN register is set, the corresponding PWM output is disabled regardless of the corresponding value of the duty cycle register. This PWM output signal remains in the off state as long as the corresponding enable/disable bit of the PWMEN register is set. The implementation of this output enable function is implemented after the crossover function.

Following a reset, all six enable bits of the PWMEN register are cleared, and all PWM outputs are enabled by default. In a manner identical to the duty cycle registers, the PWMEN is latched on the rising edge of the PWMSYNC signal. As a result, changes to this register become effective only at the start of each PWM cycle in single update mode. In double update mode, the PWMEN register can also be updated at the midpoint of the PWM cycle.

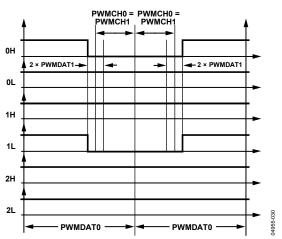

In the control of an ECM, only two inverter legs are switched at any time, and often the high-side device in one leg must be switched on at the same time as the low-side driver in a second leg. Therefore, by programming identical duty cycle values for two PWM channels (for example, PWMCH0 = PWMCH1) and setting Bit 7 of the PWMEN register to cross over the 1H/1L pair of PWM signals, it is possible to turn on the high-side switch of Phase A and the low-side switch of Phase B at the same time. In the control of ECM, it is usual for the third inverter leg (Phase C in this example) to be disabled for a number of PWM cycles. This function is implemented by disabling both the 2H and 2L PWM outputs by setting Bit 0 and Bit 1 of the PWMEN register.

This situation is illustrated in Figure 71, where it can be seen that both the 0H and 1L signals are identical because PWMCH0 = PWMCH1 and the crossover bit for Phase B is set.

Figure 71. Active Low PWM Signals Suitable for ECM Control, PWMCH0 = PWMCH1, Crossover 1H/1L Pair and Disable 0L, 1H, 2H, and 2L Outputs in Single Update Mode.

In addition, the other four signals (0L, 1H, 2H, and 2L) have been disabled by setting the appropriate enable/disable bits of the PWMEN register. In Figure 71, the appropriate value for the PWMEN register is 0x00A7. In normal ECM operation, each inverter leg is disabled for certain periods of time to change the PWMEN register based on the position of the rotor shaft (motor commutation).

#### **Gate Drive Unit**

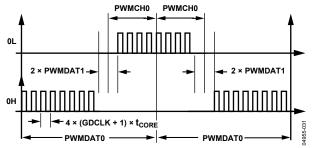

The gate drive unit of the PWM controller adds features that simplify the design of isolated gate-drive circuits for PWM inverters. If a transformer-coupled, power device, gate-drive amplifier is used, the active PWM signal must be chopped at a high frequency. The 16-bit read/write PWMCFG register programs this high frequency chopping mode. The chopped active PWM signals can be required for the high-side drivers only, the low-side drivers only, or both the high-side and low-side switches. Therefore, independent control of this mode for both high-side and low-side switches is included with two separate control bits in the PWMCFG register.

Typical PWM output signals with high frequency chopping enabled on both high-side and low-side signals are shown in Figure 72. Chopping of the high-side PWM outputs (0H, 1H, and 2H) is enabled by setting Bit 8 of the PWMCFG register. Chopping of the low-side PWM outputs (0L, 1L, and 2L) is enabled by setting Bit 9 of the PWMCFG register. The high chopping frequency is controlled by the 8-bit word (GDCLK) placed in Bit 0 to Bit 7 of the PWMCFG register. The period of this high frequency carrier is

$$t_{CHOP} = (4 \times (GDCLK + 1)) \times t_{CORE}$$

The chopping frequency is, therefore, an integral subdivision of the MicroConverter core frequency

$$f_{CHOP} = f_{CORE}/(4 \times (GDCLK + 1))$$

The GDCLK value can range from 0 to 255, corresponding to a programmable chopping frequency rate of 40.8 kHz to 10.44 MHz for a 41.78 MHz core frequency. The gate drive features must be programmed before operation of the PWM controller and are typically not changed during normal operation of the PWM controller. Following a reset, all bits of the PWMCFG register are cleared so that high frequency chopping is disabled, by default.

Figure 72. Typical PWM Signals with High Frequency Gate Chopping Enabled on Both High-Side and Low-Side Switches

#### **PWM Shutdown**

In the event of external fault conditions, it is essential that the PWM system be instantaneously shut down in a safe fashion. A low level on the PWM $_{\text{TRIP}}$  pin provides an instantaneous, asynchronous (independent of the MicroConverter core clock) shutdown of the PWM controller. All six PWM outputs are placed in the off state, that is, in low state. In addition, the PWMSYNC pulse is disabled. The PWM $_{\text{TRIP}}$  pin has an internal pull-down resistor to disable the PWM if the pin becomes disconnected. The state of the PWM $_{\text{TRIP}}$  pin can be read from Bit 3 of the PWMSTA register.

If a PWM shutdown command occurs, a PWMTRIP interrupt is generated, and internal timing of the 3-phase timing unit of the PWM controller is stopped. Following a PWM shutdown, the PWM can be reenabled (in a PWMTRIP interrupt service routine, for example) only by writing to all of the PWMDATO, PWMCHO, PWMCH1, and PWMCH2 registers. Provided that the external fault is cleared and the PWMTRIP is returned to a high level, the internal timing of the 3-phase timing unit resumes, and new duty-cycle values are latched on the next PWMSYNC boundary.

Note that the PWMTRIP interrupt is available in IRQ only, and the PWMSYNC interrupt is available in FIQ only. Both interrupts share the same bit in the interrupt controller. Therefore, only one of the interrupts can be used at a time. See the Interrupt System section for further details.

#### **PWM MMRs Interface**

The PWM block is controlled via the MMRs described in this section.

Table 66. PWMCON Register

| Name   | Address    | Default Value | Access |  |

|--------|------------|---------------|--------|--|

| PWMCON | 0xFFFFFC00 | 0x0000        | R/W    |  |

PWMCON is a control register that enables the PWM and chooses the update rate.

Table 67. PWMCON MMR Bit Descriptions

| -   | Tuble 07:1 WWGOW WINK Bit Descriptions |                                                                                                                                                    |  |  |  |  |

|-----|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit | Name                                   | Description                                                                                                                                        |  |  |  |  |

| 7:5 |                                        | Reserved.                                                                                                                                          |  |  |  |  |

| 4   | PWM_SYNCSEL                            | External sync select. Set to use external sync. Cleared to use internal sync.                                                                      |  |  |  |  |

| 3   | PWM_EXTSYNC                            | External sync select. Set to select external synchronous sync signal. Cleared for asynchronous sync signal.                                        |  |  |  |  |

| 2   | PWMDBL                                 | Double update mode. Set to 1 by user to enable double update mode. Cleared to 0 by the user to enable single update mode.                          |  |  |  |  |

| 1   | PWM_SYNC_EN                            | PWM synchronization enable. Set by user to enable synchronization. Cleared by user to disable synchronization.                                     |  |  |  |  |

| 0   | PWMEN                                  | PWM enable bit. Set to 1 by user to enable the PWM. Cleared to 0 by user to disable the PWM. Also cleared automatically with PWMTRIP (PWMSTA MMR). |  |  |  |  |

#### Table 68. PWMSTA Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| PWMSTA | 0xFFFFFC04 | 0x0000        | R/W    |

PWMSTA reflects the status of the PWM.

Table 69. PWMSTA MMR Bit Descriptions

| 1 4010 0 | Tuble 07.1 W WOTH WHITE Bit Descriptions |                                                                                                                                                                              |  |  |

|----------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit      | Name                                     | Description                                                                                                                                                                  |  |  |

| 15:10    |                                          | Reserved.                                                                                                                                                                    |  |  |

| 9        | PWMSYNCINT                               | PWM sync interrupt bit. Writing a 1 to this bit clears this interrupt.                                                                                                       |  |  |

| 8        | PWMTRIPINT                               | PWM trip interrupt bit. Writing a 1 to this bit clears this interrupt.                                                                                                       |  |  |

| 3        | PWMTRIP                                  | Raw signal from the PWM <sub>TRIP</sub> pin.                                                                                                                                 |  |  |

| 2:1      |                                          | Reserved.                                                                                                                                                                    |  |  |

| 0        | PWMPHASE                                 | PWM phase bit. Set to 1 by the Micro-Converter when the timer is counting down (first half). Cleared to 0 by the MicroConverter when the timer is counting up (second half). |  |  |

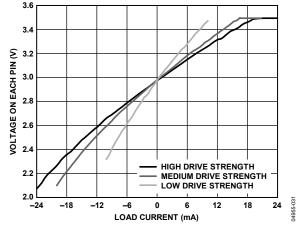

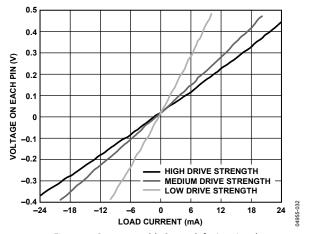

**Table 83. GPIO Drive Strength Control Bits Descriptions**

| <b>Control Bits Value</b> | Description            |

|---------------------------|------------------------|

| 00                        | Medium drive strength. |

| 01                        | Low drive strength.    |

| 1x                        | High drive strength.   |

Figure 73. Programmable Strength for High Level (Typical Values)

Figure 74. Programmable Strength for Low Level (Typical Values)

The drive strength bits can be written to one time only after reset. More writing to related bits has no effect on changing drive strength. The GPIO drive strength and pull-up disable is not always adjustable for the GPIO port. Some control bits cannot be changed (see Table 84).

**Table 84. GPxPAR Control Bits Access Descriptions**

| Bit      | GP0PAR   | GP1PAR   |

|----------|----------|----------|

| 31       | Reserved | Reserved |

| 30 to 29 | R/W      | R/W      |

| 28       | R/W      | R/W      |

| 27       | Reserved | Reserved |

| 26 to 25 | R/W      | R/W      |

| 24       | R/W      | R/W      |

| 23       | Reserved | Reserved |

| 22 to 21 | R/W      | R (b00)  |

| 20       | R/W      | R/W      |

| 19       | Reserved | Reserved |

| 18 to 17 | R (b00)  | R (b00)  |

| 16       | R/W      | R/W      |

| 15       | Reserved | Reserved |

| 14 to 13 | R (b00)  | R (b00)  |

| 12       | R/W      | R/W      |

| 11       | Reserved | Reserved |

| 10 to 9  | R (b00)  | R (b00)  |

| 8        | R/W      | R/W      |

| 7        | Reserved | Reserved |

| 6 to 5   | R (b00)  | R (b00)  |

| 4        | R/W      | R/W      |

| 3        | Reserved | Reserved |

| 2 to 1   | R (b00)  | R (b00)  |

| 0        | R/W      | R/W      |

Table 99. COMDIV1 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| COMDIV1 | 0xFFFF0704 | 0x00          | R/W    |

COMDIV1 is a divisor latch (high byte) register.

### Table 100. COMIID0 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| COMIID0 | 0xFFFF0708 | 0x01          | R      |

COMIID0 is the interrupt identification register.

Table 101. COMIID0 MMR Bit Descriptions

| Table 101. (           | Table 101. COMIIDO MMR Bit Descriptions |             |                                          |                                              |

|------------------------|-----------------------------------------|-------------|------------------------------------------|----------------------------------------------|

| Bit 2:1<br>Status Bits | Bit 0<br>NINT                           | Priority    | Definition                               | Clearing<br>Operation                        |

| 00                     | 1                                       | N/A         | No interrupt                             | N/A                                          |

| 11                     | 0                                       | 1 (Highest) | Receive line status interrupt            | Read<br>COMSTA0                              |

| 10                     | 0                                       | 2           | Receive<br>buffer full<br>interrupt      | Read<br>COMRX                                |

| 01                     | 0                                       | 3           | Transmit<br>buffer<br>empty<br>interrupt | Write data to<br>COMTX or<br>read<br>COMIID0 |

| 00                     | 0                                       | 4 (Lowest)  | Modem<br>status<br>interrupt             | Read<br>COMSTA1                              |

### Table 102. COMCON0 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| COMCON0 | 0xFFFF070C | 0x00          | R/W    |

COMCON0 is the line control register.

Table 103. COMCON0 MMR Bit Descriptions

| Bit | Name | Description                                                                                                                                                                                                                                                                                                            |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DLAB | Divisor latch access. Set by user to enable access to the COMDIVO and COMDIV1 registers. Cleared by user to disable access to COMDIV0 and COMDIV1 and enable access to COMRX and COMTX.                                                                                                                                |

| 6   | BRK  | Set break. Set by user to force SOUT to 0. Cleared to operate in normal mode.                                                                                                                                                                                                                                          |

| 5   | SP   | Stick parity. Set by user to force parity to defined values: 1 if EPS = 1 and PEN = 1, 0 if EPS = 0 and PEN = 1.                                                                                                                                                                                                       |

| 4   | EPS  | Even parity select bit. Set for even parity. Cleared for odd parity.                                                                                                                                                                                                                                                   |

| 3   | PEN  | Parity enable bit. Set by user to transmit and check the parity bit. Cleared by user for no parity transmission or checking.                                                                                                                                                                                           |

| 2   | STOP | Stop bit. Set by user to transmit 1.5 stop bits if the word length is five bits or 2 stop bits if the word length is six bits, seven bits, or eight bits. The receiver checks the first stop bit only, regardless of the number of stop bits selected. Cleared by user to generate 1 stop bit in the transmitted data. |

| 1:0 | WLS  | Word length select:<br>00 = five bits, 01 = six bits, 10 = seven bits,<br>11 = eight bits.                                                                                                                                                                                                                             |

## Table 104. COMCON1 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| COMCON1 | 0xFFFF0710 | 0x00          | R/W    |

COMCON1 is the modem control register.

### Table 105. COMCON1 MMR Bit Descriptions

|   | Bit | Name     | Description                                                                                                                                                                                                                                                                                                             |

|---|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 7:5 |          | Reserved.                                                                                                                                                                                                                                                                                                               |

|   | 4   | LOOPBACK | Loopback. Set by user to enable loopback mode. In loopback mode, SOUT (see Table 78) is forced high. The modem signals are also directly connected to the status inputs (RTS to CTS and DTR to DSR). Cleared by user to be in normal mode.                                                                              |

|   | 3   | PEN      | Parity enable bit. Set by user to transmit and check the parity bit. Cleared by user for no parity transmission or checking.                                                                                                                                                                                            |

|   | 2   | STOP     | Stop bit. Set by user to transmit 1.5 stop bits if the word length is five bits, or 2 stop bits if the word length is six bits, seven bits, or eight bits. The receiver checks the first stop bit only, regardless of the number of stop bits selected. Cleared by user to generate 1 stop bit in the transmitted data. |

|   | 1   | RTS      | Request to send. Set by user to force the RTS output to 0. Cleared by user to force the RTS output to 1.                                                                                                                                                                                                                |

| = | 0   | DTR      | Data terminal ready. Set by user to force the DTR output to 0. Cleared by user to force the DTR output to 1.                                                                                                                                                                                                            |

### Table 106. COMSTA0 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| COMSTA0 | 0xFFFF0714 | 0x60          | R      |

COMSTA0 is the line status register.

Table 107. COMSTA0 MMR Bit Descriptions

| Bit | Name | Description                                                                                                                                      |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   |      | Reserved.                                                                                                                                        |

| 6   | TEMT | COMTX and shift register empty status bit. Set automatically if COMTX and shift register are empty. Cleared automatically when writing to COMTX. |

| 5   | THRE | COMTX empty. Set automatically if COMTX is empty. Cleared automatically when writing to COMTX.                                                   |

| 4   | BI   | Break error. Set when SIN is held low for more than the maximum word length. Cleared automatically.                                              |

| 3   | FE   | Framing error. Set when an invalid stop bit occurs. Cleared automatically.                                                                       |

| 2   | PE   | Parity error. Set when a parity error occurs.<br>Cleared automatically.                                                                          |

| 1   | OE   | Overrun error. Set automatically if data is overwritten before being read. Cleared automatically.                                                |

| 0   | DR   | Data ready. Set automatically when COMRX is full.<br>Cleared by reading COMRX.                                                                   |

Table 108. COMSTA1 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| COMSTA1 | 0xFFFF0718 | 0x00          | R      |

COMSTA1 is a modem status register.

Table 109. COMSTA1 MMR Bit Descriptions

| 1 40 | Table 107. COMOTAT MINIK Bit Descriptions |                                                                                                                          |  |  |  |

|------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit  | Name                                      | Description                                                                                                              |  |  |  |

| 7    | DCD                                       | Data carrier detect.                                                                                                     |  |  |  |

| 6    | RI                                        | Ring indicator.                                                                                                          |  |  |  |

| 5    | DSR                                       | Data set ready.                                                                                                          |  |  |  |

| 4    | CTS                                       | Clear to send.                                                                                                           |  |  |  |

| 3    | DDCD                                      | Delta DCD. Set automatically if DCD changed state since last COMSTA1 read. Cleared automatically by reading COMSTA1.     |  |  |  |

| 2    | TERI                                      | Trailing edge RI. Set if RI changed from 0 to 1 since COMSTA1 was last read. Cleared automatically by reading COMSTA1.   |  |  |  |

| 1    | DDSR                                      | Delta DSR. Set automatically if DSR changed state since COMSTA1 was last read. Cleared automatically by reading COMSTA1. |  |  |  |

| 0    | DCTS                                      | Delta CTS. Set automatically if CTS changed state since COMSTA1 was last read. Cleared automatically by reading COMSTA1. |  |  |  |

Table 110. COMSCR Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| COMSCR | 0xFFFF071C | 0x00          | R/W    |

COMSCR is an 8-bit scratch register used for temporary storage. It is also used in network addressable UART mode.

Table 111. COMDIV2 Register

|         | 8          |               |        |  |  |  |

|---------|------------|---------------|--------|--|--|--|

| Name    | Address    | Default Value | Access |  |  |  |

| COMDIV2 | 0xFFFF072C | 0x0000        | R/W    |  |  |  |

COMDIV2 is a 16-bit fractional baud divide register.

Table 112. COMDIV2 MMR Bit Descriptions

| I abic I | Table 112. COMDIV2 MINIK Bit Descriptions |                                                                                                                                                                        |  |  |  |

|----------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit      | Name                                      | Description                                                                                                                                                            |  |  |  |

| 15       | FBEN                                      | Fractional baud rate generator enable bit. Set by user to enable the fractional baud rate generator. Cleared by user to generate baud rate using the standard 450 UART |  |  |  |

|          |                                           | baud rate generator.                                                                                                                                                   |  |  |  |

| 14:13    |                                           | Reserved.                                                                                                                                                              |  |  |  |

| 12:11    | FBM[1:0]                                  | M if FBM = $0$ , M = $4$ (see the Fractional Divider section).                                                                                                         |  |  |  |

| 10:0     | FBN[10:0]                                 | N (see the Fractional Divider section).                                                                                                                                |  |  |  |

#### **Network Addressable UART Mode**

This mode connects the MicroConverter to a 256-node serial network, either as a hardware single master or via software in a multimaster network. Bit 7 (ENAM) of the COMIEN1 register must be set to enable UART in network addressable mode (see Table 114). Note that there is no parity check in this mode.

#### **Network Addressable UART Register Definitions**

Four additional registers, COMIEN0, COMIEN1, COMIID1, and COMADR are used in network addressable UART mode only.

In network address mode, the least significant bit of the COMIEN1 register is the transmitted network address control bit. If set to 1, the device is transmitting an address. If cleared to 0, the device is transmitting data. For example, the following master-based code transmits the slave's address followed by the data:

#### Table 113. COMIEN1 Register

| • | Name    | Address    | Default Value | Access |

|---|---------|------------|---------------|--------|

|   | COMIEN1 | 0xFFFF0720 | 0x04          | R/W    |

COMIEN1 is an 8-bit network enable register.

**Table 114. COMIEN1 MMR Bit Descriptions**

| 1 40 | Table 114. COMILINI MIMIK Dit Descriptions |                                                                                                                                                         |  |  |  |

|------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit  | Name                                       | Description                                                                                                                                             |  |  |  |

| 7    | ENAM                                       | Network address mode enable bit. Set by user to enable network address mode. Cleared by user to disable network address mode.                           |  |  |  |

| 6    | E9BT                                       | 9-bit transmit enable bit. Set by user to enable<br>9-bit transmit. ENAM must be set. Cleared by user<br>to disable 9-bit transmit.                     |  |  |  |

| 5    | E9BR                                       | 9-bit receive enable bit. Set by user to enable<br>9-bit receive. ENAM must be set. Cleared by user<br>to disable 9-bit receive.                        |  |  |  |

| 4    | ENI                                        | Network interrupt enable bit.                                                                                                                           |  |  |  |

| 3    | E9BD                                       | Word length. Set for 9-bit data. E9BT has to be cleared. Cleared for 8-bit data.                                                                        |  |  |  |

| 2    | ETD                                        | Transmitter pin driver enable bit. Set by user to enable SOUT pin as an output in slave mode or multimaster mode. Cleared by user; SOUT is three-state. |  |  |  |

| 1    | NABP                                       | Network address bit. Interrupt polarity bit.                                                                                                            |  |  |  |

| 0    | NAB                                        | Network address bit (if NABP = 1). Set by user to transmit the slave address. Cleared by user to transmit data.                                         |  |  |  |

#### Table 115. COMIID1 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| COMIID1 | 0xFFFF0724 | 0x01          | R      |

COMIID1 is an 8-bit network interrupt register. Bit 7 to Bit 4 are reserved (see Table 116).

Table 116. COMIID1 MMR Bit Descriptions

| Bit 3:1<br>Status<br>Bits | Bit 0<br>NINT | Priority | Definition                              | Clearing<br>Operation                     |

|---------------------------|---------------|----------|-----------------------------------------|-------------------------------------------|

| 000                       | 1             |          | No interrupt                            |                                           |

| 110                       | 0             | 2        | Matching network address                | Read COMRX                                |

| 101                       | 0             | 3        | Address<br>transmitted,<br>buffer empty | Write data to<br>COMTX or<br>read COMIID0 |

| 011                       | 0             | 1        | Receive line status interrupt           | Read<br>COMSTA0                           |

| 010                       | 0             | 2        | Receive buffer full interrupt           | Read COMRX                                |

| 001                       | 0             | 3        | Transmit buffer empty interrupt         | Write data to<br>COMTX or<br>read COMIID0 |

| 000                       | 0             | 4        | Modem status interrupt                  | Read<br>COMSTA1                           |

Note that to receive a network address interrupt, the slave must ensure that Bit 0 of COMIEN0 (enable receive buffer full interrupt) is set to 1.

**Table 117. COMADR Register**

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| COMADR | 0xFFFF0728 | 0xAA          | R/W    |

COMADR is an 8-bit, read/write network address register that holds the address checked for by the network addressable UART. Upon receiving this address, the device interrupts the processor and/or sets the appropriate status bit in COMIID1.

#### **SERIAL PERIPHERAL INTERFACE**

The ADuC7019/20/21/22/24/25/26/27/28/29 integrate a complete hardware serial peripheral interface (SPI) on-chip. SPI is an industry standard, synchronous serial interface that allows eight bits of data to be synchronously transmitted and simultaneously received, that is, full duplex up to a maximum bit rate of 3.48 Mb, as shown in Table 118. The SPI interface is not operational with core clock divider (CD) bits. POWCON[2:0] = 6 or 7 in master mode.

The SPI port can be configured for master or slave operation. and typically consists of four pins: MISO (P1.5), MOSI (P1.6), SCLK (P1.4), and  $\overline{CS}$  (P1.7).

On the transmit side, the SPITX register (and a TX shift register outside it) loads data onto the transmit pin (in slave mode, MISO; in master mode, MOSI). The transmit status bit, Bit 0, in SPISTA indicates whether there is valid data in the SPITX register.

Similarly, the receive data path consists of the SPIRX register (and an RX shift register). SPISTA, Bit 3 indicates whether there is valid data in the SPIRX register. If valid data in the SPIRX register is overwritten or if valid data in the RX shift register is discarded, SPISTA, Bit 5 (the overflow bit) is set.

#### MISO (Master In, Slave Out) Pin

The MISO pin is configured as an input line in master mode and an output line in slave mode. The MISO line on the master (data in) should be connected to the MISO line in the slave device (data out). The data is transferred as byte wide (8-bit) serial data, MSB first.

#### MOSI (Master Out, Slave In) Pin

The MOSI pin is configured as an output line in master mode and an input line in slave mode. The MOSI line on the master (data out) should be connected to the MOSI line in the slave device (data in). The data is transferred as byte wide (8-bit) serial data, MSB first.

#### SCLK (Serial Clock I/O) Pin

The master serial clock (SCLK) is used to synchronize the data being transmitted and received through the MOSI SCLK period. Therefore, a byte is transmitted/received after eight SCLK periods. The SCLK pin is configured as an output in master mode and as an input in slave mode.

In master mode, the polarity and phase of the clock are controlled by the SPICON register, and the bit rate is defined in the SPIDIV register as follows:

$$f_{SERIAL CLOCK} = \frac{f_{UCLK}}{2 \times (1 + SPIDIV)}$$

The maximum speed of the SPI clock is dependent on the clock divider bits and is summarized in Table 118.

Table 118. SPI Speed vs. Clock Divider Bits in Master Mode

| CD Bits             | 0     | 1     | 2     | 3     | 4     | 5     |

|---------------------|-------|-------|-------|-------|-------|-------|

| SPIDIV in Hex       | 0x05  | 0x0B  | 0x17  | 0x2F  | 0x5F  | 0xBF  |

| SPI dpeed<br>in MHz | 3.482 | 1.741 | 0.870 | 0.435 | 0.218 | 0.109 |

In slave mode, the SPICON register must be configured with the phase and polarity of the expected input clock. The slave accepts data from an external master up to 10.4 Mb at CD = 0. The formula to determine the maximum speed is as follows:

$$f_{SERIAL\ CLOCK} = \frac{f_{HCLK}}{4}$$

In both master and slave modes, data is transmitted on one edge of the SCL signal and sampled on the other. Therefore, it is important that the polarity and phase be configured the same for the master and slave devices.

### Chip Select (CS Input) Pin

In SPI slave mode, a transfer is initiated by the assertion of  $\overline{CS}$ , which is an active low input signal. The SPI port then transmits and receives 8-bit data until the transfer is concluded by deassertion of  $\overline{CS}$ . In slave mode,  $\overline{CS}$  is always an input.

### **SPI Registers**

The following MMR registers are used to control the SPI interface: SPISTA, SPIRX, SPITX, SPIDIV, and SPICON.

### **Table 119. SPISTA Register**

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| SPISTA | 0xFFFF0A00 | 0x00          | R      |

SPISTA is an 8-bit read-only status register. Only Bit 1 or Bit 4 of this register generates an interrupt. Bit 6 of the SPICON register determines which bit generates the interrupt.

#### **Table 120. SPISTA MMR Bit Descriptions**

| 1 WOLO 12 OF 10 111 111 111 21 2 0001 1 1 1 1 1 1 1 |                                                                                                                                                                       |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit                                                 | Description                                                                                                                                                           |  |  |

| 7:6                                                 | Reserved.                                                                                                                                                             |  |  |

| 5                                                   | SPIRX data register overflow status bit. Set if SPIRX is overflowing. Cleared by reading the SPIRX register.                                                          |  |  |

| 4                                                   | SPIRX data register IRQ. Set automatically if Bit 3 or Bit 5 is set. Cleared by reading the SPIRX register.                                                           |  |  |

| 3                                                   | SPIRX data register full status bit. Set automatically if a valid data is present in the SPIRX register. Cleared by reading the SPIRX register.                       |  |  |

| 2                                                   | SPITX data register underflow status bit. Set automatically if SPITX is underflowing. Cleared by writing in the SPITX register.                                       |  |  |

| 1                                                   | SPITX data register IRQ. Set automatically if Bit 0 is clear or Bit 2 is set. Cleared by writing in the SPITX register or if finished transmission disabling the SPI. |  |  |

| 0                                                   | SPITX data register empty status bit. Set by writing to SPITX to send data. This bit is set during transmission of data. Cleared when SPITX is empty.                 |  |  |

#### Table 121. SPIRX Register

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| SPIRX | 0xFFFF0A04 | 0x00          | R      |

SPIRX is an 8-bit, read-only receive register.

### **Table 122. SPITX Register**

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| SPITX | 0xFFFF0A08 | 0x00          | W      |

SPITX is an 8-bit, write-only transmit register.

### Table 123. SPIDIV Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| SPIDIV | 0xFFFF0A0C | 0x1B          | R/W    |

SPIDIV is an 8-bit, serial clock divider register.

#### **Table 124. SPICON Register**

|  | Name   | Address    | Default Value | Access |

|--|--------|------------|---------------|--------|

|  | SPICON | 0xFFFF0A10 | 0x0000        | R/W    |

SPICON is a 16-bit control register.

## **Table 125. SPICON MMR Bit Descriptions**

| Bit   | Description                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:13 | Reserved                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12    | Continuous transfer enable      | Set by user to enable continuous transfer. In master mode, the transfer continues until no valid data is available in the TX register. CS is asserted and remains asserted for the duration of each 8-bit serial transfer until TX is empty. Cleared by user to disable continuous transfer. Each transfer consists of a single 8-bit serial transfer. If valid data exists in the SPITX register, then a new transfer is initiated after a stall period. |

| 11    | Loop back enable                | Set by user to connect MISO to MOSI and test software. Cleared by user to be in normal mode.                                                                                                                                                                                                                                                                                                                                                              |

| 10    | Slave MISO output enable        | Set this bit to disable the output driver on the MISO pin. The MISO pin becomes open drain when this bit is set. Clear this bit for MISO to operate as normal.                                                                                                                                                                                                                                                                                            |

| 9     | Clip select output enable       | Set by user in master mode to disable the chip select output. cleared by user to enable the chip select output.  P1.7 should be configured as CS before SPICON is configured as a master when the chip select output enabled is also selected.                                                                                                                                                                                                            |

| 8     | SPIRX overflow overwrite enable | Set by user, the valid data in the RX register is overwritten by the new serial byte received. Cleared by user, the new serial byte received is discarded.                                                                                                                                                                                                                                                                                                |

| 7     | SPITX underflow mode            | Set by user to transmit 0. Cleared by user to transmit the previous data.                                                                                                                                                                                                                                                                                                                                                                                 |

| 6     | Transfer and interrupt mode     | Set by user to initiate transfer with a write to the SPITX register. Interrupt occurs only when TX is empty. Cleared by user to initiate transfer with a read of the SPIRX register. Interrupt occurs only when RX is full.                                                                                                                                                                                                                               |

| 5     | LSB first transfer enable bit   | Set by user, the LSB is transmitted first. Cleared by user, the MSB is transmitted first.                                                                                                                                                                                                                                                                                                                                                                 |

| 4     | Reserved                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3     | Serial clock polarity mode bit  | Set by user, the serial clock idles high. Cleared by user, the serial clock idles low.                                                                                                                                                                                                                                                                                                                                                                    |

| 2     | Serial clock phase mode bit     | Set by user, the serial clock pulses at the beginning of each serial bit transfer. Cleared by user, the serial clock pulses at the end of each serial bit transfer.                                                                                                                                                                                                                                                                                       |

| 1     | Master mode enable bit          | Set by user to enable master mode. Cleared by user to enable slave mode.                                                                                                                                                                                                                                                                                                                                                                                  |

| 0     | SPI enable bit                  | Set by user to enable the SPI. Cleared by user to disable the SPI.                                                                                                                                                                                                                                                                                                                                                                                        |

#### I<sup>2</sup>C-COMPATIBLE INTERFACES

The ADuC7019/20/21/22/24/25/26/27/28/29 support two licensed I<sup>2</sup>C interfaces. The I<sup>2</sup>C interfaces are both implemented as a hard-ware master and a full slave interface. Because the two I<sup>2</sup>C inter-faces are identical, this data sheet describes only I2C0 in detail. Note that the two masters and one of the slaves have individual interrupts (see the Interrupt System section).

Note that when configured as an  $I^2C$  master device, the ADuC7019/20/21/22/24/25/26/27/28/29 cannot generate a repeated start condition.

The two GPIO pins used for data transfer, SDAx and SCLx, are configured in a wired-AND format that allows arbitration in a multimaster system. These pins require external pull-up resistors. Typical pull-up values are  $10~\mathrm{k}\Omega$ .

The I<sup>2</sup>C bus peripheral address in the I<sup>2</sup>C bus system is programmed by the user. This ID can be modified any time a transfer is not in progress. The user can configure the interface to respond to four slave addresses.

The transfer sequence of an I<sup>2</sup>C system consists of a master device initiating a transfer by generating a start condition while the bus is idle. The master transmits the slave device address and the direction of the data transfer during the initial address transfer. If the master does not lose arbitration and the slave acknowledges, the data transfer is initiated. This continues until the master issues a stop condition and the bus becomes idle.

The I<sup>2</sup>C peripheral can be configured only as a master or slave at any given time. The same I<sup>2</sup>C channel cannot simultaneously support master and slave modes.

#### **Serial Clock Generation**

The FC master in the system generates the serial clock for a transfer. The master channel can be configured to operate in fast mode (400 kHz) or standard mode (100 kHz).

The bit rate is defined in the I2C0DIV MMR as follows:

$$f_{SERIAL CLOCK} = \frac{f_{UCLK}}{(2 + DIVH) + (2 + DIVL)}$$

where:

$f_{UCLK}$  = clock before the clock divider.

DIVH = the high period of the clock.

DIVL = the low period of the clock.

Thus, for 100 kHz operation,

DIVH = DIVL = 0xCF

and for 400 kHz,

DIVH = 0x28, DIVL = 0x3C

The I2CxDIV registers correspond to DIVH:DIVL.

#### Slave Addresses

The registers I2C0ID0, I2C0ID1, I2C0ID2, and I2C0ID3 contain the device IDs. The device compares the four I2C0IDx registers to the address byte. To be correctly addressed, the seven MSBs of either ID register must be identical to that of the seven MSBs of the first received address byte. The LSB of the ID registers (the transfer direction bit) is ignored in the process of address recognition.

## I<sup>2</sup>C Registers

The I<sup>2</sup>C peripheral interface consists of 18 MMRs, which are discussed in this section.

Table 126. I2CxMSTA Registers

|   | Name     | Address    | Default Value | Access |

|---|----------|------------|---------------|--------|

| _ | I2C0MSTA | 0xFFFF0800 | 0x00          | R/W    |

| - | I2C1MSTA | 0xFFFF0900 | 0x00          | R/W    |

I2CxMSTA are status registers for the master channel.

Table 127. I2C0MSTA MMR Bit Descriptions

|     | Access |                                                                                                                                                                               |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Type   | Description                                                                                                                                                                   |

| 7   | R/W    | Master transmit FIFO flush. Set by user to flush the master Tx FIFO. Cleared automatically after the master Tx FIFO is flushed. This bit also flushes the slave receive FIFO. |

| 6   | R      | Master busy. Set automatically if the master is busy. Cleared automatically.                                                                                                  |

| 5   | R      | Arbitration loss. Set in multimaster mode if another master has the bus. Cleared when the bus becomes available.                                                              |

| 4   | R      | No ACK. Set automatically if there is no acknowledge of the address by the slave device. Cleared automatically by reading the I2COMSTA register.                              |