#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                 |

| Core Size                  | 16/32-Bit                                                             |

| Speed                      | 44MHz                                                                 |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                            |

| Peripherals                | PLA, PWM, PSM, Temp Sensor, WDT                                       |

| Number of I/O              | 30                                                                    |

| Program Memory Size        | 62KB (31K x16)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 32                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                           |

| Data Converters            | A/D 8x12b; D/A 4x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LFBGA, CSPBGA                                                      |

| Supplier Device Package    | 64-CSPBGA (6x6)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7028bbcz62-rl |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Parameter              | Description                                         | Min                        | Тур                            | Max  | Unit |

|------------------------|-----------------------------------------------------|----------------------------|--------------------------------|------|------|

| tsL                    | SCLK low pulse width <sup>1</sup>                   |                            | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>sн</sub>        | SCLK high pulse width <sup>1</sup>                  |                            | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>DAV</sub>       | Data output valid after SCLK edge                   |                            |                                | 25   | ns   |

| tdosu                  | Data output setup before SCLK edge                  |                            |                                | 75   | ns   |

| tdsu                   | Data input setup time before SCLK edge <sup>2</sup> | $1 \times t_{UCLK}$        |                                |      | ns   |

| <b>t</b> DHD           | Data input hold time after SCLK edge <sup>2</sup>   | $2 \times t_{\text{UCLK}}$ |                                |      | ns   |

| t <sub>DF</sub>        | Data output fall time                               |                            | 5                              | 12.5 | ns   |

| <b>t</b> <sub>DR</sub> | Data output rise time                               |                            | 5                              | 12.5 | ns   |

| t <sub>sr</sub>        | SCLK rise time                                      |                            | 5                              | 12.5 | ns   |

| t <sub>sF</sub>        | SCLK fall time                                      |                            | 5                              | 12.5 | ns   |

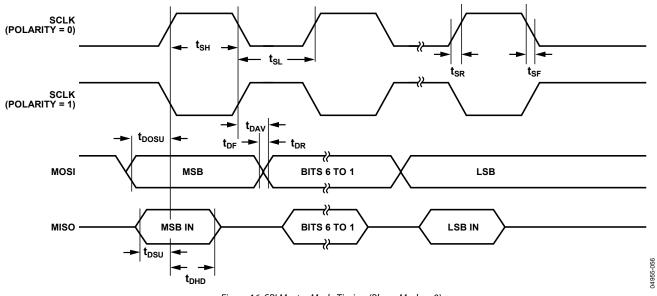

### Table 7. SPI Master Mode Timing (Phase Mode = 0)

$^{1}$  t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCONMMR. t<sub>HCLK</sub> = t<sub>UCLK</sub>/2<sup>CD</sup>; see Figure 67.

$^{2}$  t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider; see Figure 67.

Figure 16. SPI Master Mode Timing (Phase Mode = 0)

| Parameter        | Description                                         | Min                                         | Тур                            | Max  | Unit |

|------------------|-----------------------------------------------------|---------------------------------------------|--------------------------------|------|------|

| t <sub>cs</sub>  | CS to SCLK edge <sup>1</sup>                        | $(2 \times t_{HCLK}) + (2 \times t_{UCLK})$ |                                |      | ns   |

| t <sub>sL</sub>  | SCLK low pulse width <sup>2</sup>                   |                                             | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>sH</sub>  | SCLK high pulse width <sup>2</sup>                  |                                             | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>DAV</sub> | Data output valid after SCLK edge                   |                                             |                                | 25   | ns   |

| t <sub>DSU</sub> | Data input setup time before SCLK edge <sup>1</sup> | 1 × tuclk                                   |                                |      | ns   |

| t <sub>DHD</sub> | Data input hold time after SCLK edge <sup>1</sup>   | $2 \times t_{UCLK}$                         |                                |      | ns   |

| t <sub>DF</sub>  | Data output fall time                               |                                             | 5                              | 12.5 | ns   |

| t <sub>DR</sub>  | Data output rise time                               |                                             | 5                              | 12.5 | ns   |

| t <sub>sr</sub>  | SCLK rise time                                      |                                             | 5                              | 12.5 | ns   |

| t <sub>SF</sub>  | SCLK fall time                                      |                                             | 5                              | 12.5 | ns   |

| t <sub>SFS</sub> | CS high after SCLK edge                             | 0                                           |                                |      | ns   |

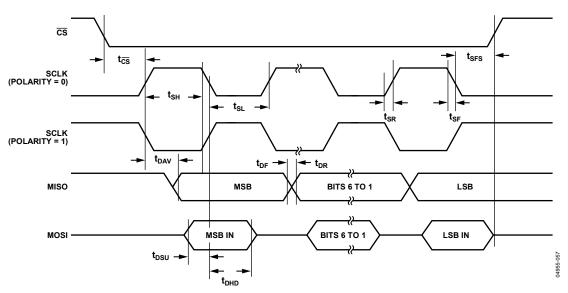

#### Table 8. SPI Slave Mode Timing (Phsae Mode = 1)

<sup>1</sup> t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider; see Figure 67. <sup>2</sup> t<sub>HCLK</sub> depends on the clock divider or CD bits in the POWCONMMR. t<sub>HCLK</sub> = t<sub>UCLK</sub>/2<sup>CD</sup>; see Figure 67.

Figure 17. SPI Slave Mode Timing (Phase Mode = 1)

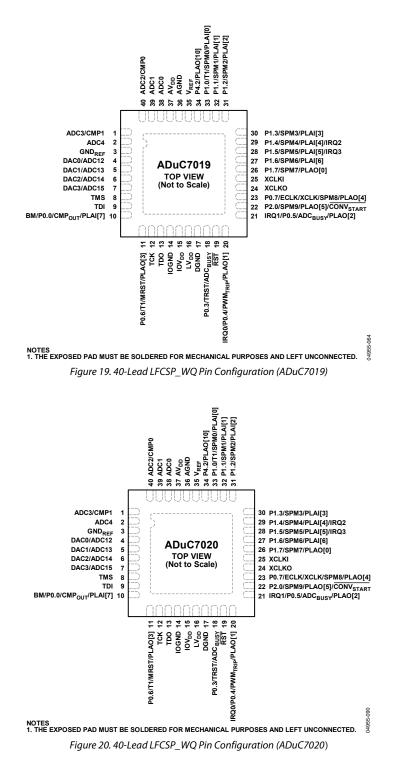

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

## ADuC7019/ADuC7020/ADuC7021/ADuC7022

| Pin No.   |      |      |                                         |                                                                                                                                                                                                            |  |  |

|-----------|------|------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7019/7020 | 7021 | 7022 | Mnemonic                                | Description                                                                                                                                                                                                |  |  |

| 22        | 22   | 21   | P2.0/SPM9/PLAO[5]/CONV <sub>START</sub> | Serial Port Multiplexed. General-Purpose Input and Output Port 2.0/UART/<br>Programmable Logic Array Output Element 5/Start Conversion Input Signal<br>for ADC.                                            |  |  |

| 23        | 23   | 22   | P0.7/ECLK/XCLK/SPM8/PLAO[4]             | Serial Port Multiplexed. General-Purpose Input and Output Port 0.7/<br>Output for External Clock Signal/Input to the Internal Clock Generator<br>Circuits/UART/ Programmable Logic Array Output Element 4. |  |  |

| 24        | 24   | 23   | XCLKO                                   | Output from the Crystal Oscillator Inverter.                                                                                                                                                               |  |  |

| 25        | 25   | 24   | XCLKI                                   | Input to the Crystal Oscillator Inverter and Input to the Internal Clock Generator Circuits.                                                                                                               |  |  |

| 26        | 26   | 25   | P1.7/SPM7/PLAO[0]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.7/UART, SPI/Programmable Logic Array Output Element 0.                                                                                    |  |  |

| 27        | 27   | 26   | P1.6/SPM6/PLAI[6]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.6/UART, SPI/Programmable Logic Array Input Element 6.                                                                                     |  |  |

| 28        | 28   | 27   | P1.5/SPM5/PLAI[5]/IRQ3                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.5/UART,<br>SPI/Programmable Logic Array Input Element 5/External Interrupt<br>Request 3, Active High.                                     |  |  |

| 29        | 29   | 28   | P1.4/SPM4/PLAI[4]/IRQ2                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.4/UART,<br>SPI/Programmable Logic Array Input Element 4/External Interrupt<br>Request 2, Active High.                                     |  |  |

| 30        | 30   | 29   | P1.3/SPM3/PLAI[3]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.3/UART, I2C1/Programmable Logic Array Input Element 3.                                                                                    |  |  |

| 31        | 31   | 30   | P1.2/SPM2/PLAI[2]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.2/UART, I2C1/Programmable Logic Array Input Element 2.                                                                                    |  |  |

| 32        | 32   | 31   | P1.1/SPM1/PLAI[1]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.1/UART, I2C0/Programmable Logic Array Input Element 1.                                                                                    |  |  |

| 33        | 33   | 32   | P1.0/T1/SPM0/PLAI[0]                    | Serial Port Multiplexed. General-Purpose Input and Output Port 1.0/<br>Timer1 Input/UART, I2C0/Programmable Logic Array Input Element 0.                                                                   |  |  |

| 34        | -    | -    | P4.2/PLAO[10]                           | General-Purpose Input and Output Port 4.2/Programmable Logic Array Output Element 10.                                                                                                                      |  |  |

| 35        | 34   | 33   | V <sub>REF</sub>                        | 2.5 V Internal Voltage Reference. Must be connected to a 0.47 $\mu F$ capacitor when using the internal reference.                                                                                         |  |  |

| 36        | 35   | 34   | AGND                                    | Analog Ground. Ground reference point for the analog circuitry.                                                                                                                                            |  |  |

| 37        | 36   | 35   | AV <sub>DD</sub>                        | 3.3 V Analog Power.                                                                                                                                                                                        |  |  |

| 0         | 0    | 0    | EP                                      | Exposed Pad. The pin configuration for the ADuC7019/ADuC7020/<br>ADuC7021/ADuC7022 has an exposed pad that must be soldered for<br>mechanical purposes and left unconnected.                               |  |  |

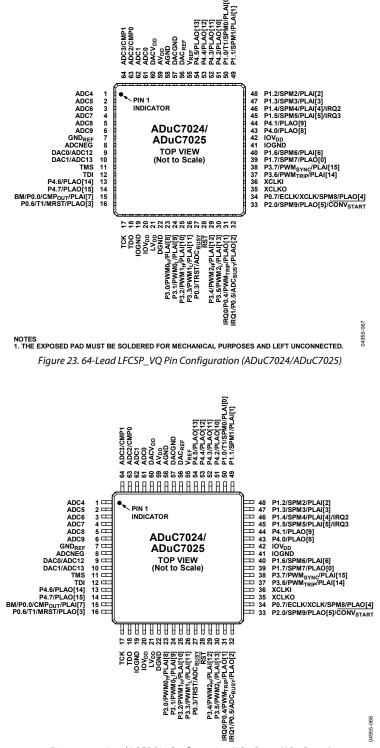

## ADuC7024/ADuC7025

Figure 24. 64-Lead LQFP Pin Configuration (ADuC7024/ADuC7025)

| Pin No. | Mnemonic                                | Description                                                                                                                                                                                                                                                                                  |

|---------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7      | P1.6/SPM6/PLAI[6]                       | Serial Port Multiplexed. General-Purpose Input and Output Port 1.6/UART, SPI/Programmable                                                                                                                                                                                                    |

| Da      |                                         | Logic Array Input Element 6.                                                                                                                                                                                                                                                                 |

| D8      |                                         | 3.3 V Supply for GPIO (see Table 78) and Input of the On-Chip Voltage Regulator.                                                                                                                                                                                                             |

| E1      | DAC3/ADC15                              | DAC3 Voltage Output/ADC Input 15.                                                                                                                                                                                                                                                            |

| E2      | DAC2/ADC14                              | DAC2 Voltage Output/ADC Input 14.                                                                                                                                                                                                                                                            |

| E3      |                                         | DAC1 Voltage Output/ADC Input 13.                                                                                                                                                                                                                                                            |

| E4      | P3.0/PWM0 <sub>H</sub> /PLAI[8]         | General-Purpose Input and Output Port 3.0/PWM Phase 0 High-Side Output/Programmable Logic Array Input Element 8.                                                                                                                                                                             |

| E5      | P3.2/PWM1 <sub>H</sub> /PLAI[10]        | General-Purpose Input and Output Port 3.2/PWM Phase 1 High-Side Output/Programmable Logic Array Input Element 10.                                                                                                                                                                            |

| E6      | P1.5/SPM5/PLAI[5]/IRQ3                  | Serial Port Multiplexed. General-Purpose Input and Output Port 1.5/UART, SPI/Programmable Logic Array Input Element 5/External Interrupt Request 3, Active High.                                                                                                                             |

| E7      | P3.7/PWM <sub>SYNC</sub> /PLAI[15]      | General-Purpose Input and Output Port 3.7/PWM Synchronization/Programmable Logic<br>Array Input Element 15.                                                                                                                                                                                  |

| E8      | XCLKI                                   | Input to the Crystal Oscillator Inverter and Input to the Internal Clock Generator Circuits.                                                                                                                                                                                                 |

| F1      | P4.6/PLAO[14]                           | General-Purpose Input and Output Port 4.6/Programmable Logic Array Output Element 14.                                                                                                                                                                                                        |

| F2      | TDI                                     | JTAG Test Port Input, Test Data In. Debug and download access.                                                                                                                                                                                                                               |

| F3      | DAC0/ADC12                              | DAC0 Voltage Output/ADC Input 12.                                                                                                                                                                                                                                                            |

| F4      | P3.1/PWM0L/PLAI[9]                      | General-Purpose Input and Output Port 3.1/PWM Phase 0 Low-Side Output/Programmable Logic Array Input Element 9.                                                                                                                                                                              |

| F5      | P3.3/PWM1L/PLAI[11]                     | General-Purpose Input and Output Port 3.3/PWM Phase 1 Low-Side Output/Programmable Logic Array Input Element 11.                                                                                                                                                                             |

| F6      | RST                                     | Reset Input, Active Low.                                                                                                                                                                                                                                                                     |

| F7      | P0.7/ECLK/XCLK/SPM8/PLAO[4]             | Serial Port Multiplexed. General-Purpose Input and Output Port 0.7/Output for External Clock Signal/Input to the Internal Clock Generator Circuits/UART/Programmable Logic Array Output Element 4.                                                                                           |

| F8      | XCLKO                                   | Output from the Crystal Oscillator Inverter.                                                                                                                                                                                                                                                 |

| G1      | BM/P0.0/CMP <sub>OUT</sub> /PLAI[7]     | Multifunction I/O Pin. Boot mode. The ADuC7028 enters UART download mode if BM is low at reset and executes code if BM is pulled high at reset through a 1 k $\Omega$ resistor/General-Purpose Input and Output Port 0.0/Voltage Comparator Output/Programmable Logic Array Input Element 7. |

| G2      | P4.7/PLAO[15]                           | General-Purpose Input and Output Port 4.7/Programmable Logic Array Output Element 15.                                                                                                                                                                                                        |

| G3      | TMS                                     | JTAG Test Port Input, Test Mode Select. Debug and download access.                                                                                                                                                                                                                           |

| G4      | TDO                                     | JTAG Test Port Output, Test Data Out. Debug and download access.                                                                                                                                                                                                                             |

| G5      | P0.3/TRST/ADC <sub>BUSY</sub>           | General-Purpose Input and Output Port 0.3/JTAG Test Port Input, Test Reset/ADC $_{\mbox{BUSY}}$ Signal Output.                                                                                                                                                                               |

| G6      | P3.4/PWM2 <sub>H</sub> /PLAI[12]        | General-Purpose Input and Output Port 3.4/PWM Phase 2 High-Side Output/Programmable Logic Array Input 12.                                                                                                                                                                                    |

| G7      | P3.5/PWM2L/PLAI[13]                     | General-Purpose Input and Output Port 3.5/PWM Phase 2 Low-Side Output/Programmable Logic Array Input Element 13.                                                                                                                                                                             |

| G8      | P2.0/SPM9/PLAO[5]/CONV <sub>START</sub> | Serial Port Multiplexed. General-Purpose Input and Output Port 2.0/UART/Programmable Logic Array Output Element 5/Start Conversion Input Signal for ADC.                                                                                                                                     |

| H1      | P0.6/T1/MRST/PLAO[3]                    | Multifunction Pin, Driven Low After Reset. General-Purpose Output Port 0.6/Timer1 Input/<br>Power-On Reset Output/Programmable Logic Array Output Element 3.                                                                                                                                 |

| H2      | тск                                     | JTAG Test Port Input, Test Clock. Debug and download access.                                                                                                                                                                                                                                 |

| H3      | IOGND                                   | Ground for GPIO (see Table 78). Typically connected to DGND.                                                                                                                                                                                                                                 |

| H4      | IOV <sub>DD</sub>                       | 3.3 V Supply for GPIO (see Table 78) and Input of the On-Chip Voltage Regulator.                                                                                                                                                                                                             |

| H5      | LV <sub>DD</sub>                        | 2.6 V Output of the On-Chip Voltage Regulator. This output must be connected to a 0.47 $\mu\text{F}$ capacitor to DGND only.                                                                                                                                                                 |

| H6      | DGND                                    | Ground for Core Logic.                                                                                                                                                                                                                                                                       |

| H7      | IRQ0/P0.4/PWM <sub>TRIP</sub> /PLAO[1]  | Multifunction I/O Pin. External Interrupt Request 0, Active High/General-Purpose Input and Output Port 0.4/PWM Trip External Input/Programmable Logic Array Output Element 1.                                                                                                                |

| H8      | IRQ1/P0.5/ADC <sub>BUSY</sub> /PLAO[2]  | Multifunction I/O Pin. External Interrupt Request 1, Active High/General-Purpose Input and Output Port 0.5/ADC <sub>BUSY</sub> Signal Output/Programmable Logic Array Output Element 2.                                                                                                      |

## TERMINOLOGY ADC SPECIFICATIONS

#### Integral Nonlinearity (INL)

The maximum deviation of any code from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point ½ LSB below the first code transition, and full scale, a point ½ LSB above the last code transition.

#### Differential Nonlinearity (DNL)

The difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### **Offset Error**

The deviation of the first code transition (0000 . . . 000) to (0000 . . . 001) from the ideal, that is,  $+\frac{1}{2}$  LSB.

#### **Gain Error**

The deviation of the last code transition from the ideal AIN voltage (full scale -1.5 LSB) after the offset error has been adjusted out.

#### Signal to (Noise + Distortion) Ratio (SINAD)

The measured ratio of signal to (noise + distortion) at the output of the ADC. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency ( $f_s/2$ ), excluding dc.

The ratio is dependent upon the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise.

The theoretical signal to (noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by

Signal to (Noise + Distortion) = (6.02 N + 1.76) dB

Thus, for a 12-bit converter, this is 74 dB.

#### **Total Harmonic Distortion (THD)**

The ratio of the rms sum of the harmonics to the fundamental.

### DAC SPECIFICATIONS

#### **Relative Accuracy**

Otherwise known as endpoint linearity, relative accuracy is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero error and full-scale error.

#### Voltage Output Settling Time

The amount of time it takes the output to settle to within a 1 LSB level for a full-scale input change.

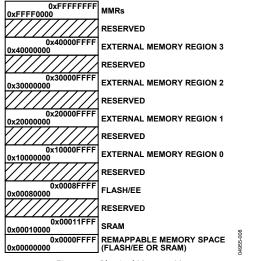

## **MEMORY ORGANIZATION**

The ADuC7019/20/21/22/24/25/26/27/28/29 incorporate two separate blocks of memory: 8 kB of SRAM and 64 kB of on-chip Flash/EE memory. The 62 kB of on-chip Flash/EE memory is available to the user, and the remaining 2 kB are reserved for the factory-configured boot page. These two blocks are mapped as shown in Figure 45.

Figure 45. Physical Memory Map

Note that by default, after a reset, the Flash/EE memory is mirrored at Address 0x00000000. It is possible to remap the SRAM at Address 0x00000000 by clearing Bit 0 of the REMAP MMR. This remap function is described in more detail in the Flash/EE Memory section.

## **MEMORY ACCESS**

The ARM7 core sees memory as a linear array of a  $2^{32}$  byte location where the different blocks of memory are mapped as outlined in Figure 45.

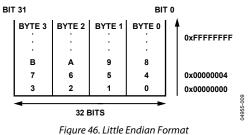

The ADuC7019/20/21/22/24/25/26/27/28/29 memory organizations are configured in little endian format, which means that the least significant byte is located in the lowest byte address, and the most significant byte is in the highest byte address.

## FLASH/EE MEMORY

The total 64 kB of Flash/EE memory is organized as  $32 \text{ k} \times 16$  bits; 31 k × 16 bits is user space and 1 k × 16 bits is reserved for the on-chip kernel. The page size of this Flash/EE memory is 512 bytes.

Sixty-two kilobytes of Flash/EE memory are available to the user as code and nonvolatile data memory. There is no distinction between data and program because ARM code shares the same space. The real width of the Flash/EE memory is 16 bits, which means that in ARM mode (32-bit instruction), two accesses to the Flash/EE are necessary for each instruction fetch. It is therefore recommended to use thumb mode when executing from Flash/EE memory for optimum access speed. The maximum access speed for the Flash/EE memory is 41.78 MHz in thumb mode and 20.89 MHz in full ARM mode. More details about Flash/EE access time are outlined in the Execution Time from SRAM and Flash/EE section.

## SRAM

Eight kilobytes of SRAM are available to the user, organized as  $2 \text{ k} \times 32$  bits, that is, two words. ARM code can run directly from SRAM at 41.78 MHz, given that the SRAM array is configured as a 32-bit wide memory array. More details about SRAM access time are outlined in the Execution Time from SRAM and Flash/EE section.

## **MEMORY MAPPED REGISTERS**

The memory mapped register (MMR) space is mapped into the upper two pages of the memory array and accessed by indirect addressing through the ARM7 banked registers.

The MMR space provides an interface between the CPU and all on-chip peripherals. All registers, except the core registers, reside in the MMR area. All shaded locations shown in Figure 47 are unoccupied or reserved locations and should not be accessed by user software. Table 16 shows the full MMR memory map.

The access time for reading from or writing to an MMR depends on the advanced microcontroller bus architecture (AMBA) bus used to access the peripheral. The processor has two AMBA buses: the advanced high performance bus (AHB) used for system modules and the advanced peripheral bus (APB) used for lower performance peripheral. Access to the AHB is one cycle, and access to the APB is two cycles. All peripherals on the ADuC7019/20/21/22/24/25/26/27/28/29 are on the APB except the Flash/EE memory, the GPIOs (see Table 78), and the PWM.

### Table 18. ADCCON MMR Bit Designations

| Bit   | Value        | Description                                                                                             |

|-------|--------------|---------------------------------------------------------------------------------------------------------|

| 15:13 |              | Reserved.                                                                                               |

| 12:10 |              | ADC clock speed.                                                                                        |

|       | 000          | fADC/1. This divider is provided to obtain                                                              |

|       |              | 1 MSPS ADC with an external clock <41.78 MHz.                                                           |

|       | 001          | fADC/2 (default value).                                                                                 |

|       | 010          | fADC/4.                                                                                                 |

|       | 011          | fADC/8.                                                                                                 |

|       | 100          | fADC/16.                                                                                                |

|       | 101          | fADC/32.                                                                                                |

| 9:8   |              | ADC acquisition time.                                                                                   |

|       | 00           | Two clocks.                                                                                             |

|       | 01           | Four clocks.                                                                                            |

|       | 10           | Eight clocks (default value).                                                                           |

|       | 11           | 16 clocks.                                                                                              |

| 7     |              | Enable start conversion.                                                                                |

|       |              | Set by the user to start any type of conversion                                                         |

|       |              | command. Cleared by the user to disable a                                                               |

|       |              | start conversion (clearing this bit does not stop the ADC when continuously converting).                |

| 6     |              | Reserved.                                                                                               |

| 0     |              | Reserved.                                                                                               |

| 5     |              | ADC power control.                                                                                      |

| J     |              | Set by the user to place the ADC in normal                                                              |

|       |              | mode (the ADC must be powered up for at least                                                           |

|       |              | 5 µs before it converts correctly). Cleared by the                                                      |

|       |              | user to place the ADC in power-down mode.                                                               |

| 4:3   |              | Conversion mode.                                                                                        |

|       | 00           | Single-ended mode.                                                                                      |

|       | 01           | Differential mode.                                                                                      |

|       | 10           | Pseudo differential mode.                                                                               |

|       | 11           | Reserved.                                                                                               |

| 2:0   |              | Conversion type.                                                                                        |

|       | 000          | Enable CONV <sub>START</sub> pin as a conversion input.                                                 |

|       | 001          | Enable Timer1 as a conversion input.                                                                    |

|       | 010          | Enable Timer0 as a conversion input.                                                                    |

|       | 011          | Single software conversion. Sets to 000 after                                                           |

|       |              | conversion (note that Bit 7 of ADCCON MMR                                                               |

|       |              | should be cleared after starting a single                                                               |

|       |              | software conversion to avoid <u>further</u><br>conversions triggered by the CONV <sub>START</sub> pin). |

|       | 100          |                                                                                                         |

|       | 100          | Continuous software conversion.                                                                         |

|       | 101<br>Other | PLA conversion.                                                                                         |

|       | Other        | Reserved.                                                                                               |

#### Table 19. ADCCP Register

\_

| ADCCP 0xFFFF0504 0x00 R/W | Name  | Address    | Default Value | Access |

|---------------------------|-------|------------|---------------|--------|

|                           | ADCCP | 0xFFFF0504 | 0x00          | R/W    |

ADCCP is an ADC positive channel selection register. This MMR is described in Table 20.

### Table 20. ADCCP<sup>1</sup> MMR Bit Designation

| Bit | Value  | Description                                   |

|-----|--------|-----------------------------------------------|

| 7:5 |        | Reserved.                                     |

| 4:0 |        | Positive channel selection bits.              |

|     | 00000  | ADC0.                                         |

|     | 00001  | ADC1.                                         |

|     | 00010  | ADC2.                                         |

|     | 00011  | ADC3.                                         |

|     | 00100  | ADC4.                                         |

|     | 00101  | ADC5.                                         |

|     | 00110  | ADC6.                                         |

|     | 00111  | ADC7.                                         |

|     | 01000  | ADC8.                                         |

|     | 01001  | ADC9.                                         |

|     | 01010  | ADC10.                                        |

|     | 01011  | ADC11.                                        |

|     | 01100  | DAC0/ADC12.                                   |

|     | 01101  | DAC1/ADC13.                                   |

|     | 01110  | DAC2/ADC14.                                   |

|     | 01111  | DAC3/ADC15.                                   |

|     | 10000  | Temperature sensor.                           |

|     | 10001  | AGND (self-diagnostic feature).               |

|     | 10010  | Internal reference (self-diagnostic feature). |

|     | 10011  | AV <sub>DD</sub> /2.                          |

|     | Others | Reserved.                                     |

<sup>1</sup> ADC and DAC channel availability depends on the part model. See Ordering Guide for details.

#### Table 21. ADCCN Register

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| ADCCN | 0xFFFF0508 | 0x01          | R/W    |

ADCCN is an ADC negative channel selection register. This MMR is described in Table 22.

## Data Sheet

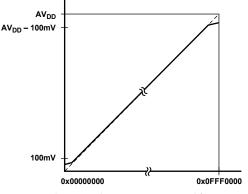

Linearity degradation near ground and AV<sub>DD</sub> is caused by saturation of the output amplifier, and a general representation of its effects (neglecting offset and gain error) is illustrated in Figure 64. The dotted line in Figure 64 indicates the ideal transfer function, and the solid line represents what the transfer function may look like with endpoint nonlinearities due to saturation of the output amplifier. Note that Figure 64 represents a transfer function in 0-to-AV<sub>DD</sub> mode only. In 0-to-V<sub>REF</sub> or 0-to-DAC<sub>REF</sub> mode (with V<sub>REF</sub> < AV<sub>DD</sub> or DAC<sub>REF</sub> < AV<sub>DD</sub>), the lower nonlinearity is similar. However, the upper portion of the transfer function follows the ideal line right to the end (V<sub>REF</sub> in this case, not AV<sub>DD</sub>), showing no signs of endpoint linearity errors.

Figure 64. Endpoint Nonlinearities Due to Amplifier Saturation

The endpoint nonlinearities conceptually illustrated in Figure 64 get worse as a function of output loading. Most of the ADuC7019/20/21/22/24/25/26/27/28/29 data sheet specifications assume a 5 k $\Omega$  resistive load to ground at the DAC output. As the output is forced to source or sink more current, the nonlinear regions at the top or bottom (respectively) of Figure 64 become larger. With larger current demands, this can significantly limit output voltage swing.

## **POWER SUPPLY MONITOR**

The power supply monitor regulates the  $IOV_{DD}$  supply on the ADuC7019/20/21/22/24/25/26/27/28/29. It indicates when the  $IOV_{DD}$  supply pin drops below one of two supply trip points. The monitor function is controlled via the PSMCON register. If enabled in the IRQEN or FIQEN register, the monitor interrupts the core using the PSMI bit in the PSMCON MMR. This bit is immediately cleared after CMP goes high.

This monitor function allows the user to save working registers to avoid possible data loss due to low supply or brown-out conditions. It also ensures that normal code execution does not resume until a safe supply level is established.

#### Table 53. PSMCON Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| PSMCON | 0xFFFF0440 | 0x0008        | R/W    |

# ADuC7019/20/21/22/24/25/26/27/28/29

#### Table 54. PSMCON MMR Bit Descriptions

| - |     |       |                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| _ | Bit | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                           |  |

|   | 3   | CMP   | Comparator bit. This is a read-only bit that<br>directly reflects the state of the comparator.<br>Read 1 indicates that the IOV <sub>DD</sub> supply is above<br>its selected trip point or that the PSM is in<br>power-down mode. Read 0 indicates that the<br>IOV <sub>DD</sub> supply is below its selected trip point. This<br>bit should be set before leaving the interrupt<br>service routine. |  |

|   | 2   | TP    | Trip point selection bit. $0 = 2.79 \text{ V}$ , $1 = 3.07 \text{ V}$ .                                                                                                                                                                                                                                                                                                                               |  |

|   | 1   | PSMEN | Power supply monitor enable bit. Set to 1 to<br>enable the power supply monitor circuit. Cleared<br>to 0 to disable the power supply monitor circuit.                                                                                                                                                                                                                                                 |  |

| _ | 0   | PSMI  | Power supply monitor interrupt bit. This bit is set<br>high by the MicroConverter after CMP goes low,<br>indicating low I/O supply. The PSMI bit can be<br>used to interrupt the processor. After CMP<br>returns high, the PSMI bit can be cleared by<br>writing a 1 to this location. A 0 write has no<br>effect. There is no timeout delay; PSMI can be<br>immediately cleared after CMP goes high. |  |

## COMPARATOR

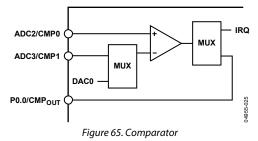

The ADuC7019/20/21/22/24/25/26/27/28/29 integrate voltage comparators. The positive input is multiplexed with ADC2, and the negative input has two options: ADC3 and DAC0. The output of the comparator can be configured to generate a system interrupt, be routed directly to the programmable logic array, start an ADC conversion, or be on an external pin, CMP<sub>OUT</sub>, as shown in Figure 65.

Note that because the ADuC7022, ADuC7025, and ADu7027 parts do not support a DAC0 output, it is not possible to use DAC0 as a comparator input on these parts.

## Hysteresis

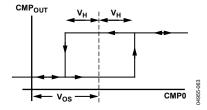

Figure 66 shows how the input offset voltage and hysteresis terms are defined.

Figure 66. Comparator Hysteresis Transfer Function

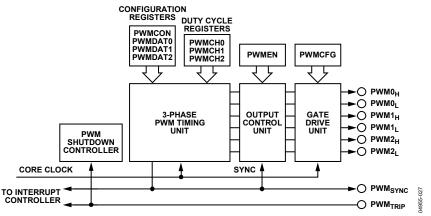

## **DESCRIPTION OF THE PWM BLOCK**

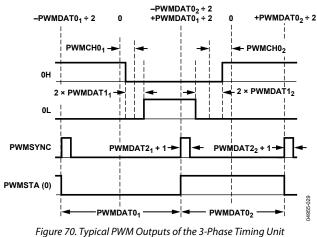

A functional block diagram of the PWM controller is shown in Figure 68. The generation of the six output PWM signals on Pin PWM0<sub>H</sub> to Pin PWM2<sub>L</sub> is controlled by the following four important blocks:

- The 3-phase PWM timing unit. The core of the PWM controller, this block generates three pairs of complemented and dead-time-adjusted, center-based PWM signals. This unit also generates the internal synchronization pulse, PWMSYNC. It also controls whether the external PWM<sub>SYNC</sub> pin is used.

- The output control unit. This block can redirect the outputs of the 3-phase timing unit for each channel to either the high-side or low-side output. In addition, the output control unit allows individual enabling/disabling of each of the six PWM output signals.

- The gate drive unit. This block can generate the high frequency chopping and its subsequent mixing with the PWM signals.

- The PWM shutdown controller. This block controls the PWM shutdown via the PWM<sub>TRIP</sub> pin and generates the correct reset signal for the timing unit.

The PWM controller is driven by the ADuC7019/20/21/22/24/ 25/26/27/28/29 core clock frequency and is capable of generating two interrupts to the ARM core. One interrupt is generated on the occurrence of a PWMSYNC pulse, and the other is generated on the occurrence of any PWM shutdown action.

## 3-Phase Timing Unit

## PWM Switching Frequency (PWMDAT0 MMR)

The PWM switching frequency is controlled by the PWM period register, PWMDAT0. The fundamental timing unit of the PWM controller is

$t_{CORE} = 1/f_{CORE}$

where  $f_{CORE}$  is the core frequency of the MicroConverter.

Therefore, for a 41.78 MHz  $f_{\rm CORE}$ , the fundamental time increment is 24 ns. The value written to the PWMDAT0 register is effectively the number of  $f_{\rm CORE}$  clock increments in one-half a PWM period. The required PWMDAT0 value is a function of the desired PWM switching frequency ( $f_{\rm PWN}$ ) and is given by

$PWMDAT0 = f_{CORE}/(2 \times f_{PWM})$

Therefore, the PWM switching period, ts, can be written as

$t_S = 2 \times PWMDAT0 \times t_{CORE}$

The largest value that can be written to the 16-bit PWMDAT0 MMR is 0xFFFF = 65,535, which corresponds to a minimum PWM switching frequency of

$f_{PWM(min)} = 41.78 \times 10^{6}/(2 \times 65,535) = 318.75 \text{ Hz}$

Note that PWMDAT0 values of 0 and 1 are not defined and should not be used.

### PWM Switching Dead Time (PWMDAT1 MMR)

The second important parameter that must be set up in the initial configuration of the PWM block is the switching dead time. This is a short delay time introduced between turning off one PWM signal (0H, for example) and turning on the complementary signal (0L). This short time delay is introduced to permit the power switch to be turned off (in this case, 0H) to completely recover its blocking capability before the complementary switch is turned on. This time delay prevents a potentially destructive short-circuit condition from developing across the dc link capacitor of a typical voltage source inverter.

The dead time is controlled by the 10-bit, read/write PWMDAT1 register. There is only one dead-time register that controls the dead time inserted into all three pairs of PWM output signals. The dead time,  $t_D$ , is related to the value in the PWMDAT1 register by

#### $t_D = PWMDAT1 \times 2 \times t_{CORE}$

Therefore, a PWMDAT1 value of 0x00A (= 10), introduces a 426 ns delay between the turn-off on any PWM signal (0H, for example) and the turn-on of its complementary signal (0L). The amount of the dead time can, therefore, be programmed in increments of  $2t_{CORE}$  (or 49 ns for a 41.78 MHz core clock).

Figure 68. Overview of the PWM Controller

Both switching edges are moved by an equal amount (PWMDAT1  $\times$   $t_{\rm CORE}$ ) to preserve the symmetrical output patterns.

Also shown are the PWMSYNC pulse and Bit 0 of the PWMSTA register, which indicates whether operation is in the first or second half cycle of the PWM period.

The resulting on times of the PWM signals over the full PWM period (two half periods) produced by the timing unit can be written as follows:

On the high side

$t_{OHH} = PWMDAT0 + 2(PWMCH0 - PWMDAT1) \times t_{CORE}$

$t_{OHL} = PWMDAT0 - 2(PWMCH0 - PWMDAT1) \times t_{CORE}$

and the corresponding duty cycles (d)

$d_{0H} = t_{0HH}/t_s = \frac{1}{2} + (PWMCH0 - PWMDAT1)/PWMDAT0$ and on the low side

$t_{0LH} = PWMDAT0 - 2(PWMCH0 + PWMDAT1) \times t_{CORE}$

$t_{oll} = PWMDAT0 + 2(PWMCH0 + PWMDAT1) \times t_{CORE}$

and the corresponding duty cycles (d)

$d_{OL} = t_{OLH}/t_S = \frac{1}{2} - (PWMCH0 + PWMDAT1)/PWMDAT0$

The minimum permissible  $t_{0H}$  and  $t_{0L}$  values are zero, corresponding to a 0% duty cycle. In a similar fashion, the maximum value is  $t_s$ , corresponding to a 100% duty cycle.

Figure 70 shows the output signals from the timing unit for operation in double update mode. It illustrates a general case where the switching frequency, dead time, and duty cycle are all changed in the second half of the PWM period. The same value for any or all of these quantities can be used in both halves of the PWM cycle. However, there is no guarantee that symmetrical PWM signals are produced by the timing unit in double update mode. Figure 70 also shows that the dead time insertions into the PWM signals are done in the same way as in single update mode.

(Double Update Mode)

In general, the on times of the PWM signals in double update mode can be defined as follows:

On the high side

$t_{0HH} = (PWMDAT0_1/2 + PWMDAT0_2/2 + PWMCH0_1 + PWMCH0_2 - PWMDAT1_1 - PWMDAT1_2) \times t_{CORE}$

$t_{0HL} = (PWMDAT0_1/2 + PWMDAT0_2/2 - PWMCH0_1 - PWMCH0_2 + PWMDAT1_1 + PWMDAT1_2) \times t_{CORE}$

where Subscript *1* refers to the value of that register during the first half cycle, and Subscript *2* refers to the value during the second half cycle.

The corresponding duty cycles (d) are

$d_{0H} = t_{0HH}/t_s = (PWMDAT0_1/2 + PWMDAT0_2/2 + PWMCH0_1 + PWMCH0_2 - PWMDAT1_1 - PWMDAT1_2)/$ (PWMDAT0\_1 + PWMDAT0\_2)

On the low side

$t_{0LH} = (PWMDAT0_1/2 + PWMDAT0_2/2 + PWMCH0_1 + PWMCH0_2 + PWMDAT1_1 + PWMDAT1_2) \times t_{CORE}$

$t_{oLL} = (PWMDAT0_1/2 + PWMDAT0_2/2 - PWMCH0_1 - PWMCH0_2 - PWMDAT1_1 - PWMDAT1_2) \times t_{CORE}$

where Subscript *1* refers to the value of that register during the first half cycle, and Subscript *2* refers to the value during the second half cycle.

The corresponding duty cycles (d) are

$d_{0L} = t_{0LH}/t_{S} = (PWMDAT0_{1}/2 + PWMDAT0_{2}/2 + PWMCH0_{1} + PWMCH0_{2} + PWMDAT1_{1} + PWMDAT1_{2})/(PWMDAT0_{1} + PWMDAT0_{2})$

For the completely general case in double update mode (see Figure 70), the switching period is given by

$t_{S} = (PWMDATO_{1} + PWMDATO_{2}) \times t_{CORE}$

Again, the values of  $t_{0H}$  and  $t_{0L}$  are constrained to lie between zero and  $t_{\text{S}}.$

PWM signals similar to those illustrated in Figure 69 and Figure 70 can be produced on the 1H, 1L, 2H, and 2L outputs by programming the PWMCH1 and PWMCH2 registers in a manner identical to that described for PWMCH0. The PWM controller does not produce any PWM outputs until all of the PWMDAT0, PWMCH0, PWMCH1, and PWMCH2 registers have been written to at least once. When these registers are written, internal counting of the timers in the 3-phase timing unit is enabled.

Writing to the PWMDAT0 register starts the internal timing of the main PWM timer. Provided that the PWMDAT0 register is written to prior to the PWMCH0, PWMCH1, and PWMCH2 registers in the initialization, the first PWMSYNC pulse and interrupt (if enabled) appear  $1.5 \times t_{CORE} \times PWMDAT0$  seconds after the initial write to the PWMDAT0 register in single update mode. In double update mode, the first PWMSYNC pulse appears after PWMDAT0 × t\_{CORE} seconds.

|      |      | Configuration |                        |      |          |  |

|------|------|---------------|------------------------|------|----------|--|

| Port | Pin  | 00            | 01                     | 10   | 11       |  |

| 0    | P0.0 | GPIO          | CMP                    | MS0  | PLAI[7]  |  |

|      | P0.1 | GPIO          | PWM2 <sub>H</sub>      | BLE  |          |  |

|      | P0.2 | GPIO          | PWM2∟                  | BHE  |          |  |

|      | P0.3 | GPIO          | TRST                   | A16  | ADCBUSY  |  |

|      | P0.4 | GPIO/IRQ0     | PWMTRIP                | MS1  | PLAO[1]  |  |

|      | P0.5 | GPIO/IRQ1     | ADCBUSY                | MS2  | PLAO[2]  |  |

|      | P0.6 | GPIO/T1       | MRST                   |      | PLAO[3]  |  |

|      | P0.7 | GPIO          | ECLK/XCLK <sup>1</sup> | SIN  | PLAO[4]  |  |

| 1    | P1.0 | GPIO/T1       | SIN                    | SCL0 | PLAI[0]  |  |

|      | P1.1 | GPIO          | SOUT                   | SDA0 | PLAI[1]  |  |

|      | P1.2 | GPIO          | RTS                    | SCL1 | PLAI[2]  |  |

|      | P1.3 | GPIO          | CTS                    | SDA1 | PLAI[3]  |  |

|      | P1.4 | GPIO/IRQ2     | RI                     | SCLK | PLAI[4]  |  |

|      | P1.5 | GPIO/IRQ3     | DCD                    | MISO | PLAI[5]  |  |

|      | P1.6 | GPIO          | DSR                    | MOSI | PLAI[6]  |  |

|      | P1.7 | GPIO          | DTR                    | CS   | PLAO[0]  |  |

| 2    | P2.0 | GPIO          |                        | SOUT | PLAO[5]  |  |

|      | P2.1 | GPIO          | PWM0 <sub>H</sub>      | WS   | PLAO[6]  |  |

|      | P2.2 | GPIO          | PWM0⊾                  | RS   | PLAO[7]  |  |

|      | P2.3 | GPIO          |                        | AE   |          |  |

|      | P2.4 | GPIO          | PWM0 <sub>H</sub>      | MS0  |          |  |

|      | P2.5 | GPIO          | PWM0∟                  | MS1  |          |  |

|      | P2.6 | GPIO          | PWM1 <sub>H</sub>      | MS2  |          |  |

|      | P2.7 | GPIO          | PWM1∟                  | MS3  |          |  |

| 3    | P3.0 | GPIO          | PWM0 <sub>H</sub>      | AD0  | PLAI[8]  |  |

|      | P3.1 | GPIO          | PWM0∟                  | AD1  | PLAI[9]  |  |

|      | P3.2 | GPIO          | PWM1 <sub>H</sub>      | AD2  | PLAI[10] |  |

|      | P3.3 | GPIO          | PWM1∟                  | AD3  | PLAI[11] |  |

|      | P3.4 | GPIO          | PWM2 <sub>H</sub>      | AD4  | PLAI[12] |  |

|      | P3.5 | GPIO          | PWM2∟                  | AD5  | PLAI[13] |  |

|      | P3.6 | GPIO          | PWM <sub>TRIP</sub>    | AD6  | PLAI[14] |  |

|      | P3.7 | GPIO          | PWM <sub>SYNC</sub>    | AD7  | PLAI[15] |  |

| 4    | P4.0 | GPIO          |                        | AD8  | PLAO[8]  |  |

|      | P4.1 | GPIO          |                        | AD9  | PLAO[9]  |  |

|      | P4.2 | GPIO          |                        | AD10 | PLAO[10] |  |

|      | P4.3 | GPIO          |                        | AD11 | PLAO[11] |  |

|      | P4.4 | GPIO          |                        | AD12 | PLAO[12] |  |

|      | P4.5 | GPIO          |                        | AD13 | PLAO[13] |  |

|      | P4.6 | GPIO          |                        | AD14 | PLAO[14] |  |

|      | P4.7 | GPIO          |                        | AD15 | PLAO[15] |  |

## Table 78. GPIO Pin Function Descriptions

<sup>1</sup>When configured in Mode 1, P0.7 is ECLK by default, or core clock output. To configure it as a clock input, the MDCLK bits in PLLCON must be set to 11. <sup>2</sup> The CONV<sub>START</sub> signal is active in all modes of P2.0.

#### Table 79. GPxCON Registers

| Name Address |            | Default Value | Access |  |

|--------------|------------|---------------|--------|--|

| GP0CON       | 0xFFFFF400 | 0x0000000     | R/W    |  |

| GP1CON       | 0xFFFFF404 | 0x0000000     | R/W    |  |

| GP2CON       | 0xFFFFF408 | 0x0000000     | R/W    |  |

| GP3CON       | 0xFFFFF40C | 0x0000000     | R/W    |  |

| GP4CON       | 0xFFFFF410 | 0x0000000     | R/W    |  |

GPxCON are the Port x control registers, which select the function of each pin of Port x as described in Table 80.

#### Table 80. GPxCON MMR Bit Descriptions

| -     |                                  |  |

|-------|----------------------------------|--|

| Bit   | Description                      |  |

| 31:30 | Reserved.                        |  |

| 29:28 | Select function of the Px.7 pin. |  |

| 27:26 | Reserved.                        |  |

| 25:24 | Select function of the Px.6 pin. |  |

| 23:22 | Reserved.                        |  |

| 21:20 | Select function of the Px.5 pin. |  |

| 19:18 | Reserved.                        |  |

| 17:16 | Select function of the Px.4 pin. |  |

| 15:14 | Reserved.                        |  |

| 13:12 | Select function of the Px.3 pin. |  |

| 11:10 | Reserved.                        |  |

| 9:8   | Select function of the Px.2 pin. |  |

| 7:6   | Reserved.                        |  |

| 5:4   | Select function of the Px.1 pin. |  |

| 3:2   | Reserved.                        |  |

| 1:0   | Select function of the Px.0 pin. |  |

|       |                                  |  |

#### Table 81. GPxPAR Registers

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| GPOPAR | 0xFFFFF42C | 0x20000000    | R/W    |

| GP1PAR | 0xFFFFF43C | 0x0000000     | R/W    |

GPxPAR program the parameters for Port 0 and Port 1. Note that the GPxDAT MMR must always be written after changing the GPxPAR MMR.

#### Table 82. GPxPAR MMR Bit Descriptions

| Bit   | Description           |

|-------|-----------------------|

| 31    | Reserved.             |

| 30:29 | Drive strength Px.7.  |

| 28    | Pull-Up Disable Px.7. |

| 27    | Reserved.             |

| 26:25 | Drive strength Px.6.  |

| 24    | Pull-Up Disable Px.6. |

| 23    | Reserved.             |

| 22:21 | Drive strength Px.5.  |

| 20    | Pull-Up Disable Px.5. |

| 19    | Reserved.             |

| 18:17 | Drive strength Px.4.  |

| 16    | Pull-Up Disable Px.4. |

| 15    | Reserved.             |

| 14:13 | Drive strength Px.3.  |

| 12    | Pull-Up Disable Px.3. |

| 11    | Reserved.             |

| 10:9  | Drive strength Px.2.  |

| 8     | Pull-Up Disable Px.2. |

| 7     | Reserved.             |

| 6:5   | Drive strength Px.1.  |

| 4     | Pull-Up Disable Px.1. |

| 3     | Reserved.             |

| 2:1   | Drive strength Px.0.  |

| 0     | Pull-Up Disable Px.0. |

| Table 05. GI ADATI Registers |            |                            |        |

|------------------------------|------------|----------------------------|--------|

| Name                         | Address    | Default Value <sup>1</sup> | Access |

| GP0DAT                       | 0xFFFFF420 | 0x000000XX                 | R/W    |

| GP1DAT                       | 0xFFFFF430 | 0x000000XX                 | R/W    |

| GP2DAT                       | 0xFFFFF440 | 0x000000XX                 | R/W    |

| GP3DAT                       | 0xFFFFF450 | 0x000000XX                 | R/W    |

| GP4DAT                       | 0xFFFFF460 | 0x000000XX                 | R/W    |

|                              |            |                            |        |

#### Table 85. GPxDAT Registers

<sup>1</sup>X = 0, 1, 2, or 3.

GPxDAT are Port x configuration and data registers. They configure the direction of the GPIO pins of Port x, set the output value for the pins configured as output, and store the input value of the pins configured as input.

#### Table 86. GPxDAT MMR Bit Descriptions

| Bit   | Description                                                                                                                                       |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:24 | Direction of the data. Set to 1 by user to configure<br>the GPIO pin as an output. Cleared to 0 by user to<br>configure the GPIO pin as an input. |  |

| 23:16 | Port x data output.                                                                                                                               |  |

| 15:8  | Reflect the state of Port x pins at reset (read only).                                                                                            |  |

| 7:0   | Port x data input (read only).                                                                                                                    |  |

#### Table 87. GPxSET Registers

| Name   | Address    | Default Value <sup>1</sup> | Access |  |

|--------|------------|----------------------------|--------|--|

| GP0SET | 0xFFFFF424 | 0x000000XX                 | W      |  |

| GP1SET | 0xFFFFF434 | 0x000000XX                 | W      |  |

| GP2SET | 0xFFFFF444 | 0x000000XX                 | W      |  |

| GP3SET | 0xFFFFF454 | 0x000000XX                 | W      |  |

| GP4SET | 0xFFFFF464 | 0x000000XX                 | W      |  |

| _      | •          | •                          |        |  |

$^{1}X = 0, 1, 2, \text{ or } 3.$

GPxSET are data set Port x registers.

#### Table 88. GPxSET MMR Bit Descriptions

| Bit   | Description                                                                                                                                                              |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:24 | Reserved.                                                                                                                                                                |  |

| 23:16 | Data Port x set bit. Set to 1 by user to set bit on Port x;<br>also sets the corresponding bit in the GPxDAT MMR.<br>Cleared to 0 by user; does not affect the data out. |  |

| 15:0  | Reserved.                                                                                                                                                                |  |

#### Table 89. GPxCLR Registers

| Name Address |            | Default Value <sup>1</sup> | Access |  |

|--------------|------------|----------------------------|--------|--|

| GP0CLR       | 0xFFFFF428 | 0x000000XX                 | W      |  |

| GP1CLR       | 0xFFFFF438 | 0x000000XX                 | W      |  |

| GP2CLR       | 0xFFFFF448 | 0x000000XX                 | W      |  |

| GP3CLR       | 0xFFFFF458 | 0x000000XX                 | W      |  |

| GP4CLR       | 0xFFFFF468 | 0x000000XX                 | W      |  |

$^{1}X = 0, 1, 2, \text{ or } 3.$

GPxCLR are data clear Port x registers.

#### Table 90. GPxCLR MMR Bit Descriptions

| Bit   | Description                                                                                                                                                                    |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:24 | Reserved.                                                                                                                                                                      |  |

| 23:16 | Data Port x clear bit. Set to 1 by user to clear bit on<br>Port x; also clears the corresponding bit in the GPxDAT<br>MMR. Cleared to 0 by user; does not affect the data out. |  |

| 15:0  | Reserved.                                                                                                                                                                      |  |

#### **SERIAL PORT MUX**

The serial port mux multiplexes the serial port peripherals (an SPI, UART, and two I<sup>2</sup>Cs) and the programmable logic array (PLA) to a set of 10 GPIO pins. Each pin must be configured to one of its specific I/O functions as described in Table 91.

#### Table 91. SPM Configuration

|        | GPIO | UART      | UART/I <sup>2</sup> C/SPI | PLA     |

|--------|------|-----------|---------------------------|---------|

| SPMMUX | (00) | (01)      | (10)                      | (11)    |

| SPM0   | P1.0 | SIN       | I2C0SCL                   | PLAI[0] |

| SPM1   | P1.1 | SOUT      | I2C0SDA                   | PLAI[1] |

| SPM2   | P1.2 | RTS       | I2C1SCL                   | PLAI[2] |

| SPM3   | P1.3 | CTS       | I2C1SDA                   | PLAI[3] |

| SPM4   | P1.4 | RI        | SCLK                      | PLAI[4] |

| SPM5   | P1.5 | DCD       | MISO                      | PLAI[5] |

| SPM6   | P1.6 | DSR       | MOSI                      | PLAI[6] |

| SPM7   | P1.7 | DTR       | CS                        | PLAO[0] |

| SPM8   | P0.7 | ECLK/XCLK | SIN                       | PLAO[4] |

| SPM9   | P2.0 | CONV      | SOUT                      | PLAO[5] |

Table 91 also details the mode for each of the SPMMUX pins. This configuration must be done via the GP0CON, GP1CON, and GP2CON MMRs. By default, these 10 pins are configured as GPIOs.

## **UART SERIAL INTERFACE**

The UART peripheral is a full-duplex, universal, asynchronous receiver/transmitter. It is fully compatible with the 16,450 serial port standard. The UART performs serial-to-parallel conversions on data characters received from a peripheral device or modem, and parallel-to-serial conversions on data characters received from the CPU. The UART includes a fractional divider for baud rate generation and has a network addressable mode. The UART function is made available on the 10 pins of the ADuC7019/20/21/22/24/25/26/27/28/29 (see Table 92).

#### Table 92. UART Signal Description

| Pin           | Signal | Description           |  |

|---------------|--------|-----------------------|--|

| SPM0 (Mode 1) | SIN    | Serial receive data.  |  |

| SPM1 (Mode 1) | SOUT   | Serial transmit data. |  |

| SPM2 (Mode 1) | RTS    | Request to send.      |  |

| SPM3 (Mode 1) | CTS    | Clear to send.        |  |

| SPM4 (Mode 1) | RI     | Ring indicator.       |  |

| SPM5 (Mode 1) | DCD    | Data carrier detect.  |  |

| SPM6 (Mode 1) | DSR    | Data set ready.       |  |

| SPM7 (Mode 1) | DTR    | Data terminal ready.  |  |

| SPM8 (Mode 2) | SIN    | Serial receive data.  |  |

| SPM9 (Mode 2) | SOUT   | Serial transmit data. |  |

## Data Sheet

The serial communication adopts an asynchronous protocol, which supports various word lengths, stop bits, and parity generation options selectable in the configuration register.

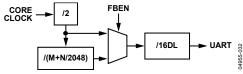

#### **Baud Rate Generation**

There are two ways of generating the UART baud rate, normal 450 UART baud rate generation and the fractional divider.

#### Normal 450 UART Baud Rate Generation

The baud rate is a divided version of the core clock using the values in the COMDIV0 and COMDIV1 MMRs (16-bit value, DL).

Baud Rate =

$$\frac{41.78 \text{ MHz}}{2^{\text{CD}} - 16 \times 2 \times \text{DL}}$$

Table 93 gives some common baud rate values.

| Table 93. l | Baud Rate | e Using tl | ne Normal | Baud | Rate G | enerator |

|-------------|-----------|------------|-----------|------|--------|----------|

|             |           |            |           |      |        |          |

| Baud Rate | CD | DL   | Actual Baud Rate | % Error |

|-----------|----|------|------------------|---------|

| 9600      | 0  | 0x88 | 9600             | 0       |

| 19,200    | 0  | 0x44 | 19,200           | 0       |

| 115,200   | 0  | 0x0B | 118,691          | 3       |

| 9600      | 3  | 0x11 | 9600             | 0       |

| 19,200    | 3  | 0x08 | 20,400           | 6.25    |

| 115,200   | 3  | 0x01 | 163,200          | 41.67   |

#### **Fractional Divider**

The fractional divider, combined with the normal baud rate generator, produces a wider range of more accurate baud rates.

Figure 75. Baud Rate Generation Options

Calculation of the baud rate using fractional divider is as follows:

Baud Rate =

$$\frac{41.78 \text{ MHz}}{2^{CD} \times 16 \times DL \times 2 \times \left(M + \frac{N}{2048}\right)}$$

$$M + \frac{N}{2048} = \frac{41.78 \text{ MHz}}{\text{Baud Rate} \times 2^{CD} \times 16 \times \text{DL} \times 2}$$

For example, generation of 19,200 baud with CD bits = 3 (Table 93 gives DL = 0x08) is

$$M + \frac{N}{2048} = \frac{41.78 \text{ MHz}}{19200 \times 2^3 \times 16 \times 8 \times 2}$$

$$M + \frac{N}{2048} = 1.06$$

where:

M = 1 $N = 0.06 \times 2048 = 128$

## ADuC7019/20/21/22/24/25/26/27/28/29

Baud Rate =

$$\frac{41.78 \text{ MHz}}{2}$$

$$2^{3} \times 16 \times 8 \times 2 \times \frac{128}{2048}$$

where:

Baud Rate = 19,200 bps

Error = 0%, compared to 6.25% with the normal baud rate generator.

#### UART Register Definitions

The UART interface consists of 12 registers: COMTX, COMRX, COMDIV0, COMIEN0, COMDIV1, COMIID0, COMCON0, COMCON1, COMSTA0, COMSTA1, COMSCR, and COMDIV2.

#### Table 94. COMTX Register

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| COMTX | 0xFFFF0700 | 0x00          | R/W    |

COMTX is an 8-bit transmit register.

#### Table 95. COMRX Register

| Name  | Address    | Default Value | Access |

|-------|------------|---------------|--------|

| COMRX | 0xFFFF0700 | 0x00          | R      |

COMRX is an 8-bit receive register.

#### Table 96. COMDIV0 Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| COMDIV0 | 0xFFFF0700 | 0x00          | R/W    |

COMDIV0 is a low byte divisor latch. COMTX, COMRX, and COMDIV0 share the same address location. COMTX and COMRX can be accessed when Bit 7 in the COMCON0 register is cleared. COMDIV0 can be accessed when Bit 7 of COMCON0 is set.

#### Table 97. COMIEN0 Register

| Name Address |            | Default Value | Access |

|--------------|------------|---------------|--------|

| COMIEN0      | 0xFFFF0704 | 0x00          | R/W    |

COMIEN0 is the interrupt enable register.

#### Table 98. COMIEN0 MMR Bit Descriptions

| Bit | Name  | Description                                                                                                                                |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | N/A   | Reserved.                                                                                                                                  |

| 3   | EDSSI | Modem status interrupt enable bit. Set by user to enable generation of an interrupt if any of COMSTA1[3:1] is set. Cleared by user.        |

| 2   | ELSI  | Rx status interrupt enable bit. Set by user to enable generation of an interrupt if any of COMSTA0[4:1] is set. Cleared by user.           |

| 1   | ETBEI | Enable transmit buffer empty interrupt. Set<br>by user to enable interrupt when buffer is<br>empty during a transmission. Cleared by user. |

| 0   | ERBFI | Enable receive buffer full interrupt. Set by user to enable interrupt when buffer is full during a reception. Cleared by user.             |

#### Table 116. COMIID1 MMR Bit Descriptions

| Bit 3:1<br>Status<br>Bits | Bit 0<br>NINT | Priority | Definition                              | Clearing<br>Operation                     |

|---------------------------|---------------|----------|-----------------------------------------|-------------------------------------------|

| 000                       | 1             |          | No interrupt                            |                                           |

| 110                       | 0             | 2        | Matching network<br>address             | Read COMRX                                |

| 101                       | 0             | 3        | Address<br>transmitted,<br>buffer empty | Write data to<br>COMTX or<br>read COMIID0 |

| 011                       | 0             | 1        | Receive line status<br>interrupt        | Read<br>COMSTA0                           |

| 010                       | 0             | 2        | Receive buffer full<br>interrupt        | Read COMRX                                |

| 001                       | 0             | 3        | Transmit buffer<br>empty interrupt      | Write data to<br>COMTX or<br>read COMIID0 |

| 000                       | 0             | 4        | Modem status<br>interrupt               | Read<br>COMSTA1                           |

Note that to receive a network address interrupt, the slave must ensure that Bit 0 of COMIEN0 (enable receive buffer full interrupt) is set to 1.

#### Table 117. COMADR Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| COMADR | 0xFFFF0728 | 0xAA          | R/W    |

COMADR is an 8-bit, read/write network address register that holds the address checked for by the network addressable UART. Upon receiving this address, the device interrupts the processor and/or sets the appropriate status bit in COMIID1.

#### SERIAL PERIPHERAL INTERFACE

The ADuC7019/20/21/22/24/25/26/27/28/29 integrate a complete hardware serial peripheral interface (SPI) on-chip. SPI is an industry standard, synchronous serial interface that allows eight bits of data to be synchronously transmitted and simultaneously received, that is, full duplex up to a maximum bit rate of 3.48 Mb, as shown in Table 118. The SPI interface is not operational with core clock divider (CD) bits. POWCON[2:0] = 6 or 7 in master mode.

The SPI port can be configured for master or slave operation. and typically consists of four pins: MISO (P1.5), MOSI (P1.6), SCLK (P1.4), and  $\overline{CS}$  (P1.7).

On the transmit side, the SPITX register (and a TX shift register outside it) loads data onto the transmit pin (in slave mode, MISO; in master mode, MOSI). The transmit status bit, Bit 0, in SPISTA indicates whether there is valid data in the SPITX register.

Similarly, the receive data path consists of the SPIRX register (and an RX shift register). SPISTA, Bit 3 indicates whether there is valid data in the SPIRX register. If valid data in the SPIRX register is overwritten or if valid data in the RX shift register is discarded, SPISTA, Bit 5 (the overflow bit) is set.

#### MISO (Master In, Slave Out) Pin

The MISO pin is configured as an input line in master mode and an output line in slave mode. The MISO line on the master (data in) should be connected to the MISO line in the slave device (data out). The data is transferred as byte wide (8-bit) serial data, MSB first.

#### MOSI (Master Out, Slave In) Pin

The MOSI pin is configured as an output line in master mode and an input line in slave mode. The MOSI line on the master (data out) should be connected to the MOSI line in the slave device (data in). The data is transferred as byte wide (8-bit) serial data, MSB first.