Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | USI                                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 2KB (1K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 32-QFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny261-15md |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- I/O and packages

- 16 programmable I/O lines

- 20-pin SOIC, 32-pad MLF and 20-lead TSSOP

- Operating voltage:

- 2.7 5.5V for Atmel ATtiny261/461/861

- Speed grade:

- Atmel<sup>®</sup> ATtiny261/461/861: 0 8MHz at 2.7 5.5V, 0 16MHz at 4.5 5.5V

- Operating temperature: Automotive (-40°C to +125°C)

- Low power consumption

- Active mode ATD On: 1MHz, 2.7V, 25°C: 300µA

- Power-down mode no watchdog: 2.7V, 25°C: 0.12µA

### • Bit 2 – EEMPE: EEPROM Master Program Enable

The EEMPE bit determines whether writing EEPE to one will have effect or not.

When EEMPE is set, setting EEPE within four clock cycles will program the EEPROM at the selected address. If EEMPE is zero, setting EEPE will have no effect. When EEMPE has been written to one by software, hardware clears the bit to zero after four clock cycles.

#### • Bit 1 – EEPE: EEPROM Program Enable

The EEPROM program enable signal EEPE is the programming enable signal to the EEPROM. When EEPE is written, the EEPROM will be programmed according to the EEPMn bits setting. The EEMPE bit must be written to one before a logical one is written to EEPE, otherwise no EEPROM write takes place. When the write access time has elapsed, the EEPE bit is cleared by hardware. When EEPE has been set, the CPU is halted for two cycles before the next instruction is executed.

#### • Bit 0 – EERE: EEPROM Read Enable

The EEPROM read enable signal – EERE – is the read strobe to the EEPROM. When the correct address is set up in the EEAR register, the EERE bit must be written to one to trigger the EEPROM read. The EEPROM read access takes one instruction, and the requested data is available immediately. When the EEPROM is read, the CPU is halted for four cycles before the next instruction is executed. The user should poll the EEPE bit before starting the read operation. If a write operation is in progress, it is neither possible to read the EEPROM, nor to change the EEAR register.

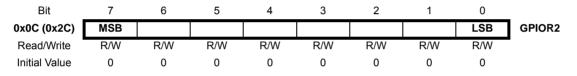

### 6.5.4 GPIOR2 – General Purpose I/O Register 2

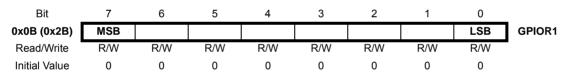

### 6.5.5 GPIOR1 – General Purpose I/O Register 1

### 6.5.6 GPIOR0 – General Purpose I/O Register 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |        |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| 0x0A (0x2A)   | MSB |     |     |     |     |     |     | LSB | GPIOR0 |

| Read/Write    | R/W | -      |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

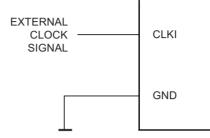

# 7.4 External Clock

To drive the device from an external clock source, CLKI should be driven as shown in Figure 7-3. To run the device on an external clock, the CKSEL fuses must be programmed to "0000".

### Figure 7-3. External Clock Drive Configuration

When this clock source is selected, start-up times are determined by the SUT fuses as shown in Table 7-3.

Table 7-3. Start-up Times for the External Clock Selection

| SUT10 | Start-up Time from Power-down and<br>Power-save | Additional Delay from Reset | Recommended Usage   |

|-------|-------------------------------------------------|-----------------------------|---------------------|

| 00    | 6CK                                             | 14CK                        | BOD enabled         |

| 01    | 6CK                                             | 14CK + 4ms                  | Fast rising power   |

| 10    | 6CK                                             | 14CK + 64ms                 | Slowly rising power |

| 11    |                                                 | Reserved                    |                     |

Note that the system clock prescaler can be used to implement run-time changes of the internal clock frequency while still ensuring stable operation. Refer to Section 7.11 "System Clock Prescaler" on page 31 for details.

# 7.5 High Frequency PLL Clock - PLL<sub>CLK</sub>

There is an internal PLL that provides nominally 64MHz clock rate locked to the RC oscillator for the use of the peripheral Timer/Counter1 and for the system clock source. When selected as a system clock source, by programming the CKSEL fuses to '0001', it is divided by four like shown in Table 7-4. When this clock source is selected, start-up times are determined by the SUT fuses as shown in Table 7-5. See also Section 7-2 "PCK Clocking System" on page 25.

### Table 7-4. PLLCK Operating Modes

| CKSEL30 | Nominal Frequency |

|---------|-------------------|

| 0001    | 16MHz             |

### Table 7-5. Start-up Times for the PLLCK

| SUT10 | Start-up Time from Power Down | Additional Delay from<br>Power-On-Reset (V <sub>CC</sub> = 5.0V) | Recommended Usage   |

|-------|-------------------------------|------------------------------------------------------------------|---------------------|

| 00    | 14CK + 1K (1024) + 4ms        | 4ms                                                              | BOD enabled         |

| 01    | 14CK + 16K (16384) + 4ms      | 4ms                                                              | Fast rising power   |

| 10    | 14CK + 1K (1024) + 64ms       | 4ms                                                              | Slowly rising power |

| 11    | 14CK + 16K (16384) + 64ms     | 4ms                                                              | Slowly rising power |

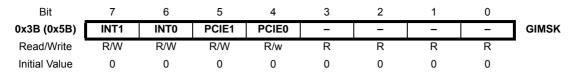

#### • Bit 7 - INT1: External Interrupt Request 1 Enable

When the INT1 bit is set (one) and the I-bit in the status register (SREG) is set (one), the external pin interrupt is enabled. The interrupt sense control0 bits 1/0 (ISC01 and ISC00) in the MCU control register (MCUCR) define whether the external interrupt is activated on rising and/or falling edge of the INT1 pin or level sensed. Activity on the pin will cause an interrupt request even if INT1 is configured as an output. The corresponding interrupt of external interrupt request 1 is executed from the INT1 interrupt vector.

#### • Bit 6 – INT0: External Interrupt Request 0 Enable

When the INT0 bit is set (one) and the I-bit in the status register (SREG) is set (one), the external pin interrupt is enabled. The interrupt sense control0 bits 1/0 (ISC01 and ISC00) in the MCU control register (MCUCR) define whether the external interrupt is activated on rising and/or falling edge of the INT0 pin or level sensed. Activity on the pin will cause an interrupt request even if INT0 is configured as an output. The corresponding interrupt of external interrupt request 0 is executed from the INT0 interrupt vector.

#### • Bit 5 – PCIE1: Pin Change Interrupt Enable

When the PCIE1 bit is set (one) and the I-bit in the status register (SREG) is set (one), pin change interrupt is enabled. Any change on any enabled PCINT7..0 or PCINT15..12 pin will cause an interrupt. The corresponding interrupt of pin change interrupt request is executed from the PCI interrupt vector. PCINT7..0 and PCINT15..12 pins are enabled individually by the PCMSK0 and PCMSK1 register.

#### • Bit 4 – PCIE0: Pin Change Interrupt Enable

When the PCIE0 bit is set (one) and the I-bit in the status register (SREG) is set (one), pin change interrupt is enabled. Any change on any enabled PCINT11..8 pin will cause an interrupt. The corresponding interrupt of pin change interrupt request is executed from the PCI interrupt vector. PCINT11..8 pins are enabled individually by the PCMSK1 register.

### • Bits 3..0 - Res: Reserved Bits

These bits are reserved bits in the Atmel<sup>®</sup> ATtiny261/461/861 and will always read as zero.

### 11.1.3 GIFR – General Interrupt Flag Register

| Bit           | 7    | 6     | 5    | 4 | 3 | 2 | 1 | 0 |      |

|---------------|------|-------|------|---|---|---|---|---|------|

| 0x3A (0x5A)   | INT1 | INTF0 | PCIF | - | - | - | _ | - | GIFR |

| Read/Write    | R/W  | R/W   | R/W  | R | R | R | R | R | -    |

| Initial Value | 0    | 0     | 0    | 0 | 0 | 0 | 0 | 0 |      |

### • Bit 7– INTF1: External Interrupt Flag 1

When an edge or logic change on the INT1 pin triggers an interrupt request, INTF1 becomes set (one). If the I-bit in SREG and the INT1 bit in GIMSK are set (one), the MCU will jump to the corresponding interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INT1 is configured as a level interrupt.

#### • Bit 6 – INTF0: External Interrupt Flag 0

When an edge or logic change on the INTO pin triggers an interrupt request, INTFO becomes set (one). If the I-bit in SREG and the INTO bit in GIMSK are set (one), the MCU will jump to the corresponding interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INTO is configured as a level interrupt.

### 14.2.1 Registers

The Timer/Counter0 low byte register (TCNT0L) and output compare registers (OCR0A and OCR0B) are 8-bit registers. Interrupt request (abbreviated to Int.Req. in Figure 14-1) signals are all visible in the timer interrupt flag register (TIFR). All interrupts are individually masked with the timer interrupt mask register (TIMSK). TIFR and TIMSK are not shown in the figure.

In 16-bit mode the Timer/Counter consists one more 8-bit register, the Timer/Counter0 high byte register (TCNT0H). Furthermore, there is only one output compare unit in 16-bit mode as the two output compare registers, OCR0A and OCR0B, are combined to one 16-bit output compare register.

OCR0A contains the low byte of the word and OCR0B contains the high byte of the word. When accessing 16-bit registers, special procedures described in Section 14.9 "Accessing Registers in 16-bit Mode" on page 76 must be followed.

### 14.2.2 Definitions

Many register and bit references in this section are written in general form. A lower case "n" replaces the Timer/Counter number, in this case 0. A lower case "x" replaces the output compare unit, in this case compare unit A or compare unit B. However, when using the register or bit defines in a program, the precise form must be used, i.e., TCNT0L for accessing Timer/Counter0 counter value and so on.

The definitions in Table 14-1 are also used extensively throughout the document.

| Parameter | Definition                                                                                                                                                                                                     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOTTOM    | The counter reaches the BOTTOM when it becomes 0.                                                                                                                                                              |

| MAX       | The counter reaches its MAXimum when it becomes 0xFF (decimal 255) in 8-bit mode or 0xFFFF (decimal 65535) in 16-bit mode.                                                                                     |

| ТОР       | The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF/0xFFFF (MAX) or the value stored in the OCR0A register. |

#### Table 14-1. Definitions

### 14.3 Timer/Counter Clock Sources

The Timer/Counter can be clocked internally, via the prescaler, or by an external clock source on the T0 pin. The clock select logic is controlled by the Clock Select (CS02:0) bits located in the Timer/Counter control register 0 B (TCCR0B), and controls which clock source and edge the Timer/Counter uses to increment its value. The Timer/Counter is inactive when no clock source is selected. The output from the clock select logic is referred to as the timer clock ( $clk_{T0}$ ). For details on clock sources and prescaler, see Section 13. "Timer/Counter0 Prescaler" on page 66.

The following code examples show how to access the 16-bit timer registers assuming that no interrupts updates the temporary register. The same principle can be used directly for accessing the OCR0A/B registers.

| Assembly Code Example             |

|-----------------------------------|

|                                   |

| ; Set TCNT0 to 0x01FF             |

| <b>ldi</b> r17,0x01               |

| ldi r16,0xFF                      |

| out TCNTOH,r17                    |

| out TCNTOL,r16                    |

| ; Read TCNT <b>0</b> into r17:r16 |

| in r16,TCNTOL                     |

| in r17,TCNTOH                     |

|                                   |

| C Code Example                    |

| unsigned int i;                   |

|                                   |

| /* Set TCNT0 to 0x01FF */         |

| TCNT0H = 0x01;                    |

| TCNTOL = 0xff;                    |

| /* Read TCNT0 into i */           |

| i = TCNTOL;                       |

| i  = ((unsigned int)TCNTOH << 8); |

|                                   |

The example code assumes that the part specific header file is included. For I/O registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The assembly code example returns the TCNT0H/L value in the r17:r16 register pair.

It is important to notice that accessing 16-bit registers are atomic operations. If an interrupt occurs between the two instructions accessing the 16-bit register, and the interrupt code updates the temporary register by accessing the same or any other of the 16-bit timer registers, then the result of the access outside the interrupt will be corrupted. Therefore, when both the main code and the interrupt code update the temporary register, the main code must disable the interrupts during the 16-bit access.

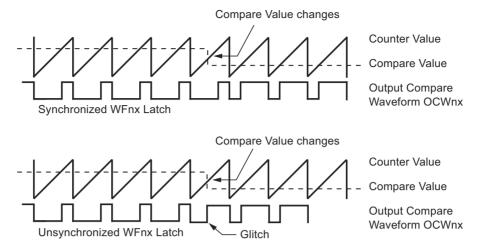

Figure 16-5. Effects of Unsynchronized OCR Latching

### 16.4.1 Force Output Compare

In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the force output compare (FOC1x) bit. Forcing compare match will not set the OCF1x flag or reload/clear the timer, but the waveform output (OCW1x) will be updated as if a real compare match had occurred (the COM1x1:0 bits settings define whether the waveform output (OCW1x) is set, cleared or toggled).

### 16.4.2 Compare Match Blocking by TCNT1 Write

All CPU write operations to the TCNT1 register will block any compare match that occur in the next timer clock cycle, even when the timer is stopped. This feature allows OCR1x to be initialized to the same value as TCNT1 without triggering an interrupt when the Timer/Counter clock is enabled.

### 16.4.3 Using the Output Compare Unit

Since writing TCNT1 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT1 when using the output compare unit, independently of whether the Timer/Counter is running or not. If the value written to TCNT1 equals the OCR1x value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT1 value equal to BOTTOM when the counter is down-counting.

The setup of the waveform Output (OCW1x) should be performed before setting the data direction register for the port pin to output. The easiest way of setting the OCW1x value is to use the force output compare (FOC1x) strobe bits in normal mode. The OC1x keeps its value even when changing between waveform generation modes.

Be aware that the COM1x1:0 bits are not double buffered together with the compare value. Changing the COM1x1:0 bits will take effect immediately.

Figure 16-9. Compare Match Output Unit, Schematic

96 ATtiny261/ATtiny461/ATtiny861/ATtiny461 [DATASHEET] 7753G-AVR-06/14

Atmel

The Timer/Counter overflow flag (TOV1) is set each time the counter reaches TOP. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

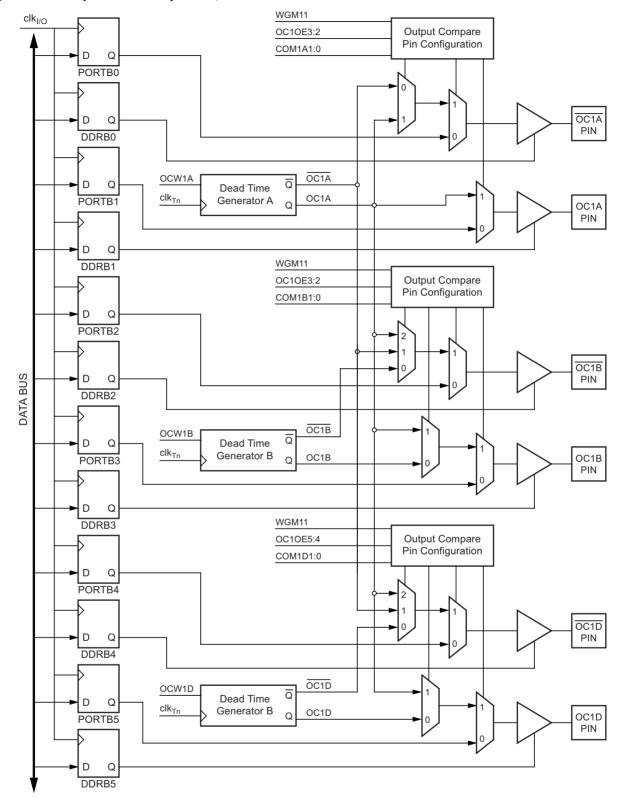

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC1x pins. Setting the COM1x1:0 bits to two will produce a non-inverted PWM and setting the COM1x1:0 to three will produce an inverted PWM output. Setting the COM1x1:0 bits to one will enable complementary compare output mode and produce both the non-inverted (OC1x) and inverted output (OC1x). The actual value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the waveform output (OCW1x) at the compare match between OCR1x and TCNT1, and clearing (or setting) the waveform output at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{\text{clkT1}}}{N}$$

The *N* variable represents the number of steps in single-slope operation. The value of *N* equals either to the TOP value.

The extreme values for the OCR1C register represents special cases when generating a PWM waveform output in the fast PWM mode. If the OCR1C is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR1C equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM1x1:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting the waveform output (OCW1x) to toggle its logical level on each Compare Match (COM1x1:0 = 1). The waveform generated will have a maximum frequency of  $f_{OC1} = f_{clkT1}/4$  when OCR1C is set to three.

The general I/O port function is overridden by the output compare value (OC1x / OC1x) from the dead time generator, if either of the COM1x1:0 bits are set and the data direction register bits for the OC1X and OC1X pins are set as an output. If the COM1x1:0 bits are cleared, the actual value from the port register will be visible on the port pin. The output compare pin configurations are described in Table 16-3.

| COM1x1 | COM1x0 | OC1x Pin     | OC1x Pin     |

|--------|--------|--------------|--------------|

| 0      | 0      | Disconnected | Disconnected |

| 0      | 1      | OC1x         | OC1x         |

| 1      | 0      | Disconnected | OC1x         |

| 1      | 1      | Disconnected | OC1x         |

Table 16-3. Output Compare Pin Configurations in Fast PWM Mode

### 16.7.3 Phase and Frequency Correct PWM Mode

The phase and frequency correct PWM mode (PWMx = 1 and WGM10 = 1) provides a high resolution phase and frequency correct PWM waveform generation option. The phase and frequency correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to TOP (defined as OCR1C) and then from TOP to BOTTOM. In non-inverting compare output mode the waveform output (OCW1x) is cleared on the compare match between TCNT1 and OCR1x while upcounting, and set on the compare match while down-counting. In inverting output compare mode, the operation is inverted. In complementary compare output mode, the waveform output is cleared on the compare match and set at BOTTOM. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The timing diagram for the phase and frequency correct PWM mode is shown on Figure 16-12 in which the TCNT1 value is shown as a histogram for illustrating the dual-slope operation. The counter is incremented until the counter value matches TOP. When the counter reaches TOP, it changes the count direction. The TCNT1 value will be equal to TOP for one timer clock cycle. The diagram includes the waveform output (OCW1x) in non-inverted and inverted compare output mode. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1.

## 16.11 Register Description

### 16.11.1 TCCR1A – Timer/Counter1 Control Register A

| Bit           | 7      | 6      | 5      | 4      | 3     | 2     | 1     | 0     |        |

|---------------|--------|--------|--------|--------|-------|-------|-------|-------|--------|

| 0x30 (0x50)   | COM1A1 | COM1A0 | COM1B1 | COM1B0 | FOC1A | FOC1B | PWM1A | PWM1B | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | W     | W     | R/W   | R/W   |        |

| Initial value | 0      | 0      | 0      | 0      | 0     | 0     | 0     | 0     |        |

#### • Bits 7,6 - COM1A1, COM1A0: Comparator A Output Mode, Bits 1 and 0

These bits control the behavior of the waveform output (OCW1A) and the connection of the output compare pin (OC1A). If one or both of the COM1A1:0 bits are set, the OC1A output overrides the normal port functionality of the I/O pin it is connected to. The complementary OC1B output is connected only in PWM modes when the COM1A1:0 bits are set to "01". Note that the data direction register (DDR) bit corresponding to the OC1A and OC1A pins must be set in order to enable the output driver.

The function of the COM1A1:0 bits depends on the PWM1A, WGM10 and WGM11 bit settings. Table 16-6 shows the COM1A1:0 bit functionality when the PWM1A bit is set to normal mode (non-PWM).

#### Table 16-6. Compare Output Mode, Normal Mode (non-PWM)

| COM1A10 | OCW1A Behavior          | OC1A Pin     | OC1A Pin     |

|---------|-------------------------|--------------|--------------|

| 00      | Normal port operation   | Disconnected | Disconnected |

| 01      | Toggle on compare match | Connected    | Disconnected |

| 10      | Clear on compare match  | Connected    | Disconnected |

| 11      | Set on compare match    | Connected    | Disconnected |

Table 16-7 shows the COM1A1:0 bit functionality when the PWM1A, WGM10 and WGM11 bits are set to fast PWM mode.

| Table 16-7. Con | npare Output | Mode, F | Fast PWM | Mode |

|-----------------|--------------|---------|----------|------|

|-----------------|--------------|---------|----------|------|

| COM1A10 | OCW1A Behavior                                     | OC1A         | OC1A         |

|---------|----------------------------------------------------|--------------|--------------|

| 00      | Normal port operation                              | Disconnected | Disconnected |

| 01      | Cleared on compare match<br>Set when TCNT1 = 0x000 | Connected    | Connected    |

| 10      | Cleared on compare match<br>Set when TCNT1 = 0x000 | Connected    | Disconnected |

| 11      | Set on compare match<br>Cleared when TCNT1 = 0x000 | Connected    | Disconnected |

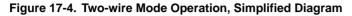

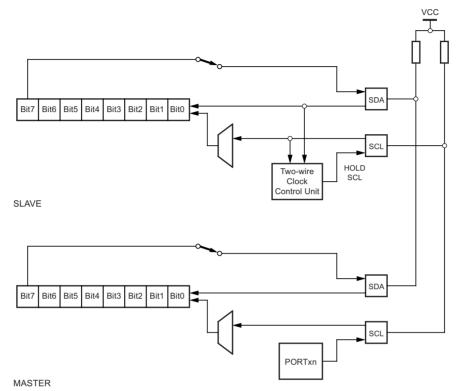

### 17.3.4 Two-wire Mode

The USI two-wire mode is compliant to the Inter IC (TWI) bus protocol, but without slew rate limiting on outputs and input noise filtering. Pin names used by this mode are SCL and SDA.

Figure 17-4 shows two USI units operating in two-wire mode, one as master and one as slave. It is only the physical layer that is shown since the system operation is highly dependent of the communication scheme used. The main differences between the master and slave operation at this level, is the serial clock generation which is always done by the master, and only the slave uses the clock control unit. Clock generation must be implemented in software, but the shift operation is done automatically by both devices. Note that only clocking on negative edge for shifting data is of practical use in this mode. The slave can insert wait states at start or end of transfer by forcing the SCL clock low. This means that the master must always check if the SCL line was actually released after it has generated a positive edge.

Since the clock also increments the counter, a counter overflow can be used to indicate that the transfer is completed. The clock is generated by the master by toggling the USCK pin via the PORT register.

The data direction is not given by the physical layer. A protocol, like the one used by the TWI-bus, must be implemented to control the data flow.

# 19.3 Operation

The ADC converts an analog input voltage to a 10-bit digital value through successive approximation. The minimum value represents GND and the maximum value represents the voltage on  $V_{CC}$ , the voltage on the AREF pin or an internal 1.1V/2.56V voltage reference.

The voltage reference for the ADC may be selected by writing to the REFS2..0 bits in ADMUX. The VCC supply, the AREF pin or an internal 1.1V / 2.56V voltage reference may be selected as the ADC voltage reference. Optionally the internal 1.1V/2.56V voltage reference may be decoupled by an external capacitor at the AREF pin to improve noise immunity.

The analog input channel and differential gain are selected by writing to the MUX5..0 bits in ADMUX. Any of the 11 ADC input pins ADC10..0 can be selected as single ended inputs to the ADC. The positive and negative inputs to the differential gain amplifier are described in Table 19-5 on page 145.

If differential channels are selected, the differential gain stage amplifies the voltage difference between the selected input pair by the selected gain factor, 1x, 8x, 20x or 32x, according to the setting of the MUX5..0 bits in ADMUX and the GSEL bit in ADCSRB. This amplified value then becomes the analog input to the ADC. If single ended channels are used, the gain amplifier is bypassed altogether.

If the same ADC input pin is selected as both the positive and negative input to the differential gain amplifier, the remaining offset in the gain stage and conversion circuitry can be measured directly as the result of the conversion. This figure can be subtracted from subsequent conversions with the same gain setting to reduce offset error to below 1 LSW.

The on-chip temperature sensor is selected by writing the code "111111" to the MUX5..0 bits in ADMUX register when the ADC11 channel is used as an ADC input.

The ADC is enabled by setting the ADC Enable bit, ADEN in ADCSRA. Voltage reference and input channel selections will not go into effect until ADEN is set. The ADC does not consume power when ADEN is cleared, so it is recommended to switch off the ADC before entering power saving sleep modes.

The ADC generates a 10-bit result which is presented in the ADC data registers, ADCH and ADCL. By default, the result is presented right adjusted, but can optionally be presented left adjusted by setting the ADLAR bit in ADMUX.

If the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the data registers belongs to the same conversion. Once ADCL is read, ADC access to data registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is read, neither register is updated and the result from the conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL registers is re-enabled.

The ADC has its own interrupt which can be triggered when a conversion completes. When ADC access to the data registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost.

### 19.4 Starting a Conversion

A single conversion is started by writing a logical one to the ADC start conversion bit, ADSC. This bit stays high as long as the conversion is in progress and will be cleared by hardware when the conversion is completed. If a different data channel is selected while a conversion is in progress, the ADC will finish the current conversion before performing the channel change.

Alternatively, a conversion can be triggered automatically by various sources. Auto triggering is enabled by setting the ADC auto trigger enable bit, ADATE in ADCSRA. The trigger source is selected by setting the ADC trigger select bits, ADTS in ADCSRB (see description of the ADTS bits for a list of the trigger sources). When a positive edge occurs on the selected trigger signal, the ADC prescaler is reset and a conversion is started. This provides a method of starting conversions at fixed intervals. If the trigger signal still is set when the conversion completes, a new conversion will not be started. If another positive edge occurs on the trigger signal during conversion, the edge will be ignored. Note that an interrupt flag will be set even if the specific interrupt is disabled or the global interrupt enable bit in SREG is cleared. A conversion can thus be triggered without causing an interrupt. However, the interrupt flag must be cleared in order to trigger a new conversion at the next interrupt event.

# **19.7 ADC Noise Canceler**

The ADC features a noise canceler that enables conversion during sleep mode to reduce noise induced from the CPU core and other I/O peripherals. The noise canceler can be used with ADC Noise Reduction and Idle mode. To make use of this feature, the following procedure should be used:

- a. Make sure that the ADC is enabled and is not busy converting. Single conversion mode must be selected and the ADC conversion complete interrupt must be enabled.

- b. Enter ADC noise reduction mode (or Idle mode). The ADC will start a conversion once the CPU has been halted.

- c. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the CPU and execute the ADC conversion complete interrupt routine. If another interrupt wakes up the CPU before the ADC conversion is complete, that interrupt will be executed, and an ADC conversion complete interrupt request will be generated when the ADC conversion completes. The CPU will remain in active mode until a new sleep command is executed.

Note that the ADC will not be automatically turned off when entering other sleep modes than Idle mode and ADC noise reduction mode. The user is advised to write zero to ADEN before entering such sleep modes to avoid excessive power consumption.

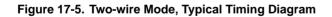

### 19.7.1 Analog Input Circuitry

The analog input circuitry for single ended channels is illustrated in Figure 19-8 An analog source applied to ADCn is subjected to the pin capacitance and input leakage of that pin, regardless of whether that channel is selected as input for the ADC. When the channel is selected, the source must drive the S/H capacitor through the series resistance (combined resistance in the input path).

The ADC is optimized for analog signals with an output impedance of approximately  $10k\Omega$  or less. If such a source is used, the sampling time will be negligible. If a source with higher impedance is used, the sampling time will depend on how long time the source needs to charge the S/H capacitor, with can vary widely. The user is recommended to only use low impedent sources with slowly varying signals, since this minimizes the required charge transfer to the S/H capacitor.

Signal components higher than the Nyquist frequency ( $f_{ADC}/2$ ) should not be present to avoid distortion from unpredictable signal convolution. The user is advised to remove high frequency components with a low-pass filter before applying the signals as inputs to the ADC.

#### Figure 19-8. Analog Input Circuitry

### 19.7.2 Analog Noise Canceling Techniques

Digital circuitry inside and outside the device generates EMI which might affect the accuracy of analog measurements. If conversion accuracy is critical, the noise level can be reduced by applying the following techniques:

- a. Keep analog signal paths as short as possible. Make sure analog tracks run over the analog ground plane, and keep them well away from high-speed switching digital tracks.

- b. Use the ADC noise canceler function to reduce induced noise from the CPU.

- c. If any port pins are used as digital outputs, it is essential that these do not switch while a conversion is in progress.

## Table 19-5. Input Channel Selections

| MUX50  | Single Ended Input | Positive Differential<br>Input | Negative Differential<br>Input | Gain    |

|--------|--------------------|--------------------------------|--------------------------------|---------|

| 000000 | ADC0 (PA0)         |                                |                                |         |

| 000001 | ADC1 (PA1)         |                                |                                |         |

| 000010 | ADC2 (PA2)         |                                |                                |         |

| 000011 | ADC3 (PA4)         |                                |                                |         |

| 000100 | ADC4 (PA5)         |                                |                                |         |

| 000101 | ADC5 (PA6)         | NA                             | NA                             | NA      |

| 000110 | ADC6 (PA7)         |                                |                                |         |

| 000111 | ADC7 (PB4)         |                                |                                |         |

| 001000 | ADC8 (PB5)         |                                |                                |         |

| 001001 | ADC9 (PB6)         |                                |                                |         |

| 001010 | ADC10 (PB7)        |                                |                                |         |

| 001011 |                    | ADC0 (PA0)                     | ADC1 (PA1)                     | 20x     |

| 001100 |                    | ADC0 (PA0)                     | ADC1 (PA1)                     | 1x      |

| 001101 | NA                 | ADC1 (PA1)                     | ADC1 (PA1)                     | 20x     |

| 001110 |                    | ADC2 (PA2)                     | ADC1 (PA1)                     | 20x     |

| 001111 |                    | ADC2 (PA2)                     | ADC1 (PA1)                     | 1x      |

| 010000 |                    | ADC2 (PA2)                     | ADC3 (PA4)                     | 1x      |

| 010001 | N1/A               | ADC3 (PA4)                     | ADC3 (PA4)                     | 20x     |

| 010010 | N/A                | ADC4 (PA5)                     | ADC3 (PA4)                     | 20x     |

| 010011 |                    | ADC4 (PA5)                     | ADC3 (PA4)                     | 1x      |

| 010100 |                    | ADC4 (PA5)                     | ADC5 (PA6)                     | 20x     |

| 010101 |                    | ADC4 (PA5)                     | ADC5 (PA6)                     | 1x      |

| 010110 | NA                 | ADC5 (PA6)                     | ADC5 (PA6)                     | 20x     |

| 010111 |                    | ADC6 (PA7)                     | ADC5 (PA6)                     | 20x     |

| 011000 | _                  | ADC6 (PA7)                     | ADC5 (PA6)                     | 1x      |

| 011001 |                    | ADC8 (PB5)                     | ADC9 (PB6)                     | 20x     |

| 011010 | -                  | ADC8 (PB5)                     | ADC9 (PB6)                     | 1x      |

| 011011 | NA                 | ADC9 (PB6)                     | ADC9 (PB6)                     | 20x     |

| 011100 |                    | ADC10 (PB7)                    | ADC9 (PB6)                     | 20x     |

| 011101 |                    | ADC10 (PB7)                    | ADC9 (PB6)                     | 1x      |

| 011110 | 1.1V               | N/A                            | N/A                            | N/A     |

| 011111 | 0V                 | IN/A                           | IN/A                           | IN/A    |

| 100000 |                    | ADC0(PA0)                      | ADC1(PA1)                      | 20x/32x |

| 100001 | N/A                | ADC0(PA0)                      | ADC1(PA1)                      | 1x/8x   |

| 100010 | IN/A               | ADC1(PA1                       | ADC0(PA0)                      | 20x/32x |

| 100011 |                    | ADC1(PA1)                      | ADC0(PA0)                      | 1x/8x   |

| 100100 |                    | ADC1(PA1)                      | ADC2(PA2)                      | 20x/32x |

| 100101 | N/A                | ADC1(PA1)                      | ADC2(PA2)                      | 1x/8x   |

| 100110 | IN/A               | ADC2(PA2                       | ADC1(PA1)                      | 20x/32x |

| 100111 |                    | ADC2(PA2)                      | ADC1(PA1)                      | 1x/8x   |

Note: 1. For temperature sensor

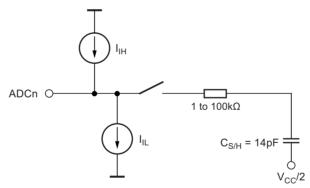

# 22.9 Serial Downloading

Both the flash and EEPROM memory arrays can be programmed using the serial SPI bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI (input) and MISO (output). After RESET is set low, the programming enable instruction needs to be executed first before program/erase operations can be executed. NOTE, in Table 22-13 on page 167, the pin mapping for SPI programming is listed. Not all parts use the SPI pins dedicated for the internal SPI interface.

#### Figure 22-7. Serial Programming and Verify<sup>(1)</sup>

Note: 1. If the device is clocked by the internal oscillator, it is no need to connect a clock source to the CLKI pin.

Table 22-13. Pin Mapping Serial Programming

| Symbol | Pins | I/O | Description     |

|--------|------|-----|-----------------|

| MOSI   | PB0  | I   | Serial data in  |

| MISO   | PB1  | 0   | Serial data out |

| SCK    | PB2  | I   | Serial clock    |

When programming the EEPROM, an auto-erase cycle is built into the self-timed programming operation (in the serial mode ONLY) and there is no need to first execute the chip erase instruction. The chip erase operation turns the content of every memory location in both the Program and EEPROM arrays into 0xFF.

Depending on CKSEL fuses, a valid clock must be present. The minimum low and high periods for the serial clock (SCK) input are defined as follows:

Low: > 2 CPU clock cycles for  $f_{ck}$  < 12MHz, 3 CPU clock cycles for  $f_{ck} \ge$  12MHz

High: > 2 CPU clock cycles for  $f_{ck}$  < 12MHz, 3 CPU clock cycles for  $f_{ck} \ge$  12MHz

# 23. Electrical Characteristics

# 23.1 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                             | Min. | Тур.                | Max.                  | Unit |

|--------------------------------------------------------|------|---------------------|-----------------------|------|

| Operating temperature                                  | -55  |                     | +125                  | °C   |

| Storage temperature                                    | -65  |                     | +150                  | °C   |

| Voltage on any pin except RESET with respect to ground | -0.5 |                     | V <sub>CC</sub> + 0.5 | V    |

| Voltage on RESET with respect to ground                | -0.5 |                     | +13.0                 | V    |

| Maximum operating voltage                              |      | 6.0                 |                       | V    |

| DC current per I/O pin                                 |      | 40.0                |                       | mA   |

| DC current V <sub>CC</sub> and GND pins                |      | 200.0               |                       | mA   |

| Injection current at V <sub>CC</sub> = 0V              |      | ±5.0 <sup>(1)</sup> |                       | mA   |

| Injection current at $V_{CC}$ = 5V                     |      | ±1.0                |                       | mA   |

Notes: 1. Maximum current per port = ±30mA

# 23.2 DC Characteristics

$T_A = -40^{\circ}$ C to +125°C,  $V_{CC} = 2.7$ V to 5.5V (unless otherwise noted)<sup>(1)</sup>

| Parameter          | Condition                          | Symbol           | Min.                              | Тур. | Max.                  | Unit |

|--------------------|------------------------------------|------------------|-----------------------------------|------|-----------------------|------|

| Input low-voltage  | Except XTAL1 and RESET pin         | V <sub>IL</sub>  | -0.5                              |      | 0.2V <sub>CC</sub>    | V    |

| Input high-voltage | Except XTAL1 and RESET pin         | V <sub>IH</sub>  | 0.7V <sub>CC</sub> <sup>(3)</sup> |      | V <sub>CC</sub> + 0.5 | V    |

| Input low-voltage  | XTAL1 pin, external clock selected | V <sub>IL1</sub> | -0.5                              |      | 0.1V <sub>CC</sub>    | V    |

| Input high-voltage | XTAL1 pin, external clock selected | V <sub>IH1</sub> | 0.8V <sub>CC</sub> <sup>(3)</sup> |      | V <sub>CC</sub> + 0.5 | V    |

| Input low-voltage  | RESET pin                          | V <sub>IL2</sub> | -0.5                              |      | 0.2V <sub>CC</sub>    | V    |

| Input high-voltage | RESET pin                          | V <sub>IH2</sub> | 0.9V <sub>CC</sub> <sup>(3)</sup> |      | V <sub>CC</sub> + 0.5 | V    |

| Input low-voltage  | RESET pin as I/O                   | V <sub>IL3</sub> | -0.5                              |      | 0.2V <sub>CC</sub>    | V    |

| Input high-voltage | RESET pin as I/O                   | V <sub>IH3</sub> | 0.7V <sub>CC</sub> <sup>(3)</sup> |      | V <sub>CC</sub> + 0.5 | V    |

Notes: 1. All DC characteristics contained in this data sheet are based on simulation and characterization of ATtiny261/461/861 AVR microcontrollers manufactured in a typical process technology. These values are preliminary values representing design targets, and will be updated after characterization of actual automotive silicon.

2. "Max" means the highest value where the pin is guaranteed to be read as low.

- 3. "Min" means the lowest value where the pin is guaranteed to be read as high.

- Although each I/O port can sink more than the test conditions (10mA at V<sub>CC</sub> = 5V, 5mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all IOL, for all ports, should not exceed 60mA.

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

Although each I/O port can source more than the test conditions (10mA at V<sub>CC</sub> = 5V, 5mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all IOH, for all ports, should not exceed 60mA.

If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

- 6. Values using methods described in Section 8.7 "Minimizing Power Consumption" on page 35. Power reduction is enabled (PRR = 0xFF) and there is no I/O drive.

- 7. BOD disabled.

### 23.4.3 External Clock Drive

#### Table 23-2. External Clock Drive

|                                                   |                     | V <sub>CC</sub> = 2 | 2.7 - 5.5V | $V_{CC} = 4$ | l.5 - 5.5V |      |

|---------------------------------------------------|---------------------|---------------------|------------|--------------|------------|------|

| Parameter                                         | Symbol              | Min.                | Max.       | Min.         | Max.       | Unit |

| Clock frequency                                   | 1/t <sub>CLCL</sub> | 0                   | 8          | 0            | 16         | MHz  |

| Clock period                                      | t <sub>CLCL</sub>   | 125                 |            | 62.5         |            | ns   |

| High time                                         | t <sub>CHCX</sub>   | 40                  |            | 20           |            | ns   |

| Low time                                          | t <sub>CLCX</sub>   | 40                  |            | 20           |            | ns   |

| Rise time                                         | t <sub>CLCH</sub>   |                     | 1.6        |              | 0.5        | μs   |

| Fall time                                         | t <sub>CHCL</sub>   |                     | 1.6        |              | 0.5        | μs   |

| Change in period from one clock cycle to the next | $\Delta t_{CLCL}$   |                     | 2          |              | 2          | %    |

### 23.5 System and Reset Characteristics

### Table 23-3. Reset, Brown-out and Internal Voltage Characteristics<sup>(1)</sup>

| Parameter                             | Condition                                     | Symbol            | Min | Тур | Max | Unit |

|---------------------------------------|-----------------------------------------------|-------------------|-----|-----|-----|------|

| Minimum pulse width on RESET pin      | V <sub>CC</sub> = 3V                          | t <sub>RST</sub>  |     |     | 2.5 | μs   |

| Brown-out detector hysteresis         |                                               | V <sub>HYST</sub> |     | 50  |     | mV   |

| Min pulse width on brown-out reset    |                                               | t <sub>BOD</sub>  |     | 2   |     | μs   |

| Bandgap reference voltage             | V <sub>CC</sub> = 3.0V, T <sub>A</sub> = 25°C | V <sub>BG</sub>   | 1.0 | 1.1 | 1.2 | V    |

| Bandgap reference start-up time       | V <sub>CC</sub> = 2.7V, T <sub>A</sub> = 25°C | t <sub>BG</sub>   |     | 40  | 70  | μs   |

| Bandgap reference current consumption | $V_{CC}$ = 2.7V, $T_{A}$ = 25°C               | I <sub>BG</sub>   |     | 15  |     | μA   |

Notes: 1. Values are guidelines only.

### Table 23-4. BODLEVEL Fuse Coding<sup>(1)</sup>

| BODLEVEL [20] Fuses | Min V <sub>BOT</sub> | Тур V <sub>вот</sub> | Max V <sub>BOT</sub> | Unit |

|---------------------|----------------------|----------------------|----------------------|------|

| 111                 | BOD disabled         |                      |                      |      |

| 110                 | 1.68                 | 1.8                  | 1.92                 |      |

| 101                 | 2.5                  | 2.7                  | 2.9                  | V    |

| 100                 | 4.0                  | 4.3                  | 4.6                  |      |

| 011                 |                      |                      |                      |      |

| 010                 | Descend              |                      |                      |      |

| 001                 | Reserved             |                      |                      |      |

| 000                 |                      |                      |                      |      |

Note: 1. V<sub>BOT</sub> may be below nominal minimum operating voltage for some devices. For devices where this is the case, the device is tested down to V<sub>CC</sub> = V<sub>BOT</sub> during the production test. This guarantees that a brown-out reset will occur before V<sub>CC</sub> drops to a voltage where correct operation of the microcontroller is no longer guaranteed.

# 24.9 Internal Oscillator Speed

Figure 24-19. Watchdog Oscillator Frequency versus Temperature

Figure 24-20. Calibrated 8.0MHz RC Oscillator Frequency versus Temperature

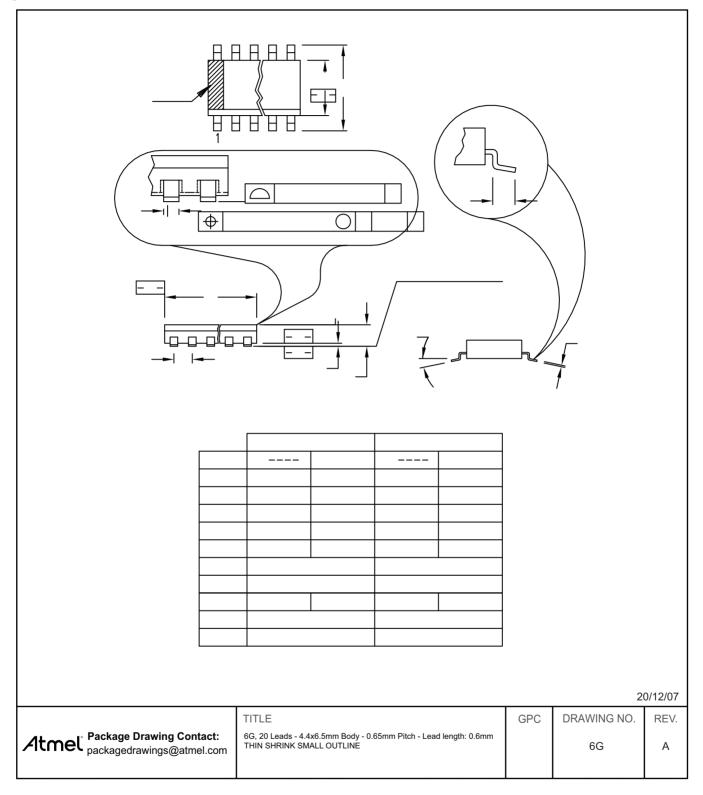

Figure 28-3. 6G

| 23.4                                                                                                                                             | Clock Characteristics                      | 173                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23.5                                                                                                                                             | System and Reset Characteristics.          | 174                                                                                                                                                       |

| 23.6                                                                                                                                             | ADC Characteristics                        | 175                                                                                                                                                       |

| 23.7                                                                                                                                             | Parallel Programming Characteristics       | 177                                                                                                                                                       |

| 23.8                                                                                                                                             | Serial Programming Characteristics         | 179                                                                                                                                                       |

| 24. T                                                                                                                                            | pical Characteristics                      | 180                                                                                                                                                       |

| 24.1                                                                                                                                             | Active Supply Current                      | 180                                                                                                                                                       |

| 24.2                                                                                                                                             | Idle Supply Current                        | 181                                                                                                                                                       |

| 24.3                                                                                                                                             | Supply Current of I/O Modules              | 182                                                                                                                                                       |

| 24.4                                                                                                                                             | Power-down Supply Current                  | 183                                                                                                                                                       |

| 24.5                                                                                                                                             | Pin Pull-up                                | 183                                                                                                                                                       |

| 24.6                                                                                                                                             | Pin Driver Strength                        | 184                                                                                                                                                       |

| 24.7                                                                                                                                             | Pin Threshold and Hysteresis               |                                                                                                                                                           |

| 24.8                                                                                                                                             | BOD Threshold and Analog Comparator Offset | 187                                                                                                                                                       |

| 24.9                                                                                                                                             | Internal Oscillator Speed                  | 188                                                                                                                                                       |

|                                                                                                                                                  |                                            |                                                                                                                                                           |

| 25. R                                                                                                                                            | egister Summary                            |                                                                                                                                                           |

|                                                                                                                                                  | •                                          | 189                                                                                                                                                       |

| 26. In                                                                                                                                           | egister Summary                            | 189<br>191                                                                                                                                                |

| 26. In<br>27. O                                                                                                                                  | egister Summary                            | 189<br>191<br>195                                                                                                                                         |

| 26. In<br>27. O<br>28. P                                                                                                                         | egister Summary                            | 189<br>191<br>195<br>196                                                                                                                                  |

| <ol> <li>26. In</li> <li>27. O</li> <li>28. P</li> <li>29. E</li> </ol>                                                                          | egister Summary                            | 189<br>191<br>195<br>196<br>200                                                                                                                           |

| 26. In<br>27. O<br>28. P                                                                                                                         | egister Summary                            | 189<br>191<br>195<br>196<br>200<br>200                                                                                                                    |

| <ol> <li>26. In</li> <li>27. O</li> <li>28. P.</li> <li>29. E</li> <li>29.1</li> </ol>                                                           | egister Summary                            | 189<br>191<br>195<br>196<br>200<br>200<br>200                                                                                                             |

| <ol> <li>26. In</li> <li>27. O</li> <li>28. P.</li> <li>29. E</li> <li>29.1</li> <li>29.2</li> </ol>                                             | egister Summary                            | 189<br>191<br>195<br>196<br>200<br>200<br>200<br>200                                                                                                      |

| <ol> <li>26. In</li> <li>27. O</li> <li>28. Pa</li> <li>29. Ea</li> <li>29.1</li> <li>29.2</li> <li>29.3</li> <li>29.4</li> </ol>                | egister Summary                            | 189<br>191<br>195<br>196<br>200<br>200<br>200<br>200<br>200                                                                                               |

| <ol> <li>26. In</li> <li>27. O</li> <li>28. Pa</li> <li>29. Ea</li> <li>29.1</li> <li>29.2</li> <li>29.3</li> <li>29.4</li> <li>30. R</li> </ol> | egister Summary                            | <ol> <li>189</li> <li>191</li> <li>195</li> <li>196</li> <li>200</li> <li>200</li> <li>200</li> <li>200</li> <li>200</li> <li>200</li> <li>201</li> </ol> |