Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                             |

| Number of I/O              | 51                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP                                                                           |

| Supplier Device Package    | 64-LQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l471rgt6tr           |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pe                                       | eripheral                                   | STM32L          | .471Zx      | STM32        | _471Qx | STM32              | L471Vx           | STM32L471Rx |              |

|------------------------------------------|---------------------------------------------|-----------------|-------------|--------------|--------|--------------------|------------------|-------------|--------------|

| Flash memor                              | у                                           | 512KB           | 1MB         | 512KB        | 1MB    | 512KB              | 1MB              | 512KB       | 1MB          |

| SRAM                                     |                                             |                 |             | 1            | 12     | 8KB                |                  |             |              |

| External men<br>static memori            | nory controller for                         | Ye              | S           | Ye           | es     | Yes                | S <sup>(1)</sup> | 1           | No           |

| Quad SPI                                 |                                             |                 |             | 1            | Y      | ſes                |                  |             |              |

|                                          | Advanced control                            |                 |             |              | 2 (1   | I6-bit)            |                  |             |              |

|                                          | General purpose                             |                 |             |              |        | 16-bit)<br>32-bit) |                  |             |              |

|                                          | Basic                                       |                 |             |              | 2 (1   | I6-bit)            |                  |             |              |

| Timers                                   | Low -power                                  |                 |             |              | 2 (1   | I6-bit)            |                  |             |              |

|                                          | SysTick timer                               |                 |             |              |        | 1                  |                  |             |              |

|                                          | Watchdog timers<br>(independent,<br>window) |                 |             |              |        | 2                  |                  |             |              |

|                                          | SPI                                         |                 |             |              |        | 3                  |                  |             |              |

|                                          | I <sup>2</sup> C                            |                 | 3           |              |        |                    |                  |             |              |

| Comm.                                    | USART<br>UART<br>LPUART                     |                 | 3<br>2<br>1 |              |        |                    |                  |             |              |

| interfaces                               | SAI                                         | 2               |             |              |        |                    |                  |             |              |

|                                          | CAN                                         | 1               |             |              |        |                    |                  |             |              |

|                                          | SDMMC                                       | Yes             |             |              |        |                    |                  |             |              |

|                                          | SWPMI                                       | Yes             |             |              |        |                    |                  |             |              |

| Digital filters f<br>modulators          | for sigma-delta                             | Yes (4 filters) |             |              |        |                    |                  |             |              |

| Number of ch                             | annels                                      | 8               |             |              |        |                    |                  |             |              |

| RTC                                      |                                             | Yes             |             |              |        |                    |                  |             |              |

| Tamper pins                              |                                             | 3 2             |             |              |        |                    |                  |             |              |

| Random gene                              | erator                                      |                 |             |              | Y      | ſes                |                  |             |              |

| GPIOs<br>Wakeup pins<br>Nb of I/Os do    |                                             | 114<br>5<br>14  |             | 10<br>5<br>1 | 5      | 8<br>5<br>(        | 5                |             | 51<br>4<br>0 |

| Capacitive sensing<br>Number of channels |                                             | 24              | ļ           | 2            | 4      | 2                  | 1                |             | 12           |

| 12-bit ADCs<br>Number of channels        |                                             | 3<br>24         |             | 3<br>1       |        |                    | 3<br>6           |             | 3<br>16      |

| 12-bit DAC channels                      |                                             | 2               |             |              |        |                    |                  |             |              |

| Internal voltage reference buffer        |                                             | Yes No          |             |              |        |                    |                  |             |              |

| Analog comp                              | arator                                      | 2               |             |              |        |                    |                  |             |              |

| Operational a                            | amplifiers                                  | 2               |             |              |        |                    |                  |             |              |

| Max. CPU fre                             | equency                                     | 80 MHz          |             |              |        |                    |                  |             |              |

| Operating vol                            | Itage                                       |                 |             |              | 1.71   | to 3.6 V           |                  |             |              |

Table 2. STM32L471xx family device features and peripheral counts

# 3.11 Clocks and startup

The clock controller (see *Figure 3*) distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source:** four different clock sources can be used to drive the master clock SYSCLK:

- 4-48 MHz high-speed external crystal or ceramic resonator (HSE), that can supply a PLL. The HSE can also be configured in bypass mode for an external clock.

- 16 MHz high-speed internal RC oscillator (HSI16), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 12 frequencies from 100 kHz to 48 MHz. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be automatically trimmed by hardware to reach better than ±0.25% accuracy. The MSI can supply a PLL.

- System PLL which can be fed by HSE, HSI16 or MSI, with a maximum frequency at 80 MHz.

- **Auxiliary clock source:** two ultralow-power clock sources that can be used to drive the real-time clock:

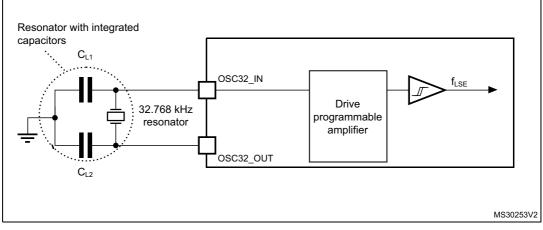

- 32.768 kHz low-speed external crystal (LSE), supporting four drive capability modes. The LSE can also be configured in bypass mode for an external clock.

- 32 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock accuracy is ±5% accuracy.

- **Peripheral clock sources:** Several peripherals (SDMMC, RNG, SAI, USARTs, I2Cs, LPTimers, ADC, SWPMI) have their own independent clock whatever the system clock. Three PLLs, each having three independent outputs allowing the highest flexibility, can generate independent clocks for the ADC, the SDMMC/RNG and the two SAIs.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 4 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI16 and a software interrupt is generated if enabled. LSE failure can also be detected and generated an interrupt.

- Clock-out capability:

- MCO: microcontroller clock output: it outputs one of the internal clocks for external use by the application

- LSCO: low speed clock output: it outputs LSI or LSE in all low-power modes (except VBAT).

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                                             | Memory address            |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = V <sub>REF+</sub> = 3.0 V (± 10 mV) | 0x1FFF 75A8 - 0x1FFF 75A9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 °C (± 5 °C), $V_{DDA} = V_{REF+} = 3.0 V (\pm 10 mV)$                                  | 0x1FFF 75CA - 0x1FFF 75CB |

| Table 8. Temperature sensor calibration values |

|------------------------------------------------|

|------------------------------------------------|

# 3.15.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference (VREFINT) provides a stable (bandgap) voltage output for the ADC and Comparators. VREFINT is internally connected to the ADC1\_IN0 input channel. The precise voltage of VREFINT is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Calibration value name | Description                                                                                                        | Memory address            |

|------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------|

| VREFINT                | Raw data acquired at a<br>temperature of 30 °C (± 5 °C),<br>V <sub>DDA</sub> = V <sub>REF+</sub> = 3.0 V (± 10 mV) | 0x1FFF 75AA - 0x1FFF 75AB |

#### Table 9. Internal voltage reference calibration values

# 3.15.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC1\_IN18 or ADC3\_IN18. As the V<sub>BAT</sub> voltage may be higher than VDDA, and thus outside the ADC input range, the VBAT pin is internally connected to a bridge divider by 3. As a consequence, the converted digital value is one third the V<sub>BAT</sub> voltage.

# 3.16 Digital to analog converter (DAC)

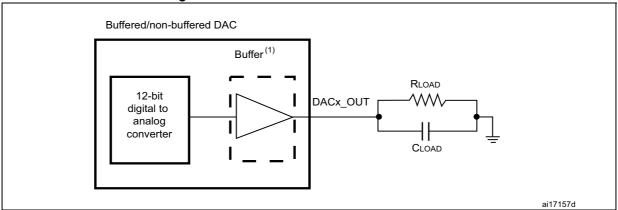

Two 12-bit buffered DAC channels can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital interface supports the following features:

- Up to two DAC output channels

- 8-bit or 12-bit output mode

- Buffer offset calibration (factory and user trimming)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Transmission

- Three transmit mailboxes

- Configurable transmit priority

- Reception

- Two receive FIFOs with three stages

- 14 Scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

- Time-triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Time Stamp sent in last two data bytes

- Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

# 3.32 Secure digital input/output and MultiMediaCards Interface (SDMMC)

The card host interface (SDMMC) provides an interface between the APB peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

The SDMMC features include the following:

- Full compliance with MultiMediaCard System Specification Version 4.2. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (forward compatibility)

- Full compliance with SD Memory Card Specifications Version 2.0

- Full compliance with SD I/O Card Specification Version 2.0: card support for two different databus modes: 1-bit (default) and 4-bit

- Data transfer up to 48 MHz for the 8 bit mode

- Data write and read with DMA capability

# **3.33** Flexible static memory controller (FSMC)

The Flexible static memory controller (FSMC) includes two memory controllers:

- The NOR/PSRAM memory controller

- The NAND/memory controller

This memory controller is also named Flexible memory controller (FMC).

The main features of the FMC controller are the following:

- Interface with static-memory mapped devices including:

- Static random access memory (SRAM)

- NOR Flash memory/OneNAND Flash memory

- PSRAM (4 memory banks)

- NAND Flash memory with ECC hardware to check up to 8 Kbyte of data

- 8-,16- bit data bus width

- Independent Chip Select control for each memory bank

- Independent configuration for each memory bank

- Write FIFO

- The Maximum FMC\_CLK frequency for synchronous accesses is HCLK/2.

#### LCD parallel interface

The FMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

# 3.34 Quad SPI memory interface (QUADSPI)

The Quad SPI is a specialized communication interface targeting single, dual or quad SPI flash memories. It can operate in any of the three following modes:

- Indirect mode: all the operations are performed using the QUADSPI registers

- Status polling mode: the external flash status register is periodically read and an interrupt can be generated in case of flag setting

- Memory-mapped mode: the external flash is memory mapped and is seen by the system as if it were an internal memory

The Quad SPI interface supports:

- Three functional modes: indirect, status-polling, and memory-mapped

- SDR and DDR support

- Fully programmable opcode for both indirect and memory mapped mode

- Fully programmable frame format for both indirect and memory mapped mode

- Each of the 5 following phases can be configured independently (enable, length, single/dual/quad communication)

- Instruction phase

- Address phase

- Alternate bytes phase

- Dummy cycles phase

- Data phase

- Integrated FIFO for reception and transmission

- 8, 16, and 32-bit data accesses are allowed

- DMA channel for indirect mode operations

- Programmable masking for external flash flag management

- Timeout management

- Interrupt generation on FIFO threshold, timeout, status match, operation complete, and access error

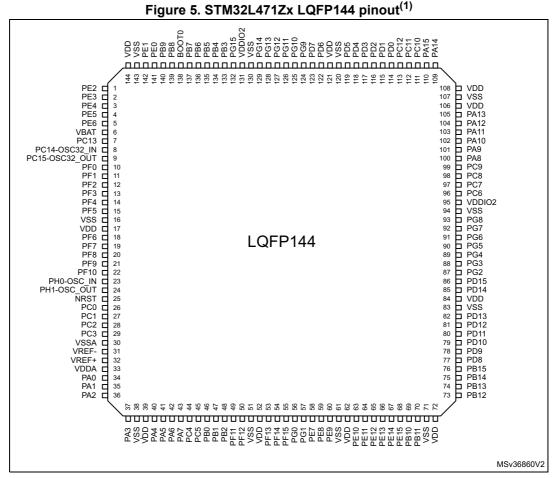

# 4 Pinouts and pin description

1. The above figure shows the package top view.

| Table 24. Embedded reset and power control block characteristics (co |                                                           |                                     |      |      |      | ,<br> |  |

|----------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------|------|------|------|-------|--|

| Symbol                                                               | Parameter                                                 | Conditions <sup>(1)</sup>           | Min  | Тур  | Мах  | Unit  |  |

| V <sub>PVD1</sub>                                                    | PVD threshold 1                                           | Rising edge                         | 2.26 | 2.31 | 2.36 | V     |  |

| PVDI                                                                 |                                                           | Falling edge                        | 2.15 | 2.20 | 2.25 |       |  |

| Varia                                                                | PVD threshold 2                                           | Rising edge                         | 2.41 | 2.46 | 2.51 | v     |  |

| V <sub>PVD2</sub>                                                    |                                                           | Falling edge                        | 2.31 | 2.36 | 2.41 | v     |  |

| V <sub>PVD3</sub>                                                    | PVD threshold 3                                           | Rising edge                         | 2.56 | 2.61 | 2.66 | v     |  |

| ♥PVD3                                                                |                                                           | Falling edge                        | 2.47 | 2.52 | 2.57 | v     |  |

| V                                                                    | PVD threshold 4                                           | Rising edge                         | 2.69 | 2.74 | 2.79 | V     |  |

| V <sub>PVD4</sub>                                                    |                                                           | Falling edge                        | 2.59 | 2.64 | 2.69 | v     |  |

| M                                                                    | DVD threshold 5                                           | Rising edge                         | 2.85 | 2.91 | 2.96 | V     |  |

| V <sub>PVD5</sub>                                                    | PVD threshold 5                                           | Falling edge                        | 2.75 | 2.81 | 2.86 | v     |  |

| N/                                                                   | DV/D thread and C                                         | Rising edge                         | 2.92 | 2.98 | 3.04 |       |  |

| V <sub>PVD6</sub>                                                    | PVD threshold 6                                           | Falling edge                        | 2.84 | 2.90 | 2.96 | V     |  |

| V <sub>hyst_BORH0</sub>                                              | Hysteresis voltage of BORH0                               | Hysteresis in<br>continuous<br>mode | -    | 20   | -    | mV    |  |

|                                                                      |                                                           | Hysteresis in other mode            | -    | 30   | -    |       |  |

| V <sub>hyst_BOR_PVD</sub>                                            | Hysteresis voltage of BORH<br>(except BORH0) and PVD      | -                                   | -    | 100  | -    | mV    |  |

| I <sub>DD</sub><br>(BOR_PVD) <sup>(2)</sup>                          | $BOR^{(3)}$ (except BOR0) and PVD consumption from $V_DD$ | -                                   | -    | 1.1  | 1.6  | μA    |  |

| V <sub>PVM2</sub>                                                    | V <sub>DDIO2</sub> peripheral voltage monitoring          | -                                   | 0.92 | 0.96 | 1    | V     |  |

| M                                                                    | V <sub>DDA</sub> peripheral voltage                       | Rising edge                         | 1.61 | 1.65 | 1.69 | V     |  |

| V <sub>PVM3</sub>                                                    | monitoring                                                | Falling edge                        | 1.6  | 1.64 | 1.68 | V     |  |

|                                                                      | V <sub>DDA</sub> peripheral voltage                       | Rising edge                         | 1.78 | 1.82 | 1.86 |       |  |

| V <sub>PVM4</sub>                                                    | monitoring                                                | Falling edge                        | 1.77 | 1.81 | 1.85 | V     |  |

| V <sub>hyst_PVM3</sub>                                               | PVM3 hysteresis                                           | -                                   | -    | 10   | -    | mV    |  |

| V <sub>hyst_PVM4</sub>                                               | PVM4 hysteresis                                           | -                                   | -    | 10   | -    | mV    |  |

| I <sub>DD</sub><br>(PVM1/PVM2)<br>(2)                                | PVM1 and PVM2<br>consumption from V <sub>DD</sub>         | -                                   | -    | 0.2  | -    | μA    |  |

| I <sub>DD</sub><br>(PVM3/PVM4)<br>(2)                                | PVM3 and PVM4<br>consumption from V <sub>DD</sub>         | -                                   | -    | 2    | -    | μA    |  |

Table 24. Embedded reset and power control block characteristics (continued)

1. Continuous mode means Run/Sleep modes, or temperature sensor enable in Low-power run/Low-power sleep modes.

2. Guaranteed by design.

3. BOR0 is enabled in all modes (except shutdown) and its consumption is therefore included in the supply current characteristics tables.

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 40*. The MCU is placed under the following conditions:

- All I/O pins are in Analog mode

- The given value is calculated by measuring the difference of the current consumptions:

- when the peripheral is clocked on

- when the peripheral is clocked off

- Ambient operating temperature and supply voltage conditions summarized in *Table 19: Voltage characteristics*

- The power consumption of the digital part of the on-chip peripherals is given in *Table 40*. The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

| Peripheral |                              | Range 1 | Range 2 | Low-power run<br>and sleep | Unit        |

|------------|------------------------------|---------|---------|----------------------------|-------------|

|            | Bus Matrix <sup>(1)</sup>    | 4.5     | 3.7     | 4.1                        |             |

|            | ADC independent clock domain | 0.4     | 0.1     | 0.2                        |             |

|            | ADC AHB clock domain         | 5.5     | 4.7     | 5.5                        |             |

|            | CRC                          | 0.4     | 0.2     | 0.3                        |             |

|            | DMA1                         | 1.4     | 1.3     | 1.4                        |             |

|            | DMA2                         | 1.5     | 1.3     | 1.4                        |             |

|            | FLASH                        | 6.2     | 5.2     | 5.8                        |             |

|            | FMC                          | 8.9     | 7.5     | 8.4                        |             |

|            | GPIOA <sup>(2)</sup>         | 4.8     | 3.8     | 4.4                        |             |

|            | GPIOB <sup>(2)</sup>         | 4.8     | 4.0     | 4.6                        |             |

|            | GPIOC <sup>(2)</sup>         | 4.5     | 3.8     | 4.3                        |             |

| AHB        | GPIOD <sup>(2)</sup>         | 4.6     | 3.9     | 4.4                        | µA/MHz      |

| 7.118      | GPIOE <sup>(2)</sup>         | 5.2     | 4.5     | 4.9                        | . p/ 010112 |

|            | GPIOF <sup>(2)</sup>         | 5.9     | 4.9     | 5.7                        |             |

|            | GPIOG <sup>(2)</sup>         | 4.3     | 3.8     | 4.2                        |             |

|            | GPIOH <sup>(2)</sup>         | 0.7     | 0.6     | 0.8                        |             |

|            | QUADSPI                      | 7.8     | 6.7     | 7.3                        |             |

|            | RNG independent clock domain | 2.2     | NA      | NA                         |             |

|            | RNG AHB clock domain         | 0.6     | NA      | NA                         |             |

|            | SRAM1                        | 0.9     | 0.8     | 0.9                        | 1           |

|            | SRAM2                        | 1.6     | 1.4     | 1.6                        |             |

| AHB        | TSC                          | 1.8     | 1.4     | 1.6                        | µA/MHz      |

|            | All AHB Peripherals          | 118.5   | 77.3    | 87.6                       | 1           |

#### Table 40. Peripheral current consumption

|                   | · · · · · · · · · · · · · · · · · · ·                                           |                          |     |     |      |

|-------------------|---------------------------------------------------------------------------------|--------------------------|-----|-----|------|

| Symbol            | Parameter                                                                       | Conditions               | Тур | Max | Unit |

| twulprum          | Wakeup time from Low-power run mode to Run mode <sup>(2)</sup>                  | Code run with MSI 2 MHz  | 5   | 7   | 110  |

| t <sub>VOST</sub> | Regulator transition time from Range 2 to Range 1 or Range 1 to Range $2^{(3)}$ | Code run with MSI 24 MHz | 20  | 40  | μs   |

#### Table 42. Regulator modes transition times<sup>(1)</sup>

1. Guaranteed by characterization results.

2. Time until REGLPF flag is cleared in PWR\_SR2.

3. Time until VOSF flag is cleared in PWR\_SR2.

### 6.3.7 External clock source characteristics

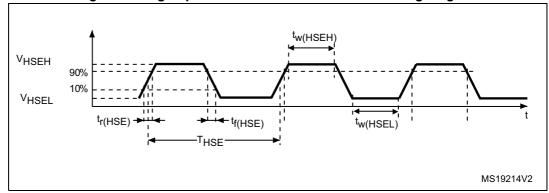

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 15: High-speed external clock source AC timing diagram*.

| Symbol               | Parameter                            | Conditions                 | Min                    | Тур | Max                    | Unit |

|----------------------|--------------------------------------|----------------------------|------------------------|-----|------------------------|------|

| f <sub>HSE_ext</sub> | User external clock source frequency | Voltage scaling<br>Range 1 | -                      | 8   | 48                     | MHz  |

|                      |                                      | Voltage scaling<br>Range 2 | -                      | 8   | 26                     |      |

| V <sub>HSEH</sub>    | OSC_IN input pin high level voltage  | -                          | $0.7 V_{\text{DDIOx}}$ | -   | V <sub>DDIOx</sub>     | V    |

| V <sub>HSEL</sub>    | OSC_IN input pin low level voltage   | -                          | V <sub>SS</sub>        | -   | 0.3 V <sub>DDIOx</sub> |      |

| t <sub>w(HSEH)</sub> | OSC IN high or low time              | Voltage scaling<br>Range 1 | 7                      | -   | -                      | 20   |

| t <sub>w(HSEL)</sub> | OSC_IN high or low time              | Voltage scaling<br>Range 2 | 18                     | -   | -                      | ns   |

#### Table 43. High-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

- 1. Guaranteed by design.

- Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

- t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

# Low-speed internal (LSI) RC oscillator

| Symbol                                 | Parameter                            | Conditions                                          |       | Тур | Max   | Unit |

|----------------------------------------|--------------------------------------|-----------------------------------------------------|-------|-----|-------|------|

| f <sub>LSI</sub>                       |                                      | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 30 °C     | 31.04 | -   | 32.96 | kHz  |

|                                        | LSI Frequency                        | V <sub>DD</sub> = 1.62 to 3.6 V, TA = -40 to 125 °C | 29.5  | -   | 34    | KIIZ |

| t <sub>SU</sub> (LSI) <sup>(2)</sup>   | LSI oscillator start-<br>up time     | -                                                   | -     | 80  | 130   | μs   |

| t <sub>STAB</sub> (LSI) <sup>(2)</sup> | LSI oscillator<br>stabilization time | 5% of final frequency                               | -     | 125 | 180   | μs   |

| I <sub>DD</sub> (LSI) <sup>(2)</sup>   | LSI oscillator power consumption     | -                                                   | -     | 110 | 180   | nA   |

Table 49. LSI oscillator characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. Guaranteed by design.

# 6.3.9 PLL characteristics

The parameters given in *Table 50* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22: General operating conditions*.

| Symbol                 | Parameter                      | Conditions              | Min    | Тур | Мах | Unit |  |

|------------------------|--------------------------------|-------------------------|--------|-----|-----|------|--|

| f                      | PLL input clock <sup>(2)</sup> | -                       | 4      | -   | 16  | MHz  |  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle     | -                       | 45     | -   | 55  | %    |  |

| £                      | DLL multiplier output clock D  | Voltage scaling Range 1 | 2.0645 | -   | 80  | MHz  |  |

| f <sub>PLL_P_OUT</sub> | PLL multiplier output clock P  | Voltage scaling Range 2 | 2.0645 | -   | 26  |      |  |

| f                      | PLL multiplier output clock Q  | Voltage scaling Range 1 | 8      | -   | 80  | MHz  |  |

| <sup>f</sup> PLL_Q_OUT |                                | Voltage scaling Range 2 | 8      | -   | 26  |      |  |

| £                      | DLL multiplier output clock D  | Voltage scaling Range 1 | 8      | -   | 80  | MHz  |  |

| <sup>f</sup> PLL_R_OUT | PLL multiplier output clock R  | Voltage scaling Range 2 | 8      | -   | 26  |      |  |

| £                      |                                | Voltage scaling Range 1 | 64     | -   | 344 | MHz  |  |

| fvco_out               | PLL VCO output                 | Voltage scaling Range 2 | 64     | -   | 128 |      |  |

| t <sub>LOCK</sub>      | PLL lock time                  | -                       | -      | 15  | 40  | μs   |  |

| Jitter                 | RMS cycle-to-cycle jitter      | o-cycle jitter          | -      | 40  | -   | 100  |  |

| Jiller                 | RMS period jitter              | System clock 80 MHz     | -      | 30  | -   | ±ps  |  |

|                        |                                | VCO freq = 64 MHz       | -      | 150 | 200 | μA   |  |

|                        | PLL power consumption on       | VCO freq = 96 MHz       | -      | 200 | 260 |      |  |

| I <sub>DD</sub> (PLL)  | V <sub>DD</sub> <sup>(1)</sup> | VCO freq = 192 MHz      | -      | 300 | 380 |      |  |

|                        |                                | VCO freq = 344 MHz      | -      | 520 | 650 |      |  |

| Table 50. | PLL. | PLLSAI1 | PLLSAI2 | characteristics <sup>(1)</sup> |

|-----------|------|---------|---------|--------------------------------|

|           |      |         |         | Characteristics                |

1. Guaranteed by design.

| Speed | Symbol | Parameter                      | Conditions                                 | Min | Max | Unit |

|-------|--------|--------------------------------|--------------------------------------------|-----|-----|------|

|       |        |                                | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 5   |      |

|       |        |                                | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1   |      |

|       | Fmax   | Movimum froquenov              | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 | MHz  |

|       | FIIIdX | Maximum frequency              | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 10  |      |

|       |        |                                | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1.5 |      |

| 00    |        |                                | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 |      |

| 00    |        |                                | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |      |

|       |        |                                | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 52  |      |

|       | Tr/Tf  | r/Tf Output rise and fall time | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 140 | ns   |

|       |        |                                | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 17  |      |

|       |        |                                | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 37  |      |

|       |        |                                | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 110 |      |

|       |        | nax Maximum frequency          | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  | MHz  |

|       | Fmax   |                                | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 10  |      |

|       |        |                                | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   |      |

|       |        |                                | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 50  |      |

|       |        |                                | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 15  |      |

| 01    |        |                                | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   |      |

| 01    |        |                                | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 9   |      |

|       |        |                                | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 16  | - ns |

|       | Tr/Tf  | Output rise and fall time      | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 40  |      |

|       | 11/11  |                                | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 4.5 |      |

|       |        |                                | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 9   |      |

|       |        |                                | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 21  |      |

#### 3. Refer to Table 58: I/O static characteristics.

4. Ton is the Refresh phase duration. Toff is the Hold phase duration. Refer to RM0392 reference manual for more details.

#### Figure 26. 12-bit buffered / non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Symbol    | Parameter                                          | Conditio                                                  | Min                       | Тур | Max       | Unit |     |

|-----------|----------------------------------------------------|-----------------------------------------------------------|---------------------------|-----|-----------|------|-----|

| DNL       | Differential non                                   | DAC output buffer ON                                      |                           | -   | -         | ±2   |     |

| DINL      | linearity <sup>(2)</sup>                           | DAC output buffer OFF                                     |                           | -   | -         | ±2   |     |

| -         | monotonicity                                       | 10 bits                                                   |                           | Ģ   | guarantee | d    |     |

| INII      | Integral non                                       | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ             |                           | -   | -         | ±4   |     |

| INL       | linearity <sup>(3)</sup>                           | DAC output buffer OFF<br>CL ≤ 50 pF, no RL                |                           | -   | -         | ±4   |     |

|           | Offset error at code 0x800 <sup>(3)</sup>          | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ             | V <sub>REF+</sub> = 3.6 V | -   | -         | ±12  | LSB |

| Offset    |                                                    |                                                           | V <sub>REF+</sub> = 1.8 V | -   | -         | ±25  |     |

|           |                                                    | DAC output buffer OFF<br>CL $\leq$ 50 pF, no RL           |                           | -   | -         | ±8   |     |

| Offset1   | Offset error at code 0x001 <sup>(4)</sup>          | DAC output buffer OFF<br>CL ≤ 50 pF, no RL                |                           | -   | -         | ±5   |     |

| OffsetCal | Offset Error at<br>code 0x800<br>after calibration | code $0x800$ DAC output buffer ON<br>CL < 50 pE RL > 5 kO | V <sub>REF+</sub> = 3.6 V | -   | -         | ±5   |     |

|           |                                                    |                                                           | V <sub>REF+</sub> = 1.8 V | -   | -         | ±7   |     |

# Table 70. DAC accuracy<sup>(1)</sup>

Г

Т

Т

#### **SPI characteristics**

Unless otherwise specified, the parameters given in *Table 82* for SPI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 22: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                       | Parameter                | Conditions                                                                                                 | Min                              | Тур               | Max                  | Unit |  |

|----------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------|----------------------|------|--|

|                                              |                          | Master mode receiver/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                       |                                  | -                 | 24                   | MHz  |  |

|                                              |                          | Master mode receiver/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                      |                                  |                   | 13                   |      |  |

|                                              |                          | Master mode transmitter<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                               |                                  |                   | 40                   |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency      | Slave mode receiver<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                                   | -                                |                   | 40                   |      |  |

|                                              |                          | Slave mode transmitter/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                     |                                  |                   | 26 <sup>(2)</sup>    |      |  |

|                                              |                          | Slave mode transmitter/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1<br>Voltage Range 2 |                                  |                   | 16 <sup>(2)</sup>    |      |  |

|                                              |                          |                                                                                                            |                                  |                   | 13                   |      |  |

|                                              |                          | 1.08 < V <sub>DDIO2</sub> < 1.32 V <sup>(3)</sup>                                                          |                                  |                   | 8                    | 1    |  |

| t <sub>su(NSS)</sub>                         | NSS setup time           | Slave mode, SPI prescaler = 2                                                                              | 4 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |  |

| t <sub>h(NSS)</sub>                          | NSS hold time            | Slave mode, SPI prescaler = 2                                                                              | 2 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time    | Master mode                                                                                                | T <sub>PCLK</sub> -2             | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2 | ns   |  |

| t <sub>su(MI)</sub>                          | Data input setup time    | Master mode                                                                                                | 3.5                              | -                 | -                    | ns   |  |

| t <sub>su(SI)</sub>                          | Data input setup time    | Slave mode                                                                                                 | 3                                | -                 | -                    | 115  |  |

| t <sub>h(MI)</sub>                           | Data input hold time     | Master mode                                                                                                | 6.5                              | -                 | -                    | ns   |  |

| t <sub>h(SI)</sub>                           |                          | Slave mode                                                                                                 | 3                                | -                 | -                    | 115  |  |

| t <sub>a(SO)</sub>                           | Data output access time  | Slave mode                                                                                                 | 9                                | -                 | 36                   | ns   |  |

| t <sub>dis(SO)</sub>                         | Data output disable time | Slave mode                                                                                                 | 9                                | -                 | 16                   | ns   |  |

| Table | 82. | SPI | characteristics <sup>(</sup> | 1) |

|-------|-----|-----|------------------------------|----|

|-------|-----|-----|------------------------------|----|

| Symbol                                  | Parameter              | Parameter Conditions                                         |    | Тур  | Мах  | Unit |

|-----------------------------------------|------------------------|--------------------------------------------------------------|----|------|------|------|

| t <sub>v(SO)</sub><br>Data output valid |                        | Slave mode 2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  | -  | 12.5 | 19   |      |

|                                         |                        | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 | -  | 12.5 | 30   | ns   |

|                                         | Data output valid time | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 2 | -  | 12.5 | 33   |      |

| -                                       |                        | Slave mode 1.08 < $V_{DDIO2}$ < 1.32 $V^{(3)}$               | -  | 25   | 62.5 |      |

| t <sub>v(MO)</sub>                      |                        | Master mode                                                  | -  | 2.5  | 12.5 |      |

| t <sub>h(SO)</sub>                      |                        | Slave mode                                                   | 9  | -    | -    |      |

| -                                       | Data output hold time  | Slave mode 1.08 < $V_{DDIO2}$ < 1.32 $V^{(3)}$               | 24 | -    | -    | ns   |

| t <sub>h(MO)</sub>                      |                        | Master mode                                                  | 0  | -    | -    |      |

# Table 82. SPI characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

2. Maximum frequency in Slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty(SCK) = 50 %.

3. SPI mapped on Port G.

#### Figure 27. SPI timing diagram - slave mode and CPHA = 0

# **SAI characteristics**

Unless otherwise specified, the parameters given in *Table 85* for SAI are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in*Table 22: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels:  $0.5 \times V_{DD}$

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CK,SD,FS).

| Symbol                   | Parameter                          | Conditions                                                            | Min | Мах  | Unit |  |

|--------------------------|------------------------------------|-----------------------------------------------------------------------|-----|------|------|--|

| f <sub>MCLK</sub>        | SAI Main clock output              | -                                                                     | -   | 50   | MHz  |  |

|                          |                                    | Master transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -   | 18.5 |      |  |

|                          |                                    | Master transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1 | -   | 12.5 |      |  |

|                          |                                    | Master receiver<br>Voltage Range 1                                    | -   | 25   |      |  |

| fск                      | SAI clock frequency <sup>(2)</sup> | Slave transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1   | -   | 22.5 | MHz  |  |

|                          |                                    | Slave transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -   | 14.5 |      |  |

|                          |                                    | Slave receiver<br>Voltage Range 1                                     | -   | 25   |      |  |

|                          |                                    | Voltage Range 2                                                       | -   | 12.5 |      |  |

|                          | EQ valid time                      | Master mode<br>2.7 $\leq$ V <sub>DD</sub> $\leq$ 3.6                  | -   | 22   | ns   |  |

| t <sub>v(FS)</sub>       | FS valid time                      | Master mode<br>1.71 $\leq V_{DD} \leq 3.6$                            | -   | 40   |      |  |

| t <sub>h(FS)</sub>       | FS hold time                       | Master mode                                                           | 10  | -    | ns   |  |

| t <sub>su(FS)</sub>      | FS setup time                      | Slave mode                                                            | 1   | -    | ns   |  |

| t <sub>h(FS)</sub>       | FS hold time                       | Slave mode                                                            | 2   | -    | ns   |  |

| t <sub>su(SD_A_MR)</sub> | Data input setup time              | Master receiver                                                       | 2.5 | -    | ne   |  |

| t <sub>su(SD_B_SR)</sub> |                                    | Slave receiver                                                        | 3   | -    | ns   |  |

| t <sub>h(SD_A_MR)</sub>  | Data input hold time               | Master receiver                                                       | 8   | -    | ns   |  |

| t <sub>h(SD_B_SR)</sub>  |                                    | Slave receiver                                                        | 4   | -    | 113  |  |

| Table 85. | SAI | characteristics <sup>(1)</sup> |

|-----------|-----|--------------------------------|

|-----------|-----|--------------------------------|

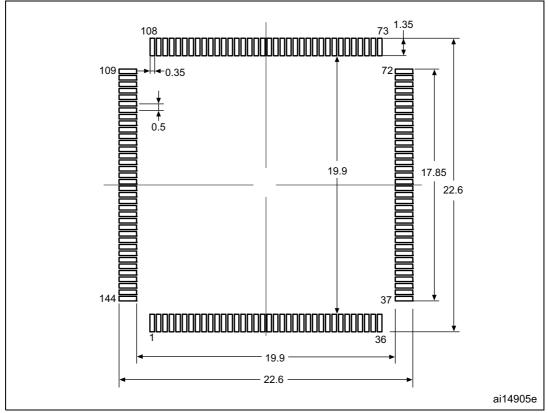

1. Dimensions are expressed in millimeters.

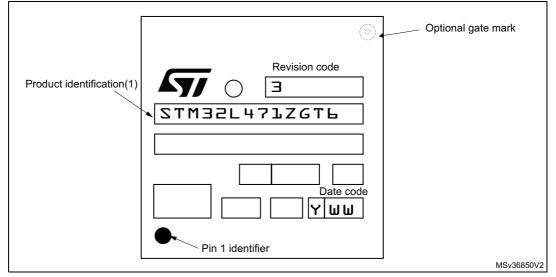

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 9 Revision history

| Table 109 | . Document | revision | history |

|-----------|------------|----------|---------|

|-----------|------------|----------|---------|

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 04-Fev-2016 | 1        | Initial release. |