### STMicroelectronics - STM32L471VET6TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                             |

| Number of I/O              | 82                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP                                                                          |

| Supplier Device Package    | 100-LQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l471vet6tr           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 6.3.27   | FSMC characteristics                    | 183 |

|---|--------|----------|-----------------------------------------|-----|

| 7 | Packa  | ige info | rmation                                 | 200 |

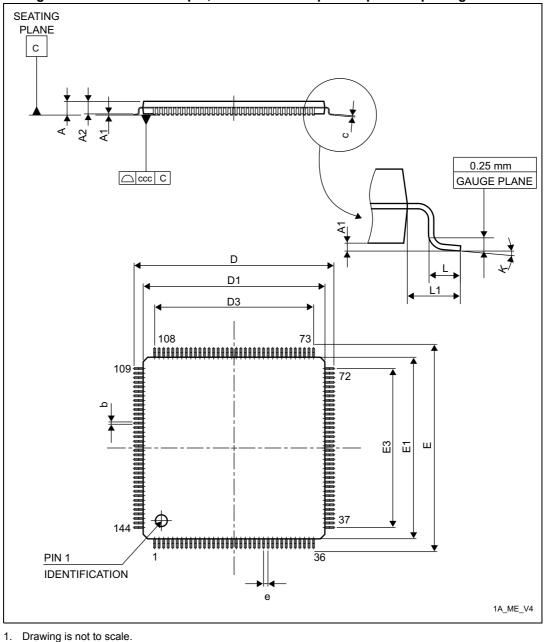

|   | 7.1    | LQFP14   | 4 package information                   | 200 |

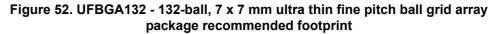

|   | 7.2    | UFBGA    | 132 package information 2               | 204 |

|   | 7.3    | LQFP10   | 0 package information                   | 207 |

|   | 7.4    | LQFP64   | package information                     | 210 |

|   | 7.5    | Thermal  | characteristics                         | 213 |

|   |        | 7.5.1    | Reference document                      | 213 |

|   |        | 7.5.2    | Selecting the product temperature range | 213 |

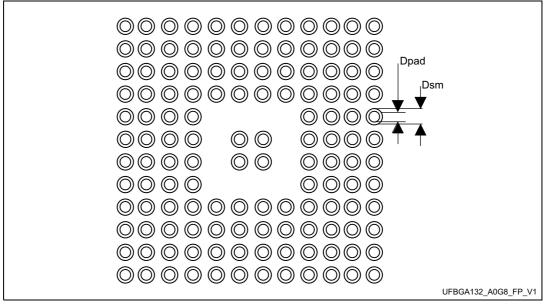

| 8 | Part n | umberi   | ng                                      | 16  |

| 9 | Revis  | ion hist | ory                                     | 217 |

## 3.4 Embedded Flash memory

STM32L471xx devices feature up to 1 Mbyte of embedded Flash memory available for storing programs and data. The Flash memory is divided into two banks allowing read-while-write operations. This feature allows to perform a read operation from one bank while an erase or program operation is performed to the other bank. The dual bank boot is also supported. Each bank contains 256 pages of 2 Kbyte.

Flexible protections can be configured thanks to option bytes:

- Readout protection (RDP) to protect the whole memory. Three levels are available:

- Level 0: no readout protection

- Level 1: memory readout protection: the Flash memory cannot be read from or written to if either debug features are connected, boot in RAM or bootloader is selected

- Level 2: chip readout protection: debug features (Cortex-M4 JTAG and serial wire), boot in RAM and bootloader selection are disabled (JTAG fuse). This selection is irreversible.

| Area      | Protection<br>level | U    | ser executio | on                 | Debug, boot from RAM or boot<br>from system memory (loader) |       |                    |  |

|-----------|---------------------|------|--------------|--------------------|-------------------------------------------------------------|-------|--------------------|--|

|           | level               | Read | Write        | Erase              | Read                                                        | Write | Erase              |  |

| Main      | 1                   | Yes  | Yes          | Yes                | No                                                          | No    | No                 |  |

| memory    | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |

| System    | 1                   | Yes  | No           | No                 | Yes                                                         | No    | No                 |  |

| memory    | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |

| Option    | 1                   | Yes  | Yes          | Yes                | Yes                                                         | Yes   | Yes                |  |

| bytes     | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |

| Backup    | 1                   | Yes  | Yes          | N/A <sup>(1)</sup> | No                                                          | No    | N/A <sup>(1)</sup> |  |

| registers | 2                   | Yes  | Yes          | N/A                | N/A                                                         | N/A   | N/A                |  |

| SDAM2     | 1                   | Yes  | Yes          | Yes <sup>(1)</sup> | No                                                          | No    | No <sup>(1)</sup>  |  |

| SRAM2     | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |

Table 3. Access status versus readout protection level and execution modes

1. Erased when RDP change from Level 1 to Level 0.

- Write protection (WRP): the protected area is protected against erasing and programming. Two areas per bank can be selected, with 2-Kbyte granularity.

- Proprietary code readout protection (PCROP): a part of the flash memory can be

protected against read and write from third parties. The protected area is execute-only:

it can only be reached by the STM32 CPU, as an instruction code, while all other

accesses (DMA, debug and CPU data read, write and erase) are strictly prohibited.

One area per bank can be selected, with 64-bit granularity. An additional option bit

(PCROP\_RDP) allows to select if the PCROP area is erased or not when the RDP

protection is changed from Level 1 to Level 0.

|                   | Table 4. STM32L471 modes overview (continued) |                  |     |       |      |            |                                                                                                                                                                                                                                       |                                                                                                                                                                                                     |                                |                               |

|-------------------|-----------------------------------------------|------------------|-----|-------|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|

|                   | Mode                                          | Regulator<br>(1) | CPU | Flash | SRAM | Clocks     | DMA & Peripherals <sup>(2)</sup>                                                                                                                                                                                                      | Wakeup source                                                                                                                                                                                       | Consumption <sup>(3)</sup>     | Wakeup time                   |

| Do                | Stop 1                                        | LPR              | No  | Off   | ON   | LSE<br>LSI | BOR, PVD, PVM<br>RTC,IWDG<br>COMPx (x=1,2)<br>DACx (x=1,2)<br>OPAMPx (x=1,2)<br>USARTx (x=15) <sup>(6)</sup><br>LPUART1 <sup>(6)</sup><br>I2Cx (x=13) <sup>(7)</sup><br>LPTIMx (x=1,2)<br>***<br>All other peripherals are<br>frozen. | Reset pin, all I/Os<br>BOR, PVD, PVM<br>RTC,IWDG<br>COMPx (x=12)<br>USARTx (x=15) <sup>(6)</sup><br>LPUART1 <sup>(6)</sup><br>I2Cx (x=13) <sup>(7)</sup><br>LPTIMx (x=1,2)<br>SWPMI1 <sup>(8)</sup> | 6.6 μA w/o RTC<br>6.9 μA w RTC | 4 μs in SRAM<br>6 μs in Flash |

| DocID027226 Rev 1 | Stop 2                                        | LPR              | No  | Off   | ON   | LSE<br>LSI | BOR, PVD, PVM<br>RTC,IWDG<br>COMPx (x=12)<br>I2C3 <sup>(7)</sup><br>LPUART1 <sup>(6)</sup><br>LPTIM1<br>***<br>All other peripherals are<br>frozen.                                                                                   | Reset pin, all I/Os<br>BOR, PVD, PVM<br>RTC,IWDG<br>COMPx (x=12)<br>I2C3 <sup>(7)</sup><br>LPUART1 <sup>(6)</sup><br>LPTIM1                                                                         | 1.1 μA w/o RTC<br>1.4 μA w/RTC | 5 μs in SRAM<br>7 μs in Flash |

23/218

Functional overview

STM32L471xx

Standby mode, supplied by the low-power Regulator (Standby with RAM2 retention mode).

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper) or a failure is detected on LSE (CSS on LSE).

The system clock after wakeup is MSI up to 8 MHz.

Shutdown mode

The Shutdown mode allows to achieve the lowest power consumption. The internal regulator is switched off so that the VCORE domain is powered off. The PLL, the HSI16, the MSI, the LSI and the HSE oscillators are also switched off.

The RTC can remain active (Shutdown mode with RTC, Shutdown mode without RTC).

The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to Backup domain is not supported.

SRAM1, SRAM2 and register contents are lost except for registers in the Backup domain.

The device exits Shutdown mode when an external reset (NRST pin), a WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper).

The system clock after wakeup is MSI at 4 MHz.

- Transmission

- Three transmit mailboxes

- Configurable transmit priority

- Reception

- Two receive FIFOs with three stages

- 14 Scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

- Time-triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Time Stamp sent in last two data bytes

- Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

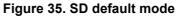

# 3.32 Secure digital input/output and MultiMediaCards Interface (SDMMC)

The card host interface (SDMMC) provides an interface between the APB peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

The SDMMC features include the following:

- Full compliance with MultiMediaCard System Specification Version 4.2. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (forward compatibility)

- Full compliance with SD Memory Card Specifications Version 2.0

- Full compliance with SD I/O Card Specification Version 2.0: card support for two different databus modes: 1-bit (default) and 4-bit

- Data transfer up to 48 MHz for the 8 bit mode

- Data write and read with DMA capability

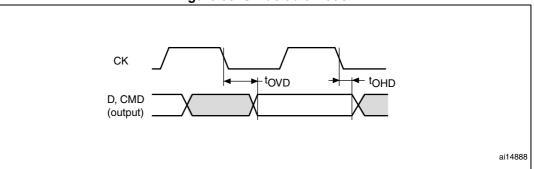

## **3.33** Flexible static memory controller (FSMC)

The Flexible static memory controller (FSMC) includes two memory controllers:

- The NOR/PSRAM memory controller

- The NAND/memory controller

This memory controller is also named Flexible memory controller (FMC).

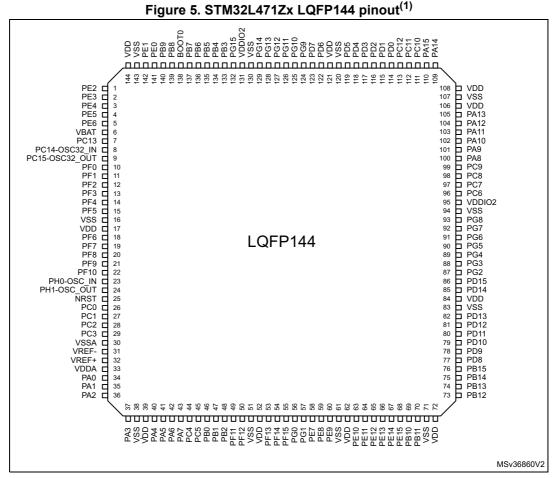

## 4 Pinouts and pin description

1. The above figure shows the package top view.

|        | Pin N   | umbe     | r       |                                       |          | 0                                                               |                                                                                 | Pin funct                                                                                       | ions                                          |

|--------|---------|----------|---------|---------------------------------------|----------|-----------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------|

| LQFP64 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure                                                   | Notes                                                                           | Alternate functions                                                                             | Additional functions                          |

| 14     | 23      | L2       | 34      | PA0                                   | I/O      | ) FT_a -                                                        |                                                                                 | TIM2_CH1, TIM5_CH1,<br>TIM8_ETR, USART2_CTS,<br>UART4_TX,<br>SAI1_EXTCLK,<br>TIM2_ETR, EVENTOUT | OPAMP1_VINP,<br>ADC12_IN5,<br>RTC_TAMP2/WKUP1 |

| -      | -       | M3       | -       | OPAMP1_VINM                           | Ι        | TT                                                              | -                                                                               | -                                                                                               | -                                             |

| 15     | 24      | M2       | 35      | PA1                                   | I/O      | FT_a                                                            | -                                                                               | TIM2_CH2, TIM5_CH2,<br>USART2_RTS_DE,<br>UART4_RX, TIM15_CH1N,<br>EVENTOUT                      | OPAMP1_VINM,<br>ADC12_IN6                     |

| 16     | 25      | K3       | 36      | PA2                                   | I/O      | FT_a                                                            | FT_a - TIM2_CH3, TIM5_CH3,<br>USART2_TX,<br>SAI2_EXTCLK,<br>TIM15_CH1, EVENTOUT |                                                                                                 | ADC12_IN7,<br>WKUP4/LSCO                      |

| 17     | 26      | L3       | 37      | PA3                                   | I/O      | TT - TIM2_CH4, TIM5_CH4,<br>USART2_RX, TIM15_CH2,<br>EVENTOUT V |                                                                                 | OPAMP1_<br>VOUT, ADC12_IN8                                                                      |                                               |

| 18     | 27      | E3       | 38      | VSS                                   | S        | -                                                               | -                                                                               | -                                                                                               | -                                             |

| 19     | 28      | H3       | 39      | VDD                                   | S        | -                                                               | -                                                                               | -                                                                                               | -                                             |

| 20     | 29      | J4       | 40      | PA4                                   | I/O      | TT_a                                                            | -                                                                               | SPI1_NSS, SPI3_NSS,<br>USART2_CK, SAI1_FS_B,<br>LPTIM2_OUT, EVENTOUT                            | ADC12_IN9,<br>DAC1_OUT1                       |

| 21     | 30      | K4       | 41      | PA5                                   | I/O      | TT_a                                                            | -                                                                               | TIM2_CH1, TIM2_ETR,<br>TIM8_CH1N, SPI1_SCK,<br>LPTIM2_ETR, EVENTOUT                             | ADC12_IN10,<br>DAC1_OUT2                      |

| 22     | 31      | L4       | 42      | PA6                                   | I/O      | FT_a                                                            | TIM1_BKIN, TIM3_CH1,<br>TIM8_BKIN, SPI1_MISO,<br>USART3_CTS,                    |                                                                                                 | OPAMP2_VINP,<br>ADC12_IN11                    |

| -      | -       | M4       | -       | OPAMP2_VINM                           | I        | TT                                                              | -                                                                               | -                                                                                               | -                                             |

| 23     | 32      | J5       | 43      | PA7                                   | I/O      | FT_a                                                            |                                                                                 |                                                                                                 | OPAMP2_VINM,<br>ADC12_IN12                    |

| 24     | 33      | K5       | 44      | PC4                                   | I/O      | FT_a                                                            | -                                                                               | USART3_TX, EVENTOUT                                                                             | COMP1_INM,<br>ADC12_IN13                      |

Table 15. STM32L471xx pin definitions (continued)

|        | Pin N   | lumbe    | r       |                                       |          | â                                                                                 |   | Pin funct                                                                                         | ions                 |

|--------|---------|----------|---------|---------------------------------------|----------|-----------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | Pin type                                                                          |   | Alternate functions                                                                               | Additional functions |

| -      | 40      | M8       | 60      | PE9                                   | I/O      | FT                                                                                | - | TIM1_CH1,<br>DFSDM_CKOUT,<br>FMC_D6, SAI1_FS_B,<br>EVENTOUT                                       | -                    |

| -      | -       | F6       | 61      | VSS                                   | S        | -                                                                                 | - | -                                                                                                 | -                    |

| -      | -       | G6       | 62      | VDD                                   | S        | -                                                                                 | - | -                                                                                                 | -                    |

| -      | 41      | L8       | 63      | PE10                                  | I/O      | FT                                                                                | - | TIM1_CH2N,<br>DFSDM_DATIN4,<br>TSC_G5_IO1,<br>QUADSPI_CLK, FMC_D7,<br>SAI1_MCLK_B,<br>EVENTOUT    | -                    |

| -      | 42      | M9       | 64      | PE11                                  | I/O      | FT - TIM1_CH2,<br>DFSDM_CKIN4,<br>TSC_G5_IO2,<br>QUADSPI_NCS, FMC_D8,<br>EVENTOUT |   | DFSDM_CKIN4,<br>TSC_G5_IO2,<br>QUADSPI_NCS, FMC_D8,                                               | -                    |

| -      | 43      | L9       | 65      | PE12                                  | I/O      | FT                                                                                | - | TIM1_CH3N, SPI1_NSS,<br>DFSDM_DATIN5,<br>TSC_G5_IO3,<br>QUADSPI_BK1_IO0,<br>FMC_D9, EVENTOUT      | -                    |

| -      | 44      | M10      | 66      | PE13                                  | I/O      | FT                                                                                | - | TIM1_CH3, SPI1_SCK,<br>DFSDM_CKIN5,<br>TSC_G5_IO4,<br>QUADSPI_BK1_IO1,<br>FMC_D10, EVENTOUT       | -                    |

| -      | 45      | M11      | 67      | PE14                                  | I/O      | FT                                                                                | - | TIM1_CH4, TIM1_BKIN2,<br>TIM1_BKIN2_COMP2,<br>SPI1_MISO,<br>QUADSPI_BK1_IO2,<br>FMC_D11, EVENTOUT | -                    |

| -      | 46      | M12      | 68      | PE15                                  | I/O      | FT                                                                                | - | TIM1_BKIN,<br>TIM1_BKIN_COMP1,<br>SPI1_MOSI,<br>QUADSPI_BK1_IO3,<br>FMC_D12, EVENTOUT             | -                    |

Table 15. STM32L471xx pin definitions (continued)

- For operation with voltage higher than Min (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDIO2</sub>) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- 4. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.5: Thermal characteristics).

- 5. In low-power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.5: Thermal characteristics).

### 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 23* are derived from tests performed under the ambient temperature condition summarized in *Table 22*.

| Table 23. Operating conditions at power-up / power-down |                                   |            |     |     |       |  |  |  |

|---------------------------------------------------------|-----------------------------------|------------|-----|-----|-------|--|--|--|

| Symbol                                                  | Parameter                         | Conditions | Min | Max | Unit  |  |  |  |

| +                                                       | V <sub>DD</sub> rise time rate    |            | 0   | 8   | uo/\/ |  |  |  |

| t <sub>VDD</sub>                                        | V <sub>DD</sub> fall time rate    | -          | 10  | 8   | μs/V  |  |  |  |

| t                                                       | V <sub>DDA</sub> rise time rate   | _          | 0   | 8   | µs/V  |  |  |  |

| t <sub>VDDA</sub>                                       | V <sub>DDA</sub> fall time rate   | -          | 10  | 8   | μ5/ V |  |  |  |

| t                                                       | V <sub>DDIO2</sub> rise time rate | _          | 0   | 8   | µs/V  |  |  |  |

| tvddio2                                                 | V <sub>DDIO2</sub> fall time rate | -          | 10  | 8   | μ3/ V |  |  |  |

Table 23. Operating conditions at power-up / power-down

### 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 24* are derived from tests performed under the ambient temperature conditions summarized in *Table 22: General operating conditions*.

| Symbol                               | Parameter                                     | Conditions <sup>(1)</sup> | Min  | Тур  | Max  | Unit |  |

|--------------------------------------|-----------------------------------------------|---------------------------|------|------|------|------|--|

| t <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization after<br>BOR0 is detected | V <sub>DD</sub> rising    | -    | 250  | 400  | μs   |  |

| V <sub>BOR0</sub> <sup>(2)</sup>     | Brown-out reset threshold 0                   | Rising edge               | 1.62 | 1.66 | 1.7  | V    |  |

| VBOR0                                | Brown-out reset threshold 0                   | Falling edge              | 1.6  | 1.64 | 1.69 | v    |  |

| V                                    | Brown-out reset threshold 1                   | Rising edge               | 2.06 | 2.1  | 2.14 | V    |  |

| V <sub>BOR1</sub>                    |                                               | Falling edge              | 1.96 | 2    | 2.04 | v    |  |

| N.                                   | Brown-out reset threshold 2                   | Rising edge               | 2.26 | 2.31 | 2.35 | V    |  |

| V <sub>BOR2</sub>                    | brown-out reset threshold 2                   | Falling edge              | 2.16 | 2.20 | 2.24 | v    |  |

| N.                                   | Brown-out reset threshold 3                   | Rising edge               | 2.56 | 2.61 | 2.66 | V    |  |

| V <sub>BOR3</sub>                    | Brown-out reset threshold 5                   | Falling edge              | 2.47 | 2.52 | 2.57 | v    |  |

| V                                    | Brown-out reset threshold 4                   | Rising edge               | 2.85 | 2.90 | 2.95 | V    |  |

| V <sub>BOR4</sub>                    | Brown-out reset threshold 4                   | Falling edge              | 2.76 | 2.81 | 2.86 | v    |  |

|                                      | Programmable voltage                          | Rising edge               | 2.1  | 2.15 | 2.19 | v    |  |

| V <sub>PVD0</sub>                    | detector threshold 0                          | Falling edge              | 2    | 2.05 | 2.1  |      |  |

Table 24. Embedded reset and power control block characteristics

|                         |                                                        |                                                                   | Conditio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ons                         | TYP   |      | ТҮР   |        |

|-------------------------|--------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|------|-------|--------|

| Symbol                  | Parameter                                              | -                                                                 | Voltage<br>scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Code                        | 25 °C | Unit | 25 °C | Unit   |

|                         |                                                        |                                                                   | and the second sec | Reduced code <sup>(1)</sup> | 2.9   |      | 111   |        |

|                         |                                                        |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Coremark                    | 3.1   |      | 118   |        |

|                         |                                                        | £ _ £                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dhrystone 2.1               | 3.1   | mA   | 119   | µA/MHz |

|                         |                                                        | f <sub>HCLK</sub> = f <sub>HSE</sub> up<br>to 48 MHz              | Ran<br>f <sub>HCLK</sub> =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Fibonacci                   | 2.9   |      | 112   |        |

| L (Bup)                 | Supply                                                 | included, bypass<br>mode PLL ON                                   | f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | While(1)                    | 2.8   |      | 108   |        |

| I <sub>DD</sub> (Run)   | D(Run) current in mode PLL ON<br>Run mode above 48 MHz |                                                                   | e 1<br>0 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reduced code <sup>(1)</sup> | 10.2  |      | 127   | µA/MHz |

|                         |                                                        | all peripherals<br>disable                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Coremark                    | 10.9  | mA   | 136   |        |

|                         |                                                        |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dhrystone 2.1               | 11.0  |      | 137   |        |

|                         |                                                        |                                                                   | Ra<br>fHCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Fibonacci                   | 10.5  |      | 131   |        |

|                         |                                                        |                                                                   | Ļ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | While(1)                    | 9.9   |      | 124   |        |

|                         |                                                        |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reduced code <sup>(1)</sup> | 272   |      | 136   |        |

|                         | Supply                                                 |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Coremark                    | 291   |      | 145   |        |

| I <sub>DD</sub> (LPRun) | current in<br>Low-power                                | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 M<br>all peripherals dis |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dhrystone 2.1               | 302   | μA   | 151   | µA/MHz |

|                         | run                                                    |                                                                   | Fibonacci                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 269                         | 1     | 135  |       |        |

|                         |                                                        |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | While(1)                    | 269   |      | 135   |        |

# Table 29. Typical current consumption in Run and Low-power run modes, with different codesrunning from Flash, ART enable (Cache ON Prefetch OFF)

1. Reduced code used for characterization results provided in Table 26, Table 27, Table 28.

| Symbol               | Parameter                                                          |                            | Conditions                  | Тур  | Max   | Unit |  |

|----------------------|--------------------------------------------------------------------|----------------------------|-----------------------------|------|-------|------|--|

|                      |                                                                    |                            | Wakeup clock MSI = 48 MHz   | 6.2  | 10.2  |      |  |

|                      |                                                                    | Range 1                    | Wakeup clock HSI16 = 16 MHz | 6.3  | 8.99  |      |  |

|                      | Wake up time from Stop 1<br>mode to Run mode in Flash              |                            | Wakeup clock MSI = 24 MHz   | 6.3  | 10.46 | 16   |  |

|                      |                                                                    | Range 2                    | Wakeup clock HSI16 = 16 MHz | 6.3  | 8.87  |      |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.0  | 13.23 |      |  |

|                      |                                                                    | Danas 1                    | Wakeup clock MSI = 48 MHz   | 4.5  | 5.78  |      |  |

|                      | Wake up time from Stop 1                                           | Range 1                    | Wakeup clock HSI16 = 16 MHz | 5.5  | 7.1   |      |  |

| t <sub>WUSTOP1</sub> | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 5.0  | 6.5   | μs   |  |

|                      | SRAM1                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 5.5  | 7.1   |      |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.2  | 13.5  |      |  |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in Flash | Regulator in<br>low-power  | Wokeup eleek MSL = 2 MHz    | 12.7 | 20    |      |  |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in SRAM1 | mode (LPR=1 in<br>PWR_CR1) | Wakeup clock MSI = 2 MHz    | 10.7 | 21.5  |      |  |

|                      |                                                                    | Dense 1                    | Wakeup clock MSI = 48 MHz   | 8.0  | 9.4   |      |  |

|                      |                                                                    | Range 1                    | Wakeup clock HSI16 = 16 MHz | 7.3  | 9.3   |      |  |

|                      | Wake up time from Stop 2<br>mode to Run mode in Flash              |                            | Wakeup clock MSI = 24 MHz   | 8.2  | 9.9   |      |  |

|                      |                                                                    | Range 2                    | Wakeup clock HSI16 = 16 MHz | 7.3  | 9.3   |      |  |

| +                    |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 10.6 | 15.8  |      |  |

| twustop2             |                                                                    | Range 1                    | Wakeup clock MSI = 48 MHz   | 5.1  | 6.7   | μs   |  |

|                      | Wake up time from Stop 2                                           | Range                      | Wakeup clock HSI16 = 16 MHz | 5.7  | 8     |      |  |

|                      | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 5.5  | 6.65  |      |  |

|                      | SRAM1                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 5.7  | 7.53  |      |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.2  | 16.6  |      |  |

| turiore              | Wakeup time from Standby                                           | Range 1                    | Wakeup clock MSI = 8 MHz    | 14.3 | 20.8  | μs   |  |

| t <sub>WUSTBY</sub>  | mode to Run mode                                                   | Range 1                    | Wakeup clock MSI = 4 MHz    | 20.1 | 35.5  | μο   |  |

| t <sub>WUSTBY</sub>  | Wakeup time from Standby                                           | Range 1                    | Wakeup clock MSI = 8 MHz    | 14.3 | 24.3  | μs   |  |

| SRAM2                | with SRAM2 to Run mode                                             |                            | Wakeup clock MSI = 4 MHz    | 20.1 | 38.5  | μo   |  |

| t <sub>WUSHDN</sub>  | Wakeup time from<br>Shutdown mode to Run<br>mode                   | Range 1                    | Wakeup clock MSI = 4 MHz    | 256  | 330.6 | μs   |  |

Table 41. Low-power mode wakeup timings<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

### 6.3.8 Internal clock source characteristics

The parameters given in *Table 47* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22: General operating conditions*. The provided curves are characterization results, not tested in production.

### High-speed internal (HSI16) RC oscillator

| Symbol                                   | Parameter                                                | Conditions                                    | Min   | Тур | Мах   | Unit |  |

|------------------------------------------|----------------------------------------------------------|-----------------------------------------------|-------|-----|-------|------|--|

| f <sub>HSI16</sub>                       | HSI16 Frequency                                          | V <sub>DD</sub> =3.0 V, T <sub>A</sub> =30 °C | 15.88 | -   | 16.08 | MHz  |  |

| TRIM                                     | HSI16 user trimming step                                 | Trimming code is not a multiple of 64         | 0.2   | 0.3 | 0.4   | %    |  |

| IRIM                                     | nono user timining step                                  | Trimming code is a multiple of 64             | -4    | -6  | -8    |      |  |

| DuCy(HSI16) <sup>(2)</sup>               | Duty Cycle                                               | -                                             | 45    | -   | 55    | %    |  |

| A (USI16)                                | HSI16 oscillator frequency                               | T <sub>A</sub> = 0 to 85 °C                   | -1    | -   | 1     | %    |  |

| ∆ <sub>Temp</sub> (HSI16)                | drift over temperature                                   | T <sub>A</sub> = -40 to 125 °C                | -2    | -   | 1.5   | %    |  |

| ∆ <sub>VDD</sub> (HSI16)                 | HSI16 oscillator frequency<br>drift over V <sub>DD</sub> | V <sub>DD</sub> =1.62 V to 3.6 V              | -0.1  | -   | 0.05  | %    |  |

| t <sub>su</sub> (HSI16) <sup>(2)</sup>   | HSI16 oscillator start-up time                           | -                                             | -     | 0.8 | 1.2   | μs   |  |

| t <sub>stab</sub> (HSI16) <sup>(2)</sup> | HSI16 oscillator<br>stabilization time                   | -                                             | -     | 3   | 5     | μs   |  |

| I <sub>DD</sub> (HSI16) <sup>(2)</sup>   | HSI16 oscillator power<br>consumption                    | -                                             | -     | 155 | 190   | μA   |  |

| Table 47. HS | 116 oscillator | <sup>r</sup> characteristics <sup>(1)</sup> |

|--------------|----------------|---------------------------------------------|

|--------------|----------------|---------------------------------------------|

1. Guaranteed by characterization results.

2. Guaranteed by design.

| Sym-<br>bol | Parameter                                      | Conditions <sup>(4)</sup>                                                                                                                                                    |                 |                          |      | Тур  | Max | Unit           |  |

|-------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|------|------|-----|----------------|--|

|             |                                                |                                                                                                                                                                              | Single          | Fast channel (max speed) | -    | 4    | 5   |                |  |

| ET          | Total                                          |                                                                                                                                                                              | ended           | Slow channel (max speed) | -    | 4    | 5   | 1              |  |

|             | unadjusted<br>error                            |                                                                                                                                                                              | Differential    | Fast channel (max speed) | -    | 3.5  | 4.5 |                |  |

|             |                                                |                                                                                                                                                                              |                 | Slow channel (max speed) | -    | 3.5  | 4.5 |                |  |

|             | Offset                                         |                                                                                                                                                                              | Single<br>ended | Fast channel (max speed) | -    | 1    | 2.5 |                |  |

| EO          |                                                |                                                                                                                                                                              |                 | Slow channel (max speed) | -    | 1    | 2.5 |                |  |

| LU          | error                                          |                                                                                                                                                                              | Differential    | Fast channel (max speed) | -    | 1.5  | 2.5 |                |  |

|             |                                                | ADC clock frequency $\leq$<br>80 MHz,<br>Sampling rate $\leq$ 5.33 Msps,<br>V <sub>DDA</sub> = VREF + = 3 V,<br>TA = 25 °Ctrive<br>ber ofal-to-<br>e and<br>rtional-to-<br>e |                 | Slow channel (max speed) | -    | 1.5  | 2.5 |                |  |

|             |                                                |                                                                                                                                                                              | Single<br>ended | Fast channel (max speed) | -    | 2.5  | 4.5 | LSB            |  |

| EG          | Cain orror                                     |                                                                                                                                                                              |                 | Slow channel (max speed) | -    | 2.5  | 4.5 |                |  |

| EG          | Gain error                                     |                                                                                                                                                                              | Differential    | Fast channel (max speed) | -    | 2.5  | 3.5 |                |  |

|             |                                                |                                                                                                                                                                              |                 | Slow channel (max speed) | -    | 2.5  | 3.5 |                |  |

|             | Differential<br>linearity<br>error             |                                                                                                                                                                              | Single<br>ended | Fast channel (max speed) | -    | 1    | 1.5 |                |  |

| ED          |                                                |                                                                                                                                                                              |                 | Slow channel (max speed) | -    | 1    | 1.5 |                |  |

| ED          |                                                |                                                                                                                                                                              | Differential    | Fast channel (max speed) | -    | 1    | 1.2 |                |  |

|             |                                                |                                                                                                                                                                              |                 | Slow channel (max speed) | -    | 1    | 1.2 |                |  |

|             | Integral<br>linearity<br>error                 |                                                                                                                                                                              | Single<br>ended | Fast channel (max speed) | -    | 1.5  | 2.5 |                |  |

| EL          |                                                |                                                                                                                                                                              |                 | Slow channel (max speed) | -    | 1.5  | 2.5 |                |  |

| LL          |                                                |                                                                                                                                                                              | Differential    | Fast channel (max speed) | -    | 1    | 2   |                |  |