# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                     |

|----------------------------|--------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                            |

| Core Size                  | 32-Bit Single-Core                                                                         |

| Speed                      | 80MHz                                                                                      |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                                      |

| Number of I/O              | 82                                                                                         |

| Program Memory Size        | 1MB (1M x 8)                                                                               |

| Program Memory Type        | FLASH                                                                                      |

| EEPROM Size                | -                                                                                          |

| RAM Size                   | 128K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                      |

| Oscillator Type            | Internal                                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                              |

| Package / Case             | 100-LQFP                                                                                   |

| Supplier Device Package    | 100-LQFP (14x14)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l471vgt6                      |

|                            |                                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.12 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. Fast I/O toggling can be achieved thanks to their mapping on the AHB2 bus.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

### 3.13 Direct memory access controller (DMA)

The device embeds 2 DMAs. Refer to *Table 7: DMA implementation* for the features implementation.

Direct memory access (DMA) is used in order to provide high-speed data transfer between peripherals and memory as well as memory to memory. Data can be quickly moved by DMA without any CPU actions. This keeps CPU resources free for other operations.

The two DMA controllers have 14 channels in total, each dedicated to managing memory access requests from one or more peripherals. Each has an arbiter for handling the priority between DMA requests.

The DMA supports:

- 14 independently configurable channels (requests)

- Each channel is connected to dedicated hardware DMA requests, software trigger is also supported on each channel. This configuration is done by software.

- Priorities between requests from channels of one DMA are software programmable (4 levels consisting of very high, high, medium, low) or hardware in case of equality (request 1 has priority over request 2, etc.)

- Independent source and destination transfer size (byte, half word, word), emulating packing and unpacking. Source/destination addresses must be aligned on the data size.

- Support for circular buffer management

- 3 event flags (DMA Half Transfer, DMA Transfer complete and DMA Transfer Error) logically ORed together in a single interrupt request for each channel

- Memory-to-memory transfer

- Peripheral-to-memory and memory-to-peripheral, and peripheral-to-peripheral transfers

- Access to Flash, SRAM, APB and AHB peripherals as source and destination

- Programmable number of data to be transferred: up to 65536.

#### Table 7. DMA implementation

| DMA features               | DMA1 | DMA2 |

|----------------------------|------|------|

| Number of regular channels | 7    | 7    |

### 3.15 Analog to digital converter (ADC)

The device embeds 3 successive approximation analog-to-digital converters with the following features:

- 12-bit native resolution, with built-in calibration

- 5.33 Msps maximum conversion rate with full resolution

- Down to 18.75 ns sampling time

- Increased conversion rate for lower resolution (up to 8.88 Msps for 6-bit resolution)

- Up to 24 external channels, some of them shared between ADC1 and ADC2, or ADC1, ADC2 and ADC3.

- 5 Internal channels: internal reference voltage, temperature sensor, VBAT/3, DAC1 and DAC2 outputs.

- One external reference pin is available on some package, allowing the input voltage range to be independent from the power supply

- Single-ended and differential mode inputs

- Low-power design

- Capable of low-current operation at low conversion rate (consumption decreases linearly with speed)

- Dual clock domain architecture: ADC speed independent from CPU frequency

- Highly versatile digital interface

- Single-shot or continuous/discontinuous sequencer-based scan mode: 2 groups of analog signals conversions can be programmed to differentiate background and high-priority real-time conversions

- Handles two ADC converters for dual mode operation (simultaneous or interleaved sampling modes)

- Each ADC support multiple trigger inputs for synchronization with on-chip timers and external signals

- Results stored into 3 data register or in RAM with DMA controller support

- Data pre-processing: left/right alignment and per channel offset compensation

- Built-in oversampling unit for enhanced SNR

- Channel-wise programmable sampling time

- Three analog watchdog for automatic voltage monitoring, generating interrupts and trigger for selected timers

- Hardware assistant to prepare the context of the injected channels to allow fast context switching

#### 3.15.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{TS}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC1\_IN17 and ADC3\_IN17 input channels which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

DocID027226 Rev 1

### 3.22 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

### 3.23 Timers and watchdogs

The STM32L471 includes two advanced control timers, up to nine general-purpose timers, two basic timers, two low-power timers, two watchdog timers and a SysTick timer. The table below compares the features of the advanced control, general purpose and basic timers.

| Timer type          | Timer resolution type factor |        | Prescaler<br>factor  | DMA Capture/<br>request compare<br>generation channels |     | Complementary<br>outputs |    |  |  |  |  |  |

|---------------------|------------------------------|--------|----------------------|--------------------------------------------------------|-----|--------------------------|----|--|--|--|--|--|

| Advanced control    | TIM1, TIM8                   | 16-bit | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536                  | Yes | 4                        | 3  |  |  |  |  |  |

| General-<br>purpose | TIM2, TIM5                   | 32-bit | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536                  | Yes | 4                        | No |  |  |  |  |  |

| General-<br>purpose | TIM3, TIM4                   | 16-bit | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536                  | Yes | 4                        | No |  |  |  |  |  |

| General-<br>purpose | TIM15                        | 16-bit | Up                   | Any integer<br>between 1<br>and 65536                  | Yes | 2                        | 1  |  |  |  |  |  |

| General-<br>purpose | TIM16, TIM17                 | 16-bit | Up                   | Any integer<br>between 1<br>and 65536                  | Yes | 1                        | 1  |  |  |  |  |  |

| Basic               | TIM6, TIM7                   | 16-bit | Up                   | Any integer<br>between 1<br>and 65536                  | Yes | 0                        | No |  |  |  |  |  |

Table 10. Timer feature comparison

### 3.23.1 Advanced-control timer (TIM1, TIM8)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

DocID027226 Rev 1

| SAI features <sup>(1)</sup>                            | SAI1       | SAI2       |

|--------------------------------------------------------|------------|------------|

| I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97         | Х          | Х          |

| Mute mode                                              | Х          | Х          |

| Stereo/Mono audio frame capability.                    | Х          | Х          |

| 16 slots                                               | Х          | Х          |

| Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit | Х          | X          |

| FIFO Size                                              | X (8 Word) | X (8 Word) |

| SPDIF                                                  | Х          | Х          |

Table 13. SAI implementation

1. X: supported

### 3.30 Single wire protocol master interface (SWPMI)

The Single wire protocol master interface (SWPMI) is the master interface corresponding to the Contactless Frontend (CLF) defined in the ETSI TS 102 613 technical specification. The main features are:

- full-duplex communication mode

- automatic SWP bus state management (active, suspend, resume)

- configurable bitrate up to 2 Mbit/s

- automatic SOF, EOF and CRC handling

SWPMI can be served by the DMA controller.

### 3.31 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

The CAN peripheral supports:

- Supports CAN protocol version 2.0 A, B Active

- Bit rates up to 1 Mbit/s

|        | Pin N   | umbe     | r       |                                       |          |               |       | Pin funct                                                                                                         | ions                               |  |  |

|--------|---------|----------|---------|---------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|

| LQFP64 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                               | Additional functions               |  |  |

| 25     | 34      | L5       | 45      | PC5                                   | I/O      | FT_a          | -     | USART3_RX, EVENTOUT                                                                                               | COMP1_INP,<br>ADC12_IN14,<br>WKUP5 |  |  |

| 26     | 35      | M5       | 46      | PB0                                   | I/O      | TT_a          | -     | TIM1_CH2N, TIM3_CH3,<br>TIM8_CH2N,<br>USART3_CK,<br>QUADSPI_BK1_IO1,<br>COMP1_OUT, EVENTOUT                       | OPAMP2_<br>VOUT, ADC12_IN15        |  |  |

| 27     | 36      | M6       | 47      | PB1                                   | I/O      | FT_a          | -     | TIM1_CH3N, TIM3_CH4,<br>TIM8_CH3N,<br>DFSDM_DATIN0,<br>USART3_RTS_DE,<br>QUADSPI_BK1_IO0,<br>LPTIM2_IN1, EVENTOUT | COMP1_INM,<br>ADC12_IN16           |  |  |

| 28     | 37      | L6       | 48      | PB2                                   | I/O      | FT_a          | -     | RTC_OUT, LPTIM1_OUT,<br>I2C3_SMBA,<br>DFSDM_CKIN0,<br>EVENTOUT                                                    | COMP1_INP                          |  |  |

| -      | -       | K6       | 49      | PF11                                  | I/O      | FT            | -     | EVENTOUT                                                                                                          | -                                  |  |  |

| -      | -       | J7       | 50      | PF12                                  | I/O      | FT            | -     | FMC_A6, EVENTOUT                                                                                                  | -                                  |  |  |

| -      | -       | -        | 51      | VSS                                   | S        | -             | -     | -                                                                                                                 | -                                  |  |  |

| -      | -       | -        | 52      | VDD                                   | S        | -             | -     | -                                                                                                                 | -                                  |  |  |

| -      | -       | K7       | 53      | PF13                                  | I/O      | FT            | -     | DFSDM_DATIN6,<br>FMC_A7, EVENTOUT                                                                                 | -                                  |  |  |

| -      | -       | J8       | 54      | PF14                                  | I/O      | FT            | -     | DFSDM_CKIN6,<br>TSC_G8_IO1, FMC_A8,<br>EVENTOUT                                                                   | -                                  |  |  |

| -      | -       | J9       | 55      | PF15                                  | I/O      | FT            | -     | TSC_G8_IO2, FMC_A9,<br>EVENTOUT                                                                                   | -                                  |  |  |

| -      | -       | H9       | 56      | PG0                                   | I/O      | FT            | -     | TSC_G8_IO3, FMC_A10,<br>EVENTOUT                                                                                  | -                                  |  |  |

| -      | -       | G9       | 57      | PG1                                   | I/O      | FT            | -     | TSC_G8_IO4, FMC_A11,<br>EVENTOUT                                                                                  | -                                  |  |  |

| -      | 38      | M7       | 58      | PE7                                   | I/O      | FT            | -     | TIM1_ETR,<br>DFSDM_DATIN2,<br>FMC_D4, SAI1_SD_B,<br>EVENTOUT                                                      | -                                  |  |  |

| -      | 39      | L7       | 59      | PE8                                   | I/O      | FT            | -     | TIM1_CH1N,<br>DFSDM_CKIN2, FMC_D5,<br>SAI1_SCK_B, EVENTOUT                                                        | -                                  |  |  |

Table 15. STM32L471xx pin definitions (continued)

|        | Pin N   | umbe     | r       |                                       |          |               |       | Pin funct                                                                                                  | ions                 |

|--------|---------|----------|---------|---------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                        | Additional functions |

| 44     | 70      | B12      | 103     | PA11                                  | I/O      | FT            | -     | TIM1_CH4, TIM1_BKIN2,<br>USART1_CTS, CAN1_RX,<br>TIM1_BKIN2_COMP1,<br>EVENTOUT                             | -                    |

| 45     | 71      | A12      | 104     | PA12                                  | I/O      | FT            | -     | TIM1_ETR,<br>USART1_RTS_DE,<br>CAN1_TX, EVENTOUT                                                           | -                    |

| 46     | 72      | A11      | 105     | PA13<br>(JTMS-SWDIO)                  | I/O      | FT            | (3)   | JTMS-SWDIO, IR_OUT,<br>EVENTOUT                                                                            | -                    |

| 47     | -       | -        | -       | VSS                                   | S        | -             | -     | -                                                                                                          | -                    |

| 48     | 73      | C11      | 106     | VDD                                   | S        | -             | -     | -                                                                                                          | -                    |

| -      | 74      | F11      | 107     | VSS                                   | S        | -             | -     | -                                                                                                          | -                    |

| -      | 75      | G11      | 108     | VDD                                   | S        | -             | -     | -                                                                                                          | -                    |

| 49     | 76      | A10      | 109     | PA14<br>(JTCK-SWCLK)                  | I/O      | FT            | (3)   | JTCK-SWCLK,<br>EVENTOUT                                                                                    | -                    |

| 50     | 77      | A9       | 110     | PA15 (JTDI)                           | I/O      | FT            | (3)   | JTDI, TIM2_CH1,<br>TIM2_ETR, SPI1_NSS,<br>SPI3_NSS,<br>UART4_RTS_DE,<br>TSC_G3_IO1, SAI2_FS_B,<br>EVENTOUT | -                    |

| 51     | 78      | B11      | 111     | PC10                                  | I/O      | FT            | -     | SPI3_SCK, USART3_TX,<br>UART4_TX, TSC_G3_IO2,<br>SDMMC1_D2,<br>SAI2_SCK_B, EVENTOUT                        | -                    |

| 52     | 79      | C10      | 112     | PC11                                  | I/O      | FT            | -     | SPI3_MISO, USART3_RX,<br>UART4_RX, TSC_G3_IO3,<br>SDMMC1_D3,<br>SAI2_MCLK_B,<br>EVENTOUT                   | -                    |

| 53     | 80      | B10      | 113     | PC12                                  | I/O      | FT            | -     | SPI3_MOSI, USART3_CK,<br>UART5_TX, TSC_G3_IO4,<br>SDMMC1_CK,<br>SAI2_SD_B, EVENTOUT                        | -                    |

| -      | 81      | C9       | 114     | PD0                                   | I/O      | FT            | -     | SPI2_NSS,<br>DFSDM_DATIN7,<br>CAN1_RX, FMC_D2,<br>EVENTOUT                                                 | -                    |

| S   |

|-----|

|     |

| _   |

| 2   |

| _   |

| ω   |

| N   |

|     |

| 4   |

| 1   |

| -   |

| ×   |

| - Q |

| ~   |

|     |

Pinouts and pin description

|        |      | AF0        | AF1                                | AF2                              | AF3       | AF4            | AF5         | AF6        | AF7                          |

|--------|------|------------|------------------------------------|----------------------------------|-----------|----------------|-------------|------------|------------------------------|

| Port   |      | SYS_AF     | TIM1/TIM2/<br>TIM5/TIM8/<br>LPTIM1 | TIM1/TIM2/<br>TIM3/TIM4/<br>TIM5 | TIM8      | 12C1/12C2/12C3 | SPI1/SPI2   | SPI3/DFSDM | USART1/<br>USART2/<br>USART3 |

|        | PA0  | -          | TIM2_CH1                           | TIM5_CH1                         | TIM8_ETR  | -              | -           | -          | USART2_CT                    |

|        | PA1  | -          | TIM2_CH2                           | TIM5_CH2                         | -         | -              | -           | -          | USART2_RTS<br>DE             |

|        | PA2  | -          | TIM2_CH3                           | TIM5_CH3                         | -         | -              | -           | -          | USART2_T>                    |

|        | PA3  | -          | TIM2_CH4                           | TIM5_CH4                         | -         | -              | -           | -          | USART2_R                     |

|        | PA4  | 4          |                                    | -                                | -         | SPI1_NSS       | SPI3_NSS    | USART2_C   |                              |

|        | PA5  | -          | TIM2_CH1                           | TIM2_ETR                         | TIM8_CH1N | -              | SPI1_SCK    | -          | -                            |

|        | PA6  | -          | TIM1_BKIN                          | TIM3_CH1                         | TIM8_BKIN | -              | - SPI1_MISO |            | USART3_CT                    |

|        | PA7  | -          | TIM1_CH1N                          | TIM3_CH2                         | TIM8_CH1N | -              | SPI1_MOSI   | -          | -                            |

| Port A | PA8  | МСО        | TIM1_CH1                           | -                                | -         | -              | -           | -          | USART1_C                     |

|        | PA9  | -          | TIM1_CH2                           | -                                | -         | -              | -           | -          | USART1_T                     |

|        | PA10 | -          | TIM1_CH3                           | -                                | -         | -              | -           | -          | USART1_R                     |

|        | PA11 | -          | TIM1_CH4                           | TIM1_BKIN2                       | -         | -              | -           | -          | USART1_C1                    |

|        | PA12 | -          | TIM1_ETR                           | -                                | -         | -              | _           | -          | USART1_RT<br>DE              |

|        | PA13 | JTMS-SWDIO | IR_OUT                             | -                                | -         | -              | -           | -          | -                            |

|        | PA14 | JTCK-SWCLK | -                                  | -                                | -         | -              | -           | -          | -                            |

|        | PA15 | JTDI       | TIM2_CH1                           | TIM2_ETR                         | -         | -              | SPI1_NSS    | SPI3_NSS   | _                            |

DocID027226 Rev 1

5

71/218

|        |      | AF8                         | AF9        | AF10            | AF11 | AF12                                    | AF13                   | AF14                                    | AF15     |  |

|--------|------|-----------------------------|------------|-----------------|------|-----------------------------------------|------------------------|-----------------------------------------|----------|--|

| Port   |      | UART4,<br>UART5,<br>LPUART1 | CAN1, TSC  | QUADSPI         | -    | SDMMC1, COMP1,<br>COMP2, FMC,<br>SWPMI1 | SAI1, SAI2             | TIM2, TIM15,<br>TIM16, TIM17,<br>LPTIM2 | EVENTOUT |  |

|        | PE0  | -                           | -          | -               | -    | FMC_NBL0                                | -                      | TIM16_CH1                               | EVENTOU  |  |

|        | PE1  | -                           | -          | -               | -    | FMC_NBL1                                | -                      | TIM17_CH1                               | EVENTOU  |  |

|        | PE2  | -                           | TSC_G7_IO1 | -               | -    | FMC_A23                                 | SAI1_MCLK_<br>A        | -                                       | EVENTOU  |  |

|        | PE3  | -                           | TSC_G7_IO2 | -               | -    | FMC_A19                                 | SAI1_SD_B              | -                                       | EVENTOU  |  |

| -      | PE4  | -                           | TSC_G7_IO3 | -               | -    | FMC_A20                                 | SAI1_FS_A              | -                                       | EVENTOU  |  |

|        | PE5  | -                           | TSC_G7_IO4 | -               | -    | FMC_A21                                 | SAI1_SCK_A             | -                                       | EVENTOU  |  |

|        | PE6  | -                           | -          | -               | -    | FMC_A22                                 | SAI1_SD_A              | -                                       | EVENTOU  |  |

|        | PE7  | -                           | -          | -               | -    | FMC_D4                                  | SAI1_SD_B              | -                                       | EVENTOU  |  |

| Port E | PE8  | -                           | -          | -               | -    | FMC_D5                                  | SAI1_SCK_B             | -                                       | EVENTOU  |  |

|        | PE9  | -                           | -          | -               | -    | FMC_D6                                  | SAI1_FS_B              | -                                       | EVENTOU  |  |

|        | PE10 | -                           | TSC_G5_IO1 | QUADSPI_CLK     | -    | FMC_D7                                  | FMC_D7 SAI1_MCLK_<br>B |                                         | EVENTOU  |  |

|        | PE11 | -                           | TSC_G5_IO2 | QUADSPI_NCS     | -    | FMC_D8                                  | -                      | -                                       | EVENTOU  |  |

|        | PE12 | -                           | TSC_G5_IO3 | QUADSPI_BK1_IO0 | -    | FMC_D9                                  | -                      | -                                       | EVENTOU  |  |

|        | PE13 | -                           | TSC_G5_IO4 | QUADSPI_BK1_IO1 | -    | FMC_D10                                 | -                      | -                                       | EVENTOU  |  |

|        | PE14 | -                           | -          | QUADSPI_BK1_IO2 | -    | FMC_D11                                 | -                      | -                                       | EVENTOU  |  |

|        | PE15 | _                           | -          | QUADSPI_BK1_IO3 | -    | FMC_D12                                 | -                      | -                                       | EVENTOL  |  |

5

STM32L471xx

Pinouts and pin description

|                   |                         |                      | Table 26. Currer                                                                                                                  |                    | ption in F<br>from Flasl |       | -     |       |        |        |       | process            | ing   |        |        |      |

|-------------------|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------|-------|-------|-------|--------|--------|-------|--------------------|-------|--------|--------|------|

|                   |                         |                      | Conditions                                                                                                                        |                    |                          | ТҮР   |       |       |        |        |       | MAX <sup>(1)</sup> |       |        |        |      |

|                   | Symbol                  | Parameter            | -                                                                                                                                 | Voltage<br>scaling | f <sub>HCLK</sub>        | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C              | 85 °C | 105 °C | 125 °C | Unit |

|                   |                         |                      | f <sub>HCLK</sub> = f <sub>HSE</sub> up to<br>48MHz included,<br>bypass mode<br>PLL ON above<br>48 MHz all<br>peripherals disable |                    | 26 MHz                   | 2.88  | 2.93  | 3.05  | 3.23   | 3.58   | 3.20  | 3.37               | 3.51  | 3.93   | 4.76   |      |

|                   |                         |                      |                                                                                                                                   |                    | 16 MHz                   | 1.83  | 1.87  | 1.98  | 2.16   | 2.49   | 2.01  | 2.16               | 2.30  | 2.72   | 3.34   |      |

|                   |                         |                      |                                                                                                                                   |                    | 8 MHz                    | 0.98  | 1.02  | 1.12  | 1.29   | 1.62   | 1.10  | 1.17               | 1.31  | 1.73   | 2.56   |      |

|                   |                         |                      |                                                                                                                                   | Range 2            | 4 MHz                    | 0.55  | 0.59  | 0.69  | 0.85   | 1.18   | 0.61  | 0.70               | 0.89  | 1.24   | 1.95   |      |

|                   |                         |                      |                                                                                                                                   |                    | 2 MHz                    | 0.34  | 0.37  | 0.47  | 0.64   | 0.96   | 0.37  | 0.46               | 0.64  | 0.98   | 1.71   |      |

|                   |                         |                      |                                                                                                                                   |                    | 1 MHz                    | 0.23  | 0.26  | 0.36  | 0.53   | 0.85   | 0.27  | 0.33               | 0.50  | 0.86   | 1.57   |      |

| D                 | L (Bup)                 | Supply current in    |                                                                                                                                   |                    | 100 kHz                  | 0.14  | 0.17  | 0.27  | 0.43   | 0.75   | 0.17  | 0.21               | 0.38  | 0.74   | 1.44   | mA   |

| DocID027226 Rev 1 | I <sub>DD</sub> (Run)   | Run mode             |                                                                                                                                   |                    | 80 MHz                   | 10.2  | 10.3  | 10.5  | 10.7   | 11.1   | 11.22 | 11.8               | 12.1  | 12.5   | 13.3   | IIIA |

| )272              |                         |                      |                                                                                                                                   |                    | 72 MHz                   | 9.24  | 9.31  | 9.47  | 9.69   | 10.1   | 10.16 | 10.7               | 11.0  | 11.4   | 12.2   |      |

| 26 F              |                         |                      |                                                                                                                                   |                    | 64 MHz                   | 8.25  | 8.32  | 8.46  | 8.68   | 9.09   | 9.08  | 9.6                | 9.9   | 10.3   | 11.1   |      |

| ζev γ             |                         |                      |                                                                                                                                   | Range 1            | 48 MHz                   | 6.28  | 6.35  | 6.5   | 6.72   | 7.11   | 6.91  | 7.3                | 7.6   | 8.0    | 8.8    | 1    |

| -                 |                         |                      |                                                                                                                                   |                    | 32 MHz                   | 4.24  | 4.30  | 4.44  | 4.65   | 5.04   | 4.66  | 4.97               | 5.26  | 5.67   | 6.51   | 1    |

|                   |                         |                      |                                                                                                                                   |                    | 24 MHz                   | 3.21  | 3.27  | 3.4   | 3.61   | 3.98   | 3.53  | 3.76               | 4.05  | 4.46   | 5.30   | 1    |

|                   |                         |                      |                                                                                                                                   |                    | 16 MHz                   | 2.19  | 2.24  | 2.36  | 2.56   | 2.94   | 2.41  | 2.66               | 2.95  | 3.16   | 3.99   | 1    |

|                   |                         | Quant                |                                                                                                                                   | •                  | 2 MHz                    | 272   | 303   | 413   | 592    | 958    | 330   | 393                | 579   | 954    | 1704   |      |

|                   |                         | Supply<br>current in | f <sub>HCLK</sub> = f <sub>MSI</sub>                                                                                              |                    | 1 MHz                    | 154   | 184   | 293   | 473    | 835    | 195   | 265                | 457   | 822    | 1572   |      |

|                   | I <sub>DD</sub> (LPRun) | Low-power            | all peripherals disat                                                                                                             | ole                | 400 kHz                  | 78    | 108   | 217   | 396    | 758    | 110   | 180                | 380   | 755    | 1505   | μA   |

|                   |                         | run mode             |                                                                                                                                   |                    | 100 kHz                  | 42    | 73    | 182   | 360    | 723    | 75    | 138                | 331   | 706    | 1456   | 1    |

1. Guaranteed by characterization results, unless otherwise specified.

|                         |                                  |                                                                                                                       | Conditio                              | ons                         | TYP   |      | ТҮР   |        |  |

|-------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|-------|------|-------|--------|--|

| Symbol                  | Parameter                        | -                                                                                                                     | - Voltage Code                        |                             | 25 °C | Unit | 25 °C | Unit   |  |

|                         |                                  |                                                                                                                       | z                                     | Reduced code <sup>(1)</sup> | 2.9   |      | 111   |        |  |

|                         |                                  |                                                                                                                       | 2<br>MH                               | Coremark                    | 3.1   |      | 118   |        |  |

|                         |                                  | $f_{HCLK} = f_{HSE}$ up<br>to 48 MHz<br>included, bypass<br>mode PLL ON<br>above 48 MHz<br>all peripherals<br>disable | Range 2<br><sub>:LK</sub> = 26 MHz    | Dhrystone 2.1               | 3.1   | mA   | 119   | µA/MHz |  |

|                         | Supply<br>current in<br>Run mode |                                                                                                                       | Ran<br>f <sub>HCLK</sub> =            | Fibonacci                   | 2.9   |      | 112   |        |  |

| I <sub>DD</sub> (Run)   |                                  |                                                                                                                       | Ę.                                    | While(1)                    | 2.8   |      | 108   |        |  |

|                         |                                  |                                                                                                                       | Range 1<br>f <sub>HCLK</sub> = 80 MHz | Reduced code <sup>(1)</sup> | 10.2  |      | 127   | µA/MHz |  |

|                         |                                  |                                                                                                                       |                                       | Coremark                    | 10.9  | mA   | 136   |        |  |

|                         |                                  |                                                                                                                       |                                       | Dhrystone 2.1               | 11.0  |      | 137   |        |  |

|                         |                                  |                                                                                                                       |                                       | Fibonacci                   | 10.5  |      | 131   |        |  |

|                         |                                  |                                                                                                                       | Ļ.                                    | While(1)                    | 9.9   |      | 124   |        |  |

|                         |                                  |                                                                                                                       |                                       | Reduced code <sup>(1)</sup> | 272   |      | 136   |        |  |

|                         | Supply                           |                                                                                                                       |                                       | Coremark                    | 291   |      | 145   |        |  |

| I <sub>DD</sub> (LPRun) | current in<br>Low-power          | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 M<br>all peripherals dis                                                     |                                       | Dhrystone 2.1               | 302   | μA   | 151   | µA/MHz |  |

|                         | run                              | - P                                                                                                                   |                                       | Fibonacci                   | 269   |      | 135   |        |  |

|                         |                                  |                                                                                                                       |                                       | While(1)                    | 269   |      | 135   |        |  |

# Table 29. Typical current consumption in Run and Low-power run modes, with different codesrunning from Flash, ART enable (Cache ON Prefetch OFF)

1. Reduced code used for characterization results provided in Table 26, Table 27, Table 28.

|        |                                              |                                                          | Table 38. Curre                                         | ent cor         | isumpt | ion in : | Shutdo | wn mod | le (cont | inued) |       |                    |        |                       |     |

|--------|----------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|-----------------|--------|----------|--------|--------|----------|--------|-------|--------------------|--------|-----------------------|-----|

| Svi    | Cumhal                                       | Devenuetor                                               | Conditions                                              |                 |        |          | TYP    |        |          |        |       | MAX <sup>(1)</sup> | )      |                       | 11  |

|        | Symbol                                       | mbol Parameter                                           | -                                                       | V <sub>DD</sub> | 25 °C  | 55 °C    | 85 °C  | 105 °C | 125 °C   | 25 °C  | 55 °C | 85 °C              | 105 °C | -<br>-<br>-<br>-<br>- |     |

|        |                                              |                                                          |                                                         | 1.8 V           | 210    | 378      | 1299   | 3437   | 9357     | -      | -     | -                  | -      | -                     |     |

|        |                                              | Supply current                                           | RTC clocked by LSE                                      | 2.4 V           | 303    | 499      | 1577   | 4056   | 10825    | -      | -     | -                  | -      | -                     |     |

|        |                                              | in Shutdown                                              | bypassed at 32768 Hz                                    | 3 V             | 422    | 655      | 1925   | 4820   | 12569    | -      | -     | -                  | -      | -                     |     |

|        | I <sub>DD</sub> (Shutdown                    | mode<br>(backup                                          |                                                         | 3.6 V           | 584    | 888      | 2511   | 6158   | 15706    | -      | -     | -                  | -      | -                     | n A |

|        | with RTC)                                    | registers                                                |                                                         | 1.8 V           | 329    | 499      | 1408   | 3460   | -        | -      | -     | -                  | -      | -                     |     |

|        |                                              | retained) RTC                                            | RTC clocked by LSE quartz <sup>(2)</sup> in low drive   | 2.4 V           | 431    | 634      | 1688   | 4064   | -        | -      | -     | -                  | -      | -                     |     |

|        |                                              | enabled                                                  | mode                                                    | 3 V             | 554    | 791      | 2025   | 4795   | -        | -      | -     | -                  | -      | -                     | nA  |

|        |                                              |                                                          |                                                         | 3.6 V           | 729    | 1040     | 2619   | 6129   | -        | -      | -     | -                  | -      | -                     |     |

| DocID0 | I <sub>DD</sub> (wakeup<br>from<br>Shutdown) | Supply current<br>during wakeup<br>from Shutdown<br>mode | Wakeup clock is<br>MSI = 4 MHz.<br>See <sup>(3)</sup> . | 3 V             | 0.6    | -        | -      | -      | -        | -      | -     | -                  | -      | -                     | mA  |

1. Guaranteed by characterization results, unless otherwise specified.

2. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

3. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in *Table 41: Low-power mode wakeup timings*.

DocID027226 Rev 1

### 6.3.8 Internal clock source characteristics

The parameters given in *Table 47* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22: General operating conditions*. The provided curves are characterization results, not tested in production.

#### High-speed internal (HSI16) RC oscillator

| Symbol                                   | Parameter                                                | Conditions                                    | Min   | Тур | Мах   | Unit |

|------------------------------------------|----------------------------------------------------------|-----------------------------------------------|-------|-----|-------|------|

| f <sub>HSI16</sub>                       | HSI16 Frequency                                          | V <sub>DD</sub> =3.0 V, T <sub>A</sub> =30 °C | 15.88 | -   | 16.08 | MHz  |

| TRIM                                     | HSI16 user trimming step                                 | Trimming code is not a multiple of 64         | 0.2   | 0.3 | 0.4   | %    |

| I INIM                                   | nono user timining step                                  | Trimming code is a multiple of 64             | -4    | -6  | -8    | 70   |

| DuCy(HSI16) <sup>(2)</sup>               | Duty Cycle                                               | -                                             | 45    | -   | 55    | %    |

| A (USI16)                                | HSI16 oscillator frequency                               | T <sub>A</sub> = 0 to 85 °C                   | -1    | -   | 1     | %    |

| ∆ <sub>Temp</sub> (HSI16)                | drift over temperature                                   | T <sub>A</sub> = -40 to 125 °C                | -2    | -   | 1.5   | %    |

| ∆ <sub>VDD</sub> (HSI16)                 | HSI16 oscillator frequency<br>drift over V <sub>DD</sub> | V <sub>DD</sub> =1.62 V to 3.6 V              | -0.1  | -   | 0.05  | %    |

| t <sub>su</sub> (HSI16) <sup>(2)</sup>   | HSI16 oscillator start-up time                           | -                                             | -     | 0.8 | 1.2   | μs   |

| t <sub>stab</sub> (HSI16) <sup>(2)</sup> | HSI16 oscillator<br>stabilization time                   | -                                             | -     | 3   | 5     | μs   |

| I <sub>DD</sub> (HSI16) <sup>(2)</sup>   | HSI16 oscillator power<br>consumption                    | -                                             | -     | 155 | 190   | μA   |

| Table 47. HS | 116 oscillator | <sup>r</sup> characteristics <sup>(1)</sup> |

|--------------|----------------|---------------------------------------------|

|--------------|----------------|---------------------------------------------|

1. Guaranteed by characterization results.

2. Guaranteed by design.

| Symbol           | Parameter                                                                    | Conditions                                                                                                                                                                                               | Min | Тур | Max                    | Unit |

|------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------|------|

|                  |                                                                              | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                                                                                                        | -   | -   | ±100                   |      |

|                  | FT_xx input leakage current <sup>(3)</sup>                                   | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)(5)} \end{array}$                                                                                                        | -   | -   | 650 <sup>(3)(6)</sup>  |      |

|                  |                                                                              | $\begin{array}{l} {\sf Max}({\sf V}_{{\sf DDXXX}})\text{+1 V} < \\ {\sf VIN} \leq 5.5 \; {\sf V}^{(3)(5)} \end{array}$                                                                                   | -   | -   | 200 <sup>(6)</sup>     |      |

|                  |                                                                              | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                                                                                                        | -   | -   | ±150                   |      |

|                  | FT_lu, FT_u and<br>PC3 IO                                                    | $ \begin{array}{c c} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)} \end{array} & - \\ \hline Max(V_{DDXXX}) + 1 \ V < \\ VIN \leq 5.5 \ V^{(4)(5)(7)} \end{array} & - \\ \end{array} $ | -   | -   | 2500 <sup>(3)(7)</sup> |      |

| l <sub>lkg</sub> |                                                                              | $\begin{array}{l} {\sf Max}({\sf V}_{{\sf DDXXX}}){\rm +1~V} < \\ {\sf VIN} \leq 5.5~{\sf V}^{(4)(5)(7)} \end{array}$                                                                                    | -   | -   | 250 <sup>(7)</sup>     | nA   |

|                  | TT xx input leakage                                                          | $V_{\text{IN}} \leq \text{Max}(V_{\text{DDXXX}})^{(6)}$                                                                                                                                                  | -   | -   | ±150                   |      |

|                  | current                                                                      | Max(V <sub>DDXXX</sub> ) ≤ V <sub>IN</sub> <<br>3.6 V <sup>(6)</sup>                                                                                                                                     | -   | -   | 2000 <sup>(3)</sup>    |      |

|                  | OPAMPx_VINM<br>(x=1,2) dedicated<br>input leakage current<br>(UFBGA132 only) | T <sub>J</sub> = 75 °C                                                                                                                                                                                   | -   | -   | 1                      |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(8)</sup>                           | V <sub>IN</sub> = V <sub>SS</sub>                                                                                                                                                                        | 25  | 40  | 55                     | kΩ   |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent resistor <sup>(8)</sup>                         | V <sub>IN</sub> = V <sub>DDIOx</sub>                                                                                                                                                                     | 25  | 40  | 55                     | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                                          | -                                                                                                                                                                                                        | -   | 5   | -                      | pF   |

| Table 58. I/O static characteristics (c | continued) |

|-----------------------------------------|------------|

|-----------------------------------------|------------|

1. Refer to Figure 21: I/O input characteristics.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. Max(V<sub>DDXXX</sub>) is the maximum value of all the I/O supplies. Refer to Table: Legend/Abbreviations used in the pinout table.

- 5. All TX\_xx IO except FT\_lu, FT\_u and PC3.

- 6. This value represents the pad leakage of the IO itself. The total product pad leakage is provided by this formula:  $I_{Total\_lleak\_max} = 10 \ \mu A + [number of IOs where V_{IN} is applied on the pad] \times I_{lkg}(Max)$ .

- 7. To sustain a voltage higher than MIN( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{DDIO2}$ ) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- 8. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

|             | 145                    | ne or . Abo accuracy - III                                              |              |                          | nava | /    |     |    |

|-------------|------------------------|-------------------------------------------------------------------------|--------------|--------------------------|------|------|-----|----|

| Sym-<br>bol | Parameter              | C                                                                       | Min          | Тур                      | Max  | Unit |     |    |

|             |                        | ADC clock frequency ≤                                                   | Single       | Fast channel (max speed) | -    | -69  | -67 |    |

|             | Total                  | 80 MHz,<br>Sampling rate ≤ 5.33 Msps,                                   | ended        | Slow channel (max speed) | -    | -71  | -67 |    |

| THD         | harmonic<br>distortion | $1.65 \text{ V} \le \text{V}_{\text{DDA}} = \text{V}_{\text{REF+}} \le$ |              | Fast channel (max speed) | -    | -72  | -71 | dB |

|             |                        | 3.6 V,<br>Voltage scaling Range 1                                       | Differential | Slow channel (max speed) | -    | -72  | -71 |    |

Table 67. ADC accuracy - limited test conditions  $3^{(1)(2)(3)}$  (continued)

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

<sup>4.</sup> The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

| Symbol                                  | Parameter                                            | Conditions                                         |                                            |    | Тур        | Max | Unit   |

|-----------------------------------------|------------------------------------------------------|----------------------------------------------------|--------------------------------------------|----|------------|-----|--------|

|                                         |                                                      | PGA Gain = 2                                       |                                            | -  | 80/80      | -   |        |

|                                         | R2/R1 internal                                       | PGA Gain = 4                                       |                                            | -  | 120/<br>40 | -   |        |

| R <sub>network</sub>                    | resistance<br>values in PGA<br>mode <sup>(5)</sup>   | PGA Gain = 8                                       |                                            | -  | 140/<br>20 | -   | kΩ/kΩ  |

|                                         |                                                      | PGA Gain = 16                                      |                                            | -  | 150/<br>10 | -   |        |

| Delta R                                 | Resistance<br>variation (R1 or<br>R2)                | -                                                  |                                            |    | -          | 15  | %      |

| PGA gain error                          | PGA gain error                                       |                                                    | -                                          | -1 | -          | 1   | %      |

|                                         |                                                      | Gain = 2                                           | -                                          | -  | GBW/<br>2  | -   |        |

| PGA BW                                  | PGA bandwidth<br>for different non<br>inverting gain | Gain = 4                                           | -                                          | -  | GBW/<br>4  | -   | MHz    |

| FGA BW                                  |                                                      | Gain = 8                                           | -                                          | -  | GBW/<br>8  | -   | INITIZ |

|                                         |                                                      | Gain = 16                                          | -                                          | -  | GBW/<br>16 | -   |        |

|                                         |                                                      | Normal mode                                        | at 1 kHz, Output<br>loaded with 4 kΩ       | -  | 500        | -   |        |

| en                                      | Voltage noise                                        | Low-power mode                                     | at 1 kHz, Output loaded with 20 k $\Omega$ | -  | 600        | -   | nV/√Hz |

| en                                      | density                                              | Normal mode                                        | at 10 kHz, Output<br>loaded with 4 kΩ      | -  | 180        | -   |        |

|                                         |                                                      | Low-power mode at 10 kHz, Output loaded with 20 kΩ |                                            | -  | 290        | -   |        |

|                                         | OPAMP                                                | Normal mode                                        | no Load, quiescent                         | -  | 120        | 260 |        |

| I <sub>DDA</sub> (OPAMP) <sup>(3)</sup> | consumption<br>from V <sub>DDA</sub>                 | Low-power mode                                     | mode                                       | -  | 45         | 100 | μA     |

Table 73. OPAMP characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design, unless otherwise specified.

2. The temperature range is limited to 0 °C-125 °C when  $V_{\text{DDA}}$  is below 2 V

3. Guaranteed by characterization results.

4. Mostly I/O leakage, when used in analog mode. Refer to IIkg parameter in Table 58: I/O static characteristics.

5. R2 is the internal resistance between OPAMP output and OPAMP inverting input. R1 is the internal resistance between OPAMP inverting input and ground. The PGA gain =1+R2/R1

#### **Quad SPI characteristics**

Unless otherwise specified, the parameters given in *Table 83* and *Table 84* for Quad SPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 15 or 20 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics.

| Symbol              | Parameter                | Conditions                                                                   | Min                    | Тур | Max                    | Unit |

|---------------------|--------------------------|------------------------------------------------------------------------------|------------------------|-----|------------------------|------|

|                     |                          | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 20 pF<br>Voltage Range 1 | -                      | -   | 40                     |      |

| F <sub>СК</sub>     | Quad SPI clock frequency | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 15 pF<br>Voltage Range 1 | -                      | -   | 48                     | MHz  |

| 1/t <sub>(CK)</sub> |                          | 2.7 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 15 pF<br>Voltage Range 1  | -                      | -   | 60                     |      |

|                     |                          | 1.71 < V <sub>DD</sub> < 3.6 V C <sub>LOAD</sub> = 20 pF<br>Voltage Range 2  | -                      | -   | 26                     |      |

| t <sub>w(CKH)</sub> | Quad SPI clock high and  | f <sub>AHBCLK</sub> = 48 MHz, presc=0                                        | t <sub>(CK)</sub> /2-2 | -   | t <sub>(CK)</sub> /2   |      |

| t <sub>w(CKL)</sub> | low time                 | AHBCLK- 40 Min 12, prese-0                                                   | t <sub>(СК)</sub> /2   | -   | t <sub>(CK)</sub> /2+2 |      |

| t                   | Data input setup time    | Voltage Range 1                                                              | 4                      | -   | -                      |      |

| t <sub>s(IN)</sub>  | Data input setup time    | Voltage Range 2                                                              | 3.5                    |     |                        |      |

| +                   | Data input hold time     | Voltage Range 1                                                              |                        | -   | -                      | ns   |

| t <sub>h(IN)</sub>  | Data input hold time     | Voltage Range 2                                                              | 6.5                    | -   | -                      | 115  |

| +                   | Data output valid time   | Voltage Range 1                                                              | -                      | 2.5 | 5                      |      |

| t <sub>v(OUT)</sub> | Data output valid time   | Voltage Range 2                                                              | -                      | 3   | 5                      |      |

| +                   | Data output hold time    | Voltage Range 1                                                              | 1.5                    | -   | -                      |      |

| <sup>t</sup> h(OUT) | Data output hold time    | Voltage Range 2                                                              | 2                      | -   | -                      |      |

1. Guaranteed by characterization results.

| Symbol                      | Parameter                                  | Min                    | Мах | Unit |

|-----------------------------|--------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                             | 2T <sub>HCLK</sub> -1  | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                      | 2   |      |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub> +0.5 | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                | -                      | 2.5 |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high               | 1                      | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)       | -                      | 3.5 |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>HCLK</sub>      | -   |      |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                 | -                      | 2   |      |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high               | T <sub>HCLK</sub> +1   | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid          | -                      | 4   |      |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid        | 0                      | -   |      |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low | -                      | 5.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                 | -                      | 2.5 |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high               | T <sub>HCLK</sub> +1   | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high        | 0                      | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high         | 4                      | -   |      |

1. CL = 30 pF.

2. Guaranteed by characterization results.

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |

|--------|--------|-------------|--------|-----------------------|--------|--------|--|

|        | Min    | Тур         | Мах    | Min                   | Тур    | Max    |  |

| D3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| Е      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |  |

| k      | 0.0°   | 3.5°        | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |

| ccc    | -      | -           | 0.080  | -                     | -      | 0.0031 |  |

## Table 105. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

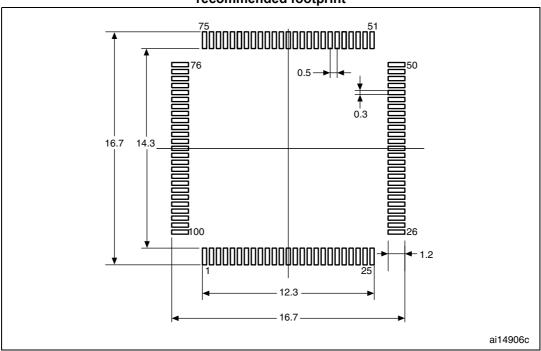

# Figure 55. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

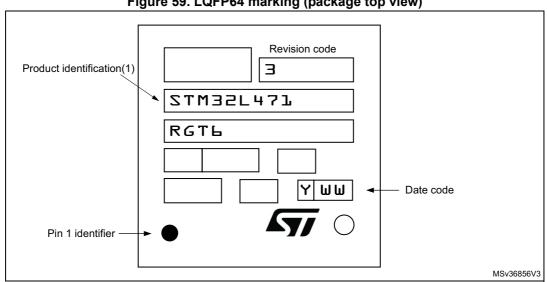

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 59. LQFP64 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering complex to run qualification activity. 1. samples to run qualification activity.

### 7.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 22: General operating conditions*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I/O}}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma \; ((\mathsf{V}_{\mathsf{DDIOx}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                 | Value | Unit |

|-----------------|---------------------------------------------------------------------------|-------|------|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 45    | °C/W |

|                 | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14mm                | 42    |      |

|                 | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm               | 32    |      |

|                 | Thermal resistance junction-ambient<br>UFBGA132 - 7 × 7 mm                | 55    |      |

Table 107. Package thermal characteristics

### 7.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

### 7.5.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Part numbering*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32L471xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.