Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 25MHz                                                                         |

| Connectivity               | SCI, SmartCard                                                                |

| Peripherals                | DMA, PWM, WDT                                                                 |

| Number of I/O              | 70                                                                            |

| Program Memory Size        | 384KB (384K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 16K × 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-BFQFP                                                                     |

| Supplier Device Package    | 100-QFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3068fbl25v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|           |                                    | Pin No.                      | _                |                                                                                                                                  |

|-----------|------------------------------------|------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Туре      | Symbol                             | FP-100B<br>TFP-100B          | I/O              | Name and Function                                                                                                                |

| I/O ports | P67 to P60                         | 61,<br>72 to 69,<br>60 to 58 | Input/<br>output | <b>Port 6:</b> Eight input/output pins. The direction of each pin can be selected in the port 6 data direction register (P6DDR). |

|           | P7 <sub>7</sub> to P7 <sub>0</sub> | 85 to 78                     | Input            | Port 7: Eight input pins                                                                                                         |

|           | P8 <sub>4</sub> to P8 <sub>0</sub> | 91 to 87                     | Input/<br>output | <b>Port 8:</b> Five input/output pins. The direction of each pin can be selected in the port 8 data direction register (P8DDR).  |

|           | P9 <sub>5</sub> to P9 <sub>0</sub> | 17 to 12                     | Input/<br>output | <b>Port 9:</b> Six input/output pins. The direction of each pin can be selected in the port 9 data direction register (P9DDR).   |

|           | PA <sub>7</sub> to PA <sub>0</sub> | 100 to 93                    | Input/<br>output | <b>Port A:</b> Eight input/output pins. The direction of each pin can be selected in the port A data direction register (PADDR). |

|           | PB <sub>7</sub> to PB <sub>0</sub> | 9 to 2                       | Input/<br>output | <b>Port B:</b> Eight input/output pins. The direction of each pin can be selected in the port B data direction register (PBDDR). |

### Section 5 Interrupt Controller

|                                               |                            | Vector   | Vector A         |                                      |       |          |

|-----------------------------------------------|----------------------------|----------|------------------|--------------------------------------|-------|----------|

| Interrupt Source                              | Origin                     | Number   | Advanced Mode    | Normal Mode                          | IPR   | Priority |

| IMIA2<br>(compare match/<br>input capture A2) | 16-bit timer<br>channel 2  | 32       | H'0080 to H'0083 | H'0040 to H'0041                     | IPRA0 | High     |

| IMIB2<br>(compare match/<br>input capture B2) |                            | 33       | H'0084 to H'0087 | H'0042 to H'0043                     |       |          |

| OVI2 (overflow 2)                             |                            | 34       | H'0088 to H'008B | H'0044 to H'0045                     | _     |          |

| Reserved                                      | _                          | 35       | H'008C to H'008F | H'0046 to H'0047                     |       |          |

| CMIA0<br>(compare match<br>A0)                | 8-bit timer<br>channel 0/1 | 36       | H'0090 to H'0093 | H'0048 to H'0049                     | IPRB7 |          |

| CMIB0<br>(compare match<br>B0)                |                            | 37       | H'0094 to H'0097 | H'004A to H'004B                     |       |          |

| CMIA1/CMIB1<br>(compare match<br>A1/B1)       |                            | 38       | H'0098 to H'009B | H'004C to H'004D                     |       |          |

| TOVI0/TOVI1<br>(overflow 0/1)                 |                            | 39       | H'009C to H'009F | H'004E to H'004F                     |       | _        |

| CMIA2<br>(compare match<br>A2)                | 8-bit timer<br>channel 2/3 | 40       | H'00A0 to H'00A3 | H'0050 to H'0051                     | IPRB6 |          |

| CMIB2<br>(compare match<br>B2)                |                            | 41       | H'00A4 to H'00A7 | H'0052 to H'0053                     |       |          |

| CMIA3/CMIB3<br>(compare match<br>A3/B3)       |                            | 42       | H'00A8 to H'00AB | H'0054 to H'0055                     |       |          |

| TOVI2/TOVI3<br>(overflow 2/3)                 |                            | 43       | H'00AC to H'00AF | H'0056 to H'0057                     |       | _        |

| DEND0A                                        | DMAC                       | 44       |                  |                                      | IPRB5 |          |

| DEND0B<br>DEND1A                              |                            | 45<br>46 |                  | H'005A to H'005B<br>H'005C to H'005D |       |          |

| DEND1B                                        |                            | 40<br>47 | H'00BC to H'00BF |                                      |       |          |

| Reserved                                      | _                          | 48       | H'00C0 to H'00C3 | H'0060 to H'0061                     | _     | -        |

|                                               |                            | 49       | H'00C4 to H'00C7 |                                      |       |          |

|                                               |                            | 50       | H'00C8 to H'00CB |                                      |       | Y        |

|                                               |                            | 51       | H'00CC to H'00CF | H'0066 to H'0067                     |       | Low      |

Note: \* Lower 16 bits of the address.

Rev. 3.00 Sep 14, 2005 page 102 of 910 REJ09B0258-0300

### 6.2.2 Access State Control Register (ASTCR)

ASTCR is an 8-bit readable/writable register that selects whether each area is accessed in two states or three states.

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------|------|------|------|------|------|------|------|------|

|               | AST7 | AST6 | AST5 | AST4 | AST3 | AST2 | AST1 | AST0 |

| Initial value | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Read/Write    | R/W  |

|               |      |      |      |      |      |      |      |      |

Bits selecting number of states for access to each area

ASTCR is initialized to H'FF by a reset and in hardware standby mode. It is not initialized in software standby mode.

Bits 7 to 0—Area 7 to 0 Access State Control (AST7 to AST0): These bits select whether the corresponding area is accessed in two or three states.

| Bits 7 to 0<br>AST7 to AST0 | Description                               |                 |

|-----------------------------|-------------------------------------------|-----------------|

| 0                           | Areas 7 to 0 are accessed in two states   |                 |

| 1                           | Areas 7 to 0 are accessed in three states | (Initial value) |

ASTCR specifies the number of states in which external areas are accessed. On-chip memory and registers are accessed in a fixed number of states that does not depend on ASTCR settings. These settings are therefore meaningless in the single-chip modes (modes 6 and 7).

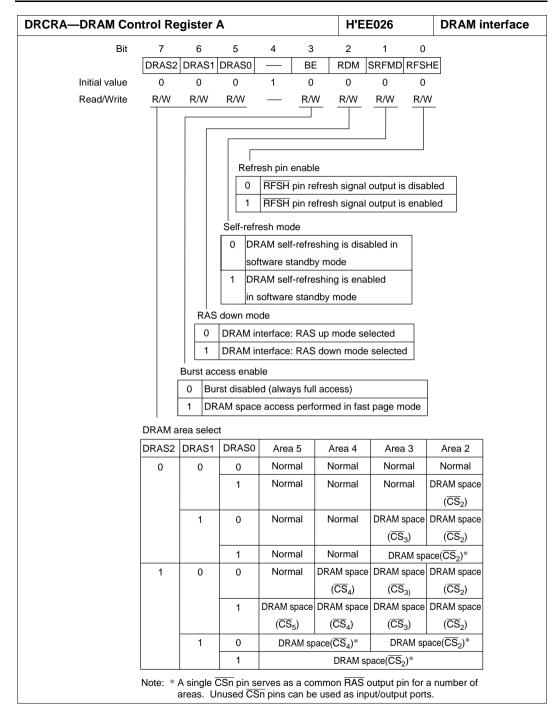

When the corresponding area is designated as DRAM space by bits DRAS2 to DRAS0 in DRAM control register A (DRCRA), the number of access states does not depend on the AST bit setting. When an AST bit is cleared to 0, programmable wait insertion is not performed.

| ABWCR | ASTCR | WCRH/\ | CRH/WCRL Bus Specifications (Basic Bus Interface) |           |               | Bus Specifications (Basic Bus Interface) |  |  |  |

|-------|-------|--------|---------------------------------------------------|-----------|---------------|------------------------------------------|--|--|--|

| ABWn  | ASTn  | Wn1    | Wn0                                               | Bus Width | Access States | Program Wait States                      |  |  |  |

| 0     | 0     | _      | _                                                 | 16        | 2             | 0                                        |  |  |  |

|       | 1     | 0      | 0                                                 |           | 3             | 0                                        |  |  |  |

|       |       |        | 1                                                 |           |               | 1                                        |  |  |  |

|       |       | 1      | 0                                                 |           |               | 2                                        |  |  |  |

|       |       |        | 1                                                 |           |               | 3                                        |  |  |  |

| 1     | 0     | _      | _                                                 | 8         | 2             | 0                                        |  |  |  |

|       | 1     | 0      | 0                                                 |           | 3             | 0                                        |  |  |  |

|       |       |        | 1                                                 |           |               | 1                                        |  |  |  |

|       |       | 1      | 0                                                 |           |               | 2                                        |  |  |  |

|       |       |        | 1                                                 |           |               | 3                                        |  |  |  |

| Table 6.3 | Bus Specifications for Each Area (Basic Bus Interface) |  |

|-----------|--------------------------------------------------------|--|

|-----------|--------------------------------------------------------|--|

Note: n = 7 to 0

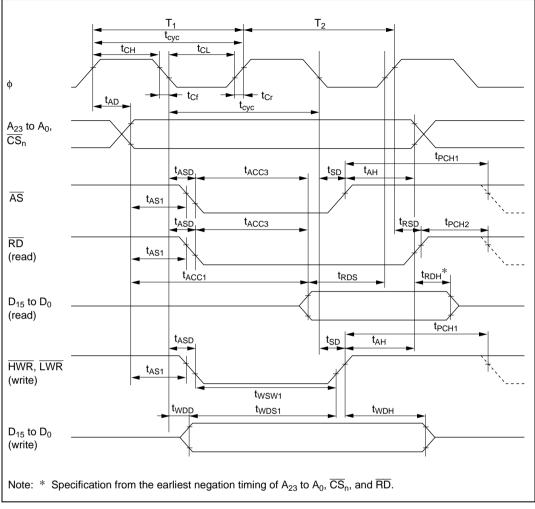

### 6.3.3 Memory Interfaces

The H8/3068F memory interfaces comprise a basic bus interface that allows direct connection of ROM, SRAM, and so on; a DRAM interface that allows direct connection of DRAM; and a burst ROM interface that allows direct connection of burst ROM. The interface can be selected independently for each area.

An area for which the basic bus interface is designated functions as normal space, an area for which the DRAM interface is designated functions as DRAM space, and area 0 for which the burst ROM interface is designated functions as burst ROM space.

### 6.3.5 Address Output Method

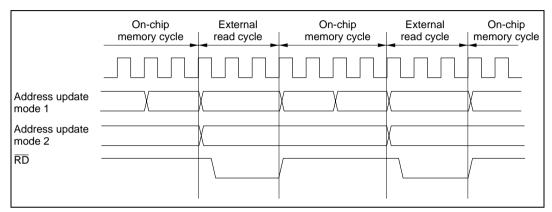

The H8/3068F provides a choice of two address update methods: either the same method as in the previous H8/300H Series (address update mode 1), or a method in which address update is restricted to external space accesses or self-refresh cycles (address update mode 2).

**Address Update Mode 1:** Address update mode 1 is compatible with the previous H8/300H Series. Addresses are always updated between bus cycles.

Address Update Mode 2: In address update mode 2, address updating is performed only in external space accesses or self-refresh cycles. In this mode, the address can be retained between an external space read cycle and an instruction fetch cycle (on-chip memory) by placing the program in on-chip memory. Address update mode 2 is therefore useful when connecting a device that requires address hold time with respect to the rise of the  $\overline{RD}$  strobe.

Switching between address update modes 1 and 2 is performed by means of the ADRCTL bit in ADRCR. The initial value of ADRCR is the address update mode 1 setting, providing compatibility with the previous H8/300H Series.

## 8.2 Port 1

### 8.2.1 Overview

Port 1 is an 8-bit input/output port also used for address output, with the pin configuration shown in figure 8.1. The pin functions differ between the expanded modes with on-chip ROM disabled, expanded modes with on-chip ROM enabled, and single-chip mode. In modes 1 to 4 (expanded modes with on-chip ROM disabled), they are address bus output pins ( $A_7$  to  $A_0$ ).

In modes 5 (expanded modes with on-chip ROM enabled), settings in the port 1 data direction register (P1DDR) can designate pins for address bus output ( $A_7$  to  $A_0$ ) or generic input. In mode 6 and 7 (single-chip mode), port 1 is a generic input/output port.

When DRAM is connected to area 2, 3, 4, 5,  $A_7$  to  $A_0$  output row and column addresses in read and write cycles. For details see section 6.5, DRAM Interface.

Pins in port 1 can drive one TTL load and a 90-pF capacitive load. They can also drive an LED or a darlington transistor pair.

|         | Port 1 pins                       | Modes 1 to 4                                       | Modes 5                                                                                            | Mode 6 and 7                                                     |

|---------|-----------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|         |                                   | A <sub>7</sub> (output)<br>A <sub>6</sub> (output) | P1 <sub>7</sub> (input)/A <sub>7</sub> (output)<br>P1 <sub>6</sub> (input)/A <sub>6</sub> (output) | P1 <sub>7</sub> (input/output)<br>P1 <sub>6</sub> (input/output) |

| Derit 4 | ← P1 <sub>5</sub> /A <sub>5</sub> | A <sub>5</sub> (output)                            | P1 <sub>5</sub> (input)/A <sub>5</sub> (output)                                                    | P1 <sub>5</sub> (input/output)                                   |

|         | ► P1 <sub>4</sub> /A <sub>4</sub> | A <sub>4</sub> (output)                            | P1 <sub>4</sub> (input)/A <sub>4</sub> (output)                                                    | P1 <sub>4</sub> (input/output)                                   |

| Port 1  | ► P1 <sub>3</sub> /A <sub>3</sub> | A <sub>3</sub> (output)                            | P1 <sub>3</sub> (input)/A <sub>3</sub> (output)                                                    | P1 <sub>3</sub> (input/output)                                   |

|         | ► P1 <sub>2</sub> /A <sub>2</sub> | A <sub>2</sub> (output)                            | P1 <sub>2</sub> (input)/A <sub>2</sub> (output)                                                    | P1 <sub>2</sub> (input/output)                                   |

|         | ► P1 <sub>1</sub> /A <sub>1</sub> | A <sub>1</sub> (output)                            | P1 <sub>1</sub> (input)/A <sub>1</sub> (output)                                                    | P1 <sub>1</sub> (input/output)                                   |

|         | ← P1 <sub>0</sub> /A <sub>0</sub> | A <sub>0</sub> (output)                            | P1 <sub>0</sub> (input)/A <sub>0</sub> (output)                                                    | P1 <sub>0</sub> (input/output)                                   |

### 9.5.3 Interrupt Sources

Each 16-bit timer channel can generate a compare match/input capture A interrupt, a compare match/input capture B interrupt, and an overflow interrupt. In total there are nine interrupt sources of three kinds, all independently vectored. An interrupt is requested when the interrupt request flag are set to 1.

The priority order of the channels can be modified in interrupt priority registers A (IPRA). For details see section 5, Interrupt Controller.

Table 9.6 lists the interrupt sources.

| Table 9.6 | <b>16-bit timer Interrupt Sources</b> |

|-----------|---------------------------------------|

|-----------|---------------------------------------|

| Channel | Interrupt<br>Source    | Description                                                                    | Priority*       |

|---------|------------------------|--------------------------------------------------------------------------------|-----------------|

| 0       | IMIA0<br>IMIB0<br>OVI0 | Compare match/input capture A0<br>Compare match/input capture B0<br>Overflow 0 | High            |

| 1       | IMIA1<br>IMIB1<br>OVI1 | Compare match/input capture A1<br>Compare match/input capture B1<br>Overflow 1 |                 |

| 2       | IMIA2<br>IMIB2<br>OVI2 | Compare match/input capture A2<br>Compare match/input capture B2<br>Overflow 2 | <b>↓</b><br>Low |

Note: \* The priority immediately after a reset is indicated. Inter-channel priorities can be changed by settings in IPRA.

**Bit 7—Watchdog Timer Reset (WRST):** During watchdog timer operation, this bit indicates that TCNT has overflowed and generated a reset signal. This reset signal resets the entire H8/3068F chip internally.

| Bit 7<br>WRST | Description                                                                                       |                 |

|---------------|---------------------------------------------------------------------------------------------------|-----------------|

| 0             | [Clearing condition]<br>Reset signal at RES pin.<br>Read WRST when WRST =1, then write 0 in WRST. | (Initial value) |

| 1             | [Setting condition]<br>Set when TCNT overflow generates a reset signal during watchdog timer o    | peration        |

#### Bit 6—Reserved

Bits 5 to 0—Reserved: These bits cannot be modified and are always read as 1.

#### 12.2.4 Notes on Register Access

The watchdog timer's TCNT, TCSR, and RSTCSR registers differ from other registers in being more difficult to write. The procedures for writing and reading these registers are given below.

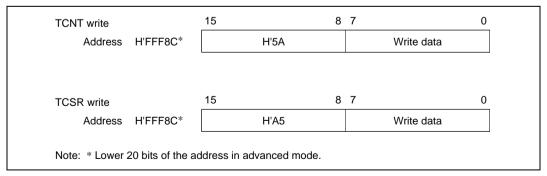

**Writing to TCNT and TCSR:** These registers must be written by a word transfer instruction. They cannot be written by byte instructions. Figure 12.2 shows the format of data written to TCNT and TCSR. TCNT and TCSR both have the same write address. The write data must be contained in the lower byte of the written word. The upper byte must contain H'5A (password for TCNT) or H'A5 (password for TCSR). This transfers the write data from the lower byte to TCNT or TCSR.

### Figure 12.2 Format of Data Written to TCNT and TCSR

### Synchronous mode

Serial data communication is synchronized with a clock signal. The SCI can communicate with other chips having a synchronous communication function.

There is a single serial data communication format.

- Data length: 8 bits

- Receive error detection: overrun errors

- Full-duplex communication

The transmitting and receiving sections are independent, so the SCI can transmit and receive simultaneously. The transmitting and receiving sections are both double-buffered, so serial data can be transmitted and received continuously.

- The following settings can be made for the serial data to be transferred:

- LSB-first or MSB-first transfer

- Inversion of data logic level

- Built-in baud rate generator with selectable bit rates

- Selectable transmit/receive clock sources: internal clock from baud rate generator, or external clock from the SCK pin

- Four types of interrupts

Transmit-data-empty, transmit-end, receive-data-full, and receive-error interrupts are requested independently. The transmit-data-empty and receive-data-full interrupts from SCI0 can activate the DMA controller (DMAC) to transfer data.

Features of the smart card interface are listed below.

- Asynchronous communication

- Data length: 8 bits

- Parity bits generated and checked

- Error signal output in receive mode (parity error)

- Error signal detect and automatic data retransmit in transmit mode

- Supports both direct convention and inverse convention

- Built-in baud rate generator with selectable bit rates

- Three types of interrupts

Transmit-data-empty, receive-data-full, and transmit/receive-error interrupts are requested independently. The transmit-data-empty and receive-data-full interrupts can activate the DMA controller (DMAC) to transfer data.

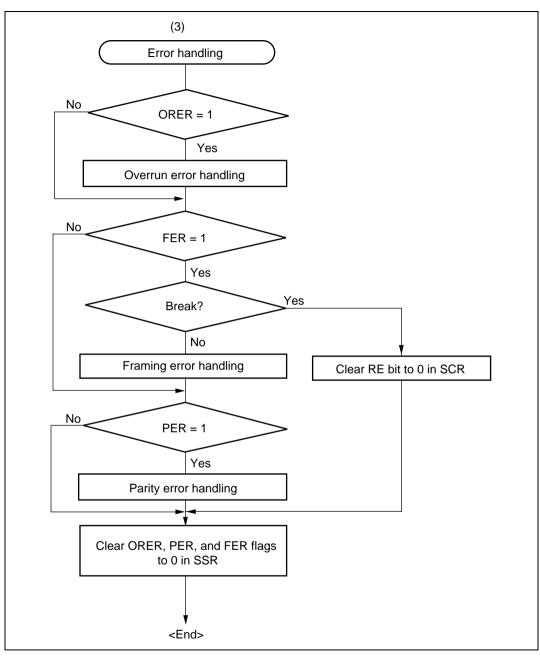

Figure 13.7 Sample Flowchart for Receiving Serial Data (2)

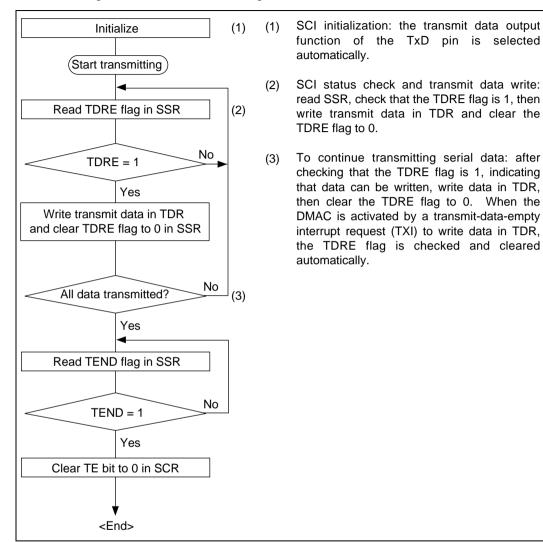

• Transmitting Serial Data (Synchronous Mode): Figure 13.16 shows a sample flowchart for transmitting serial data and indicates the procedure to follow.

Figure 13.16 Sample Flowchart for Serial Transmitting

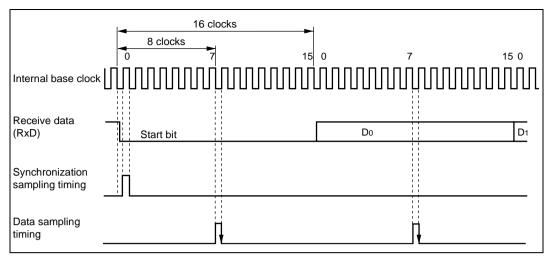

Figure 13.21 Receive Data Sampling Timing in Asynchronous Mode

The receive margin in asynchronous mode can therefore be expressed as shown in equation (1).

$$M = \left| (0.5 - \frac{1}{2N}) - (L - 0.5) F - \frac{|D - 0.5|}{N} (1 + F) \right| \times 100\%$$

.....(1)

- M: Receive margin (%)

- N: Ratio of clock frequency to bit rate (N = 16)

- D: Clock duty cycle (L = 0 to 1.0)

- L: Frame length (L = 9 to 12)

- F: Absolute deviation of clock frequency

From equation (1), if F = 0 and D = 0.5, the receive margin is 46.875%, as given by equation (2).

This is a theoretical value. A reasonable margin to allow in system designs is 20% to 30%.

## 14.2 Register Descriptions

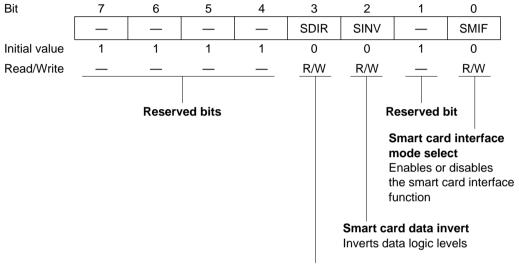

This section describes the new or modified registers and bit functions in the smart card interface.

### 14.2.1 Smart Card Mode Register (SCMR)

SCMR is an 8-bit readable/writable register that selects smart card interface functions.

Smart card data transfer direction Selects the serial/parallel conversion format

SCMR is initialized to H'F2 by a reset and in standby mode.

Bits 7 to 4—Reserved: Read-only bits, always read as 1.

**Bit 3—Smart Card Data Transfer Direction (SDIR):** Selects the serial/parallel conversion format.\*<sup>1</sup>

| Bit 3<br>SDIR | Description                             |                 |

|---------------|-----------------------------------------|-----------------|

| 0             | TDR contents are transmitted LSB-first  | (Initial value) |

|               | Receive data is stored LSB-first in RDR |                 |

| 1             | TDR contents are transmitted MSB-first  |                 |

|               | Receive data is stored MSB-first in RDR |                 |

Figure 21.8 Basic Bus Cycle: Two-State Access

| ISRA—Timer Int          | errup                                                                                                                                                                                                                              | t Sta                          | tus Register A                                                                                                                                           | H'FFF64                                                                   | 16-bit timer (all channels) |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------|--|

|                         | Bit:<br>Initial va<br>Read/W                                                                                                                                                                                                       |                                | — IMIEA2 IMIEA1 IMI<br>1 0 0                                                                                                                             | 4 3 2 1<br>EA0 — IMFA2 IMF<br>0 1 0 0<br>W — <u>R/(W)*</u> <u>R/(</u>     | A1 IMFA0<br>0               |  |

|                         |                                                                                                                                                                                                                                    |                                | DMAC activated by II<br>[Setting conditions]<br>TCNT0=GRA0 when                                                                                          | /IFA0=1, then write 0 in IM<br>VIA0 interrupt.<br>GRA0 functions as an ou | Itput compare register.     |  |

|                         | 1       TCNT0 value is transferred to GRA0 by an input capture signal when GRA0 functions as an input capture register.         Input capture/compare match flag A1                                                                |                                |                                                                                                                                                          |                                                                           |                             |  |

|                         | [Clearing conditions]       (Initial value)         0       Read IMFA1 when IMFA1=1, then write 0 in IMFA1         DMAC activated by IMIA1 interrupt.                                                                              |                                |                                                                                                                                                          |                                                                           |                             |  |

|                         |                                                                                                                                                                                                                                    | 1                              | [Setting conditions]<br>TCNT1=GRA1 when GRA<br>TCNT1 value is transferre<br>functions as an input capt                                                   | d to GRA1 by an input ca                                                  |                             |  |

|                         | Input capture/compare match flag A2         [Clearing conditions]       (Initial value)         0       Read IMFA2 when IMFA2=1, then write 0 in IMFA2         DMAC activated by IMIA2 interrupt.                                  |                                |                                                                                                                                                          |                                                                           |                             |  |

|                         | 1       [Setting conditions]         TCNT2=GRA2 when GRA2 functions as an output compare register.         1       TCNT2 value is transferred to GRA2 by an input capture signal when GRA2 functions as an input capture register. |                                |                                                                                                                                                          |                                                                           |                             |  |

|                         | 0 IMIA<br>1 IMIA<br>capture/co                                                                                                                                                                                                     | ∖0 inter<br>∖0 inter<br>ompare | npare match interrupt enable<br>rrupt requested by IMFA0 fla<br>rrupt requested by IMFA0 is<br>e match interrupt enable A1<br>requested by IMFA1 flag is | ag is disabled<br>enabled                                                 | (Initial value)             |  |

| Input captur<br>0 IMIA: | IMIA1 int<br>re/compar<br>2 interrup                                                                                                                                                                                               | terrupt<br>re mat<br>ot requ   | requested by IMFA1 is enal<br>ch interrupt enable A2<br>ested by IMFA2 flag is disab<br>ested by IMFA2 is enabled                                        | bled                                                                      |                             |  |

|                         |                                                                                                                                                                                                                                    |                                | ested by INIFA2 is enabled                                                                                                                               |                                                                           | ]                           |  |

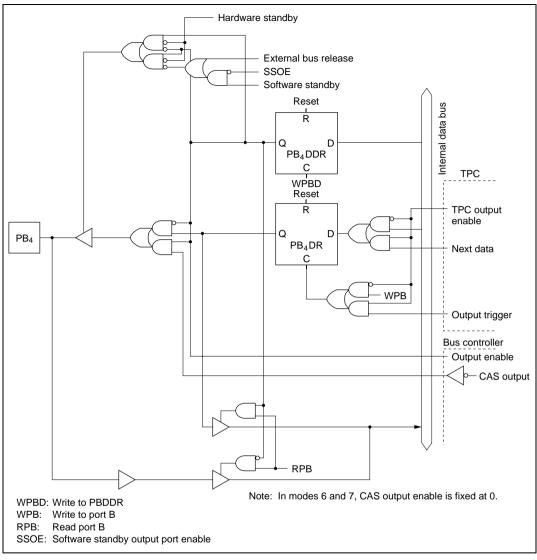

Figure C.11 (e) Port B Block Diagram (Pin PB<sub>4</sub>)

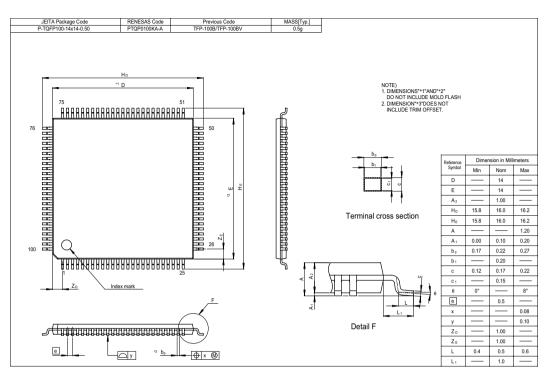

Figure G.2 Package Dimensions (TFP-100B)