Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 17x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f311-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| 15.UART0                                                                  |

|---------------------------------------------------------------------------|

| Table 15.1. Timer Settings for Standard Baud Rates                        |

| Using the Internal Oscillator                                             |

| Table 15.2. Timer Settings for Standard Baud Rates                        |

| Using an External 25 MHz Oscillator 170                                   |

| Table 15.3. Timer Settings for Standard Baud Rates                        |

| Using an External 22.1184 MHz Oscillator                                  |

| Table 15.4. Timer Settings for Standard Baud Rates                        |

| Using an External 18.432 MHz Oscillator                                   |

| Table 15.5. Timer Settings for Standard Baud Rates                        |

| Using an External 11.0592 MHz Oscillator 172                              |

| Table 15.6. Timer Settings for Standard Baud Rates                        |

| Using an External 3.6864 MHz Oscillator 172                               |

| 16. Enhanced Serial Peripheral Interface (SPI0)                           |

| Table 16.1. SPI Slave Timing Parameters    185                            |

| 17. Timers                                                                |

| 18. Programmable Counter Array                                            |

| Table 18.1. PCA Timebase Input Options    204                             |

| Table 18.2. PCA0CPM Register Settings for PCA Capture/Compare Modules 205 |

| Table 18.3. Watchdog Timer Timeout Intervals    214                       |

| 19. Revision Specific Behavior                                            |

| 20. C2 Interface                                                          |

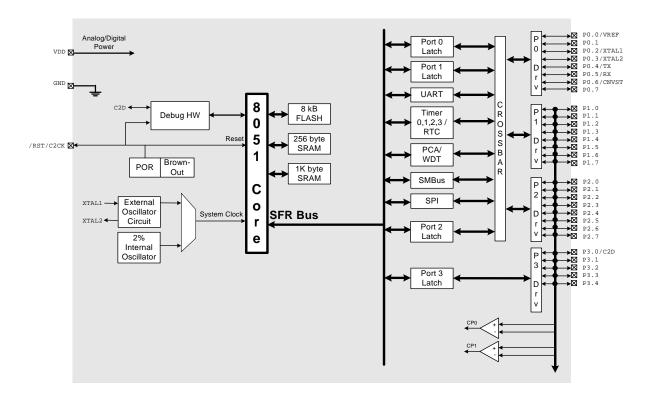

Figure 1.5. C8051F314 Block Diagram

Inputs are measured from '0' to VREF \* 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to '0'.

| Input Voltage    | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------|----------------------------------------------|---------------------------------------------|

| VREF x 1023/1024 | 0x03FF                                       | 0xFFC0                                      |

| VREF x 512/1024  | 0x0200                                       | 0x8000                                      |

| VREF x 256/1024  | 0x0100                                       | 0x4000                                      |

| 0                | 0x0000                                       | 0x0000                                      |

When in Differential Mode, conversion codes are represented as 10-bit signed 2's complement numbers. Inputs are measured from -VREF to VREF \* 511/512. Example codes are shown below for both right-justified and left-justified data. For right-justified data, the unused MSBs of ADC0H are a sign-extension of the data word. For left-justified data, the unused LSBs in the ADC0L register are set to '0'.

| Input Voltage   | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|-----------------|----------------------------------------------|---------------------------------------------|

| VREF x 511/512  | 0x01FF                                       | 0x7FC0                                      |

| VREF x 256/512  | 0x0100                                       | 0x4000                                      |

| 0               | 0x0000                                       | 0x0000                                      |

| –VREF x 256/512 | 0xFF00                                       | 0xC000                                      |

| –VREF           | 0xFE00                                       | 0x8000                                      |

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to '0' the corresponding bit in register PnMDIN (for n = 0,1,2,3). To force the Crossbar to skip a Port pin, set to '1' the corresponding bit in register PnSKIP (for n = 0,1,2). See **Section "13. Port Input/Output" on page 129** for more Port I/O configuration details.

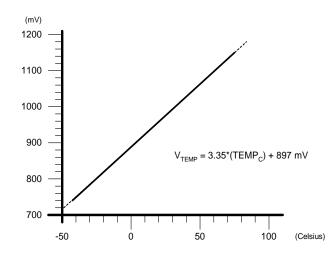

### 5.2. Temperature Sensor

The typical temperature sensor transfer function is shown in Figure 5.2. The output voltage ( $V_{TEMP}$ ) is the positive ADC input when the temperature sensor is selected by bits AMX0P4-0 in register AMX0P.

Figure 5.2. Typical Temperature Sensor Transfer Function

| SFR Definition 5.3. ADC0CF: ADC0 Configuration | า |

|------------------------------------------------|---|

|------------------------------------------------|---|

| R/W               | R/W<br>4 AD0SC3                                                                 | R/W<br>AD0SC2                                  | R/W<br>AD0SC1                           | R/W<br>AD0SC0                | R/W<br>AD0LJST | R/W<br>- | R/W  | Reset Value          |

|-------------------|---------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|------------------------------|----------------|----------|------|----------------------|

| Bit7              | Bit6                                                                            | Bit5                                           | Bit4                                    | Bit3                         | Bit2           | Bit1     | Bit0 | SFR Address:<br>0xBC |

| Bits7–3:          | AD0SC4–0:<br>SAR Conver<br><i>AD0SC</i> refer<br>ments are gi<br><i>AD0SC</i> = | rsion clock i<br>rs to the 5-b<br>ven in Table | s derived fr<br>bit value hel<br>e 5.1. | om system                    | clock by the   | •        |      |                      |

| Bit2:<br>Bits1–0: | AD0LJST: A<br>0: Data in A<br>1: Data in A<br>UNUSED. R                         | DC0H:ADC0<br>DC0H:ADC0                         | OL registers<br>OL registers            | are right-ju<br>are left-jus |                |          |      |                      |

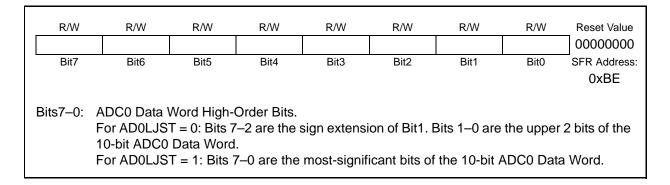

#### SFR Definition 5.4. ADC0H: ADC0 Data Word MSB

### SFR Definition 5.5. ADC0L: ADC0 Data Word LSB

| R/W  | R/W                                                    | R/W         | R/W         | R/W  | R/W  | R/W  | R/W  | Reset Value   |

|------|--------------------------------------------------------|-------------|-------------|------|------|------|------|---------------|

| Bit7 | Bit6                                                   | Bit5        | Bit4        | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:  |

|      |                                                        |             |             |      |      |      |      | 0xBD          |

|      | ADC0 Data V<br>For AD0LJST<br>For AD0LJST<br>read '0'. | Γ = 0: Bits | 7–0 are the |      |      |      |      | ) will always |

| R/W               | R/W                                            | R/W                        | R/W                          | R/W           | R/W          | R/W            | R/W     | Reset Value  |

|-------------------|------------------------------------------------|----------------------------|------------------------------|---------------|--------------|----------------|---------|--------------|

|                   |                                                |                            |                              | REFSL         | TEMPE        | BIASE          |         | 00000000     |

| Bit7              | Bit6                                           | Bit5                       | Bit4                         | Bit3          | Bit2         | Bit1           | Bit0    | SFR Address: |

|                   |                                                |                            |                              |               |              |                |         | 0xD1         |

| Bits7–4:<br>Bit3: | UNUSED. R<br>REFSL: Volt<br>This bit selec     | age Refere<br>cts the sour | nce Select.<br>ce for the ir | nternal volta | ge referenc  | æ.             |         |              |

|                   | 0: VREF inp<br>1: V <sub>DD</sub> used         | •                          | •                            | reference.    |              |                |         |              |

| Bit2:             | TEMPE: Ten<br>0: Internal Te<br>1: Internal Te | emperature                 | Sensor off.                  |               |              |                |         |              |

| Bit1:             | BIASE: Inter<br>0: Internal B<br>1: Internal B | ias Generat                | or off.                      | rator Enable  | Bit. (Must I | be '1' if usin | g ADC). |              |

| Bit0:             | UNUSED. R                                      | ead = 0b. V                | Vrite = don'                 | t care.       |              |                |         |              |

## Table 6.1. External Voltage Reference Circuit Electrical Characteristics

$V_{DD}$  = 3.0 V; -40 to +85 °C unless otherwise specified

| Parameter           | Conditions                              | Min | Тур | Max             | Units |

|---------------------|-----------------------------------------|-----|-----|-----------------|-------|

| Input Voltage Range |                                         | 0   |     | V <sub>DD</sub> | V     |

| Input Current       | Sample Rate = 200 ksps;<br>VREF = 3.0 V |     | 12  |                 | μA    |

| R/W      | R/W                              | R/W                                                           | R/W                                                               | R/W                                               | R/W                          | R/W      | R/W    | Reset Value |

|----------|----------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------|------------------------------|----------|--------|-------------|

| -        | -                                | <b>CP0RIE</b>                                                 | CP0FIE                                                            | -                                                 | -                            | CP0MD1   | CP0MD0 | 0000001     |

| Bit7     | Bit6                             | Bit5                                                          | Bit4                                                              | Bit3                                              | Bit2                         | Bit1     | Bit0   | SFR Addres  |

|          |                                  |                                                               |                                                                   |                                                   |                              |          |        | 0x9D        |

| 3its7–6: | UNUSED. F                        | Read = $00b$ .                                                | Write = dor                                                       | i't care.                                         |                              |          |        |             |

| Bit5:    | CP0RIE: Co                       | omparator R                                                   | ising-Edge                                                        | Interrupt En                                      | able.                        |          |        |             |

|          | 0: Compara                       |                                                               |                                                                   |                                                   |                              |          |        |             |

|          | 1: Compara                       | •                                                             | • •                                                               |                                                   |                              |          |        |             |

| Bit4:    | CP0FIE: Co                       | •                                                             | • •                                                               |                                                   | able.                        |          |        |             |

|          | 0: Compara                       | •                                                             |                                                                   |                                                   |                              |          |        |             |

|          |                                  |                                                               |                                                                   |                                                   |                              |          |        |             |

|          | 1: Compara                       | •                                                             | •                                                                 |                                                   |                              |          |        |             |

| Bits1–0: | 1: Compara<br>CP0MD1–C           | tor falling-ed                                                | dge interrup                                                      | t enabled.                                        | t                            |          |        |             |

| Bits1–0: | CP0MD1-C                         | tor falling-eo<br>P0MD0: Co                                   | dge interrup<br>mparator0 l                                       | t enabled.<br>Mode Selec                          |                              |          |        |             |

| Bits1–0: |                                  | tor falling-eo<br>P0MD0: Co                                   | dge interrup<br>mparator0 l                                       | t enabled.<br>Mode Selec                          |                              |          |        |             |

| Bits1–0: | CP0MD1-C                         | tor falling-eo<br>P0MD0: Co                                   | dge interrup<br>mparator0 l                                       | t enabled.<br>Mode Selec<br>e for Compa           |                              | ne (TYP) | ٦      |             |

| Bits1–0: | CP0MD1–C<br>These bits s         | tor falling-ed<br>POMD0: Co<br>select the re                  | dge interrup<br>omparator0 l<br>sponse time                       | t enabled.<br>Mode Selec<br>ofor Compa<br>CP0 Res | rator0.                      | . ,      | -      |             |

| Bits1–0: | CP0MD1–C<br>These bits s         | tor falling-ed<br>POMD0: Co<br>select the re<br><b>CP0MD1</b> | dge interrup<br>omparator0 l<br>sponse time<br><b>CP0MD0</b>      | t enabled.<br>Mode Selec<br>ofor Compa<br>CP0 Res | rator0.<br><b>sponse Tir</b> | . ,      | ]      |             |

| Bits1–0: | CP0MD1–C<br>These bits s<br>Mode | tor falling-ed<br>POMD0: Co<br>select the re<br>CPOMD1<br>0   | dge interrup<br>omparator0 l<br>sponse time<br><b>CP0MD0</b><br>0 | t enabled.<br>Mode Selec<br>ofor Compa<br>CP0 Res | rator0.<br><b>sponse Tir</b> | . ,      |        |             |

| R/W                                    | R/W                                                                                                                                                                                                                                                  | R/W    | R/W    | R/W    | R/W        | R/W        | R/W    | Reset Value  |  |  |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|------------|------------|--------|--------------|--|--|--|--|

| -                                      | -                                                                                                                                                                                                                                                    | CP1RIE | CP1FIE | -      | -          | CP1MD1     | CP1MD0 | 00000010     |  |  |  |  |

| Bit7                                   | Bit6                                                                                                                                                                                                                                                 | Bit5   | Bit4   | Bit3   | Bit2       | Bit1       | Bit0   | SFR Address: |  |  |  |  |

|                                        |                                                                                                                                                                                                                                                      |        |        |        |            | 0x9C       |        |              |  |  |  |  |

| Bits7–6:<br>Bit5:<br>Bit4:<br>Bits1–0: | 0: Comparator rising-edge interrupt disabled<br>1: Comparator rising-edge interrupt enabled.<br>CP1FIE: Comparator Falling-Edge Interrupt Enable.<br>0: Comparator falling-edge interrupt disabled.<br>1: Comparator falling-edge interrupt enabled. |        |        |        |            |            |        |              |  |  |  |  |

|                                        | Mode                                                                                                                                                                                                                                                 | CP1MD1 | CP1MD0 | CP1 Re | sponse Til | ne (TYP)   |        |              |  |  |  |  |

|                                        | 0                                                                                                                                                                                                                                                    | 0      | 0      |        | st Respons | <u>, ,</u> |        |              |  |  |  |  |

|                                        |                                                                                                                                                                                                                                                      |        |        |        |            |            |        |              |  |  |  |  |

|                                        | 2                                                                                                                                                                                                                                                    | 1      | 0      |        | —          |            | 1      |              |  |  |  |  |

|                                        | 3                                                                                                                                                                                                                                                    | 1      | 1      | Lowest | Power Con  | sumption   | 7      |              |  |  |  |  |

|                                        |                                                                                                                                                                                                                                                      |        |        |        |            |            |        |              |  |  |  |  |

CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

#### 8.1.2. MOVX Instruction and Program Memory

The MOVX instruction is typically used to access external data memory (Note: the C8051F31x does not support external data or program memory). In the CIP-51, the MOVX write instruction is used to accesses external RAM and the on-chip program memory space implemented as re-programmable Flash memory. The Flash access feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to **Section "10. Flash Memory" on page 111** for further details.

| Mnemonic          | Description                              | Bytes | Clock<br>Cycles |  |  |  |  |

|-------------------|------------------------------------------|-------|-----------------|--|--|--|--|

|                   | Arithmetic Operations                    | •     |                 |  |  |  |  |

| ADD A, Rn         | Add register to A                        | 1     | 1               |  |  |  |  |

| ADD A, direct     | Add direct byte to A                     | 2     | 2               |  |  |  |  |

| ADD A, @Ri        | 1                                        | 2     |                 |  |  |  |  |

| ADD A, #data      |                                          |       |                 |  |  |  |  |

| ADDC A, Rn        | Add register to A with carry             | 1     | 1               |  |  |  |  |

| ADDC A, direct    | Add direct byte to A with carry          | 2     | 2               |  |  |  |  |

| ADDC A, @Ri       | Add indirect RAM to A with carry         | 1     | 2               |  |  |  |  |

| ADDC A, #data     | Add immediate to A with carry            | 2     | 2               |  |  |  |  |

| SUBB A, Rn        | Subtract register from A with borrow     | 1     | 1               |  |  |  |  |

| SUBB A, direct    | Subtract direct byte from A with borrow  | 2     | 2               |  |  |  |  |

| SUBB A, @Ri       | Subtract indirect RAM from A with borrow | 1     | 2               |  |  |  |  |

| SUBB A, #data     | Subtract immediate from A with borrow    | 2     | 2               |  |  |  |  |

| INC A             | Increment A                              | 1     | 1               |  |  |  |  |

| INC Rn            | Increment register                       | 1     | 1               |  |  |  |  |

| INC direct        | Increment direct byte                    | 2     | 2               |  |  |  |  |

| INC @Ri           | Increment indirect RAM                   | 1     | 2               |  |  |  |  |

| DEC A             | Decrement A                              | 1     | 1               |  |  |  |  |

| DEC Rn            | Decrement register                       | 1     | 1               |  |  |  |  |

| DEC direct        | Decrement direct byte                    | 2     | 2               |  |  |  |  |

| DEC @Ri           | Decrement indirect RAM                   | 1     | 2               |  |  |  |  |

| INC DPTR          | Increment Data Pointer                   | 1     | 1               |  |  |  |  |

| MUL AB            | Multiply A and B                         | 1     | 4               |  |  |  |  |

| DIV AB            | Divide A by B                            | 1     | 8               |  |  |  |  |

| DA A              | Decimal adjust A                         | 1     | 1               |  |  |  |  |

|                   | Logical Operations                       |       |                 |  |  |  |  |

| ANL A, Rn         | AND Register to A                        | 1     | 1               |  |  |  |  |

| ANL A, direct     | AND direct byte to A                     | 2     | 2               |  |  |  |  |

| ANL A, @Ri        | AND indirect RAM to A                    | 1     | 2               |  |  |  |  |

| ANL A, #data      | AND immediate to A                       | 2     | 2               |  |  |  |  |

| ANL direct, A     | AND A to direct byte                     | 2     | 2               |  |  |  |  |

| ANL direct, #data | AND immediate to direct byte             | 3     | 3               |  |  |  |  |

| ORL A, Rn         | OR Register to A                         | 1     | 1               |  |  |  |  |

### Table 8.1. CIP-51 Instruction Set Summary

instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### 8.3.1. MCU Interrupt Sources and Vectors

The MCUs support 14 interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 8.4 on page 96. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

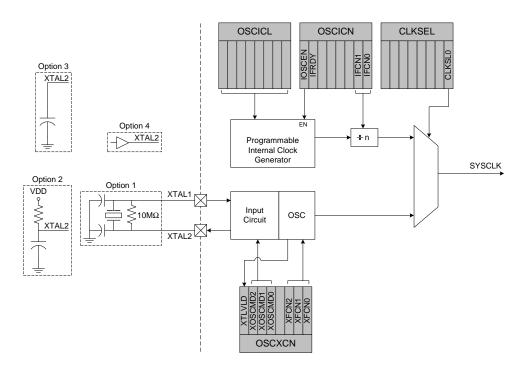

## 12. Oscillators

C8051F31x devices include a programmable internal oscillator and an external oscillator drive circuit. The internal oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 12.1. The system clock can be sourced by the external oscillator circuit, the internal oscillator, or a scaled version of the internal oscillator. The internal oscillator's electrical specifications are given in Table 12.1 on page 123.

Figure 12.1. Oscillator Diagram

### 12.1. Programmable Internal Oscillator

All C8051F31x devices include a programmable internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be programmed via the OSCICL register as defined by SFR Definition 12.1 OSCICL is factor calibrated to obtain a 24.5 MHz frequency.

Electrical specifications for the precision internal oscillator are given in Table 12.1 on page 123. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

## 12.2. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 12.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 12.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 12.4).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see **Section "13.1. Priority Crossbar Decoder" on page 131** for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See **Section "13.2. Port I/O Initialization" on page 133** for details on Port input mode selection.

### 12.3. System Clock Selection

The CLKSL0 bit in register CLKSEL selects which oscillator is used as the system clock. CLKSL0 must be set to '1' for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal and external oscillator, so long as the selected oscillator is enabled and has settled. The internal oscillator requires little start-up time and may be selected as the system clock immediately following the OSCICN write that enables the internal oscillator. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use as the system clock. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external oscillator is settled. **To avoid reading a false XTLVLD, in crystal mode software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD.** RC and C modes typically require no startup time.

### 12.4. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 12.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 12.4. For example, an 11.0592 MHz crystal requires an XFCN setting of 111b.

When the crystal oscillator is first enabled, the oscillator amplitude detection circuit requires a settling time to achieve proper bias. Introducing a delay of 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

- Step 1. Force the XTAL1 and XTAL2 pins low by writing 0s to the port latch.

- Step 2. Configure XTAL1 and XTAL2 as analog inputs.

- Step 3. Enable the external oscillator.

- Step 4. Wait at least 1 ms.

- Step 5. Poll for XTLVLD => '1'.

- Step 6. Switch the system clock to the external oscillator.

Note: Tuning-fork crystals may require additional settling time before XTLVLD returns a valid result.

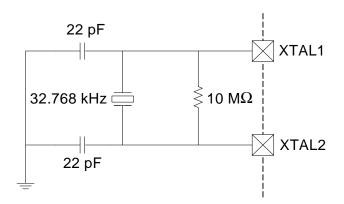

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

**Note:** The load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal data sheet when completing these calculations.

For example, a tuning-fork crystal of 32.768 kHz with a recommended load capacitance of 12.5 pF should use the configuration shown in Figure 12.1, Option 1. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal, as shown in Figure 12.2.

Figure 12.2. 32.768 kHz External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

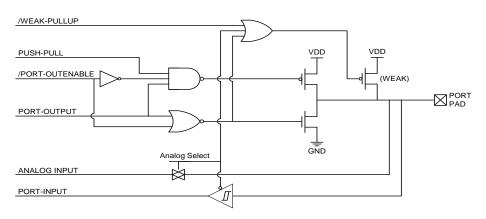

Figure 13.2. Port I/O Cell Block Diagram

|         | P0                                    |   |   |   |   |   |                                | P1 |   |   |   |   | P2                     |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

|---------|---------------------------------------|---|---|---|---|---|--------------------------------|----|---|---|---|---|------------------------|---|---|---|---|---|---|---|---|-----------------------------------------------------------------------------------------------------------------|---|---|

|         |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| PIN I/O | 0                                     | 1 | 2 | 3 | 4 | 5 | 6                              | 7  | 0 | 1 | 2 | 3 | 4                      | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5                                                                                                               | 6 |   |

| ТХО     |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| RX0     |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| SCK     |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| MISO    |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| MOSI    |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| NSS*    |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| SDA     |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| SCL     |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| CP0     |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| CP0A    |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   | e de la come |   |   |

| CP1     |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   | lable                                                                                                           |   |   |

| CP1A    |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   | Signals Unavailable                                                                                             |   |   |

| SYSCLK  |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   | ň                                                                                                               |   |   |

| CEX0    |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   | nals                                                                                                            |   |   |

| CEX1    |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   | Sig                                                                                                             |   |   |

| CEX2    |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| CEX3    |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| CEX4    |                                       |   | 1 |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   | 1 |                                                                                                                 |   |   |

| ECI     |                                       |   | 1 |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   | ]                                                                                                               |   |   |

| то      |                                       |   | 1 |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

| T1      |                                       |   |   |   |   |   |                                |    |   |   |   |   |                        |   |   |   |   |   |   |   |   |                                                                                                                 |   | ] |

|         | 0 0 <u>1 1</u> 0 0 0 0<br>P0SKIP[0:7] |   |   |   |   | 0 | 0 0 0 0 0 0 0 0<br>P1SKIP[0:7] |    |   |   |   | 0 | 0 0 0 0<br>P2SKIP[0:3] |   |   |   |   |   |   |   |   |                                                                                                                 |   |   |

SF Signals Special Function Signals are not assigned by the Crossbar. When these signals are enabled, the Crossbar must be manually configured to skip their corresponding port pins.

\*Note: NSS is only pinned out in 4-wire SPI mode.

Note: P1.6,P1.7,P2.6,P2.7 only available on the C8051F310/1/2/3/4/5; P1SKIP[7:6] should always be set to 11b for the C8051F316/7 devices.

### Figure 13.4. Crossbar Priority Decoder with Crystal Pins Skipped

Registers XBR0 and XBR1 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when the UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, pending the state of the NSS-MD1-NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

| R/W   | R/W           | R/W                      | R/W           | R/W          | R/W     | R/W   | R/W   | Reset Value |

|-------|---------------|--------------------------|---------------|--------------|---------|-------|-------|-------------|

| CP1AE | -             | CP0AE                    | CP0E          | SYSCKE       | SMB0E   | SPI0E | URTOE | 00000000    |

| Bit7  | Bit6          | Bit4                     | Bit1          | SFR Address: |         |       |       |             |

| Ditt  | Bito          | Bit5                     | BRI           | Bit0         | 0xE1    |       |       |             |

|       |               |                          |               |              |         |       |       |             |

| Bit7: | CP1AE: Cor    | nparator1 A              | synchrono     | us Output F  | nable   |       |       |             |

|       | 0: Asynchroi  | •                        |               |              |         |       |       |             |

|       | 1: Asynchroi  |                          |               |              |         |       |       |             |

| Bit6: | CP1E: Com     |                          |               |              |         |       |       |             |

|       | 0: CP1 unav   |                          | •             |              |         |       |       |             |

|       | 1: CP1 route  |                          |               |              |         |       |       |             |

| Bit5: | CP0AE: Cor    | nparator0 <sup>.</sup> A | synchrono     | us Output E  | nable   |       |       |             |

|       | 0: Asynchro   | nous CP0 u               | navailable    | at Port pin. |         |       |       |             |

|       | 1: Asynchroi  |                          |               |              |         |       |       |             |

| Bit4: | CP0E: Com     | parator0 Ou              | tput Enable   | e            |         |       |       |             |

|       | 0: CP0 unav   | ailable at P             | ort pin.      |              |         |       |       |             |

|       | 1: CP0 route  | ed to Port pi            | n.            |              |         |       |       |             |

| Bit3: | SYSCKE: /S    | YSCLK Ou                 | tput Enable   | e            |         |       |       |             |

|       | 0: /SYSCLK    | unavailable              | e at Port pir | า.           |         |       |       |             |

|       | 1: /SYSCLK    |                          |               | oin.         |         |       |       |             |

| Bit2: | SMB0E: SM     |                          |               |              |         |       |       |             |

|       | 0: SMBus I/0  |                          |               | oins.        |         |       |       |             |

|       | 1: SMBus I/0  |                          | Port pins.    |              |         |       |       |             |

| Bit1: | SPI0E: SPI I  |                          |               |              |         |       |       |             |

|       | 0: SPI I/O ur |                          | •             |              |         |       |       |             |

|       | 1: SPI I/O ro |                          |               |              |         |       |       |             |

| Bit0: | URT0E: UA     |                          |               |              |         |       |       |             |

|       | 0: UART I/O   |                          |               |              |         |       |       |             |

|       | 1: UART TX    | 0, RX0 rout              | ed to Port p  | oins P0.4 an | d P0.5. |       |       |             |

|       |               |                          |               |              |         |       |       |             |

### SFR Definition 13.1. XBR0: Port I/O Crossbar Register 0

#### 14.3.2. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 14.3.3. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 14.3.4. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50  $\mu$ s, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods. If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. Note that a clock source is required for free timeout detection, even in a slave-only implementation.

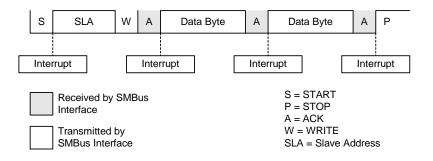

### 14.5. SMBus Transfer Modes

The SMBus interface may be configured to operate as master and/or slave. At any particular time, it will be operating in one of the following four modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. The SMBus interface enters Master Mode any time a START is generated, and remains in Master Mode until it loses an arbitration or generates a STOP. An SMBus interrupt is generated at the end of all SMBus byte frames; however, note that the interrupt is generated before the ACK cycle when operating as a receiver, and after the ACK cycle when operating as a transmitter.

#### 14.5.1. Master Transmitter Mode

Serial data is transmitted on SDA while the serial clock is output on SCL. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 0 (WRITE). The master then transmits one or more bytes of serial data. After each byte is transmitted, an acknowledge bit is generated by the slave. The transfer is ended when the STO bit is set and a STOP is generated. Note that the interface will switch to Master Receiver Mode if SMB0DAT is not written following a Master Transmitter interrupt. Figure 14.5 shows a typical Master Transmitter sequence. Two transmit data bytes are shown, though any number of bytes may be transmitted. Notice that the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

Figure 14.5. Typical Master Transmitter Sequence

## 18. Programmable Counter Array

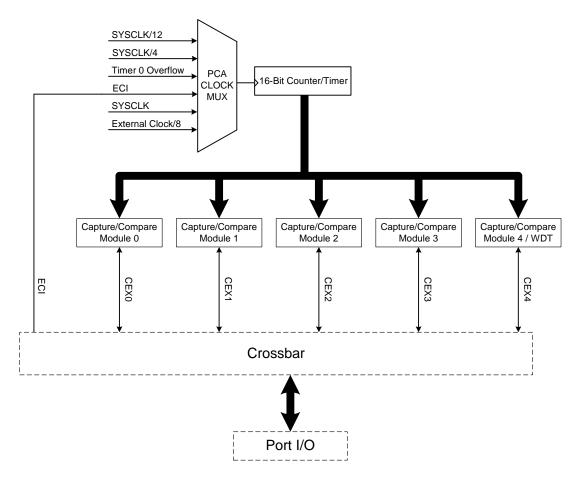

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and five 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "13.1. Priority Crossbar Decoder" on page 131 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "18.2. Capture/Compare Modules" on page 205). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 18.1

**Important Note:** The PCA Module 4 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See **Section 18.3** for details.

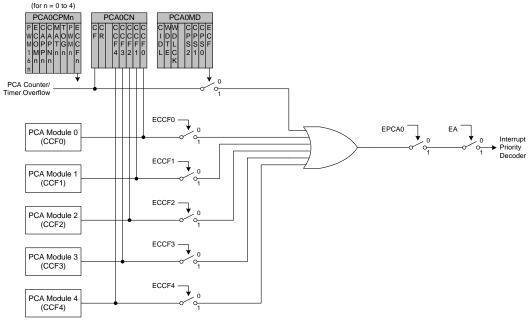

Figure 18.1. PCA Block Diagram

#### 18.2. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

Table 18.2 summarizes the bit settings in the PCA0CPMn registers used to select the PCA capture/compare module's operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note: PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1. See Figure 18.3 for details on the PCA interrupt configuration.

| PWM16    | ECOM   | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                                |

|----------|--------|------|------|-----|-----|-----|------|-----------------------------------------------|

| Х        | Х      | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge<br>on CEXn |

| Х        | Х      | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on CEXn    |

| Х        | Х      | 1    | 1    | 0   | 0   | 0   | Х    | Capture triggered by transition on<br>CEXn    |

| Х        | 1      | 0    | 0    | 1   | 0   | 0   | Х    | Software Timer                                |

| Х        | 1      | 0    | 0    | 1   | 1   | 0   | Х    | High Speed Output                             |

| Х        | 1      | 0    | 0    | Х   | 1   | 1   | Х    | Frequency Output                              |

| 0        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 8-Bit Pulse Width Modulator                   |

| 1        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 16-Bit Pulse Width Modulator                  |

| X = Don' | t Care |      |      |     |     |     |      |                                               |

### Table 18.2. PCA0CPM Register Settings for PCA Capture/Compare Modules