Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 29                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 21x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f312-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR | Definition | 13.5. P0MDOUT: Port0 Output Mode                     | 137 |

|-----|------------|------------------------------------------------------|-----|

| SFR | Definition | 13.6. P0SKIP: Port0 Skip                             | 137 |

| SFR | Definition | 13.7. P1: Port1                                      | 138 |

| SFR | Definition | 13.8. P1MDIN: Port1 Input Mode                       | 138 |

| SFR | Definition | 13.9. P1MDOUT: Port1 Output Mode                     | 139 |

| SFR | Definition | 13.10. P1SKIP: Port1 Skip                            | 139 |

| SFR | Definition | 13.11. P2: Port2                                     | 140 |

| SFR | Definition | 13.12. P2MDIN: Port2 Input Mode                      | 140 |

|     |            | 13.13. P2MDOUT: Port2 Output Mode                    |     |

| SFR | Definition | 13.14. P2SKIP: Port2 Skip                            | 141 |

| SFR | Definition | 13.15. P3: Port3                                     | 142 |

| SFR | Definition | 13.16. P3MDIN: Port3 Input Mode                      | 142 |

| SFR | Definition | 13.17. P3MDOUT: Port3 Output Mode                    | 143 |

|     |            | 14.1. SMB0CF: SMBus Clock/Configuration              |     |

|     |            | 14.2. SMB0CN: SMBus Control                          |     |

| SFR | Definition | 14.3. SMB0DAT: SMBus Data                            | 156 |

| SFR | Definition | 15.1. SCON0: Serial Port 0 Control                   | 168 |

| SFR | Definition | 15.2. SBUF0: Serial (UART0) Port Data Buffer         | 169 |

| SFR | Definition | 16.1. SPI0CFG: SPI0 Configuration                    | 180 |

|     |            | 16.2. SPI0CN: SPI0 Control                           |     |

| SFR | Definition | 16.3. SPI0CKR: SPI0 Clock Rate                       | 182 |

| SFR | Definition | 16.4. SPI0DAT: SPI0 Data                             | 182 |

|     |            | 17.1. TCON: Timer Control                            |     |

|     |            | 17.2. TMOD: Timer Mode                               |     |

| SFR | Definition | 17.3. CKCON: Clock Control                           | 193 |

| SFR | Definition | 17.4. TL0: Timer 0 Low Byte                          | 194 |

|     |            | 17.5. TL1: Timer 1 Low Byte                          |     |

|     |            | 17.6. THO: Timer 0 High Byte                         |     |

|     |            | 17.7. TH1: Timer 1 High Byte                         |     |

| SFR | Definition | 17.8. TMR2CN: Timer 2 Control                        | 197 |

| SFR | Definition | 17.9. TMR2RLL: Timer 2 Reload Register Low Byte      | 198 |

| SFR | Definition | 17.10. TMR2RLH: Timer 2 Reload Register High Byte    | 198 |

| SFR | Definition | 17.11. TMR2L: Timer 2 Low Byte                       | 198 |

|     |            | 17.12. TMR2H Timer 2 High Byte                       |     |

| SFR | Definition | 17.13. TMR3CN: Timer 3 Control                       | 201 |

| SFR | Definition | 17.14. TMR3RLL: Timer 3 Reload Register Low Byte     | 202 |

| SFR | Definition | 17.15. TMR3RLH: Timer 3 Reload Register High Byte    | 202 |

|     |            | 17.16. TMR3L: Timer 3 Low Byte                       |     |

|     |            | 17.17. TMR3H Timer 3 High Byte                       |     |

|     |            | 18.1. PCA0CN: PCA Control                            |     |

| SFR | Definition | 18.2. PCA0MD: PCA Mode                               | 216 |

| SFR | Definition | 18.3. PCA0CPMn: PCA Capture/Compare Mode Registers . | 217 |

|     |            | 18.4. PCA0L: PCA Counter/Timer Low Byte              |     |

|     |            | 18.5. PCA0H: PCA Counter/Timer High Byte             |     |

|     |            | 18.6. PCA0CPLn: PCA Capture Module Low Byte          |     |

|     |            |                                                      |     |

| SFR Definition 18.7. PCA0CPHn: PCA Capture Module High Byte      | . 219 |

|------------------------------------------------------------------|-------|

| C2 Register Definition 20.1. C2ADD: C2 Address                   | . 223 |

| C2 Register Definition 20.2. DEVICEID: C2 Device ID              | . 223 |

| C2 Register Definition 20.3. REVID: C2 Revision ID               | . 224 |

| C2 Register Definition 20.4. FPCTL: C2 Flash Programming Control | . 224 |

| C2 Register Definition 20.5. FPDAT: C2 Flash Programming Data    | . 224 |

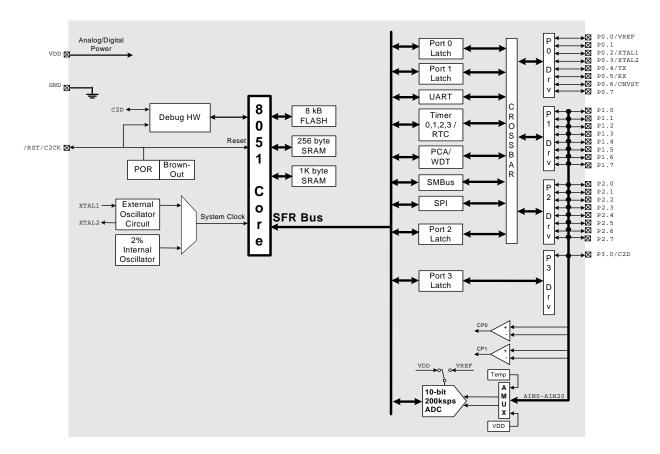

Figure 1.4. C8051F313 Block Diagram

# Table 3.1. Global DC Electrical Characteristics (Continued)

-40°C to +85°C, 25 MHz System Clock unless otherwise specified.

| Parameter                                       | Conditions                                                  | Min     | Тур      | Max  | Units  |

|-------------------------------------------------|-------------------------------------------------------------|---------|----------|------|--------|

| Digital Supply Current—CPU Inac                 | ctive (Idle Mode, not fetching instru                       | uctions | from Fla | ish) |        |

| I <sub>DD</sub> (Note 3)                        | $V_{DD}$ = 3.0 V, F = 25 MHz                                |         | 3.8      | 4.3  | mA     |

|                                                 | V <sub>DD</sub> = 3.0 V, F = 1 MHz                          | —       | 0.20     | —    | mA     |

|                                                 | V <sub>DD</sub> = 3.0 V, F = 80 kHz                         | —       | 16       | —    | μA     |

|                                                 | V <sub>DD</sub> = 3.6 V, F = 25 MHz                         | —       | 4.8      | 5.3  | mA     |

| I <sub>DD</sub> Supply Sensitivity (Note 3,     | F = 25 MHz                                                  | —       | 44       | _    | %/V    |

| Note 4)                                         | F = 1 MHz                                                   | _       | 56       | _    | %/V    |

| I <sub>DD</sub> Frequency Sensitivity (Note 3,  | $V_{DD}$ = 3.0 V, F $\leq$ 1 MHz, T = 25 °C                 |         | 0.21     |      | mA/MHz |

| Note 6)                                         | V <sub>DD</sub> = 3.0 V, F > 1 MHz, T = 25 °C               | —       | 0.15     | _    | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F <u>&lt;</u> 1 MHz, T = 25 °C     | —       | 0.28     |      | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F > 1 MHz, T = 25 °C               | _       | 0.19     | _    | mA/MHz |

| Digital Supply Current<br>(Stop Mode, shutdown) | Oscillator not running,<br>V <sub>DD</sub> Monitor Disabled | _       | < 0.1    | _    | μA     |

#### Notes:

- 1. Given in Table 9.1 on page 110.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

- 3. Based on device characterization data, not production tested.

- 4. Active and Inactive I<sub>DD</sub> at voltages and frequencies other than those specified can be calculated using the I<sub>DD</sub> Supply Sensitivity. For example, if the V<sub>DD</sub> is 3.3 V instead of 3.0 V at 25 MHz: I<sub>DD</sub> = 7.8 mA typical at 3.0 V and f = 25 MHz. From this, I<sub>DD</sub> = 7.8 mA + 0.67 x (3.3 V 3.0 V) = 8 mA at 3.3 V and f = 25 MHz.

- 5. I<sub>DD</sub> can be estimated for frequencies ≤ 15 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> for > 15 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:

$V_{DD}$  = 3.0 V; F = 20 MHz,  $I_{DD}$  = 7.8 mA – (25 MHz – 20 MHz) x 0.21 mA/MHz = 6.75 mA.

Idle I<sub>DD</sub> can be estimated for frequencies ≤ 1 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate Idle I<sub>DD</sub> for > 1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:

$V_{DD}$  = 3.0 V; F = 5 MHz, Idle I<sub>DD</sub> = 4.8 mA – (25 MHz – 5 MHz) x 0.15 mA/MHz = 1.8 mA.

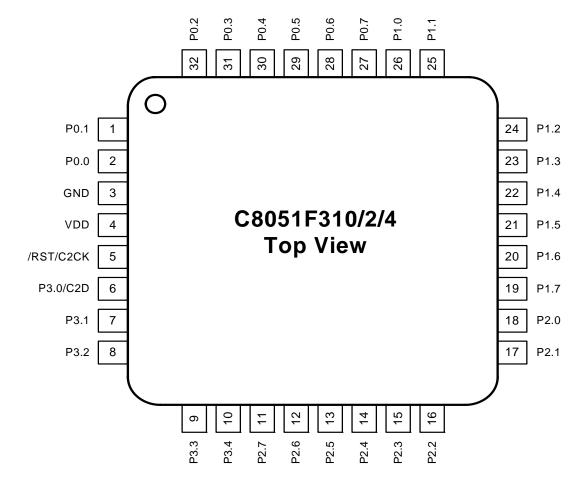

Figure 4.1. LQFP-32 Pinout Diagram (Top View)

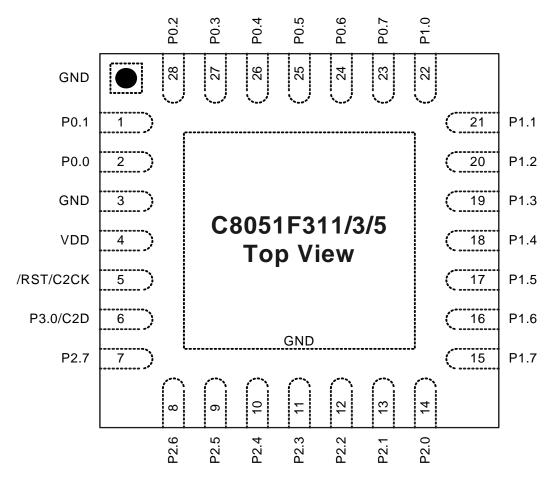

Figure 4.3. QFN-28 Pinout Diagram (Top View)

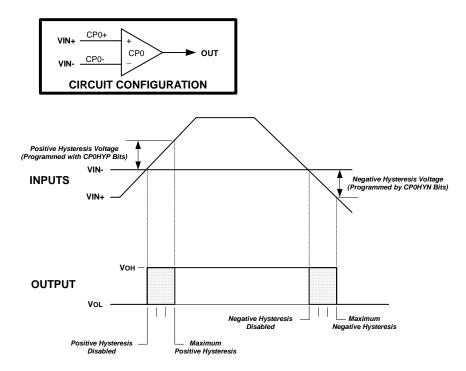

Figure 7.3. Comparator Hysteresis Plot

The Comparator hysteresis is software-programmable via its Comparator Control register CPTnCN (for n = 0 or 1). The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator hysteresis is programmed using Bits3-0 in the Comparator Control Register CPTnCN (shown in SFR Definition 7.1 and SFR Definition 7.4). The amount of negative hysteresis voltage is determined by the settings of the CPnHYN bits. As shown in Table 7.1, settings of 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPnHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see **Section "8.3. Interrupt Handler" on page 93**). The CPnFIF flag is set to logic 1 upon a Comparator falling-edge interrupt, and the CPnRIF flag is set to logic 1 upon the Comparator rising-edge interrupt. Once set, these bits remain set until cleared by software. The output state of the Comparator can be obtained at any time by reading the CPnOUT bit. The Comparator is enabled by setting the CPnEN bit to logic 1, and is disabled by clearing this bit to logic 0.

The output state of the Comparator can be obtained at any time by reading the CPnOUT bit. The Comparator is enabled by setting the CPnEN bit to logic 1, and is disabled by clearing this bit to logic 0.

Note that false rising edges and falling edges can be detected when the comparator is first powered-on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed. This Power Up Time is specified in Table 7.1 on page 78.

| R/W      | R                        | R/W    | R/W    | R/W           | R/W           | R/W          | R/W        | Reset Value  |

|----------|--------------------------|--------|--------|---------------|---------------|--------------|------------|--------------|

| CP1EN    | CP1OUT                   | CP1RIF | CP1FIF | CP1HYP1       | CP1HYP0       | CP1HYN1      | CP1HYN0    | 00000000     |

| Bit7     | Bit6 Bit5 Bit            |        | Bit4   | Bit3          | Bit2          | Bit1         | Bit0       | SFR Address: |

|          |                          |        |        |               |               |              |            | 0x9A         |

|          |                          |        |        |               |               |              |            |              |

| Bit7:    | CP1EN: Cor               | •      |        |               |               |              |            |              |

|          | 0: Comparat              |        |        |               |               |              |            |              |

| Dito     | 1: Comparat              |        |        |               |               |              |            |              |

| Bit6:    | CP1OUT: Co               |        |        | ate Flag.     |               |              |            |              |

|          | 0: Voltage or            |        |        |               |               |              |            |              |

| D:45     | 1: Voltage or            |        |        |               |               |              |            |              |

| Bit5:    | CP1RIF: Co               |        |        |               |               | aa thia flag | waa laat a | loorod       |

|          | 0: No Compa              |        |        |               |               | ce this hag  | was last c | leared.      |

| Bit4:    | 1: Comparat              | -      | -      | •             |               |              |            |              |

| DIL4.    | CP1FIF: Cor              |        |        |               |               | a this floo  |            | loorod       |

|          | 0: No Comparat           |        |        |               |               | ice this hay | was last ( | leareu.      |

| Bits3-2: | 1: Comparat<br>CP1HYP1–0 | -      | -      | •             |               | c.           |            |              |

| DII53-2. | 00: Positive             |        |        | le riysteresi |               | 5.           |            |              |

|          | 00: Positive             |        |        |               |               |              |            |              |

|          | 10: Positive             | •      |        |               |               |              |            |              |

|          | 11: Positive I           |        |        |               |               |              |            |              |

| Bits1–0: | CP1HYN1-0                |        |        | ive Hysteres  | sis Control B | its          |            |              |

| Ditor 0. | 00: Negative             | •      | -      | •             |               | 110.         |            |              |

|          | 01: Negative             |        |        |               |               |              |            |              |

|          | 10: Negative             |        |        |               |               |              |            |              |

|          | 11: Negative             |        |        |               |               |              |            |              |

|          |                          |        |        |               |               |              |            |              |

|          |                          |        |        |               |               |              |            |              |

# SFR Definition 7.4. CPT1CN: Comparator1 Control

#### 8.4.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ sec.

| R/W      | R/W                                              | R/W                    | R/W          | R/W            | R/W          | R/W           | R/W           | Reset Value  |  |  |  |

|----------|--------------------------------------------------|------------------------|--------------|----------------|--------------|---------------|---------------|--------------|--|--|--|

| GF5      | GF4                                              | 4 GF3 GF2 GF1 GF0 STOP |              | IDLE           | 00000000     |               |               |              |  |  |  |

| Bit7     | Bit6                                             | Bit0                   | SFR Address: |                |              |               |               |              |  |  |  |

|          | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Ac<br>Oxi |                        |              |                |              |               |               |              |  |  |  |

|          |                                                  |                        |              |                |              |               |               |              |  |  |  |

| Bits7–2: | GF5–GF0: G                                       |                        |              |                | •            |               |               |              |  |  |  |

|          | These are ge                                     |                        | -            | r use under    | software c   | ontrol.       |               |              |  |  |  |

| Bit1:    | STOP: Stop                                       |                        |              |                |              |               |               |              |  |  |  |

|          | Setting this b                                   | •                      |              | •              |              | t will always | be read a     | s 0.         |  |  |  |

|          | 1: CPU goes                                      |                        | •            | nal oscillato  | r stopped).  |               |               |              |  |  |  |

| Bit0:    | IDLE: Idle M                                     | ode Select.            |              |                |              |               |               |              |  |  |  |

|          | Setting this b                                   | bit will place         | e the CIP-51 | in Idle mod    | de. This bit | will always   | be read as    | s 0.         |  |  |  |

|          | 1: CPU goes                                      | s into Idle m          | ode. (Shuts  | s off clock to | CPU, but o   | clock to Tim  | iers, Interru | upts, Serial |  |  |  |

|          | Ports, and A                                     | nalog Perip            | herals are s | still active.) |              |               |               |              |  |  |  |

|          |                                                  |                        |              |                |              |               |               |              |  |  |  |

# SFR Definition 8.12. PCON: Power Control

any other reset source. For example, if the  $V_{DD}$  monitor is enabled and a software reset is performed, the  $V_{DD}$  monitor will still be enabled after the reset.

**Important Note:** The  $V_{DD}$  monitor must be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. The procedure for configuring the  $V_{DD}$  monitor as a reset source is shown below:

- Step 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = '1').

- Step 2. Wait for the V<sub>DD</sub> monitor to stabilize (see Table 9.1 for the V<sub>DD</sub> Monitor turn-on time). Note: This delay should be omitted if software contains routines that erase or write Flash memory.

- Step 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = '1').

See Figure 9.2 for  $V_{DD}$  monitor timing; note that the reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 9.1 for complete electrical characteristics of the  $V_{DD}$  monitor.

| SFR Definition 9.1. VDM0CN: | V <sub>DD</sub> Monitor Control |

|-----------------------------|---------------------------------|

|-----------------------------|---------------------------------|

| R/W      | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R                                                                                                                  | R                                                        | R                                        | R                            | R            | R            | Reset Value |  |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------|------------------------------|--------------|--------------|-------------|--|--|--|--|--|--|

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |                                                          | Reserved                                 |                              |              |              | Variable    |  |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit5                                                                                                               | Bit4                                                     | Bit3                                     | Bit2                         | Bit1         | Bit0         | J vanabio   |  |  |  |  |  |  |

| Diti     | Dito                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dito                                                                                                               | Ditt                                                     | Bito                                     | DILL                         | Ditt         | SFR Address: | 0xFF        |  |  |  |  |  |  |

| Bit7:    | <ul> <li>t7: VDMEN: V<sub>DD</sub> Monitor Enable.</li> <li>This bit is turns the V<sub>DD</sub> monitor circuit on/off. The V<sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (Figure 9.2). The V<sub>DD</sub> Monitor must be allowed to stabilize before it is selected as a reset source. Selecting the V<sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset.</li> </ul> |                                                                                                                    |                                                          |                                          |                              |              |              |             |  |  |  |  |  |  |

| Bit6:    | See Table 9.<br>0: $V_{DD}$ Monit<br>1: $V_{DD}$ Monit<br>$V_{DD}$ STAT: V<br>This bit indic<br>0: $V_{DD}$ is at c<br>1: $V_{DD}$ is abc                                                                                                                                                                                                                                                                                                                                               | tor Disabled<br>for Enabled<br>f <sub>DD</sub> Status.<br>ates the cu<br>for below the<br>pove the V <sub>DD</sub> | I.<br>rrent power<br>V <sub>DD</sub> monit<br>monitor th | supply stat<br>tor threshold<br>reshold. | us (V <sub>DD</sub> Mo<br>d. | onitor outpu | t).          |             |  |  |  |  |  |  |

| Bits5–0: | Reserved. R                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ead = Varia                                                                                                        | ble. Write =                                             | don't care                               |                              |              |              |             |  |  |  |  |  |  |

# 9.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 9.1 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

#### 10.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modi-fying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

The following guidelines are recommended for any system that contains routines which write or erase Flash from code.

#### 10.4.1. $V_{DD}$ Maintenance and the $V_{DD}$ Monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Make certain that the minimum  $V_{DD}$  rise time specification of 1 ms is met. If the system cannot meet this rise time specification, then add an external  $V_{DD}$  brownout circuit to the RST pin of the device that holds the device in reset until  $V_{DD}$  reaches 2.7 V and re-asserts RST if  $V_{DD}$  drops below 2.7 V.

- 3. Enable the on-chip V<sub>DD</sub> monitor and enable the V<sub>DD</sub> monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For 'C'-based systems, this will involve modifying the startup code added by the 'C' compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> monitor and enabling the V<sub>DD</sub> monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 4. As an added precaution, explicitly enable the V<sub>DD</sub> monitor and enable the V<sub>DD</sub> monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> monitor enable instructions should be placed just after the instruction to set PSWE to a '1', but before the Flash write or erase operation instruction.

- Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct. "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a '1'. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 10.4.2. PSWE Maintenance

- 7. Reduce the number of places in code where the PSWE bit (b0 in PSCTL) is set to a '1'. There should be exactly one routine in code that sets PSWE to a '1' to write Flash bytes and one routine in code that sets PSWE and PSEE both to a '1' to erase Flash pages.

- 8. Minimize the number of variable accesses while PSWE is set to a '1'. Handle pointer address updates and loop variable maintenance outside the "PSWE = 1; ... PSWE = 0;" area. Code examples showing this can be found in AN201, "Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 9. Disable interrupts prior to setting PSWE to a '1' and leave them disabled until after PSWE has been reset to '0'. Any interrupts posted during the Flash write or erase operation will be serviced in priority order after the Flash operation has been completed and interrupts have been re-enabled by software.

# SFR Definition 12.3. CLKSEL: Clock Select

| R/W                                                                                                                                                                                                                                                                         | R/W        | R/W      | R/W      | R/W      | R/W      | R/W      | R/W    | Reset Value |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|----------|----------|----------|----------|--------|-------------|--|--|--|--|

| Reserved                                                                                                                                                                                                                                                                    | d Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | CLKSL0 | 00000000    |  |  |  |  |

| Bit7                                                                                                                                                                                                                                                                        | Bit6       | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0   | SFR Address |  |  |  |  |

|                                                                                                                                                                                                                                                                             |            |          |          |          |          |          |        | 0xA9        |  |  |  |  |

| Bits7–1: Reserved. Read = 000000b, Must Write = 0000000.<br>Bit0: CLKSL0: System Clock Source Select Bit.<br>0: SYSCLK derived from the Internal Oscillator, and scales per the IFCN bits in register<br>OSCICN.<br>1: SYSCLK derived from the External Oscillator circuit. |            |          |          |          |          |          |        |             |  |  |  |  |

# Table 12.1. Internal Oscillator Electrical Characteristics

$V_{DD}$  = 2.7 to 3.6 V; –40 to +85 °C unless otherwise specified.

| Parameter                                                     | Conditions   | Min | Тур  | Max  | Units |

|---------------------------------------------------------------|--------------|-----|------|------|-------|

| Internal Oscillator Frequency                                 |              | 24  | 24.5 | 25   | MHz   |

| Internal Oscillator Supply<br>Current (from V <sub>DD</sub> ) | OSCICN.7 = 1 | _   | 450  | 1000 | μA    |

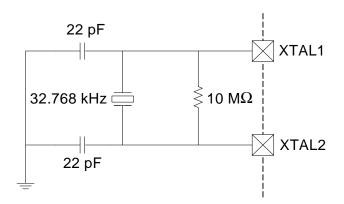

# 12.4. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 12.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 12.4. For example, an 11.0592 MHz crystal requires an XFCN setting of 111b.

When the crystal oscillator is first enabled, the oscillator amplitude detection circuit requires a settling time to achieve proper bias. Introducing a delay of 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

- Step 1. Force the XTAL1 and XTAL2 pins low by writing 0s to the port latch.

- Step 2. Configure XTAL1 and XTAL2 as analog inputs.

- Step 3. Enable the external oscillator.

- Step 4. Wait at least 1 ms.

- Step 5. Poll for XTLVLD => '1'.

- Step 6. Switch the system clock to the external oscillator.

Note: Tuning-fork crystals may require additional settling time before XTLVLD returns a valid result.

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

**Note:** The load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal data sheet when completing these calculations.

For example, a tuning-fork crystal of 32.768 kHz with a recommended load capacitance of 12.5 pF should use the configuration shown in Figure 12.1, Option 1. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal, as shown in Figure 12.2.

Figure 12.2. 32.768 kHz External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

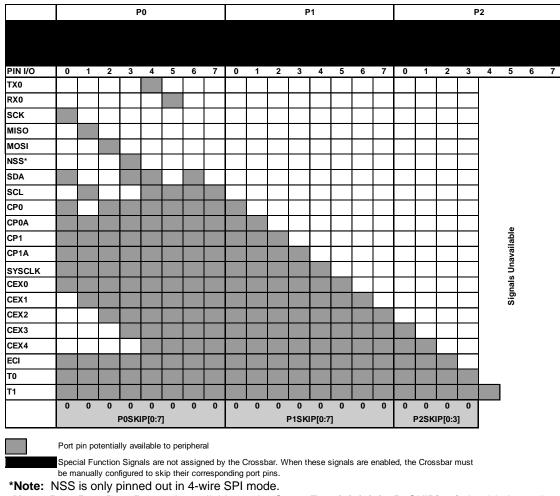

#### 13.1. Priority Crossbar Decoder

The Priority Crossbar Decoder (Figure 13.3) assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource (excluding UART0, which is always at pins 4 and 5). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO.

**Important Note on Crossbar Configuration:** If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to P0.0 if VREF is used, P0.3 and/or P0.2 if the external oscillator circuit is enabled, P0.6 if the ADC is configured to use the external conversion start signal (CNVSTR), and any selected ADC or Comparator inputs. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin. Figure 13.3 shows the Crossbar Decoder priority with no Port pins skipped (P0SKIP, P1SKIP, P2SKIP = 0x00); Figure 13.4 shows the Crossbar Decoder priority with the XTAL1 (P0.2) and XTAL2 (P0.3) pins skipped (P0SKIP = 0x0C to skip P0.2 and P0.3 for XTAL use).

Note: P1.6,P1.7,P2.6,P2.7 only available on the C8051F310/1/2/3/4/5; P1SKIP[7:6] should always be set to 11b for the C8051F316/7 devices.

#### Figure 13.3. Crossbar Priority Decoder with No Pins Skipped

|         |   |   |   | F         | °0          |        |   |   |   | P1 |   |           |             |        |   |   |   |           |             | F       | 22 |                                                                                                                 |   |   |

|---------|---|---|---|-----------|-------------|--------|---|---|---|----|---|-----------|-------------|--------|---|---|---|-----------|-------------|---------|----|-----------------------------------------------------------------------------------------------------------------|---|---|

|         |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| PIN I/O | 0 | 1 | 2 | 3         | 4           | 5      | 6 | 7 | 0 | 1  | 2 | 3         | 4           | 5      | 6 | 7 | 0 | 1         | 2           | 3       | 4  | 5                                                                                                               | 6 |   |

| ТХО     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| RX0     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| SCK     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| MISO    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| MOSI    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| NSS*    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| SDA     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| SCL     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| CP0     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| CP0A    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    | e de la come |   |   |

| CP1     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    | lable                                                                                                           |   |   |

| CP1A    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    | Signals Unavailable                                                                                             |   |   |

| SYSCLK  |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    | ň                                                                                                               |   |   |

| CEX0    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    | nals                                                                                                            |   |   |

| CEX1    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    | Sig                                                                                                             |   |   |

| CEX2    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| CEX3    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| CEX4    |   |   | 1 |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         | 1  |                                                                                                                 |   |   |

| ECI     |   |   | 1 |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    | ]                                                                                                               |   |   |

| то      |   |   | 1 |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   |   |

| T1      |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |         |    |                                                                                                                 |   | 1 |

|         | 0 | 0 | 1 | 1<br>P0SK | 0<br>IP[0:7 | 0<br>] | 0 | 0 | 0 | 0  | 0 | 0<br>P1SK | 0<br>IP[0:7 | 0<br>] | 0 | 0 | 0 | 0<br>P2SK | 0<br>IP[0:3 | 0<br>5] |    |                                                                                                                 |   | - |

SF Signals Special Function Signals are not assigned by the Crossbar. When these signals are enabled, the Crossbar must be manually configured to skip their corresponding port pins.

\*Note: NSS is only pinned out in 4-wire SPI mode.

Note: P1.6,P1.7,P2.6,P2.7 only available on the C8051F310/1/2/3/4/5; P1SKIP[7:6] should always be set to 11b for the C8051F316/7 devices.

# Figure 13.4. Crossbar Priority Decoder with Crystal Pins Skipped

Registers XBR0 and XBR1 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when the UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, pending the state of the NSS-MD1-NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

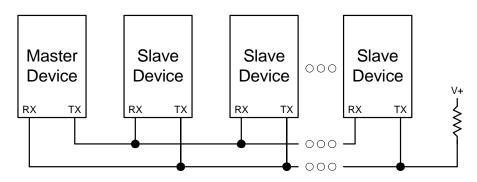

#### 15.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 15.6. UART Multi-Processor Mode Interconnect Diagram

# SFR Definition 15.2. SBUF0: Serial (UART0) Port Data Buffer

| R/W      | R/W                                                                             | R/W                                      | R/W                                          | R/W                        | R/W                             | R/W          | R/W           | Reset Value |

|----------|---------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------|----------------------------|---------------------------------|--------------|---------------|-------------|

|          |                                                                                 |                                          |                                              |                            |                                 |              |               | 00000000    |

| Bit7     | Bit6                                                                            | Bit5                                     | Bit4                                         | Bit3                       | Bit2                            | Bit1         | Bit0          | _           |

|          |                                                                                 |                                          |                                              |                            |                                 |              | SFR Address   | :: 0x99     |

| Bits7–0: | SBUF0[7:0]:<br>This SFR ac<br>data is writte<br>sion. Writing<br>tents of the r | cesses two<br>en to SBUF(<br>a byte to S | registers; a<br>), it goes to<br>BUF0 initia | transmit sh<br>the transmi | ift register a<br>t shift regis | ter and is h | eld for seria | I transmis- |

# 16.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

#### 16.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

#### 16.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

#### 16.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 16.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 16.2, Figure 16.3, and Figure 16.4 for typical connection diagrams of the various operational modes. Note that the setting of NSSMD bits affects the pinout of the device. When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "13. Port Input/Output" on page 129 for general purpose port I/O and crossbar information.

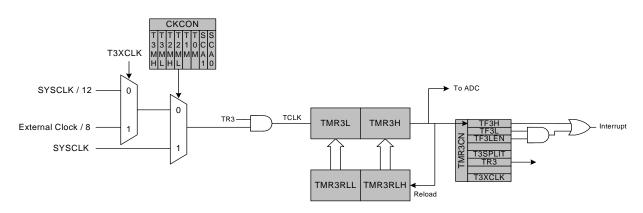

# 17.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T3SPLIT bit (TMR3CN.3) defines the Timer 3 operation mode.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 17.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TM32RLL) is loaded into the Timer 3 register as shown in Figure 17.4, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled, an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x000.

Figure 17.6. Timer 3 16-Bit Mode Block Diagram

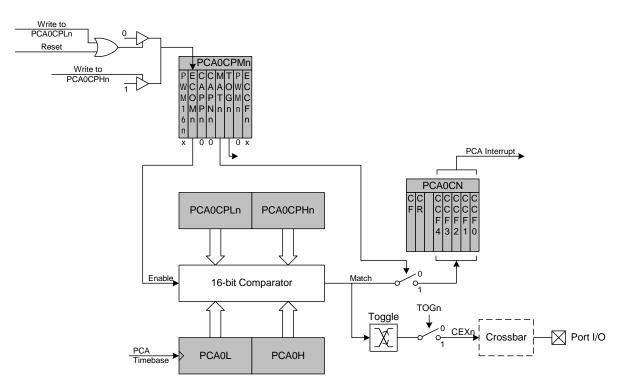

#### 18.2.3. High-Speed Output Mode

In High Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn) Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 18.6. PCA High Speed Output Mode Diagram