Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 29                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 21x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-LQFP                                                         |

| Supplier Device Package    | 32-LQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f312-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 16.8. SPI Master Timing (CKPHA = 0)       183         Figure 16.9. SPI Master Timing (CKPHA = 1)       183         Figure 16.10. SPI Slave Timing (CKPHA = 0)       184         Figure 16.11. SPI Slave Timing (CKPHA = 1)       184 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17. Timers                                                                                                                                                                                                                                  |

| Figure 17.1. T0 Mode 0 Block Diagram 188                                                                                                                                                                                                    |

| Figure 17.2. T0 Mode 2 Block Diagram 189                                                                                                                                                                                                    |

| Figure 17.3. T0 Mode 3 Block Diagram 190                                                                                                                                                                                                    |

| Figure 17.4. Timer 2 16-Bit Mode Block Diagram 195                                                                                                                                                                                          |

| Figure 17.5. Timer 2 8-Bit Mode Block Diagram 196                                                                                                                                                                                           |

| Figure 17.6. Timer 3 16-Bit Mode Block Diagram 199                                                                                                                                                                                          |

| Figure 17.7. Timer 3 8-Bit Mode Block Diagram 200                                                                                                                                                                                           |

| 18. Programmable Counter Array                                                                                                                                                                                                              |

| Figure 18.1. PCA Block Diagram 203                                                                                                                                                                                                          |

| Figure 18.2. PCA Counter/Timer Block Diagram 204                                                                                                                                                                                            |

| Figure 18.3. PCA Interrupt Block Diagram                                                                                                                                                                                                    |

| Figure 18.4. PCA Capture Mode Diagram 206                                                                                                                                                                                                   |

| Figure 18.5. PCA Software Timer Mode Diagram 207                                                                                                                                                                                            |

| Figure 18.6. PCA High Speed Output Mode Diagram 208                                                                                                                                                                                         |

| Figure 18.7. PCA Frequency Output Mode 209                                                                                                                                                                                                  |

| Figure 18.8. PCA 8-Bit PWM Mode Diagram 210                                                                                                                                                                                                 |

| Figure 18.9. PCA 16-Bit PWM Mode 211                                                                                                                                                                                                        |

| Figure 18.10. PCA Module 4 with Watchdog Timer Enabled 212                                                                                                                                                                                  |

| 19. Revision Specific Behavior                                                                                                                                                                                                              |

| Figure 19.1. Reading Package Marking 221                                                                                                                                                                                                    |

| 20. C2 Interface                                                                                                                                                                                                                            |

| Figure 20.1. Typical C2 Pin Sharing 225                                                                                                                                                                                                     |

### 1.1. CIP-51<sup>™</sup> Microcontroller Core

### 1.1.1. Fully 8051 Compatible

The C8051F31x family utilizes Silicon Laboratories' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The CIP-51 core offers all the peripherals included with a standard 8052, including four 16-bit counter/timers, a full-duplex UART with extended baud rate configuration, an enhanced SPI port, 1280 bytes of internal RAM, 128 byte Special Function Register (SFR) address space, and 29/25/21 I/O pins.

### 1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12-to-24 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

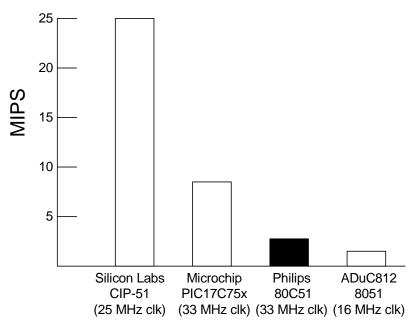

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. Figure 1.9 shows a comparison of peak throughputs for various 8-bit microcontroller cores with their maximum system clocks.

Figure 1.9. Comparison of Peak MCU Execution Speeds

## 2. Absolute Maximum Ratings

| Parameter                                                              | Conditions | Min  | Тур | Max | Units |

|------------------------------------------------------------------------|------------|------|-----|-----|-------|

| Ambient temperature under bias                                         |            | -55  | —   | 125 | °C    |

| Storage Temperature                                                    |            | -65  | —   | 150 | °C    |

| Voltage on any Port I/O Pin or RST with respect to GND                 |            | -0.3 | —   | 5.8 | V     |

| Voltage on $V_{DD}$ with respect to GND                                |            | -0.3 | —   | 4.2 | V     |

| Maximum Total current through V <sub>DD</sub> and GND                  |            | _    | _   | 500 | mA    |

| Maximum output current sunk by $\overline{\text{RST}}$ or any Port pin |            |      |     | 100 | mA    |

| *Note: Stresses above those listed under "Abso                         |            | • •  | •   |     | •     |

## Table 2.1. Absolute Maximum Ratings<sup>\*</sup>

\***Note:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

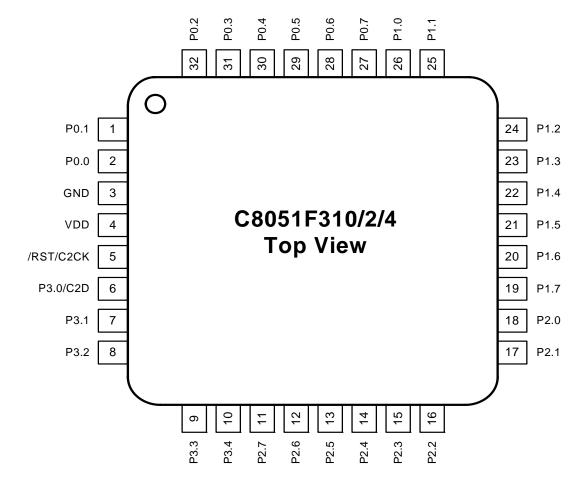

Figure 4.1. LQFP-32 Pinout Diagram (Top View)

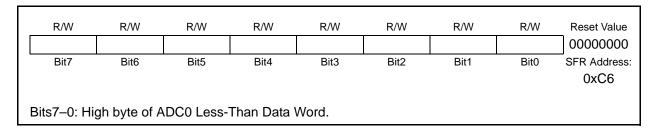

### SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte

### SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte

|   | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |  |  |  |  |

|---|------------------------------------------------|------|------|------|------|------|------|------|--------------|--|--|--|--|

|   |                                                |      |      |      |      |      |      |      | 0000000      |  |  |  |  |

|   | Bit7                                           | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |  |  |  |  |

|   |                                                |      |      |      |      |      |      |      |              |  |  |  |  |

|   |                                                |      |      |      |      |      |      |      |              |  |  |  |  |

| E | Bits7–0: Low byte of ADC0 Less-Than Data Word. |      |      |      |      |      |      |      |              |  |  |  |  |

## 6. Voltage Reference (C8051F310/1/2/3/6 only)

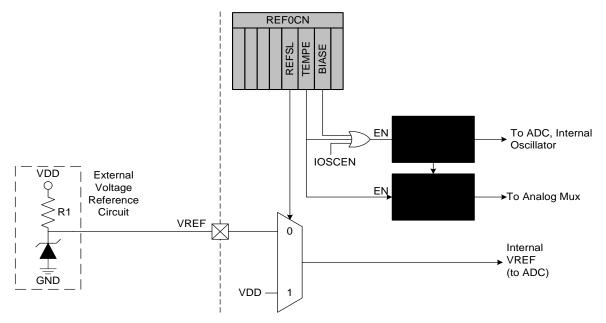

The voltage reference MUX on C8051F310/1/2/3/6 devices is configurable to use an externally connected voltage reference, or the power supply voltage (see Figure 6.1). The REFSL bit in the Reference Control register (REF0CN) selects the reference source. For an external source, REFSL should be set to '0'; For  $V_{DD}$  as the reference source, REFSL should be set to '1'.

The BIASE bit enables the internal voltage bias generator, which is used by the ADC, Temperature Sensor, and Internal Oscillator. This bit is forced to logic 1 when any of the aforementioned peripherals is enabled. The bias generator may be enabled manually by writing a '1' to the BIASE bit in register REF0CN; see SFR Definition 6.1 for REF0CN register details. The electrical specifications for the voltage reference circuit are given in Table 6.1.

**Important Note About the VREF Input:** Port pin P0.0 is used as the external VREF input. When using an external voltage reference, P0.0 should be configured as analog input and skipped by the Digital Crossbar. To configure P0.0 as analog input, set to '0' Bit0 in register P0MDIN. To configure the Crossbar to skip P0.0, set to '1' Bit0 in register P0SKIP. Refer to **Section "13. Port Input/Output" on page 129** for complete Port I/O configuration details.

The temperature sensor connects to the highest order input of the ADC0 positive input multiplexer (see **Section "5.1. Analog Multiplexer" on page 51** for details). The TEMPE bit in register REF0CN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

Figure 6.1. Voltage Reference Functional Block Diagram

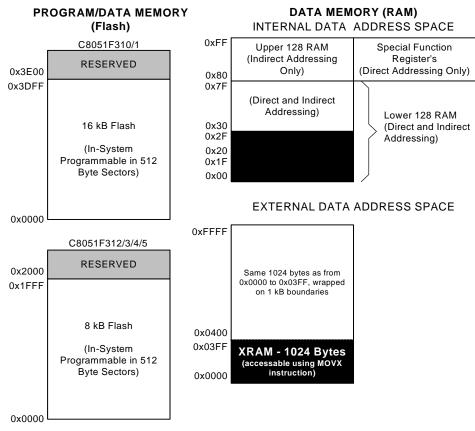

### 8.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The CIP-51 memory organization is shown in Figure 8.2.

#### 8.2.1. Program Memory

The CIP-51 core has a 64k-byte program memory space. The C8051F310/1 and C8051F312/3/4/5 implement 16 and 8 kB, respectively, of this program memory space as in-system, re-programmable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x3FFF or 0x0000 to 0x1FFF. Addresses above 0x3E00 are reserved on the 16 kB devices.

Program memory is normally assumed to be read-only. However, the CIP-51 can write to program memory by setting the Program Store Write Enable bit (PSCTL.0) and using the MOVX instruction. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to **Section "10. Flash Memory" on page 111** for further details.

| Register       | Address          | Description                                        | Page |

|----------------|------------------|----------------------------------------------------|------|

| SFRs are liste | ed in alphabetic | al order. All undefined SFR locations are reserved |      |

| ACC            | 0xE0             | Accumulator                                        | 92   |

| ADC0CF         | 0xBC             | ADC0 Configuration                                 | 59   |

| ADC0CN         | 0xE8             | ADC0 Control                                       | 60   |

| ADC0GTH        | 0xC4             | ADC0 Greater-Than Compare High                     | 61   |

| ADC0GTL        | 0xC3             | ADC0 Greater-Than Compare Low                      | 61   |

| ADC0H          | 0xBE             | ADC0 High                                          | 59   |

| ADC0L          | 0xBD             | ADC0 Low                                           | 59   |

| ADC0LTH        | 0xC6             | ADC0 Less-Than Compare Word High                   | 62   |

| ADC0LTL        | 0xC5             | ADC0 Less-Than Compare Word Low                    | 62   |

| AMX0N          | 0xBA             | AMUX0 Negative Channel Select                      | 58   |

| AMX0P          | 0xBB             | AMUX0 Positive Channel Select                      | 57   |

| В              | 0xF0             | B Register                                         | 93   |

| CKCON          | 0x8E             | Clock Control                                      | 193  |

| CLKSEL         | 0xA9             | Clock Select                                       | 123  |

| CPT0CN         | 0x9B             | Comparator0 Control                                | 72   |

| CPT0MD         | 0x9D             | Comparator0 Mode Selection                         | 74   |

| CPT0MX         | 0x9F             | Comparator0 MUX Selection                          | 73   |

| CPT1CN         | 0x9A             | Comparator1 Control                                | 75   |

| CPT1MD         | 0x9C             | Comparator1 Mode Selection                         | 77   |

| CPT1MX         | 0x9E             | Comparator1 MUX Selection                          | 76   |

| DPH            | 0x83             | Data Pointer High                                  | 91   |

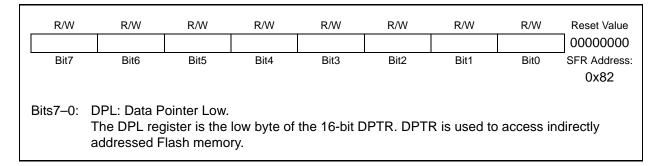

| DPL            | 0x82             | Data Pointer Low                                   | 90   |

| EIE1           | 0xE6             | Extended Interrupt Enable 1                        | 99   |

| EIP1           | 0xF6             | Extended Interrupt Priority 1                      | 100  |

| EMI0CN         | 0xAA             | External Memory Interface Control                  | 119  |

| FLKEY          | 0xB7             | Flash Lock and Key                                 | 117  |

| FLSCL          | 0xB6             | Flash Scale                                        | 117  |

| IE             | 0xA8             | Interrupt Enable                                   | 97   |

| IP             | 0xB8             | Interrupt Priority                                 | 98   |

| IT01CF         | 0xE4             | INT0/INT1 Configuration                            | 101  |

| OSCICL         | 0xB3             | Internal Oscillator Calibration                    | 122  |

| OSCICN         | 0xB2             | Internal Oscillator Control                        | 122  |

| OSCXCN         | 0xB1             | External Oscillator Control                        | 125  |

| P0             | 0x80             | Port 0 Latch                                       | 136  |

| POMDIN         | 0xF1             | Port 0 Input Mode Configuration                    | 136  |

| POMDOUT        | 0xA4             | Port 0 Output Mode Configuration                   | 137  |

| POSKIP         | 0xD4             | Port 0 Skip                                        | 137  |

| P1             | 0x90             | Port 1 Latch                                       | 138  |

| P1MDIN         | 0xF2             | Port 1 Input Mode Configuration                    | 138  |

| P1MDOUT        | 0xA5             | Port 1 Output Mode Configuration                   | 139  |

| P1SKIP         | 0xD5             | Port 1 Skip                                        | 139  |

| P2             | 0xA0             | Port 2 Latch                                       | 140  |

| P2MDIN         | 0xF3             | Port 2 Input Mode Configuration                    | 140  |

| P2MDOUT        | 0xA6             | Port 2 Output Mode Configuration                   | 141  |

## Table 8.3. Special Function Registers

| Register          | Address     | Description                     | Page |

|-------------------|-------------|---------------------------------|------|

| TMR2L             | 0xCC        | Timer/Counter 2 Low             | 198  |

| TMR2RLH           | 0xCB        | Timer/Counter 2 Reload High     | 198  |

| TMR2RLL           | 0xCA        | Timer/Counter 2 Reload Low      | 198  |

| TMR3CN            | 0x91        | Timer/Counter 3Control          | 201  |

| TMR3H             | 0x95        | Timer/Counter 3 High            | 202  |

| <b>TMR3L</b> 0x94 |             | Timer/Counter 3Low              | 202  |

| TMR3RLH           | 0x93        | Timer/Counter 3 Reload High     | 202  |

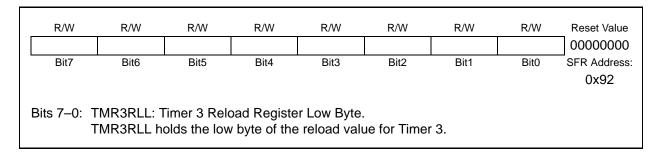

| TMR3RLL           | 0x92        | Timer/Counter 3 Reload Low      | 202  |

| VDM0CN            | 0xFF        | V <sub>DD</sub> Monitor Control | 107  |

| XBR1              | 0xE2        | Port I/O Crossbar Control 1     | 135  |

| XBR0              | 0xE1        | Port I/O Crossbar Control 0     | 134  |

| 0x84-0x86, 0x     | x96-0x97,   |                                 |      |

| 0xAB-0xAF, 0      | )xB4, 0xB9, |                                 |      |

| 0xBF, 0xC7, 0     | 0xC9, 0xCE, | Reserved                        |      |

| 0xCF, 0xD2, 0     |             |                                 |      |

| 0xDF, 0xE3, 0     | 0xE5, 0xF5  |                                 |      |

### Table 8.3. Special Function Registers (Continued)

#### 8.2.7. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic 1. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

### SFR Definition 8.1. DPL: Data Pointer Low Byte

### 8.3.2. External Interrupts

The /INT0 and /INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The IN0PL (/INT0 Polarity) and IN1PL (/INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (**Section "17.1. Timer 0 and Timer 1" on page 187**) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | /INT0 Interrupt              |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | /INT1 Interrupt              |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

/INT0 and /INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 8.11). Note that /INT0 and /INT0 Port pin assignments are independent of any Crossbar assignments. /INT0 and /INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to /INT0 and/or /INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see **Section** "13.1. Priority Crossbar Decoder" on page 131 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the /INT0 and /INT1 external interrupts, respectively. If an /INT0 or /INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

#### 8.3.3. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP or EIP1) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 8.4.

### 8.3.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

### 8.4. Power Management Modes

The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not effected). Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power. SFR Definition 8.12 describes the Power Control Register (PCON) used to control the CIP-51's power management modes.

Although the CIP-51 has Idle and Stop modes built in (as with any standard 8051 architecture), power management of the entire MCU is better accomplished by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off the oscillators lowers power consumption considerably; however, a reset is required to restart the MCU.

#### 8.4.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to **Section "9.6. PCA Watchdog Timer Reset" on page 108** for more information on the use and configuration of the WDT.

# Note: Any instruction that sets the IDLE bit should be immediately followed by an instruction that has 2 or more opcode bytes. For example:

// in 'C':

PCON |= 0x01; // set IDLE bit

PCON = PCON; // ... followed by a 3-cycle dummy instruction

; in assembly:

ORL PCON, #01h ; set IDLE bit

MOV PCON, PCON; ... followed by a 3-cycle dummy instruction

If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from IDLE mode when a future interrupt occurs.

NOTES:

NOTES:

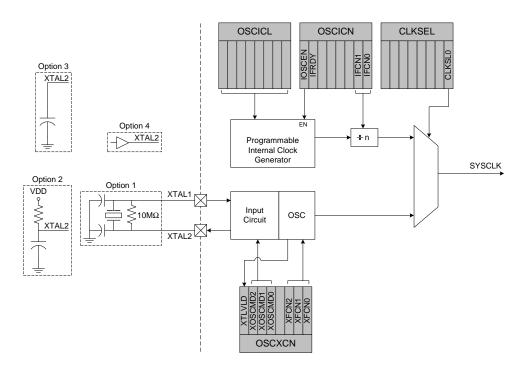

## 12. Oscillators

C8051F31x devices include a programmable internal oscillator and an external oscillator drive circuit. The internal oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 12.1. The system clock can be sourced by the external oscillator circuit, the internal oscillator, or a scaled version of the internal oscillator. The internal oscillator's electrical specifications are given in Table 12.1 on page 123.

Figure 12.1. Oscillator Diagram

### 12.1. Programmable Internal Oscillator

All C8051F31x devices include a programmable internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be programmed via the OSCICL register as defined by SFR Definition 12.1 OSCICL is factor calibrated to obtain a 24.5 MHz frequency.

Electrical specifications for the precision internal oscillator are given in Table 12.1 on page 123. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

### 12.2. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 12.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 12.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 12.4).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see **Section "13.1. Priority Crossbar Decoder" on page 131** for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See **Section "13.2. Port I/O Initialization" on page 133** for details on Port input mode selection.

### 12.3. System Clock Selection

The CLKSL0 bit in register CLKSEL selects which oscillator is used as the system clock. CLKSL0 must be set to '1' for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal and external oscillator, so long as the selected oscillator is enabled and has settled. The internal oscillator requires little start-up time and may be selected as the system clock immediately following the OSCICN write that enables the internal oscillator. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use as the system clock. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external oscillator is settled. **To avoid reading a false XTLVLD**, in crystal mode software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD. RC and C modes typically require no startup time.

|         | P0                                    |   |   |   |   |   |   |                                  |   | P1 |   |   |                        |   |   |   | P2 |   |   |   |   |                                                                                                                 |   |   |

|---------|---------------------------------------|---|---|---|---|---|---|----------------------------------|---|----|---|---|------------------------|---|---|---|----|---|---|---|---|-----------------------------------------------------------------------------------------------------------------|---|---|

|         |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| PIN I/O | 0                                     | 1 | 2 | 3 | 4 | 5 | 6 | 7                                | 0 | 1  | 2 | 3 | 4                      | 5 | 6 | 7 | 0  | 1 | 2 | 3 | 4 | 5                                                                                                               | 6 |   |

| ТХО     |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| RX0     |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| SCK     |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| MISO    |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| MOSI    |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| NSS*    |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| SDA     |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| SCL     |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| CP0     |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| CP0A    |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   | e de la come |   |   |

| CP1     |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   | lable                                                                                                           |   |   |

| CP1A    |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   | Signals Unavailable                                                                                             |   |   |

| SYSCLK  |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   | ň                                                                                                               |   |   |

| CEX0    |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   | nals                                                                                                            |   |   |

| CEX1    |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   | Sig                                                                                                             |   |   |

| CEX2    |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| CEX3    |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| CEX4    |                                       |   | 1 |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   | 1 |                                                                                                                 |   |   |

| ECI     |                                       |   | 1 |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   | ]                                                                                                               |   |   |

| то      |                                       |   | 1 |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

| T1      |                                       |   |   |   |   |   |   |                                  |   |    |   |   |                        |   |   |   |    |   |   |   |   |                                                                                                                 |   | 1 |

|         | 0 0 <u>1 1</u> 0 0 0 0<br>P0SKIP[0:7] |   |   |   |   |   | 0 | 0 0 0 0 0 0 0 0 0<br>P1SKIP[0:7] |   |    |   |   | 0 0 0 0<br>P2SKIP[0:3] |   |   |   |    |   |   |   |   |                                                                                                                 |   |   |

SF Signals Special Function Signals are not assigned by the Crossbar. When these signals are enabled, the Crossbar must be manually configured to skip their corresponding port pins.

\*Note: NSS is only pinned out in 4-wire SPI mode.

Note: P1.6,P1.7,P2.6,P2.7 only available on the C8051F310/1/2/3/4/5; P1SKIP[7:6] should always be set to 11b for the C8051F316/7 devices.

### Figure 13.4. Crossbar Priority Decoder with Crystal Pins Skipped

Registers XBR0 and XBR1 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when the UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, pending the state of the NSS-MD1-NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

### 13.2. Port I/O Initialization

Port I/O initialization consists of the following steps:

- Step 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- Step 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- Step 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- Step 4. Assign Port pins to desired peripherals.

- Step 5. Enable the Crossbar (XBARE = (1')).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a '1' indicates a digital input, and a '0' indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 13.4 for the PnMDIN register details.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is '0', a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a '0' to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to '1' enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Configuration Wizard utility of the Silicon Labs IDE software will determine the Port I/O pin-assignments based on the XBRn Register settings.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. Port output drivers are disabled while the Crossbar is disabled.

| R/W      | R/W                                                                                                                            | R/W                                                                    | R/W                                       | R/W                          | R/W         | R/W          | R/W           | Reset Value  |

|----------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------|------------------------------|-------------|--------------|---------------|--------------|

| P2.7     | P2.6                                                                                                                           | P2.5                                                                   | P2.4                                      | P2.3                         | P2.2        | P2.1         | P2.0          | 11111111     |

| Bit7     | Bit6                                                                                                                           | Bit5                                                                   | Bit4                                      | Bit3                         | Bit2        | Bit1         | Bit0          | SFR Address: |

|          |                                                                                                                                |                                                                        |                                           |                              |             | (bi          | t addressable | e) 0xA0      |

| Bits7–0: | P2.[7:0]<br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>Read - Alway<br>pin when cor<br>0: P2.n pin is<br>1: P2.n pin is | Output.<br>o Output (hi<br>ys reads '1'<br>ofigured as<br>s logic low. | gh impedar<br>if selected<br>digital inpu | nce if corres<br>as analog i | sponding P2 | 2MDOUT.n     | ,             | reads Port   |

| Note:    | Only P2.0–P2                                                                                                                   | .5 are assoc                                                           | iated with Po                             | ort pins on the              | e C8051F31  | 6/7 devices. |               |              |

|          |                                                                                                                                |                                                                        |                                           |                              |             |              |               |              |

### SFR Definition 13.11. P2: Port2

## SFR Definition 13.12. P2MDIN: Port2 Input Mode

| R/W                                                                                                                                                                                                                                                                                                                                                            | R/W                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value                      |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|----------------------------------|--|--|--|--|

| Bit7                                                                                                                                                                                                                                                                                                                                                           | Bit6                                                                                  | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | BitO | 11111111<br>SFR Address:<br>0xF3 |  |  |  |  |

| <ul> <li>Bits7–0: Analog Input Configuration Bits for P2.7–P2.0 (respectively).</li> <li>Port pins configured as analog inputs have their weak pullup, digital driver, and digital receiver disabled.</li> <li>0: Corresponding P2.n pin is configured as an analog input.</li> <li>1: Corresponding P2.n pin is not configured as an analog input.</li> </ul> |                                                                                       |      |      |      |      |      |      |                                  |  |  |  |  |

| Note:                                                                                                                                                                                                                                                                                                                                                          | <b>Note:</b> Only P2.0–P2.5 are associated with Port pins on the C8051F316/7 devices. |      |      |      |      |      |      |                                  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |      |      |      |      |      |      |                                  |  |  |  |  |

### SFR Definition 17.14. TMR3RLL: Timer 3 Reload Register Low Byte

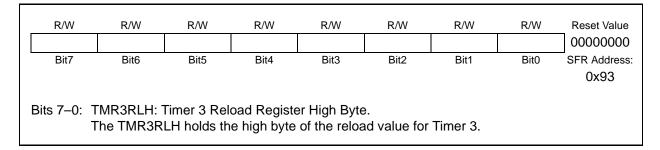

### SFR Definition 17.15. TMR3RLH: Timer 3 Reload Register High Byte

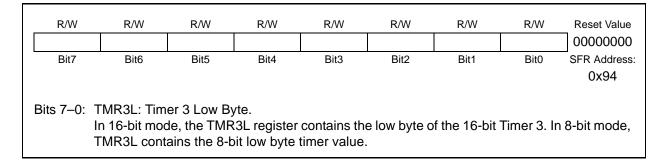

### SFR Definition 17.16. TMR3L: Timer 3 Low Byte

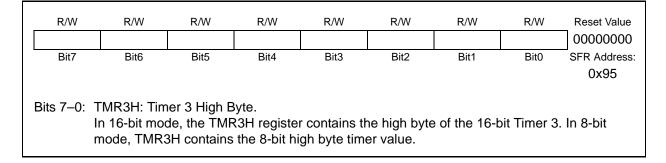

### SFR Definition 17.17. TMR3H Timer 3 High Byte

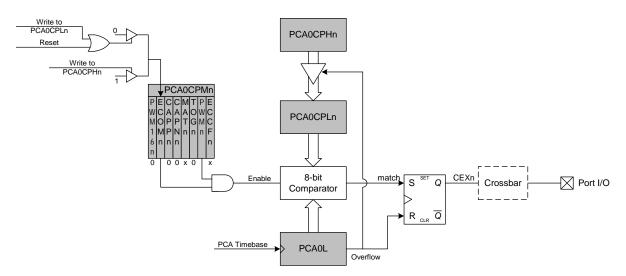

### 18.2.5. 8-Bit Pulse Width Modulator Mode

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer. The duty cycle of the PWM output signal is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 18.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register enables 8-Bit Pulse Width Modulator mode. The duty cycle for 8-Bit PWM Mode is given by Equation 18.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

### Equation 18.2. 8-Bit PWM Duty Cycle

$DutyCycle = \frac{(256 - PCA0CPHn)}{256}$

Using Equation 18.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to '0'.

Figure 18.8. PCA 8-Bit PWM Mode Diagram